# Optimizing heat harvesting in a membrane based planar $\mu$ TEG: modelling and fabrication, & vice versa

Zahia Bougrioua, Ibrahim Bel-Hadj, Katir Ziouche

#### ▶ To cite this version:

Zahia Bougrioua, Ibrahim Bel-Hadj, Katir Ziouche. Optimizing heat harvesting in a membrane based planar  $\mu$ TEG: modelling and fabrication, & vice versa. ECT 2019 – 17th European Conference on Thermoelectrics, Sep 2019, Limassol, Cyprus. . hal-02906736

HAL Id: hal-02906736

https://hal.science/hal-02906736

Submitted on 9 Dec 2020

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

Limassol (CYPRUS) September 23rd-25th, 2019

# Optimizing heat harvesting in a membrane based planar µTEG: modelling and fabrication, & vice versa

Zahia BOUGRIOUA\*, Ibrahim BEL-HADJ, Katir ZIOUCHE

IEMN. Institut d'Electronique de Micro-électronique et de Nanotechnologie. CNRS and Lille University, avenue Poincaré, 59652 Villeneuve d'Ascq, FRANCE

F-mail \* zahia.bougrioua@iemn.fr

#### 1/ Introduction

Micro-thermoelectric generators ( $\mu TEGs$ ) are energy harvesting solutions to supply electrical power for autonomous microsystems and other miniature applications. We study here original all-Silicon  $\mu TEGs$  with a planar configuration in which the heat to harvest flows in-plane of a TE thin film. Such configuration in which the heat to harvest flows in-plane or a LE tinh rilm. Such planar modules are based on a polySi/Au thermopile periodically distributed onto dielectric membranes; a heat-collector permits to concentrate the energy to harvest onto half the junctions of the thermopile. This planar topology allows the implementation of thermocouples with a high aspect ratio compared to classical vertical TEGs. Heat concentrator is able to collect any form of lost heat (even evaporation enthalpy a priori, or radiation...)

### 2. IEMN µTEG design & process

1st Initial design: semi-3D micro thermoelectric generator, planar structure.

CMOS compatible process of microfabrication. Surface foot -print ~ 1/3 cm², build up with 2 parts:

- Bottom part: N<sub>M</sub> membranes periodically etched in a Si(100) substrate & made of a dielectric bilayer (1,4µm SiO<sub>2</sub>/Si<sub>4</sub>N<sub>y</sub>). A poly-Silicon (pSi,  $\mathbf{e}_{11}$ =0.3-0.9  $\mu$ m thick, first thermoelement) stripe is deposited on this bilayer & is periodically covered with gold ( $\mathbf{A}_{11}$ ,  $\mathbf{e}^{21}$  thermoelement). This defines a **zig-zag shaped thermopile**, series of pSi/Au thermocouples (TC).  $\mathbf{N}_{M}$  tested : 1, 2, 5, 10  $\mathbf{E}_{11}$  and  $\mathbf{E}_{11}$  and  $\mathbf{E}_{12}$  are  $\mathbf{E}_{13}$  and  $\mathbf{E}_{12}$  are  $\mathbf{E}_{13}$  and  $\mathbf{E}_{12}$  are  $\mathbf{E}_{13}$  and  $\mathbf{E}_{13}$  are  $\mathbf{E}_{13}$  are  $\mathbf{E}_{13}$  and  $\mathbf{E}_{13}$  are  $\mathbf{E}_{13}$  are  $\mathbf{E}_{13}$  and  $\mathbf{E}_{13}$  are  $\mathbf{E}_{13}$  are  $\mathbf{E}_{13}$  and  $\mathbf{E}_{13}$  are  $\mathbf{E}_{13}$  and  $\mathbf{E}_{13}$  are  $\mathbf{E}_{13}$  and  $\mathbf{E}_{13}$  are  $\mathbf{E}_{13}$  are  $\mathbf{E}_{13}$  are  $\mathbf{E}_{13}$  and  $\mathbf{E}_{13}$  are

- \* The pSi width (L =50, 70 or 200 μm) is larger than the Au plated parts (10 μm)  $\Rightarrow$  this **modulated-width** thermopile has a reduced internal electrical resistance R<sub>INT</sub> → electrical & thermal simulations show a gain in output power generated for larger stripes

- \* The TC number, N, is a function of  $N_M$  and  $L: N=x.N_M$  (x=144, 112, 46 for  $L=50, 70, 200\mu$ ). For fixed L,  $R_{INT}$  is the same.

- \* The whole is covered with a 15 $\mu$ m thick Polylmide layer (robustness & electrical isolation): 15 $\mu$ m is a compromise (for 2m- $\mu$ G up thigher  $\Delta$ T for 30 $\mu$ m PI but the benefice fastly diminish with N<sub>M</sub> for 10 $\mu$ TEG it is even worse; see evolution in figure section 4.C/...)

- Second part: heat concentrator HC ( $surf=0.3cm^3$ ) also fabricated starting from Si(100). It has as much pillars ( $N_{M}$ ) as there are membranes ( $200\mu$  thick,  $5.1 \text{ mm} \log \&$  width optimised versus  $N_{M}$ ). Pillars canalyze the heat flow to harvest  $(\Phi$ , that arrives on its surface into half of the thermopile junctions. A periodical  $\Delta T$  is created at each TC.

The HC has also 4 bosses at its corners (mechanical stability, avoid membranes breaking) that short-cut one part of  $\Phi$ :  $\Phi_{\text{Total}} - \Phi_{\text{Dillers}} + \Phi_{\text{Borres}} + \Phi_{\text{convection}} + \Phi_{\text{conviction}}$ The generated Seebeck voltage at thermopile ends is :  $V_S = N. a_{TE/Au} . \Delta T_{TC}$

#### 3. Characterisation of µTEG performance

Typical µTEG experimental behaviour; at RT, the heat to harvest is varied from low to very high (Φ:0-aw)

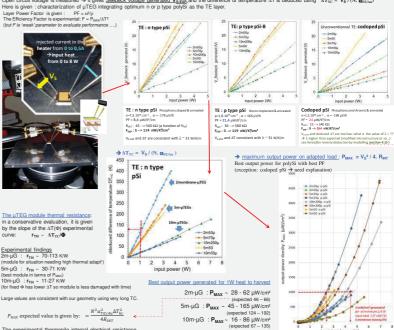

Open circuit voltage is measured -9 it gives <u>Seebeck voltage generated V\_s.p.p.</u> and the difference of temperature ΔT is deduced using  $\Delta T_{TC} = V_g / (N. \sigma_{TC/An})$ Here is given: characterization of LTEG interacting optimum n or p two policy is at the TE layer.

→ However, in any case, these values are low because of large internal electrical resistance R<sub>INT</sub> of the thermopiles pSi/Au.

μTEGs with codoped pSi: not taken into account

#### 4. Thermal Modelling - Reducing heat losses & considering superior TE layer properties

#### Renewed design to improve the performance: a few routes to be validated by forthcoming experiments

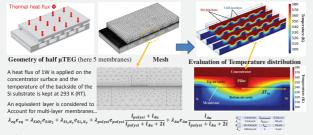

• 4.A/ 3D thermal modelling using COMSOL Multiphysics®, 4.D/ Modelling the impact of TE thermal conductivity

#### 4.B/ Geometrical structure optimisation (Φ=1W)

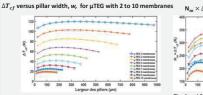

The difference of temperature at each TC in the thermopile has a maximum at an optimum pillar width value

$N_m \times \Delta T_{cf}$  versus w  $\rightarrow$  indicative of  $P_{MAX}$

The difference of temperature being higher for

μTEGs with 4 membranes, these latter will have the highest thermal resistance r<sub>TH</sub> compared to 5m-µTEG

→ to be taken into account in future design

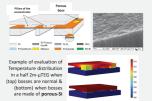

• 4.C/ Reducing the heat lost in

#### the bosses of the heat-concentrator Reducing $\Phi_{\text{Bosses}}$ by lowering bosses thermal conductivity: done via

local fabrication of Porous Silicone by anodization then oxidization (annealing at high temperature) λ<sub>Si</sub> = 140 W/m/K VERSUS λ<sub>porous-Si oxidized</sub> ~1 W/m/K

ating the influence of two thicknesses : i/ of porous bosses and ii/ of polyimide protection layer

## & optimisation of generated output power b/ Considering different TE layers with different thermal conductivities \( \bar{\lambda} \) a/ Considering a metal TE layer with good PF and which im less R... (reduced value and no parasitic contact resistance) tan/Au thermopile $\Delta T_{cf}$ to be generated as a function of input heat to harvest trimental codoping →To be confirmed λ= 31.4 λ= 60 VS TE laver λ λ= 140 TE thermal conductivity $\lambda$ (W/K/m) -<u>Cases for TE layers with PF 8 or 21:</u> --Experimental points: p and n type polySi as for p-pSi layer eng-280m, an extrapolation for 600nm is calculate. --Nanostructured TE layer taken with \( \lambda = 4 \) W/K/m

All-Silicon planar μΤΕG with a modular thermal resistance (11-113 K/W) are fabricated by CMOS compatible microtechnology, integrating a thermopile built up with microfnano-structured polySi as TE material. The number of membranes on which is periodically laying the thermopile can be varied and the heat to harvest is collected through a pillar-based Sconcentrator. The weak point of our μΤΕGs is their high internal electrical resistance: P<sub>MAX</sub> are moderate: up to 62μW/cm², 164μW/cm², and 86μW/cm², for respectively 2,5 or 10 membranes μΤΕGs (1W heat injected).

To better clarify further improvements to be carried out, while keeping the high  $r_{\rm TM}$  values, COMSOL 3D thermal simulation was done for different new

- the optimum membrane number is 4 (not 5): same  $P_{MAX}$  and higher  $r_{TH}$  use larger stripe (1=200 $\mu$ m versus currently 70 $\mu$ m) should be considered (20% increase in  $P_{MAX}$ )

- nation of parasitic heat losses:

\*Polyimide layer: confirmation of an optimal thickness (around 15µm)

\*a modified hear-collector/concentrator with corner bosses made of porous Silicon allows to generate up to 64% more power, but this requires to be validated by experiments (soon)

- Higher Power Factor (PF) effect: considering a thermopile integrating a Constantan layer can double P<sub>MAX</sub> (~300 µW/cm² for 1W injected). Compared to modules with *non optimum polyši* (ie. with Pf < 10 µW/k?m or so) this represent a reliable way to enhance P<sub>MAX</sub> by a factor of up to 3. However this is only valid for a Ts stripe width of 1:e50 µm (for larger It decreases) ⇒ this is being evaluated (together with 4-membranes configuration and porous bosses in the heat-concentrator)

- High PF but bad microstructure of the TE layer: it results in poorer module performance ("cold case" explained: codoped polySi layer may have λ>60W/K/m...)

- Considering nanostructured TE layer with a thermal conductivity λ reduced by a factor of 10 compared to polySi (ie even better than Cn) should result in a higher ΔT (24,6% for 5m-μTεG), so in a P<sub>Max</sub> 65% higher (assuming same PF as our best ρ-type polySi) in such cases 550-660 μy(m<sup>2</sup>n Should be obtained for a 5m-μTeE harvesting 1 Winput heat.

de Microélectronique et de Nanotechnologie