## High-Frequency Noise Characterization and Modeling of Graphene Field-Effect Transistors

Marina Deng, Dalal Fadil, Wei Wei, Emiliano Pallecchi, Henri Happy, Gilles Dambrine, Magali de Matos, Thomas Zimmer, Sébastien Frégonèse

#### ▶ To cite this version:

Marina Deng, Dalal Fadil, Wei Wei, Emiliano Pallecchi, Henri Happy, et al.. High-Frequency Noise Characterization and Modeling of Graphene Field-Effect Transistors. IEEE Transactions on Microwave Theory and Techniques, 2020, 68 (6), pp.2116-2123. 10.1109/TMTT.2020.2982396. hal-02540064

### HAL Id: hal-02540064 https://hal.science/hal-02540064v1

Submitted on 5 Jul 2021

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# High Frequency Noise Characterization and Modelling of Graphene Field Effect Transistors

M. Deng, *Member*, *IEEE*, D. Fadil, W. Wei, E. Pallecchi, H. Happy, G. Dambrine, *Fellow IEEE*, M. De Matos, T. Zimmer, *Senior Member*, *IEEE*, S. Fregonese

Abstract— This paper presents the small-signal and noise characterisation of different technologies based on CVD and SiC graphene field effect transistors. The noise model, built on noise figure measurements under  $50\Omega$  using the  $F_{50}$  method, was verified by additional source-pull measurements, with a special care to the GFET stability. The four noise parameters were then extracted using the validated  $F_{50}$  model up to 18 GHz and correlations between noise and small-signal parameters were shown for two different configurations: top-gated and back-gated GFETs.

Index Terms— FET, graphene, high frequency noise, sourcepull, small signal model

#### I. INTRODUCTION

RAPHENE research activities for circuit design have recently started and analogue and RF circuits have already been demonstrated up to microwave frequency range, despite the low maturity of the graphene material. Benefiting from the high carrier mobility and the ambipolar nature of the electronic transport in the graphene field effect transistor (GFET), interesting performances for key RF circuits for signal transmission and reception continue to be reported: [1]-[7]. Most recent results report an 88-100 GHz mixer exhibiting a 18-19 dB conversion loss [1] and an amplifier with 3.4 dB gain and 6.2 dB noise figure at 14.3 GHz, with a matching network only based on microstrip lines [4].

A good modelling of the graphene transistor, based on DC and RF device characterization, is essential for circuits design. So far, only few works related to GFET high frequency (HF) noise characterization and modelling have been reported [8]-[13]. Tanzid et al. reported in [9] the four noise parameters extraction using source-pull measurements of a GFET transistor, biased at the highest possible  $g_m$ . In regards to the tremendous literature of the graphene FET and  $f_T/f_{max}$  measurements, the poor literature on HF noise characterization topic is directly correlated to the complexity of this characterization type. In fact, the HF noise measurements are

highly complex and require access to rare characterization facilities containing a source-pull tuner together with a HF noise measurement bench.

noise measurements Actually, source-pull complicated calibration, since the source-pull tuner and the noise receiver need to be calibrated before measuring the device under test. Then, DC and S-parameters of the device under test have to be recorded before the noise figure measurements. This long characterization process may degrade the noise measurement accuracy, due to eventual stochastic errors accumulation and degradation of the device under test. These measurements require automatic source-pull measurements that can set the device under an unstable operation by presenting a source coefficient reflection out of its stability region in the Smith chart, leading to oscillations and a potential damage of the transistor. Hence, considering the low maturity of the devices and the difficulty to fabricate them, a special care must be taken for their measurements in order to avoid the transistor's breaking/breakdown.

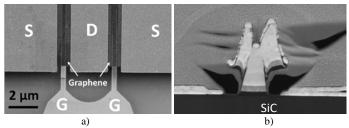

In this paper, we propose and validate a safe and timeefficient noise characterization and modelling procedure based on the measurement of noise figures under 50  $\Omega$  ( $F_{50}$ ) on GFET devices, as initiated in our previous work up to 6 GHz using only  $F_{50}$  measurements [8]. Although the  $F_{50}$  method proved its efficiency on HEMT [15] and MOSFET [16] devices, it has not been validated so far on emerging transistor technologies such as GFET. In order to validate this technique, the noise model elaborated using  $F_{50}$  method was verified for various source impedances thanks to selective source-pull measurements on GFET devices out of their unstable region at 15 GHz. This safe methodology was applied to two different GFET technologies (see Fig. 1): 1) two back-gated graphene transistors with a channel made by graphene grown by chemical vapor deposition (CVD) on copper, 2) three top-gated graphene transistors based **CVD** graphene grown

Manuscript received October 15, 2019; revised December 28, 2020; accepted January 27, 2020.

This work was funded by the European Union's Horizon 2020 research and innovation program under Grant Agreement No. GrapheneCore2 785219 (Graphene Flagship), and was partly supported by the French RENATECH network.

This paper is an expanded version from the IEEE MTT-S International Microwave Workshop Series on Advanced Materials and Processes 2019, Bochum, Germany, July 16th-18th, 2019.

(Corresponding author: Marina DENG.)

M. Deng, M. De Matos, T. Zimmer and S. Fregonese are currently with IMS laboratory, University of Bordeaux (e-mail: marina.deng@ims-bordeaux.fr).

D. Fadil, W. Wei, E. Pallecchi, H. Happy and G. Dambrine are with Univ. Lille, CNRS, UMR 8520 - IEMN, F-59000 Lille, France.

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier XXXXXXXXXXXXX

Fig. 1. Graphene transistors structures: a) SEM image of a back-gated CVD GFET: b) Cross section of a top gated GFET on SiC substrate

Silicon-Carbide (SiC) substrate. The fabrication process is based on our previous work: [11] for CVD on SiO<sub>2</sub> transistors and [13] for CVD on SiC.

First, section II explains the small-signal and noise model parameter extraction procedure. Then, section III details the noise model validation strategy, which leads to the noise parameters extraction results up to 18 GHz. This noise characterization procedure was applied to obtain the results presented in [14].

#### II. GRAPHENE FET HIGH FREQUENCY MODELLING

#### A. Measurement setup

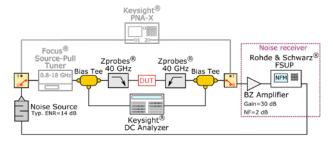

The 0.8-18 GHz high frequency noise and source-pull measurement bench is depicted in Fig. 2. The noise receiver is composed of Rohde & Schwarz® FSUP signal source analyzer and a BZ® 0.8-18 GHz wideband amplifier. Using switches at port 1 and port 2, S-parameter measurements up to 26.5 GHz can also be performed with a Keysight® PNA-X. Then, using the same bench, DC, S-parameter measurements and noise measurements up to 18 GHz were carried out under multiple bias points.

#### B. Small-signal GFET modelling

#### 1) Extrinsic model parameters' extraction

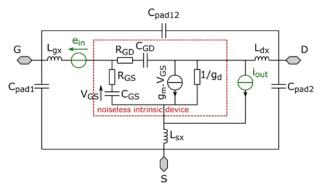

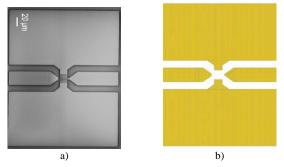

Based on the field-effect transistor noise model described in [17], the small-signal equivalent circuit that we used is illustrated in Fig. 3. The extrinsic part represents the parasitic contribution originated from the accesses of the transistor. They can be modelled by capacitances ( $C_{pad1}$ ,  $C_{pad12}$  and  $C_{pad2}$ ) and inductances ( $L_{gx}$ ,  $L_{dx}$  and  $L_{sx}$ ). The capacitances are modelled by a  $\pi$ -network of three capacitances and extracted from a measurement of an open structure fabricated on the same substrate as GFET (see Fig. 4-a-b). The pad inductances are assessed thanks to an ADS-momentum electromagnetic simulation and adjusted on the measured S-parameters of the GFET, because no short test structures were available for the transistors under test on the measured samples. The parasitic contribution of these extrinsic parameter are subtracted out of each transistor S-parameters' measurement using a deembedding correction.

#### 2) Intrinsic model parameters' extraction

For a given bias point, the intrinsic model parameters are extracted from the de-embedded S-parameters of the GFET using a simple matrix calculation. It is worth to notice that for the intrinsic circuit considered here, the contact resistances are not extracted.

Fig. 2. Block diagram of the on-wafer F50 noise measurement setup up to 18 GHz.

Fig. 3. GFET small-signal and noise equivalent circuit.

Fig. 4. Picture of test structures: a) transistor, b) Open-Pad dedicated to transistor S-parameters measurement correction (de-embedding).

The same small-signal and noise characterization, modelling procedure was applied to 9 transistors totally. The devices belong to five wafers:

- CVD1: back-gated transistors on silicon substrate with Hall mobility of 2800 cm²/V.s and contact resistance (Rc) of 2 k $\Omega$ . $\mu$ m

- CVD2: back-gated transistors on silicon substrate with Hall mobility of 2100 cm²/V.s and contact resistance of 125  $\Omega.\mu m$

- SiC\_A: bilayer graphene growth by CVD on SiC substrate with mobility of 850 cm<sup>2</sup>/Vs,  $R_C$ =650  $\Omega$ . $\mu$ m

- SiC\_B: monolayer graphene growth by CVD on SiC substrate with mobility of 3200 cm<sup>2</sup>/Vs

- SiC\_C: graphene growth by graphitization of SiC substrate with mobility of 600 cm<sup>2</sup>/Vs,  $R_C$ =990  $\Omega.\mu m$

For transistors on silicon substrate, the mobilities were measured from Van der Pauw structures using Hall effect measurement. For transistors on SiC substrate, the mobilities were extracted from non-contact Terahertz spectroscopic measurement technique [18]. The transmission line measurement (TLM) approach is used to extract contact

resistance as illustrated in [19]. The TLM structures were fabricated on the same together chip with graphene transistors.

Table I summarizes the best  $f_T$  and  $f_{max}$  couples for each type of transistors.

As an example, the small-signal characterization and modelling procedure of the SiC\_A GFET will be detailed in the paper. This transistor under test was biased at a fixed value of 1.5 V drain-to-source voltage (close to maximum  $g_m$  for this transistor) and the gate-to-source voltage was swept from 0 to 1.2 V with a 0.1 V-step.

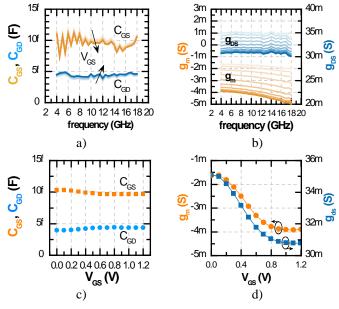

In the small-signal equivalent circuit parameters extraction procedure, the intrinsic capacitances' mean values are averaged over the whole measurement frequency range, the intrinsic resistances' mean are obtained at high frequency (since they are masked by the capacitances at lower frequencies), between 14 and 16 GHz, and the conductance at 5 GHz (see Fig. 5). The small-signal extrinsic and intrinsic parameters extraction results are respectively given in Table II and Table III.

TABLE I

BEST EXTRINSIC (AS-MEASURED) RF PERFORMANCES OF THE 5 CVD AND SIC

| GFET TECHNOLOGIES |         |         |         |         |        |  |

|-------------------|---------|---------|---------|---------|--------|--|

|                   | CVD1    | CVD2    | SiC_A   | SiC_B   | SiC_C  |  |

| Wg                | 2×12 μm | 2×12 μm | 2×15 µm | 2×15 μm | 12 µm  |  |

| $l_g$             | 200 nm  | 300 nm  | 80 nm   | 80 nm   | 140 nm |  |

| $f_T$             | 5 GHz   | 19 GHz  | 28 GHz  | 19 GHz  | 25 GHz |  |

| $f_{max}$         | 3 GHz   | 12 GHz  | 17 GHz  | 17 GHz  | 19 GHz |  |

|                   |         |         |         |         |        |  |

Fig. 5. Intrinsic capacitances and conductances extraction versus frequency and gate voltage:  $V_{DS}{=}1.5V$ ,  $V_{GS}{=}0.1.2V$  with 0.1V-step. Transistor under test: SiC\_A GFET, W=2x12  $\mu$ m, L=150 nm

TABLE II

EXTRINSIC PARAMETERS FOR CVD2 AND SIC\_A GFETS

|   |       | $C_{pad1}$ | C <sub>pad12</sub> | $C_{pad2}$ | $\mathbf{L}_{\mathbf{g}\mathbf{x}}$ | $L_{\text{dx}}$ | $\mathbf{L}_{\mathbf{sx}}$ |

|---|-------|------------|--------------------|------------|-------------------------------------|-----------------|----------------------------|

| _ | CVD2  | 8.1 fF     | 1 fF               | 8.2 fF     | 58 pH                               | 38 pH           | 1pH                        |

|   | SiC_A | 8.2 fF     | 0.7 fF             | 7.8 fF     | 60 pH                               | 40 pH           | 0 pH                       |

| INTRINSIC | INTRINSIC PARAMETERS FOR CVD2 SIC_A GFET AT VG=0.7 AND TV |                 |                           |                                     |  |  |  |

|-----------|-----------------------------------------------------------|-----------------|---------------------------|-------------------------------------|--|--|--|

|           | $R_{GS}/R_{GD/}$                                          | $C_{GS}/C_{GD}$ | $\mathbf{g}_{\mathbf{m}}$ | $\mathbf{g}_{\mathbf{d}\mathbf{s}}$ |  |  |  |

| CVD2      | 63 / 98 Ω                                                 | 38 / 45 fF      | -10.3 mS                  | 26 mS                               |  |  |  |

| SiC A     | 100/100 O                                                 | 97/44fF         | -3 8 mS                   | 31 mS                               |  |  |  |

#### C. High frequency noise modelling

The noise equivalent circuit is depicted in Fig. 3 and is based on [17]. The intrinsic part of the device is considered as noiseless. The noise model relies on two extrinsic uncorrelated noise sources, respectively an input voltage noise source  $e_{in}$  and an output current noise source  $i_{out}$ . These two noise sources are related to the electrical equivalent circuit as given in equations 1 and 2:

$$\overline{e_{in}^2} = 4kT_{in}Re(H_{11})\Delta f \tag{1}$$

$$\overline{i_{out}^2} = 4kT_{out}Re(H_{22})\Delta f \tag{2}$$

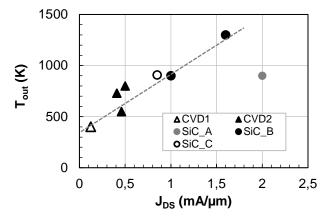

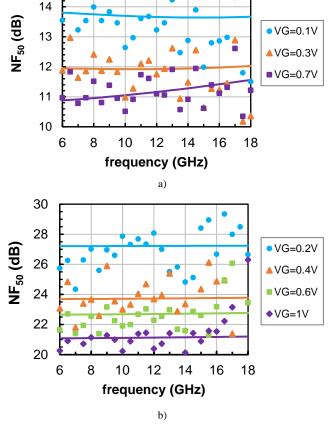

Following the noise modelling procedure described in [17],  $T_{in}$  is approximated by the ambient temperature and  $T_{out}$  is adjusted to fit the measured noise figure up to 18 GHz curve for each  $V_{GS}$  value (see Fig. 6). With measured noise figures standing between 20 and 30 dB for SiC GFET (see Fig. 7-a) and between 10 and 16 dB for CVD GFET (See Fig. 7-b), the T<sub>out</sub> values range between 400 and 1300 K. These high values of noise figures or noise temperatures can be explained by the dependence of  $T_{out}$  on the drain current density  $J_{DS}$ , which is specific to field effect transistors [20][21]. As shown in Fig. 6,  $T_{out}$  shows a linear dependence on  $J_{DS}$  for most of the measured CVD and SiC GFETs, which were biased close to maximum  $g_m$ . In fact, SiC GFETs feature higher current densities due to a high residual carrier density in the graphene sheet compared to CVD GFETs which reduces the access resistance. Furthermore, the  $NF_{50}$  measurement accuracy (see Fig. 7) is affected by the impedance mismatch at the input of the transistor. Indeed, under 50  $\Omega$  input impedance, the graphene transistors show a small gain ( $|S_{2l}|$ <-15 dB) and a high level of noise, which results in a  $\pm 1$  dB  $NF_{50}$  measurement accuracy.

Fig. 6. Output equivalent temperature versus drain-to-source current density for different technologies of CVD and SiC GFETs. The dashed line only provides a visual guide (not a fit to the experimental data).

15

Fig. 7. Measured and simulated noise figure under 50  $\Omega$  versus frequency up to 18 GHz for: a) CVD2 GFET; b) SiC\_A GFET.

#### III. NOISE PARAMETER EXTRACTION

#### A. Small-signal model validation up to 18 GHz

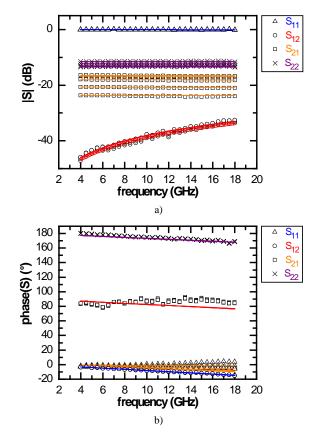

An accurate modelling of the transistor's S-parameters is crucial to accurately estimate the transistor's gain and precisely assess the optimum noise reflection coefficient  $\Gamma_{opt}$ .

Following the small-signal equivalent circuit procedure described in Section II, a satisfying agreement was obtained from 4 to 18 GHz between the simulated and the measured S-parameters for SiC\_A GFET as shown in Fig. 8. This guarantees the accuracy of the simulated gain through the final small-signal and noise model.

## B. Noise model validation by source-pull measurements at 15 GHz

The source-pull tuner was used to vary the source impedance,  $\Gamma_S$ , presented to the transistor at its gate input terminal. While monitoring the drain current to detect any instability that could damage the transistor, we chose to first increase the magnitude and then increase the phase by keeping the magnitude constant.

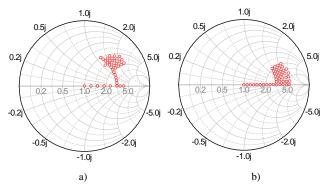

An example of the design of experiment (DOE) is given in Fig. 9. The quarter top right of the Smith Chart was selected in order to be close to the optimum noise area, which approximately corresponds to the conjugate of parameter  $S_{11}$  for FETs.

Fig. 8. Measured and simulated S-parameters versus frequency up to 18 GHz for SiC\_A GFET: a) in magnitude; b) in phase. Bias conditions:  $V_{DS}$ =1.5V,  $V_{GS}$ =0.2-1V (step=0.2V)

Fig. 9. Synthesized impedances for source-pull measurements at 15 GHz for a) CVD2 and b) SiC\_A GFETs.  $\Gamma_S$  is increased from 0 to 0.7 and then for a fixed magnitude the phase is increased from 0° to 30°.

The measurement frequency was fixed to 15 GHz, reasonably far from the source-pull tuner calibration frequency limit at 18 GHz. Moreover, when increasing the magnitude of  $\Gamma_S$ , the upper limit was fixed to  $|\Gamma_S|$ =0.7. Indeed, above 0.7 and close to 18 GHz, the source-pull tuner shows more and more insertion loss, which strongly affects the sensitivity of the noise figure meter and consequently degrades the noise figure measurement accuracy.

In order to reproduce the source-pull setup measurements, the  $F_{50}$  noise model was simulated using the measured source impedances as Port-1 terminal impedance. The comparison between the simulated and measured noise figure and

associated gain, when sweeping  $\Gamma_S$  magnitude and phase, is respectively shown in Fig. 10 and 11. The agreement between noise measurement and simulation is satisfying, especially for this delicate type of measurement. On noise figures, we observed a 0.3 dB mean error (2%) with magnitude sweep and 1.4 dB mean error (9%) with phase sweep. The measurement and simulation of the associated gain are quasi-superimposed, proving the accurate modelling of the S-parameters. This agreement between the simulated  $F_{50}$  data and the source-pull noise measurements at 15 GHz indicates that the  $F_{50}$  method can be applied to extract the HF noise parameters of graphene transistors.

#### C. Noise parameters extraction up to 18 GHz

The two-port noise figure as function of the source impedance is expressed by equation (3):

$$F(\Gamma_S) = F_{min} + \frac{4R_n}{Z_0} \times \frac{|\Gamma_{opt} - \Gamma_S|^2}{|1 + \Gamma_{opt}|^2 \times (1 - |\Gamma_S|^2)}$$

(3) where  $F_{min}$ ,  $R_n$  and  $\Gamma_{opt}$  represents the noise parameters as

defined in [22].

The noise and small-signal modelling procedure was applied to the five transistors whose  $f_T/f_{max}$  are presented in Table 1. The noise parameters of each transistor were simulated from the corresponding F<sub>50</sub> noise model using Keysight® ADS RF simulator. The validity of the noise parameters extraction was verified by computing the Lange noise parameter, N [20]. Considering all the transistors, quantity  $4NT_0/T_{min}$  stands between 1 and 2 for the entire frequency range from 2 to 18

Fig. 10. Noise figures at 15 GHz versus  $|\Gamma_S|$  for CVD2 GFET: a) DOE with  $\Gamma_S$  magnitude increase; b) measured and simulated noise figure and associated gain according to DOE-a; c) DOE with  $\Gamma_S$  phase increase at  $|\Gamma_S|=0.5$ ; d) measured and simulated noise figure and associated gain according to DOE-c.

Fig. 11. Noise figures at 15 GHz versus  $|\Gamma_S|$  for SiC\_A GFET: a) DOE with  $\Gamma_S$  magnitude increase; b) measured and simulated noise figure and associated gain according to DOE-a; c) DOE with  $\Gamma_S$  phase increase at  $|\Gamma_S|$ =0.5; d) measured and simulated noise figure and associated gain according to DOE-c.

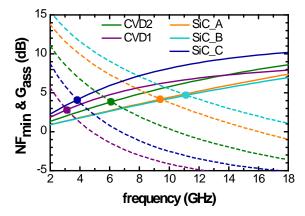

GHz. This validated the physical aspect of the extracted noise parameters. The minimum noise figures and associated gains for all characterized transistors are depicted in Fig. 12. The intersection point between  $NF_{min}$  and  $G_{ass}$  marks the upper frequency limitation for low noise amplifier design consideration using each device. Then, last generations of GFETs on SiC (SiC\_A and SiC\_B) show higher gain and lower noise than CVD GFETs and seem to be more suitable for RF design above 9 GHz. The main challenge lies in the matching solution, since the optimum source reflection coefficient is located at the border of the Smith Chart for these transistors.

Fig. 12. Extraction of the GFETs minimum noise figure (straight line) and associated gain (dashed line) using the noise model from 2 to 18 GHz

#### D. Noise parameters correlation with model parameters

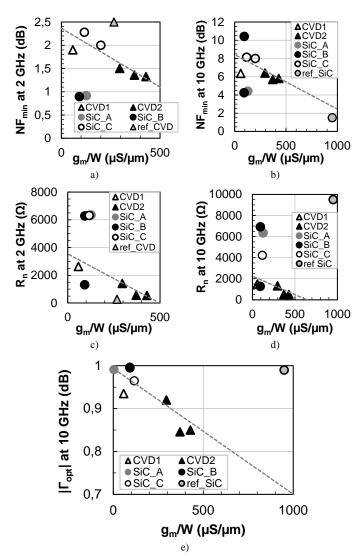

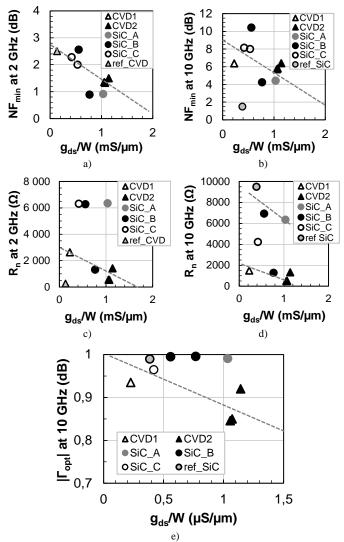

In order to quantify the impact of the small-signal model parameters on the noise performances, the correlation between the transconductance and the output conductance and the four noise parameters was studied. To equally compare the five types of GFETs,  $g_m$  and  $g_{ds}$  was normalized by the gate width, as shown in Fig. 13 and 14.  $NF_{min}$  and  $R_n$  are plotted at both 2 and 10 GHz to allow comparison with the state-of-the-art CVD GFET at 2 GHz [9] (ref CVD) and SiC GFET at 10 GHz [12] (ref\_SiC). As expected [20], NF<sub>min</sub> shows a linear evolution with respect of  $g_m/W$  for most of transistors, especially CVD GFETs. However, increasing simultaneously  $g_m$  and  $g_{ds}$  for both types of GFETs allows a reduction of the transistor's noise but it has also a positive impact on  $R_n$  and  $|\Gamma_{opt}|$ . In fact, from transistor technology's point of view, decreasing  $R_n$  is of utmost importance to minimize the sensitivity to noise mismatch and reducing  $|\Gamma_{opt}|$  offers realistic matching conditions, possibly using small passive devices.

Fig. 13. Noise parameters versus transconductance normalized by gate width. The dashed lines only provide a visual guide (not a fit to the experimental data).

Fig. 14. Noise parameters versus output conductance normalized by gate width. The dashed lines are only a guide to the eye (not a fit to the experimental data).

#### IV. CONCLUSION

The high frequency noise and small-signal characterization and modelling of CVD graphene grown GFETs and SiC GFETs up to 18 GHz was presented. Based on the F50 method, the noise parameter extraction was completed using a noise model that was validated by additional and selective source-pull measurements. This work shows that, combined with Sparameter measurements, simple noise figure measurements under 50  $\Omega$  are sufficient to build an accurate noise model in order to estimate the high frequency noise performance of a FET technology. For the first time, this safe, time-efficient and methodology cost-effective was validated by characterization of GFETs fabricated using different process and graphene materials. This suggests its possible extension for high frequency noise characterization of other emerging transistors technology based on low dimensional materials. Furthermore, its application to several GFETs has clearly shown that  $g_m$  and  $g_{ds}$  are key parameters to improve  $f_T$  and  $f_{max}$ , but also the noise parameters such as  $NF_{min}$ ,  $R_n$  or  $\Gamma_{opt}$  of the graphene transistors.

#### REFERENCES

- [1] O. Habibpour, Z. S. He, W. Strupinski, N. Rorsman, T. Ciuk, P. Ciepielewski, H. Zirath, "A W-band MMIC Resistive Mixer Based on Epitaxial Graphene FET," *IEEE Microw. Wireless Compon. Lett.*, vol. 27, no. 2, pp. 168–170, Feb. 2017.

- [2] H. M. D. Kabir and S. M. Salahuddin, "A frequency multiplier using three ambipolar graphene transistors," *Microelectron. J.*, vol. 70, pp. 12–15, Dec. 2017.

- [3] A. Hamed, O. Habibpour, M. Saeed, H. Zirath, and R. Negra, "W-Band Graphene-Based Six-Port Receiver," *IEEE Microw. and Compon. Lett.*, vol. 28, no. 4, pp. 347–349, Apr. 2018.

- [4] C. Yu, Z. Z. He, Q. B. Liu, X. B. Song, P. Xu, T. T. Han, J. Li, Z. H. Feng, S. J. Cai, "Graphene Amplifier MMIC on SiC Substrate," IEEE Electron Device Lett., vol. 37, no. 5, pp. 684–687, May 2016.

- [5] A. A. Generalov, M. A. Andersson, X. Yang, A. Vorobiev, and J. Stake, "A 400-GHz Graphene FET Detector," *IEEE Trans. THz Sci. and Technol.*, vol. 7, no. 5, pp. 614–616, Sep. 2017.

- [6] S. Fukushima, M. Shimatani, S. Okuda, S. Ogawa, Y. Kanai, T. Ono, and K. Matsumoto, "High responsivity middle-wavelength infrared graphene photodetectors using photo-gating," *Appl. Phys. Lett.*, 113, 061102, Aug. 2018.

- [7] T. Zimmer and S. Fregonese, "Graphene Transistor-Based Active Balun Architectures," *IEEE Trans. Electron Devices*, vol. 62, no. 9, pp. 3079–3083, Sep. 2015.

- [8] D. Mele, S. Fregonese, S. Lepilliet, E. Pichonat, G. Dambrine, and H. Happy, "High frequency noise characterisation of graphene FET device," in *IEEE MTT-S Int. Microw. Symp. Dig.*, 2013, pp. 1–4.

- [9] M. Tanzid, M. A. Andersson, J. Sun, and J. Stake, "Microwave noise characterization of graphene field effect transistors," *Appl. Phys. Lett.*, 104, 013502, Jan. 2014.

- [10] S. Fregonese, M. de Matos, D. Mele, C. Maneux, H. Happy, and T. Zimmer, "Source-Pull and Load-Pull Characterization of Graphene FET," *IEEE J. Electron Devices Soc.*, vol. 3, no. 1, pp. 49–53, Jan. 2015.

- [11] W. Wei, D. Fadil, E. Pallecchi, G. Dambrine, M. Deng, S. Fregonese, T. Zimmer, "High frequency and noise performance of GFETs," in *Proc. Int. Conf. Noise Fluctuations (ICNF)*, 2017, pp. 1–5.

- [12] C. Yu, Z. Z. He, X. B. Song, Q. B. Liu, S. B. Dun, T. T. Han, J. J. Wang, C. J. Zhou, J. C. Guo, Y. J. Lv, S. J. Cai, Z. H. Feng, "High-frequency noise characterization of graphene field effect transistors on SiC substrates," *Appl. Phys. Lett.* 111, 033502, Jul. 2017.

- [13] D. Fadil, W. Wei, M. Deng, S. Fregonese, W. Strupinski, E. Pallecchi, and H. Happy, "2D-Graphene Epitaxy on SiC for RF Application: Fabrication, Electrical Characterization and Noise Performance," in *IEEE MTT-S Int. Microw. Symp. Dig.*, 2018, pp. 228–231.

- [14] E. Pallecchi, H. Happy, W. Wei, M. Deng, S. Fregonese, D. Fadil, D. Zhou, S. Ben Salk, W. Strupinski, "Graphene Field Effect Transistors for High Frequency applications", Proc. IEEE MTT-S Int. Microw. Workshop Adv. Mater. Processes RF THz Appl., July 2019.

- [15] C. Gardès, S. Bagumako, L. Desplanque, N. Wichmann, S. Bollaert, F. Danneville, X. Wallart and Y. Roelens, "100 nm AlSb/InAs HEMT for Ultra-Low-Power Consumption, Low-Noise Applications," *The Scientific World Journal*, vol. 2014, Article ID 136340, 6 pages, 2014.

- [16] F. Danneville L. Poulain, Y. Tagro, S. Lépilliet, B. Dormieu, D. Gloria, P. Scheer, G. Dambrine, "RF and broadband noise investigation in High-k/Metal Gate 28-nm CMOS bulk transistor," *Int. J. Numer. Model.*, vol. 27, no. 5–6, pp. 736–747, 2014.

- [17] G. Dambrine, H. Happy, F. Danneville, and A. Cappy, "A new method for on wafer noise measurement," *IEEE Trans. Microw. Theory Techn.*, vol. 41, no. 3, pp. 375–381, Mar. 1993.

- [18] J. D. Buron, F. Pizzocchero, P. U. Jepsen, D. H. Petersen, J. M. Caridad, B. S. Jessen, T. J. Booth, and P. Bøggild, "Graphene mobility mapping," Sci. Rep., vol. 5, no. 1, Jul. 2015.

- [19] W. Wei, D. D. Fazio, U. Sassi, A. C. Ferrari, E. Pallecchi, H. Happy, "Graphene Field Effect Transistors with optimized Contact Resistance for Current Gain", *Proc. 75th Annu. Device Res. Conf. (DRC)*, South Bend, IN, USA, 25-28 June 2017

- [20] M. W. Pospieszalski, "Interpreting Transistor Noise," *IEEE Microw. Mag.*, vol. 11, no. 6, pp. 61–69, Oct. 2010.

- [21] G. Dambrine, J. P. Raskin, F. Danneville, D. V. Janvier, J. P. Colinge, and A. Cappy, "High-frequency four noise parameters of silicon-oninsulator-based technology MOSFET for the design of low-noise RF

- integrated circuits," *IEEE Trans. Electron Devices*, vol. 46, no. 8, pp. 1733–1741, Aug. 1999.

- [22] S. A. Maas, "Noise in Linear and Nonlinear Circuits", Artech House, 2005.

Marina Deng received the Ph.D. degree in electronics from the University of Lille, Villeneuve-d'Ascq, France, in 2014. During her Ph.D. research with IEMN, she worked on SiGe HBT small-signal and high-frequency noise

characterization and modeling in the sub-THz range. Since November 2015, she has been an Associate Professor with the University of Bordeaux, Talence, France, within the MODEL team. Her current research focuses on millimeter-wave and sub-millimeter-wave characterization of HF transistors, including on-wafer calibration and HF noise measurements.

**Dalal Fadil** received her PhD in Electronics, Microelectronics and Nanoelectronics Engineering in 2011 from University of Caen, France. She worked as postdoctoral research scientist with Carbon group in the IEMN laboratory in 2016 on fabrication and characterization of high frequency transistors based 2D materials, including graphene field effect transistor.

Wei Wei received the master's degree in materials science and engineering from Hunan University, Changsha, China, in 2011 and the Ph.D. degree in passive and active flexible electronics from University of Lille, Villeneuve-d'Ascq, France, in 2016. He is currently a postdoctoral research scientist in IEMN, working on process technologies for graphene-based high frequency electronics.

Emiliano Pallecchi received the Ph.D. degree in physics from the University of Regensburg, Regensburg, Germany, in 2008. He is currently an Associate Professor with the Carbon Group, Institute of Electronics, Microelectronics and Nanotechnology, Lille 1 University, Villeneuve-d'Ascq, France.

Henri Happy received the Ph.D. degree in electrical engineering from the University of Lille 1, Villeneuve d'Ascq, France, in 1992. He joined the Institute of Electronics, Microelectronics and Nanotechnology, Villeneuve d'Ascq, in 1988, where he is currently a Full Professor with the University Lille 1. Since 2004, he has been focusing on carbon nanodevices (carbon nanotube, graphene). These activities concern understanding of fundamental limitations and improvement of high frequency performance of carbon devices, and

their applications in emerging fields of RF circuits on flexible substrates. This includes graphene growth either on SiC and metal substrate, fabrication and characterization of graphene FET.

Gilles Dambrine received the engineer diploma, the Ph.D. degree and the Habilitation à Diriger des Recherches (HDR) degree from the University of Lille, France in 1986, 1989 and 1996 respectively. He was permanent researcher at the CNRS between 1989 and 1999. He is full Professor of Electronic at the University of Lille since 1999. His main research interests are concerned with the characterization and modelling of ultimate low-noise devices for application in millimeter and sub-millimeter wave ranges. Over these few years, his research interests are

oriented to the study of the microwave properties and applications of nanodevices. He is author and co-author of 140 papers and communications and 6 chapters of books, in the field of microwave devices. From 2010-2020, he was deputy director of the Institute of Electronics, Microelectronics and Nanotechnologies - IEMN gathering about 500 researchers and PhD students. from 2017 - 2020, he is scientific delegate in charge of industrial partnership and innovation at CNRS headquarter. He received the IEEE Fellow grade in 2016. Since 2018, he is member of EuMA BoD.

Magali De Matos received the M.S. degree in microelectronics from the University of Bordeaux, France in 1999. She then joined the Laboratory of Integration from Materials to Systems, IC Design Team, IMS, University of Bordeaux, as a Research Engineer. Since 2007, she has been in charge of the characterization platform NANOCOM at IMS, providing support to Ph.D. students working in the domains of IC design and compact modeling of devices. She is involved in sub-THz S-parameter

characterization with the Nanoelectronics Group.

Thomas Zimmer received the M.Sc. degree in physics from the University of Würzburg, Germany, in 1989 and the Ph.D. degree in electronics from the University Bordeaux 1, Talence, France, in 1992. From 1989 to 1990, he was with the Fraunhofer Institute, Erlangen, Germany. Since 1992, he is with the IMS Institute, Talence, France. Since 2003, he is Full Professor at the University Bordeaux.

His research interests are focused on electrical compact modeling and characterization of HF devices such as HBT (SiGe, InP), graphene nanotubes and

graphene transistors. He was a cofounder of the company XMOD Technologies and is Senior Member IEEE. He has served as a Reviewer for many journals (IEEE ED, EDL, SSE...), was the TPC (Technical Program Chair) of the ESSDERC 2012 conference and participated on the Program Committee of several conferences (BCTM, ESSDERC, EuMW, ...). He has authored or coauthored more than 250 peer-reviewed scientific articles, two books and contributed to 8 book-chapters. He currently holds four patents. In 2018, he received the Jan Van Vessem Award from the IEEE International Solid-State Circuit Conference.

Sébastien Fregonese was born in Bordeaux, France, in 1979. He received the M.Sc. and Ph.D. degrees in electronics from Université Bordeaux, Bordeaux, France, in 2002 and 2005, respectively. During his Ph.D. research, he investigated SiGe heterojunction bipolar transistor (HBTs), with emphasis on compact modeling. From 2005 to 2006, he was a Post-Doctoral Researcher with TU Delft, Delft, The Netherlands, where his research activities dealt with the Si strain FET emerging devices, focusing on process and

device simulation. In 2007, he joined CNRS, IMS, Bordeaux, as a Researcher. From 2011 to 2012, he was a Visiting Researcher with the University of Lille, France, focusing on the graphene FET device modeling. He is involved in a couple of National and European research projects such as the European FP7 IP Dot5, Dot7, FET GRADE, and H2020 TARANTO. His current research interests include electrical compact modeling and characterization of HF devices such as SiGe HBTs and carbon-based transistors.