## Coulomb blockade in monolithic and monocrystalline Al-Ge-Al nanowire heterostructures

M. Sistani, J. Delaforce, K. Bharadwaj, M. Luong, J. Nacenta Mendivil, Nicolas Roch, M. den Hertog, R. B. G. Kramer, Olivier Buisson, A. Lugstein, et al.

### ▶ To cite this version:

M. Sistani, J. Delaforce, K. Bharadwaj, M. Luong, J. Nacenta Mendivil, et al.. Coulomb blockade in monolithic and monocrystalline Al-Ge-Al nanowire heterostructures. Applied Physics Letters, 2020, 116 (1), pp.013105. 10.1063/1.5126088. hal-02524097

HAL Id: hal-02524097

https://hal.science/hal-02524097

Submitted on 2 Apr 2020

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Coulomb blockade in monolithic and monocrystalline Al-Ge-Al nanowire heterostructures

M. Sistani and A. Lugstein

Institute of Solid State Electronics, Technische Universität Wien, Gußhausstrahausstraße 25-25a, 1040 Vienna, Austria

J. Delaforce, K. Bharadwaj, M. Luong, J. Nacenta Mendivil, N. Roch, M. den Hertog, R.B.G. Kramer, O. Buisson, and C. Naud\*

Institut NEEL CNRS/UGA UPR2940, 25 avenue des Martyrs, 38042 Grenoble, France

(Dated: March 29, 2020)

#### **Abstract**

This document is the unedited Author's version of a Submitted Work after peer review that was subsequently accepted for publication in Applied Physics Letters 116, 013105 (2020). To access the final edited and published work see [https://doi.org/10.1063/1.5126088].

We report the realization of Ge single-hole transistors based on Al-Ge-Al nanowire (NW) heterostructures. The formation of this axial structure is enabled by a thermal induced exchange reaction at 350°C between the initial Ge NW and Al contact pads, leading to a monolithic and monocrystalline Al-Ge-Al NW. The 25nm-diameter Ge segment is a quasi-1D hole channel. Its length is defined by two abrupt Al-Ge Schottky tunnel barriers. At low temperatures the device shows a single hole transistor signature with well pronounced Coulomb oscillations. The barrier strength between the Ge segment and the Al leads can be tuned as function of the gate voltage  $V_G$ . It leads to a zero conductance at  $V_G$ = 0V to a few quantum conductance at  $V_G$ = -15V. When the gate voltage increases from -5V to -3V, the charging energy is extracted and it varies from 0.39 meV to 2.42 meV.

<sup>\*</sup> cecile.naud@neel.cnrs.fr

Motivated by the ability to monitor and manipulate the motion of an individual charge carrier [1, 2], substantial effort has been devoted to the fabrication of single electron transistors (SETs) and quantum dots. They consist of a small gate dependent island isolated from two charge reservoirs by two tunnel junctions. A gate electrode is used to shift the Fermi level of the island to control the flow of single charge carriers to and from the reservoirs. The ability to control the flow of single charge carriers makes these devices promising candidates for highly sensitive charge detectors, nanoelectronics featuring low power dissipation, single-electron turnstile devices and charge or spin quantum bit[3].

The accessibility of such quantum devices are limited by their low working temperature, the maximum temperature at which the single charge carrier state can be reached. The working temperature is dependent on the charging energy  $(E_C)$ , the energy required to introduce a single charge carrier to the island.  $E_C$  is inversely proportional to the total capacitance  $(C_T)$  of the system; a sum of the capacitance of the tunnel junctions between the reservoirs and the island and the capacitance between the gate electrode and the island. Therefore, fabricating reproducible nano-devices with small capacitances, especially those of the tunnel junctions, is a critical milestone for the development in nanoelectronics.

In pursuit of such a milestone, multiple processes have been developed: A lift-off process can be employed to obtain a SET device onto a planar substrate[4]. The dimensions of these devices, thus the resulting capacitances, are limited by the resolution of the lithography. On another hand, one can take advantage of semiconducting nanowires (NWs) or carbon nanotubes to define the island. With this bottom-up approach, the capacitance of the tunnel junctions are directly correlated to the way the connection between the reservoir and nanowire is realized. For example, forming a nanosize gap between the two electrodes by electromigration allows one to connect a molecular system with a quasi-atomic contact [5]. However, such a process is difficult to implement.

Alternative bottom-up fabricated nanostructures emerged as promising systems predicted to overcome the limitations of planar architectures [6]. Among them, considerable effort has been devoted to fabricate quasi-1D nanostructures such as vapor-liquid-solid (VLS) [7] grown nanowires enabling the customization of morphology, geometry, composition or crystal orientation. Recently, band-structure engineering by controlled epitaxial growth of core-shell NWs provoked the investigation of one-dimensional hole-gas systems [8], attractive for both fundamental studies and future nanoelectronics [9]. Despite the vast body of pioneering experimental work on GeSi [10] and Ge-Si core-shell structures [11, 12] the investigation of Coulomb blockade effects in pure Ge

based nanostructures is still evasive. This is mainly associated to limitations in fabricating reliable contacts to Ge nanostructures [13]. To improve the metal contact with Ge heterostructures significant research has been carried out on the formation of germanide contacts through the thermal diffusion of metals into Ge NWs[14, 15]. However, the resistivity of these quasi-metallic structures is still significantly higher compared to pure metals [16]. Hence, material combinations with no intermetallic phase formation, such as our Al-Ge system, enabling true metal-semiconductor heterostructures with abrupt interfaces received a considerable amount of attention [17]. The realisation of a true metal-semiconductor interface provides a controllable mechanism to fabricate reproducible and effective nanoelectronic devices.

In this work, we investigate the low temperature transport properties of Al-Ge heterostructure nanowires. We report the observation of Coulomb blockade up to 10K in such hybrid quantum devices with a Ge segment length ( $L_{Ge}$ ) of 162 nm and a diameter of 25nm. Modelling the system as a quantum dot isolated by the two Al/Ge Schottky tunnel barriers, we detail the characteristic parameters of this system. In particular, we show that the transparency of the tunnel junctions are gate tuneable.

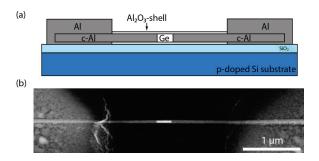

The Ge NWs used for the experiments were grown on Si <100> substrates using the VLS process with germane ( $GeH_4$ , 2% diluted in He) as precursor and a 2 nm thick sputtered Au layer as the 1D growth promoting catalyst. The actual growth was performed using a low pressure hot wall CVD chamber at 50 mbar and a gas flow of 100 sccm for both, the precursor gas and  $H_2$  as carrier gas. The temperature was ramped up at a rate of  $60^{\circ}$ C/min to the target temperature of 340°C. The rather high growth temperature ensures uniform catalyst diameter and good NW epitaxy. After a 10 min nucleation phase, the temperature is lowered to 300°C. Typical growth duration of 60 min result in 8  $\mu$ m long NWs and uniform diameters of about 25 nm. Subsequently to the growth, the NWs were uniformly coated with 20 nm  $Al_2O_3$  by atomic layer deposition. For device fabrication, the Ge NWs were drop casted onto an oxidized highly p-doped Si substrate. Al contacts to the Ge NWs were fabricated by electron-beam lithography, sputter deposition, and lift-off techniques. The subsequent thermally induced exchange reaction was achieved by rapid thermal annealing at a temperature of T = 350°C in a forming gas atmosphere. This initiates the substitution of the Ge core by c-Al[17]. Consecutive annealing cycles have been used to tune the Ge segment length  $L_{Ge}$ .

Applying this process enables the reliable fabrication of monolithic axial Al-Ge-Al nanowire heterostructures with tunable Ge segments contacted by self-aligned monocrystalline Al leads.

FIG. 1. (a) Schematic illustration of the passivated NW heterostructure comprising one-dimensional selfaligned c-Al leads contacting a Ge segment. (b) HAADF STEM image showing an actual Al-Ge-Al NW heterostructure device with  $L_{Ge} = 200$  nm.

The nanowire is integrated in a back-gated field effect transistor architecture (Figure 1a). A High Angle Annular Dark field Scanning Transmission Electron Microscopy (HAADF STEM) image showing the actual Al-Ge-Al nanowire heterostructure is shown in Figure 1b. This image has been obtained on a probe corrected Titan Themis working at 200 kV. For STEM observations, devices were fabricated on electron transparent  $Si_3N_4$  membranes, as described in ref[18].

Independent of metal type and doping concentrations metal-germanium junctions form Schottky contacts exhibiting very strong Fermi-level pinning close to the valence band.[19, 20] In analogy to high electric fields across the nanowire, Fermi level pinning results in significant band bending[21]. According to simulations of the field distribution in Ge nanowires by Lee et al[22], the importance of this effect is significantly enhanced for thin nanowires, where the depletion regions approach each other. Assuming thermionic emission, the room temperature Schottky barrier height of the Al-Ge interface was experimentally determined to be 361 meV[17]. Although nominally undoped Ge nanowires were used for device fabrication, negative surface charges accumulating in interband trap levels[21] lead to an overall p-type behavior of the devices. By applying a gate voltage, the Fermi level of the Ge NW can be effectively shifted, modulating the charge carrier concentration and therefore the conductivity in the channel.

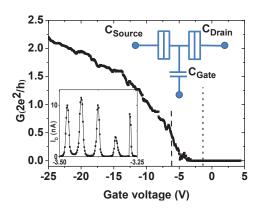

The low temperature transport properties of the nanowire heterostructures were investigated in a home-made pumped He<sup>3</sup> cryostat. Using a two probe configuration the current ( $I_D$ ) was measured as a function of the back-gate voltage ( $V_G$ )) and source drain bias voltage ( $V_D$ ). We have measured several heterostructures with germanium lengths ( $L_{Ge}$ ) ranging from 100 nm to 800 nm with diameters of 25 nm. For all measured devices, we observed the same global behavior. Figure 2 shows the field effect induced by the gate voltage for a device with  $L_{Ge} = 162$  nm for a

bias voltage of 1 mV at T = 350 mK. The conductance was directly obtained from the measured current according to G =  $I_D/V_D$  and is plotted in units of  $G_0 = \frac{2e^2}{h}$ . The pinch-off gate voltage of the heterostructure device is approximately  $V_G$ =-1.5 V. For gate voltages between  $V_G$  = +5 V and -1.5 V, we observe a conductance below  $10^{-5}G_0$ . As the gate voltage becomes more negative, oscillations appear in the conductance. To illustrate this regime, we plot the current  $I_D$  versus the gate voltage in the inset of the figure 2. We clearly see periodic peaks of current. These peaks are separated by regions of very low current. These oscillations are resulting from the Coulomb blockade phenomenon. With a further decrease of the gate voltage, the conductance of the overall system rises and the conductance oscillations disappear. It can be explained by a reduction of the width of the tunnel barrier of the Al-Ge junction, leading to an increase of the junction transparency. Considering that Ge nanowires with diameters of 25 nm are close to the Bohr radius of Ge[23], quantum confinement should result in a band structure being composed of multiple 1D sub-bands. Assuming a square-well confining potential[24], the number of possible conductance channels should be limited to four [25]. However, the conductance of the device is saturating below this value at about 2.5 G<sub>0</sub>. This limited conductance could be explained by the limited transparency of the conducting channels or by a contact resistance.

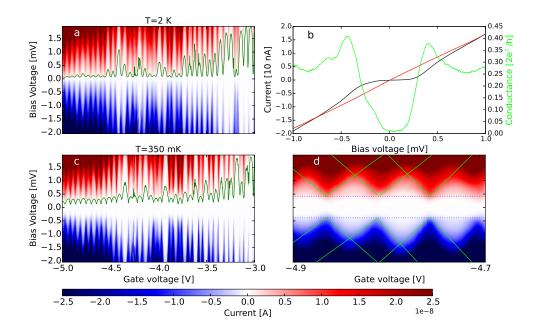

Figure 3 (a), (c) and (d) shows the color scale representation of the current  $(I_D)$  as function

FIG. 2. Conductance plotted in units of quantum conductance  $G_0$  as a function of gate voltage of an heterostructure with  $L_{Ge} = 162$  nm for a bias voltage of 1 mV recorded at T = 350 mK. Lines are used to show the different regimes of transport. Dotted line indicates the pinch-off gate voltage. The diagram shows a single hole transistor: an island related via two tunnel junctions to two reservoirs and capacitively coupled to a gate. Inset: current versus the gate voltage between -3.25 V and -3.5V for  $V_D = 0.5$  mV.

of the back-gate voltage ( $V_G$ ) and the applied source-drain voltage ( $V_D$ ) at T = 350 mK and 2K. The gate voltage window has been selected in the intermediate regime for which quantum transport phenomena is well observed. Zero current, therefore zero conductance, is represented by white regions in the 2D plots. Clear diamond like shapes at the boundary between zero and non-zero current can be observed. Such features, characteristic of Coulomb blockade, are called Coulomb diamonds[10, 26, 27]. The diamonds do not close at zero bias voltage. Figure 3 b shows the  $I_D$ - $V_D$  characteristic curves at 350 mK and 2K at a charge degeneracy point. The differential conductance calculated from the current is also plotted. At 350 mK, well below the critical temperature of Aluminium  $T_C^{AL}$ = 1.46 K[28], the  $I_D$ - $V_D$  curve presents a suppression of the current for small bias voltages and this zero current feature disappears at 2K. In conductance, this feature translates to a region of low conductance bounded by two peaks. This behavior can be explained by the suppression of quasi-particles through the NW for  $IV_DIe < 2 \Delta_{AI}$  due to the gap of the superconducting Al leads [10, 29]. From the separation between the two peaks, therefore 4  $\Delta_{AI}$ , we extract  $\Delta_{AI} = 202 \ \mu eV$ , which is consistent with the aluminum energy gap.

Figure 3 (c) reveals rich transport properties within the clear Coulomb diamond structure. For  $-5V < V_G < -4.5V$ , the height and periodicity of the diamonds is almost constant. As  $V_G$  is increased periodic fluctuations of the magnitude of the peaks of the diamonds appear. When  $-4 \ V < V_G < -3.4 \ V$ , we observe diamond pairing where the addition of a hole from a 2N state to a 2N+1 state requires additional charging energy. When  $-4.5 \ V < V_G < -4 \ V$ , we observe a second periodicity with higher diamond peaks at the 4N and 4N + 1 hole filling point. Further, a global decay of the Coulomb diamond height is observed as the  $V_G$  is decreased from  $-3.0 \ V$  to  $-4.5 \ V$ . In order to better visualize the variation of the transport, we have superimposed iso-current curves on the stability diagrams of Figure 3. These curves trace the variation of the bias voltage versus the gate voltage in order to keep the current through the dot at a constant of 0.5 nA. We clearly observe oscillations of the bias voltage versus the gate voltage with periodicity equal to that of the observed Coulomb diamonds and amplitude proportional to the charging energy of the system. The iso-current curves agree with the observations of stability diagram: an overall decay of the amplitude of the oscillations is combined with a periodic modulation of their amplitude as the gate voltage decreases.

As a first approximation, we consider the Al-Ge-Al nanowire heterostructure as a single hole transistor, equivalent to an SET, (see diagram of Figure 2). The Ge segment is then described by a metallic island connected via two tunnel junctions to two reservoirs (Al leads). The periodicity of the diamonds and the slopes of their edges are related to the three capacitances of the SET[25].

FIG. 3. (a) and (c) 2D plots showing the measured current versus the bias voltage and the gate voltage of a device with  $L_{Ge} = 162$  nm recorded at T = 350 mK and 2K. Green lines indicates iso-current curves of 0.5 nA through the nanowire. (b) Slice of the 2D plots at  $V_G = -4.866$  V at T = 350 mK (black curve) and T = 2K (red curve). The calculated differential conductance of the black curve has been superimposed (green curve)(d) Zoom onto few diamonds in order to visualize the gap. Superimposed to the 2D plot, we have added the slopes used to estimate the capacitances.

From the periodicity of the diamonds as function of the gate voltage, we extract the gate capacitance:  $C_{Gate} = 3 \times 10^{-18}$  F. The slopes of the diamonds give the ratio of the source ( $C_{Source}$ ) and drain ( $C_{Drain}$ ) capacitances to the gate capacitance[30]. We extracted the slopes of the diamonds from the 2D plot. In the gate voltage regime of -5 V< $V_G$ <-4.5 V,  $C_{Source} \simeq C_{Drain} \simeq 100 \times 10^{-18}$  F are deduced. Figure 3 (d) shows a zoom onto the gate region -4.9V< $V_G$ <-4.7V in which we superimposed to the experimental data the extracted slopes.

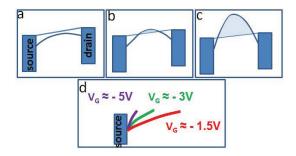

The global decay of the Coulomb diamonds suggests that there is a gate dependence on the charging energy of the quantum dot. Analysis of the slopes of the diamonds reveals that the source and drain capacitances increase from approximately  $15 \times 10^{-18}$  F to  $100 \times 10^{-18}$  F. Consequently, the charging energy  $E_C = \frac{e^2}{2(C_{Gate} + C_{Drain} + C_{Source})}$  decreases from 2.42 meV to 0.39 meV. Figure 4 is a schematic representation of the band structure of these heterostructures that we propose to explain the global decay of the charging energy. For -1.5 V <  $V_G$  < +5 V, the Ge segment is depleted of

FIG. 4. Schematics of the band diagram of the heterostructure (a) in the insulator regime, (b) in the intermediate regime and (c) in the metallic like dot regime. A positive bias voltage is applied. (d) A Zoom onto the Al-Ge contact is presented in order to show the Fermi level pinning and the variation of the Schottky tunnel barrier strength versus the gate voltage.

holes and consequently we are in an insulating regime, thus we observe a current close to zero (see Figure 4a). By reducing  $V_G$  ( $V_G < -1.5$  V), the valence band is shifted above the Fermi level facilitating hole tunneling into the dot. However, Fermi level pinning fixes the valence band to below the Fermi level of the electrodes resulting in a bow shaped valence band in the dot. This bowing creates a gate dependency on the size of the dot; as  $V_G$  is reduced, the valence band is shifted and becomes further bowed, increasing the area of the dot, thus increasing its capacitance and reducing its charging energy. This gives rise to the global decay of the Coulomb diamond height observed in Figure 3. For large negative gate voltage ( $V_G < -4.5$ V), the valence band is far above the Fermi level (see Figure 4 (c)). This increases the hole concentration in the Ge facilitating a large quantum dot insensitive to changes in size, leading to a metallic like island where we observe regular Coulomb diamonds.

There are many possible interpretations of the not monotonous fluctuations of the charging energy. These fluctuations could be due to scattering of the holes inside the dot [31]. Such scattering is common with lateral quantum dots, such as nanowire heterostructures, where interactions with the irregular boundaries of the dots results in chaotic transport. These disordered dots should reveal aperiodic fluctuations.

As depicted in Figure 4 (b), in the intermediate gate voltage regime, the valence band is close to the Fermi level in such a way that any accident in the valence band due to charge trapping or impurities could generate tunnel barriers which are equivalent to a chain of islands. The conductance from source to drain would occur by tunneling through this chain, resulting in varying diamond heights due to the addition of the charging energies related to each island[26].

The Coulomb diamond pairing as well as the four periodicity suggests an alternative phenomena is behind the fluctuations. As observed in high quality quantum dots experiences[32, 33], atomic like electron/hole filling of orbitals can be obtained. The observed pairing of diamonds could be attributed to the lifting of spin degeneracy due to Coulomb repulsion. In Ge, light-hole-heavy-hole (LH-HH) degeneracy is known to be lifted by confinement or strain [34, 35]. The lifting of the fourfold degeneracy, resulting from the combination of LH-HH and spin degeneracy [36], could explain the observed higher peaks at the 4N and 4N + 1 hole filling point. However, conclusion on an exact interpretation requires further investigation beyond the scope of this paper.

The temperature dependence is consistent with the charging energy we deduced from the stability diagram. The amplitude of the Coulomb oscillations at gate voltage around -5 V, is strongly reduced at 2 K and almost vanishing at 10 K (see supporting information). This is explained by the low charging energy  $E_C/k_B = 4.5K$ . Nevertheless, the Coulomb oscillations around  $V_G$  -3 V are reduced but still visible at 10 K. This persistence is consistent with the estimated charging energy for such gate voltage:  $E_C/k_B = 28K$ .

In conclusion, we have demonstrated the realization of monolithically integrated Ge channels contacted by monocrystalline quasi-1D Al contacts. The fabrication process used induces sharp interfaces between the semiconductor segment and superconducting leads. Based on these heterostructures, we have systematically investigated single-hole tunneling effects in Ge quantum dots defined by tunable Schottky barriers. We observe and discuss the multiple regimes in the hole transport: from a pinch off voltage of approximately  $V_G = -1.5$  V, the Ge segment behaves as a quantum dot with very rich properties. With a sufficiently negative gate voltage a metallic like SET is reached.

#### SUPPLEMENTARY MATERIAL

The supplementary material shows the 2D plot of the current versus the gate voltage and the bias voltage at 350mK, 2K, 5K and 10K.

#### **ACKNOWLEDGMENTS**

J. Delaforce acknowledges the European Union's Horizon 2020 research and innovation programme under the Marie Skłodowska-Curie grant agreement No 754303. M. Sistani and A. Lug-

stein acknowledge financial support by the Austrian Science Fund (FWF): project no: P29729-N27. They thank the Center for Micro- and Nanostructures, TU Wien for providing the cleanroom facilities. O. Buisson and C. Naud was supported by the ANR QPSNanowires (ANR-15-CE30-0021). M.A. Luong acknowledges support from the Laboratoire d'excellence LANEF in Grenoble (ANR-10-LABX-51-01). We benefited from the access to the technological platform NanoCarac of CEA-Minatech in collaboration with the LEMMA group, and Nanofab from institute NEEL.

[1] M. I. Lutwyche and Y. Wada, Journal of Applied Physics 75, 3654 (1994).

- [4] T. A. Fulton and G. J. Dolan, Phys. Rev. Lett. 59, 109 (1987).

- [5] H. Park, J. Park, A. K. L. Lim, E. H. Anderson, A. P. Alivisatos, and P. L. McEuen, Nature 407, 1476 (2000).

- [6] F. A. Zwanenburg, A. A. van Loon, G. A. Steele, C. E. W. M. van Rijmenam, T. Balder, Y. Fang, C. M. Lieber, and L. P. Kouwenhoven, Journal of Applied Physics 105, 124314 (2009), https://doi.org/10.1063/1.3155854.

- [7] R. S. Wagner and W. C. Ellis, Applied Physics Letters 4, 89 (1964), https://doi.org/10.1063/1.1753975.

- [8] W. Lu, J. Xiang, B. P. Timko, Y. Wu, and C. M. Lieber, Proceedings of the National Academy of Sciences **102**, 10046 (2005), https://www.pnas.org/content/102/29/10046.full.pdf.

- [9] S. K. Ray, A. K. Katiyar, and A. K. Raychaudhuri, Nanotechnology 28, 092001 (2017).

- [10] G. Katsaros, P. Spathis, M. Stoffel, F. Fournel, V. Mongillo, Bouchiat, F. Lefloch, A. Rastelli, O. G. Schmidt, and S. De Franceschi, Nature Nanotechnology 5, 458 (2010).

- [11] J. Xiang, A. Vidan, M. Tinkham, R. M. Westervelt, and C. M. Lieber, Nature Nanotechnology 1, 208 (2006).

- [12] S. Conesa-Boj, A. Li, S. Koelling, M. Brauns, J. Ridderbos, T. T. Nguyen, M. A. Verheijen, P. M. Koenraad, F. A. Zwanenburg, and E. P. A. M. Bakkers, Nano Letters 17, 2259 (2017), pMID: 28231017, https://doi.org/10.1021/acs.nanolett.6b04891.

- [13] N. Neophytou, Jing Guo, and M. S. Lundstrom, IEEE Transactions on Nanotechnology 5, 385 (2006).

- [14] Y. Wu, J. Xiang, C. Yang, W. Lu, and C. M. Lieber, Nature **430** (2004), 10.1038/nature02674.

<sup>[2]</sup> E. D. U. C. Devoret, Michel H., Nature **360**, 547 (1992).

<sup>[3]</sup> R. Hanson, L. P. Kouwenhoven, J. R. Petta, S. Tarucha, and L. M. K. Vandersypen, Rev. Mod. Phys. 79, 1217 (2007).

- [15] Y.-C. Chou, W.-W. Wu, S.-L. Cheng, B.-Y. Yoo, N. Myung, L. J. Chen, and K. N. Tu, Nano Letters 8, 2194 (2008), pMID: 18616326, https://doi.org/10.1021/nl080624j.

- [16] B. Liu, Y. Wang, S. Dilts, T. S. Mayer, and S. E. Mohney, Nano Letters 7, 818 (2007), pMID: 17295545, https://doi.org/10.1021/nl062393r.

- [17] S. Kral, C. Zeiner, M. Stöger-Pollach, E. Bertagnolli, M. I. den Hertog, M. Lopez-Haro, E. Robin, K. El Hajraoui, and A. Lugstein, Nano Letters 15, 4783 (2015), pMID: 26052733, https://doi.org/10.1021/acs.nanolett.5b01748.

- [18] K. El hajraoui, M. A. Luong, E. Robin, F. Brunbauer, C. Zeiner, A. Lugstein, P. Gentile, J.-L. RouviÃ"re, and M. Den Hertog, Nano Letters 19, 2897 (2019), pMID: 30908919, https://doi.org/10.1021/acs.nanolett.8b05171.

- [19] A. Thanailakis and D. Northrop, Solid-State Electronics 16, 1383 (1973).

- [20] A. Dimoulas, P. Tsipas, A. Sotiropoulos, and E. K. Evangelou, Applied Physics Letters **89**, 252110 (2006), https://doi.org/10.1063/1.2410241.

- [21] T. Hanrath and B. A. Korgel, The Journal of Physical Chemistry B **109**, 5518 (2005), pMID: 16851592, https://doi.org/10.1021/jp044491b.

- [22] C.-J. Kim, H.-S. Lee, Y.-J. Cho, K. Kang, and M.-H. Jo, Nano Letters **10**, 2043 (2010), pMID: 20420371, https://doi.org/10.1021/nl100136b.

- [23] Y. Wu and P. Yang, Chemistry of Materials 12, 605 (2000), https://doi.org/10.1021/cm9907514.

- [24] D. Ferry, S. Goodnick, and J. Bird, Transport in Nanostructures (Cambridge University Press, 2009).

- [25] S. Datta, *Electronic Transport in Mesoscopic Systems*, Cambridge Studies in Semiconductor Physics and Microelectronic Engineering (Cambridge University Press, 1995).

- [26] C. Thelander, T. Mårtensson, M. T. Björk, B. J. Ohlsson, M. W. Larsson, L. R. Wallenberg, and L. Samuelson, Applied Physics Letters 83, 2052 (2003), https://doi.org/10.1063/1.1606889.

- [27] D. Averin and K. K. Likharev, Journal of Low Temperature Physics 62, 345 (1986).

- [28] F. M. Brunbauer, E. Bertagnolli, J. Majer, and A. Lugstein, Nanotechnology 27, 385704 (2016).

- [29] M. Taupin, E. Mannila, P. Krogstrup, V. F. Maisi, H. Nguyen, S. M. Albrecht, J. Nygård, C. M. Marcus, and J. P. Pekola, Phys. Rev. Applied 6, 054017 (2016).

- [30] F. A. Zwanenburg, A. S. Dzurak, A. Morello, M. Y. Simmons, L. C. L. Hollenberg, G. Klimeck, S. Rogge, S. N. Coppersmith, and M. A. Eriksson, Rev. Mod. Phys. 85, 961 (2013).

- [31] Y. Alhassid, Reviews of Modern Physics 72, 895 (2000), arXiv: cond-mat/0102268.

- [32] S. Tarucha, D. G. Austing, T. Honda, R. v. d. Hage, and L. P. Kouwenhoven, Japanese Journal of Applied Physics **36**, 3917 (1997).

- [33] S. Moriyama, T. Fuse, M. Suzuki, Y. Aoyagi, and K. Ishibashi, Physical Review Letters **94** (2005), 10.1103/PhysRevLett.94.186806.

- [34] J. Wang, A. Rahman, G. Klimeck, and M. Lundstrom, in *IEEE InternationalElectron Devices Meeting*, 2005. *IEDM Technical Digest*. (2005) pp. 4 pp.–533, iSSN: 0163-1918, 2156-017X.

- [35] H. Watzinger, C. Kloeffel, L. Vukušić, M. D. Rossell, V. Sessi, J. Kukučka, R. Kirchschlager, E. Lausecker, A. Truhlar, M. Glaser, A. Rastelli, A. Fuhrer, D. Loss, and G. Katsaros, Nano Letters 16, 6879 (2016).

- [36] C. Kloeffel, M. Trif, and D. Loss, Physical Review B 84 (2011).