# Meet the Sherlock Holmes' of Side Channel Leakage: A Survey of Cache SCA Detection Techniques

Ayaz Akram, Maria Mushtaq, Muhammad Khurram Bhatti, Vianney Lapotre,

Guy Gogniat

# ► To cite this version:

Ayaz Akram, Maria Mushtaq, Muhammad Khurram Bhatti, Vianney Lapotre, Guy Gogniat. Meet the Sherlock Holmes' of Side Channel Leakage: A Survey of Cache SCA Detection Techniques. IEEE Access, 2020, 8, pp.70836-70860. 10.1109/ACCESS.2020.2980522 . hal-02508889

# HAL Id: hal-02508889 https://hal.science/hal-02508889v1

Submitted on 25 Nov 2021

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

Distributed under a Creative Commons Attribution 4.0 International License

Received January 20, 2020, accepted February 26, 2020, date of publication March 13, 2020, date of current version April 28, 2020. Digital Object Identifier 10.1109/ACCESS.2020.2980522

# Meet the Sherlock Holmes' of Side Channel Leakage: A Survey of Cache SCA Detection Techniques

# AYAZ AKRAM<sup>®</sup><sup>1</sup>, MARIA MUSHTAQ<sup>2</sup>, MUHAMMAD KHURRAM BHATTI<sup>®</sup><sup>3</sup>, VIANNEY LAPOTRE<sup>®</sup><sup>4</sup>, AND GUY GOGNIAT<sup>®</sup><sup>4</sup>

<sup>1</sup>Department of Computer Science, University of California, Davis, Davis, CA 95616, USA

<sup>2</sup>LIRMM, CNRS, Université de Montpellier, 34095 Montpellier, France

<sup>3</sup>Department of Electrical Engineering, Information Technology University, Lahore 54890, Pakistan

<sup>4</sup>Lab–STICC, University of South Brittany, 56100 Lorient, France

Corresponding author: Ayaz Akram (yazakram@ucdavis.edu)

This work was supported in part by the PHC PERIDOT Project e-health SECURE under Grant 3-6/HEC/R&D/PERIDOT/2017.

**ABSTRACT** Cache Side Channel Attacks (SCAs) have gained a lot of attention in the recent past. Since, these attacks exploit the caching hardware vulnerabilities, they are fast and dangerous. Detection of cache side channel attacks is an important step towards mitigating against such hostile entities. Researchers have already proposed different techniques to detect cache side channel attacks. This paper provides a detailed survey of literature related to the state-of-the-art detection techniques for cache based side channel attacks. We identify a set of important characteristics that can be used to characterize a CSCA (cache side channel attack) detection technique. We use the identified features to compare and contrast the most important detection techniques and provide the important observations. We also identify some of the challenges that the research community will have to resolve in future to improve the efficiency of cache side channel detection techniques. To the best of our knowledge, this is the first work to do such a study. We believe that this paper will prove useful to researchers in the area of systems security.

**INDEX TERMS** Cache-based side channel attacks (SCAs), cryptography, survey, detection, machine learning, anomaly & signature detection.

#### I. INTRODUCTION

Information security is becoming a major concern with each passing day as innovative and smart security attacks keep on appearing. With the emergence of new fields like IoT, Blockchain, Cloud-Computing and Cyber-Physical Systems (CPS), the amount of produced digital data has increased exponentially over the past few years. Roughly 2.5 quintillion bytes of data is produced each single day according to IBM Big Data Research. Since it is expensive to process such big amounts of data on end-user devices, any required processing on this data is usually done in centralized computing environments (i.e. Cloud Systems). Cloud Computing platforms have been continuously evolving with their increasing use. Current cloud computing facilities are provided in various forms like Software-as-a-Service (SaaS), Platform as-a-Service (PaaS), and Infrastructure-as-a-Service (IaaS) [1]. Such services extensively use virtualization technology to provide isolated

The associate editor coordinating the review of this manuscript and approving it for publication was Mohammad Ayoub Khan<sup>(1)</sup>.

processing capability to users without any interference. Multiple Virtual Machines (VMs) are executed on the shared hardware resources which create a possibility of security breaches. Malicious VMs that share hardware resources (co-reside) with other VMs (referred as victim VMs) can obtain their information [2]-[4] and perform Side Channel Attacks (SCAs) on victim VMs [5], [6]. Significant amount of research has been performed in the field of cryptography leading to the development of different crypto-algorithms like ECC, AES, RSA, and ElGamal etc. Theoretically, these algorithms are very hard to break and require enormous computing power. For instance, for a 128-bit AES key, it would take  $5.4 \times 10^{18}$  years to crack the AES using a computer capable of performing  $10^6$  decryption operations per  $\mu$ s [7]. However, many research works have shown that cryptosystems, such as AES, can be compromised due to the vulnerabilities of the hardware on which they run. Side Channel Attacks (SCAs) do not target the algorithm of crypto-systems itself. Rather, they target the underlying implementation of systems on which these crypto-systems execute [8] as shown

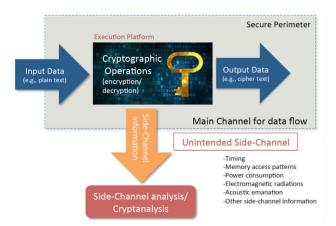

FIGURE 1. Unintended Side-Channel information leakage.

in Figure 1. SCAs can use a variety of physical parameters, e.g., power consumption [9], EM (electro-magnetic) radiation [10], memory accesses or fault occurrence [5], [11]–[18] to extract secret keys/information. The baseline idea here is that the SCAs can analyze the variations in the previously mentioned parameters during the execution of crypto-systems on a particular hardware and can determine the secret information used by crypto-systems based on the observed parameters.

In modern processors, memory is used in a hierarchy (registers, caches, main memory (RAM) and storage) to improve performance of running processes by exploitation of spatial and temporal locality found in the accessed data. The level closest to the processor, i.e., registers, is fastest to access but limited in number. The next level of hierarchy is composed of caches that are used to hold part of the main memory, which is to be accessed frequently. Modern Intel processors consist of hierarchical caches up to three different levels (i.e., L1, L2, and L3) that vary in their sizes and response times. Last level of cache (L3) is usually shared among multiple cores in modern Intel processors. Cache side channel attack (CSCA) is a special type of SCA in which a malicious process deduces secret information of a victim process by observing its use of caching hardware [19]. In this paper, we focus on Cache Side Channel Attacks (CSCAs) in Intel' x86 Architecture based processors. Different cache properties of Intel's Architecture like inclusivity and flushing have also been used as vulnerabilities [5], [14], [20]. Inclusivity ensures that the cache blocks or lines present in higher level of cache would also be present in lower level caches. Flushing (eviction of any cache line with a particular address in all levels of cache) has been made possible with the help of instructions like CLFLUSH in Intel's x86 Instruction Set Architecture (ISA). CSCAs on other architectures like ARM have also been shown to be practical [21]–[23].

*Contributions:* This paper presents a survey of techniques that have been proposed to detect cache based side channel attacks. We classify these techniques into different categories based on their design characteristics. We provide a comparison of these techniques using a broad set of parameters and

#### **TABLE 1.** List of acronyms.

| Name                         | Abbreviation |

|------------------------------|--------------|

| Side Channel Attack          | SCA          |

| Cache Side Channel Attack    | CSCA         |

| Evict and Time               | E+T          |

| Flush+Reload                 | F+R          |

| Flush+Flush                  | F+F          |

| Hardware Performance Counter | HPC          |

| Machine Learning             | ML           |

| Last Level Cache             | LLC          |

| Virtual Machine              | VM           |

| Attacker Address Space       | AAS          |

| Victim Address Space         | VAS          |

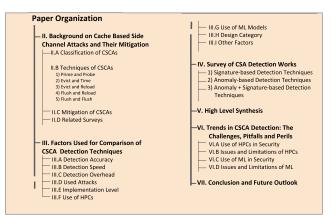

FIGURE 2. Paper organization.

enlist important findings, a high-level synthesis, and future possibilities based on our analysis of the surveyed techniques. A list of acronyms that will be used in this paper is shown in Table 1. The organization for the rest of this paper is shown in Figure 2. Section 2 discusses the background of CSCA and the most popular techniques that have been proposed to perform and mitigate such attacks. Section 3 defines and explains the most important set of parameters that can be used to compare different CSCA detection mechanisms. Section 4 presents a detailed survey of the CSCA detection techniques found in literature. Section 5 provides a summary of the most significant findings of this study and Section 6 concludes this paper.

*Scope:* Many countermeasures and mitigation techniques have been proposed against CSCAs in literature. However, we limit the scope of this work to only CSCA detection approaches. CSCAs are possible on different attack targets. However, this work only considers CSCA attacks against crypto systems. Moreover, only CSCAs in x86 architecture are considered, while they have shown to be possible on other architectures (like ARM) as well.

#### II. BACKGROUND ON CACHE BASED SIDE CHANNEL ATTACKS AND THEIR MITIGATION

In this section, we will discuss the classification of cache side channel attacks, different techniques that have been

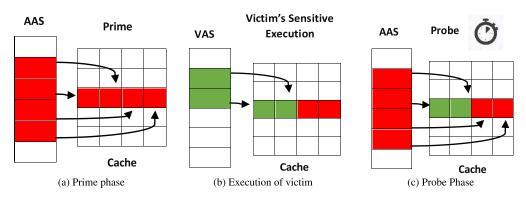

FIGURE 3. Working principle of Prime+Probe (AAS: Attacker Addr. Space, VAS: Victim Addr. Space).

proposed to perform such attacks and mitigation solutions that have been presented against these cache side channel attacks. We will also discuss any works that are related to our paper. Readers who already have a background knowledge of cache side channel attacks can skip this section.

### A. CLASSIFICATION OF CACHE SIDE CHANNEL ATTACKS

Different classifications of CSCAs based on different factors can be found in literature [24], [25]. The inherent feature that most of the cache side channel attacks exploit is the cache timing and access patterns. In order to make an attack possible, usually the attacker needs to identify the victim's memory addresses by observing the shared cache with the victim. Further, an attacker would also have to determine if a particular memory access by the victim results into a hit or a miss. Mostly attackers observe the victim's memory accesses indirectly rather than directly. Therefore, cache side channel attacks can be classified into Access Based Attacks (e.g. Prime+Probe, Flush+Reload) and Timing Based Attacks (Evict-and-Time, Cache collision) [24]. In Access-Based attacks, after the interference of attacker with the victim, the attacker observes the time that each of its memory access takes. It is assumed that the attacker will have logical access to a shared cache used by the victim process. In Timing Based Attacks unlike Access-Based attacks, attacker measures the execution time of a security critical operation performed by the victim rather than measuring the time of its own memory accesses [24].

Another classification of CSCAs is done by Page et al [25], according to which CSCAs are categorized into two types; Time driven and Trace attacks [25]. These attack types are based on the type of information leaked by the attack. Time-driven attacks commonly named as timing attacks depend on quantifiable execution time which relays information of secret cryptographic operations. This information is useful during the encryption process where number of cache hits and misses relay variable timing information. Timing difference of cache hits and misses allows the attacker to know the interesting addresses where victim is operating. Once this information is revealed, attacker is able to retrieve entire secret key. Thus, such timing attacks are capable of measuring entire execution time efficiently. Time-driven attacks are further categorized into active time-driven cache attacks and passive time-driven cache attacks. In passive time-driven attacks, attacker has no direct influence on victim's machine and attacker is unable to probe the timing information directly [26], [27]. In active time-driven attacks, the attacker actively influences the victim's machine because it can execute directly on victim's machine. Therefore, attacker is well informed about timing information of victim by which it can manipulate a lot of information [26], [28], [29]. Trace-driven attacks manipulate the trace of victim's accesses [25], [30]–[33]. This type of attack focuses to access the cache line which is frequently used by victim.

# B. TECHNIQUES OF CACHE SIDE CHANNEL ATTACKS

This sub-section discusses most of the famous techniques that have been proposed to perform CSCAs.

# 1) PRIME AND PROBE TECHNIQUE

Prime+Probe attacks belong to the category of Trace Driven attacks and are common to exploit last level shared caches across multiple cores. Many CSCAs have made use of this technique: [6], [12], [20], [22], [34]–[39]. A prime+probe attack works in two phases (prime phase and probe phase) as show in Figure 3. During the prime phase, attacker fills the shared cache with its own data as shown in Figure 3a. Attacker then goes to an idle mode and waits for victim to execute which will use few of the cache sets primed by the attacker as shown in Figure 3b. During the probe phase (shown in Figure 3c), attacker tries to load the data from the cache that it had primed (filled) earlier. If any of the cache sets have been overwritten by the victim process, it will take longer for attacker to access them (as they will have to be brought from main memory due to cache replacement). This way, attacker can get to know if the victim has used particular addresses and can extract secret data from this information.

This technique has been used at different cache levels like L1-data (L1-D) cache [35], [36], L1-instruction (L1-I) cache [40] and Last Level Cache (LLC) [41].

VAS

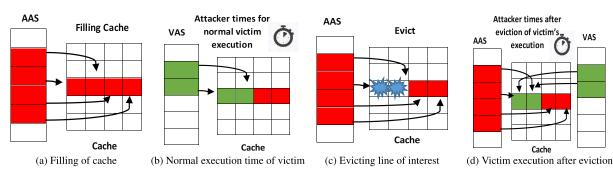

FIGURE 4. Working principle of Evict+Time.

FIGURE 5. Working principle of Evict+Reload.

### 2) EVICT AND TIME TECHNIQUE

This technique falls under the class of Time-Driven attacks. It works in a three-step process as shown in Figure 4. In the first step, as shown in Figure 4a attacker adds its own data in the cache. In the second step, attacker lets the victim process to execute normally, loads back its cache sets and notes the time of execution of the victim as shown in Figure 4b. In the third step, as shown in Figure 4c the attacker program removes a cache set (call it 'X') and lets victim execute. Then attacker analyses the variation in execution time of the victim process based on which it can be inferred if the line 'X' was accessed by the victim process or not (Figure 4d). Some of the implementations based on this technique of attack are: [12], [16], [35], [42].

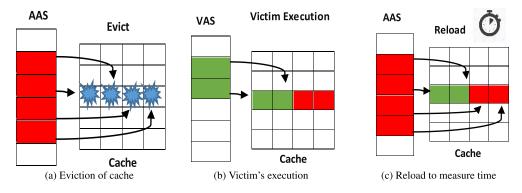

# 3) EVICT AND RELOAD TECHNIQUE

Evict+Reload (E+R) is a variation of Evict+Time (E+T) [15]. As shown in Figure 5, this technique works in two step. The first step is the eviction of cache sets shown in Figure 5a. The attacker then lets the victim run normally (Figure 5b). In the next step, the attacker reloads the data from cache and measures time of access to determine if it is a hit or a miss as shown in Figure 5c. Based on this information attacker can determine if the victim accessed particular address or not.

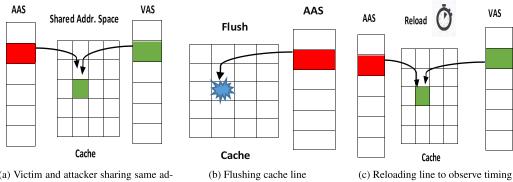

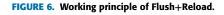

# 4) FLUSH AND RELOAD TECHNIQUE

Flush+Reload [5] shown in Figure 6, belonging to the class of Trace-Driven and Access Based attacks, relies on page sharing. There exist numerous cache attacks that used Flush+Reload technique: [11], [18], [20], [43]-[46]. In the first step of the attack (Flush), the attacker process evicts a shared cache set using available privileged instruction of CLFLUSH, shown in Fire 6b. Attacker lets the victim execute normally after flushing a shared cache line. In the next step of the attack (Reload), the attacker reloads the shared cache line and measures the loading time as shown in Figure 6c. The measured time indicates if the shared cache line was accessed by the victim or not.

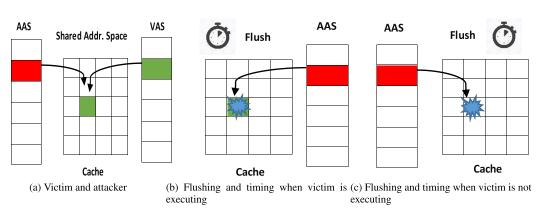

# 5) FLUSH AND FLUSH TECHNIQUE

Flush+Flush [14], also belongs to the class of Trace-Driven attacks and replaces the Reload step of a Flush+ Reload attack with a Flush. This attack relies on measuring the execution time of CLFLUSH instruction as shown in Figure 7.

In the first phase of the attack, the attacker evicts/ flushes a particular cache line from the shared (with the victim) address space 7b. The attacker then lets the victim process execute normally which may or may not access the flushed cache line. In the second phase, the attacker flushes the same cache line and measures the time that the flushing operation takes as shown in Figure 7c. Using the measured time of the flushing (which would vary depending on the existence of target cache line in the cache), attacker can determine if the victim accessed that cache line or not during its normal execution. Since, attacker does not make any extra cache accesses/reads, it is harder to track this type of attack. That's why Flush+Flush is considered to be a stealthy attack.

(a) Victim and attacker sharing same address space

FIGURE 7. Working principle of Flush+Flush.

Moreover, this type of attack is very fast. However, it is thought of having more noise and normally results into higher error rates compared to F+R and P+P attacks [5], [14], [30].

# C. MITIGATION OF CACHE SIDE CHANNEL ATTACKS

Various research works have focused on the mitigation of cache side channel attacks in the recent past. Some of these techniques focus on resource isolation by partitioning caches either through software or in the hardware [31], [47], [47], [48], [48]-[52]. Partitioned portions of the cache are essentially reserved for the protected program and this non-interference avoids CSCAs to work. Due to cache partitioning / reservation, these techniques impose significant performance bottlenecks. Further, they also increase hardware overheads due to the need of specialized hardware features like in [50]. Another technique that has been proposed as a defense against CSCAs is the randomization of the mapping between memory and cache sets [53]. This way same addresses of different applications can be mapped to different sets in the cache thus thwarting possibility of CSCAs. Another approach to mitigate CSCAs is the addition of noise either in HPCs or clock sources (used for time measurements). This has been done both in the software [54]–[56] and hardware [57].

Although a lot of research efforts have been done to propose novel mitigation techniques against malicious side-channel attacks, such techniques still need improvements. Mitigation techniques generally focus on a specific vulnerability and don't provide an all-weather protection as it can be expensive and complex. At the same time, there has been a continuous progress in the domain of attacks which keep on getting complicated and stealthier. Therefore, the gap between the demands of a CSCA mitigation technique and what they offer is increasing as well. We argue that in this scenario, CSCA detection techniques can work in synergy with CSCA mitigation and prevention techniques to simplify their design and performance cost. CSCA mitigation and prevention techniques would be activated only if a detection technique raises an alarming flag. CSCA detection techniques have to be accurate and fast in order to be useful when coupled with CSCA mitigation techniques. Researchers have proposed various techniques to detect cache based side channel attacks. It is important to understand the existing CSCA detection mechanisms and identify any improvements that can be done. Despite the importance of CSCA detection techniques, there does not exist any work that tried to survey current CSCA detection techniques. Our paper discusses the details of state-of-the-art CSCA detection techniques and compares them using a common set of parameters.

## D. RELATED SURVEYS

There exist a few survey papers which review side channel attacks in general or cache side channel attacks in specific. However, we have not been able to find any work that focuses on the review of research works that performed run-time detection of cache based side channel attacks (CSCAs). Szefer [58] broadly reviewed various microarchitectural side channel attacks along with their defense mechanisms that have been proposed so far. Ge et al. [13] also surveyed microarchitectural side channel attacks specially in cloud systems and discussed future trends and possible solutions for such attacks. Ge et al. [30] enlist a variety of cache side channel attacks and mitigation strategies specifically on modern hardware. Similarly, [59] discusses different software and hardware attacks and also studies the performance overheads of different measures against attacks specifically for AES crypto algorithms. Lyu and Mishra [60] studied CSCAs on famous encryption algorithms alongwith their countermeasures. Kong et al. [52] studied hardware-software techniques for a defense for CSCAs. Jin [61] discussed the basic concepts of hardware security in general. Zhou and Feng [62] surveyed various approaches to perform side channel attacks and their mitigation techniques. Younis et al. [63] provided an extensive analysis of CSCAs in cloud systems and compared few CSCA mitigation and detection mechanisms. The comparison is performed using three categories of CSCAs (Prime+Probe, Flush+Reload and Flush+Flush). The CSCA detection techniques that were evaluated and compared in detail include HomeAlone detection solution [64] and two-stage detection technique [10]. We will discuss these techniques in detail later on.

## III. FACTORS USED FOR COMPARISON OF CSCA DETECTION TECHNIQUES

We identify a number of important factors that can be used to compare and characterize the proposed CSCA detection techniques. It should be noted that this list is not exhaustive, but a list of the most important factors that we recognized based on the studied CSCA detection techniques.

# A. DETECTION ACCURACY

Detection accuracy should be considered to be the primary metric to judge any intrusion detection mechanism. Since, detection of side channel attacks is a binary classification problem, detection inaccuracy can be further divided into false positives (cases when a no-attack condition is detected as an attack) and false negatives (cases when an attack condition is detected as no-attack) to analyze detection results in details. Two of the commonly used metrics that have been used to represent detection accuracy in the reviewed literature are Percentage Accuracy and F-score. The reason for using F-score often over percentage accuracy is following: F-score is generally not influenced by data sets in which one class might have much more number of samples (also known as *skewed class*) than the other classes.

#### **B. DETECTION SPEED**

The speed with which an attack is detected is another important indicator for evaluating any detection proposal. Detection speed is usually a trade-off between overhead of a detection system and timely intrusion detection. Detection speed is a function of the crypto-system (which the attack is targeting) and the attack itself and should be considered accordingly. For example, Flush+Reload on RSA is a single-encryption round attack and for detection to be useful the attack should be detected before half of the total bits are encrypted. On the other hand, Flush+Flush on AES requires hundreds of encryption rounds to be successful, so its detection can be useul even if it is done after number of encryption rounds. Few of the mostly used metrics to indicate detection speed in literature include: the absolute time, the number of encryption rounds being performed by the crypto-system and the number of bits being encrypted by the crypto-system by which a detection mechanism is capable of detecting an attack.

# C. DETECTION OVERHEAD

Nothing is free. The detection mechanism will always incur some performance overhead depending on its complexity and the level of implementation. Detection overhead can be defined as the slowdown of the process to be protected due to the implemented detection mechanism. The detection overhead will be determined by the detection granularity which specifies how often the detection mechanism would be activated to make a decision based on the information provided. Secondly, the perceivable detection overhead is related to the implementation of the detection mechanism as well.

It is important to note that in this work we mainly consider the runtime detection overhead. There exist other types of overheads as well like time to train and implement a particular detection strategy. However, such overheads are usually one-time (or rare) and can be considered insignificant in comparison to runtime detection overhead.

#### D. USED ATTACKS

There are various techniques to perform cache side channel attacks (CSCAs) as discussed in the previous section. The difficulty of detection of a CSCA varies depending on the used technique and the crypto-system under consideration. For example, Flush+Flush attack is considered to be more stealthier compared to Flush+ Reload attack [14]. Therefore, in order to perform a comparison of CSCA detection techniques it is essential to identify particular attack techniques along with the crypto-systems that were used to evaluate the working of a detection mechanism for CSCA.

#### E. IMPLEMENTATION LEVEL

CSCA detection mechanism can be implemented at different levels in a computer system. The possible implementation levels include: victim application (crypto-system) itself, as a separate application/process, within the operating system, inside each Virtual Machine (VM) or directly inside the hardware. It is important to compare CSCA detection techniques based on how they are physically implemented as each level of implementation will have its own strengths and weaknesses. For example, implementing a CSCA detection mechanism as a separate application can be slow, but such a solution can work with legacy systems/hardware. On the other hand, a detection mechanism implemented inside the hardware will be fast but will not be portable to legacy systems/hardware.

### F. USE OF HARDWARE PERFORMANCE COUNTERS (HPCs)

Hardware performance counters (HPCs) are special purpose hardware registers available in most of the modern processor families. HPCs are used to monitor performance of applications by counting a number of microarchitectural and architectural events (like cache misses, executed instructions, branch mispredictions etc.) during the application's execution on the hardware. Intel x86 based processors [65] provide access to hundreds of hardware events that can be tracked using HPCs. However, due to limitation of the number of physical registers, only a few of the events can be monitored simultaneously (usually 4 to 8). Different libraries and APIs like PerfMon [66], OProfile [67], Perf tool [68], Intel Vtune Analyzer [69], and PAPI [70] can be used to configure and read HPCs. Most of the CSCA detection mechanisms have tried to use HPCs in their detection algorithms. Therefore, it is significant to observe how do the used HPCs differ across CSCA detection approaches.

#### G. USE OF MACHINE LEARNING (ML) MODELS

Machine learning techniques have influenced many fields and are gaining popularity in the field of information security as well [71]. Differentiating an attack from a non-attack case is basically a classification problem. Many side-channel detection techniques have used ML models (classifiers) to distinct attacks and non-attacks. Majority of the supervised machine learning classifiers fall into two classes of linear and non-linear models. Commonly used ML classifiers in CSCA detection techniques inlcude: Linear Discriminant Analysis (LDA), Logistic Regression (LR), Support Vector Machine (SVM), Random Forest, Decision Tree, K-Nearest Neighbor (KNN) and Neural Networks (NN). Details of these ML models can be obtained from these soruces: [72]–[74]. Each machine learning algorithm has different structure and will have different computational and memory cost for training and performing an inference decision based on the trained model. Therefore, analysis of types of ML models used in a side-channel detection technique becomes an important parameter to compare different detection techniques.

#### H. DESIGN CATEGORY

Most of the side-channel detection techniques can be divided into two basic categories based on their design: Signature based detection and Anomaly based detection. Signature based detection approaches rely on signature of "known side-channel attacks" which usually consist of selected hardware events that will be affected by those attacks. At run-time, program execution is compared with the already generated signatures and in case of a match an attack is detected. Such detection approaches usually show very good accuracy in detection of known attacks [75]. However, they might suffer from low accuracy for detection of unknown or modified attacks [75]. Anomaly-based detection approaches generate model of the behavior of normal/benign applications. Any significant "deviation" from such model will be considered an attack. Anomaly-based detection techniques are capable of identifying unknown or modified attacks [75]. However, they can have high false positive rates [75] as it is hard to build models including every possible benign application and many benign applications can resemble cache based side channel attacks due to their high memory usage.

Some research works [75], [76] have also combined both anomaly and signature based detection designs to achieve better results.

#### I. OTHER FACTORS

A couple of other factors that can prove to be valuable while comparing different detection techniques include: *Load/Noise:* This refers to the use of load/noise in the background while evaluating the proposed attack detection mechanism. It is important for the robustness of a detection technique to perform well when the system is under load (as would be the case most of the times, when attacks take place). *Attacker Identification:* This checks if the detection mechanism can also identify the actual process performing the attack. If the attacker is also identified it makes it much easier for mitigation techniques to deal with system under attacks.

#### **IV. SURVEY OF CSCA DETECTION TECHNIQUES**

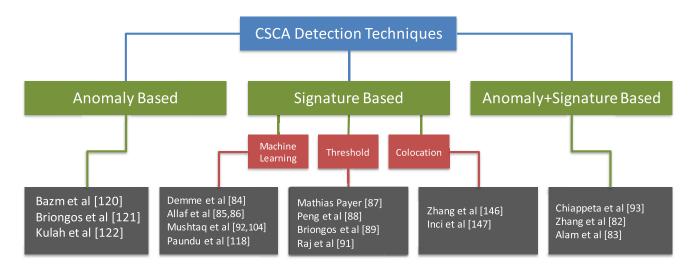

This section discusses in detail the surveyed literature about detection of cache based side channel attacks. Table 2 presented in next section summarizes and shows a comparison of all surveyed CSCA detection techniques on a common set of parameters. The reader should use special care while comparing different detection techniques based on the metrics (of Table 2) as the point of reference of some of these metrics (like detection accuracy, detection speed) could be different. For example, the reported detection accuracy of two techniques can be based on different attacks. As discussed in the previous section, CSCA detection techniques either employ anomaly based detection, signature based detection or a combination of both. Majority of the CSCA detection techniques are signature based techniques: [77]-[85] or a combination of both signature and anomaly based techniques [75], [76], [86]. Figure 8 shows a classification of CSCA detection techniques based on their fundamental design type.

| A. Akram et al.: Meet the Sherlock Holmes' of Side Channel Leakage: Survey of Cache SCA Detection Techniques |

|--------------------------------------------------------------------------------------------------------------|

|--------------------------------------------------------------------------------------------------------------|

# TABLE 2. Summary of the reviewed CSCA detection techniques.

| Reference                              | Category                         | Example<br>Attacks                                                                                                                                                                                                                                                                                                                                                   | Detection<br>Accuracy                                 | Detection<br>Speed                                       | Detection<br>overhead                                                                                                   | ML-Based                                                       | Attacker<br>Identifica-<br>tion                 | Use of<br>HPCs                              | Impl.<br>Level                             | Load/<br>Noise | Crypto<br>System |

|----------------------------------------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|-------------------------------------------------|---------------------------------------------|--------------------------------------------|----------------|------------------|

| Demme et<br>al [77]                    | Signature<br>Based<br>Detection  | P+P                                                                                                                                                                                                                                                                                                                                                                  | 100%                                                  | N/A                                                      | N/A                                                                                                                     | Yes (KNN,<br>DT, RF and<br>ANN)                                | Yes                                             | Yes                                         | Application<br>&<br>Hardware               | N/A            |                  |

| Allaf et al<br>[78]                    | Signature<br>Based<br>Detection  | F+R & P+P                                                                                                                                                                                                                                                                                                                                                            | 97% (F+R),<br>98% (P+P)                               | 2% of time<br>to complete<br>attack                      | N/A                                                                                                                     | Yes (NN,<br>DT, KNN)                                           | Yes                                             | Yes                                         | Yes                                        | Yes            | AES              |

| Allaf et al<br>[79]                    | Signature<br>Based<br>Detection  | F+R                                                                                                                                                                                                                                                                                                                                                                  | 99%<br>(Native),<br>96%<br>(Cloud)                    | N/A                                                      | N/A                                                                                                                     | Yes (KNN)                                                      | Yes                                             | Yes                                         | Application                                | Yes            | AES              |

| Mushtaq et<br>al [85]                  | Signature<br>Based<br>Detection  | F+R & F+F                                                                                                                                                                                                                                                                                                                                                            | > 99%<br>(both<br>attacks)                            | 1% of<br>RSA,<br>12.5%<br>of AES<br>completion           | < 2%                                                                                                                    | Yes (LDA,<br>LR, SVM)                                          | No                                              | Yes                                         | Application                                | Yes            | RSA &<br>AES     |

| Mushtaq et<br>al [99]                  | Signature-<br>Based<br>Detection | F+R & F+F                                                                                                                                                                                                                                                                                                                                                            | > 99%<br>(both<br>attacks)                            | $\begin{array}{llllllllllllllllllllllllllllllllllll$     | <ul> <li>2 for</li> <li>RSA and</li> <li>10%</li> <li>for AES</li> <li>completion</li> </ul>                            | Yes (LDA,<br>LR, SVM,<br>QDA)                                  | Ńo                                              | Yes                                         | Application                                | Yes            | RSA &<br>AES     |

| Mushtaq et<br>al [97]                  | Signature-<br>Based<br>Detection | P+P                                                                                                                                                                                                                                                                                                                                                                  | %66 <                                                 | 1-2%<br>of AES<br>completion                             | < 3-4%                                                                                                                  | Yes (LDA,<br>LR, SVM,<br>QDA)                                  | No                                              | Yes                                         | Application                                | Yes            | RSA &<br>AES     |

| Mathias<br>Payer [153]                 | Signature<br>Based<br>Detection  | F+R & P+P                                                                                                                                                                                                                                                                                                                                                            | 100%                                                  | N/A                                                      | < 2%                                                                                                                    | No                                                             | Yes                                             | Yes                                         | Kernel                                     | No             |                  |

| Peng et al<br>[81]                     | Signature<br>Based<br>Detection  | F+R                                                                                                                                                                                                                                                                                                                                                                  | 100%                                                  | N/A                                                      | N/A                                                                                                                     | No                                                             | Yes                                             | Yes                                         | Application                                | No             |                  |

| Briongos et<br>al [82]                 | Signature<br>Based<br>Detection  | F+R                                                                                                                                                                                                                                                                                                                                                                  | >96%                                                  | N/A                                                      | N/A                                                                                                                     | No                                                             | N/A                                             | Yes                                         | Application                                | No             | AES              |

| Raj and<br>Dhara-<br>nipragada<br>[84] | Signature<br>Based<br>Detection  | P+P, F+R                                                                                                                                                                                                                                                                                                                                                             | N/A                                                   | N/A                                                      | <8%                                                                                                                     | No                                                             | No                                              | Yes                                         | MV                                         | No             |                  |

|                                        | Note<br>F+                       | Note: N/A: Not Available/Applicable, HPC: Hardware Performace Counter, P+P: Prime+Probe, F+R: Flush+Reload,<br>F+F: Flush+Flush, E+T: Evict+Time, VM: Virtual Machine, CVM: Cross Virtual Machine, Impl:Implementation<br>ML: Machine Learning. Also, note that the mentioned detection accuracy,speed and overhead are the best-case<br>measures for each technique | ilable/Applical<br>, E+T: Evict+1<br>earning. Also, 1 | ole, HPC: Har<br>Fime, VM: Vir<br>note that the m<br>mea | Hardware Performace Count<br>: Virtual Machine, CVM: Cro<br>he mentioned detection accur<br>measures for each technique | ace Counter, J<br>CVM: Cross V<br>:tion accuracy,<br>technique | P+P: Prime+P<br>/irtual Machin<br>speed and ove | robe, F+R: F<br>e, Impl:Imp<br>rhead are th | lush+Reload,<br>lementation<br>e best-case |                |                  |

# 1) SIGNATURE-BASED DETECTION TECHNIQUES

One of the earliest CSCA detection works was done by Demme *et al.* [77] who tried to detect malware and CSCAs

based on signatures. Demme *et al.* [77] claimed to use hardware performance counters (HPCs) for the first time to solve the problem of malware and side-channels detection.

## TABLE 2. (Continued.)

| Example Detection<br>Attacks Accuracy<br>Reference                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Attack, Clock, 0.83 (Ref. Application: 0.95 (App. Thread Thread), 0.95 (App. Thread), 0.95 (App. Thread), 0.96 (CPU Speed Ma-Manipula- nipulation)                                                                                                                                                                                                                                                                                                                                                          |

| 100%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| P+P, F+R, 0.99 (AUC) N/A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| P+P, E+T N/A N/A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 100% N/A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| ~                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 0.93         for           P+P         (phy.           &         CVM)           0.99         &           0.97         for           F+F         8         CVM)           0.97         for           60.97         for           60.97         for           60.97         for           60.97         for           60.97         for           60.97         for           60.96         for           60.82         & 0.96           for         F+F           (phy.         &           CVM)         X/A |

| Note: N/A: Not Available/Applicable, HPC: Hardware Performace Counter, P+P: Prime+Probe, F+R: Flush+Reload,<br>F+F: Flush+Flush, E+T: Evict+Time, VM: Virtual Machine, CVM: Cross Virtual Machine, Impl:Implementation<br>ML: Machine Learning. Also, note that the mentioned detection accuracy,speed and overhead are the best-case<br>measures for each technique                                                                                                                                        |

# TABLE 2. (Continued.)

| Reference                | Category                                       | Example<br>Attacks                                                    | Detection<br>Accuracy                                  | Detection<br>Speed                                       | Detection<br>overhead                                                                                                 | ML-Based                                                                                                                                                                                                                                                                                                                                                    | Attacker<br>Identifica-<br>tion                  | Use of<br>HPCs                               | Impl.<br>Level                                                                          | Load/<br>Noise | Crypto<br>System                              |

|--------------------------|------------------------------------------------|-----------------------------------------------------------------------|--------------------------------------------------------|----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|----------------------------------------------|-----------------------------------------------------------------------------------------|----------------|-----------------------------------------------|

| Chiappetta<br>et al [86] | Anomaly +<br>Signature<br>Based<br>Detection   | F+R                                                                   | F-Score:<br>0.93<br>(AES), 1.0<br>(ECDSA)              | 1/5th of<br>attack<br>completion                         | N/A                                                                                                                   | Yes<br>(Anomaly<br>Detection,<br>Neural-<br>Network)                                                                                                                                                                                                                                                                                                        | Yes                                              | Yes                                          | Application                                                                             | Yes            | AES &<br>ECDS                                 |

| Zhang et al<br>[75]      | Anomaly +<br>Signature<br>Based<br>Detection   | P+P, F+R                                                              | 100%                                                   | order of ms                                              | < 5%                                                                                                                  | No                                                                                                                                                                                                                                                                                                                                                          | N/A                                              | Yes                                          | MV                                                                                      | N/A            | Both<br>symmet-<br>ric and<br>asym-<br>metric |

| Alam et al<br>[76]       | Anomaly +<br>Signature<br>Based<br>Detection   | [145],                                                                | %66<                                                   | N/A                                                      | N/A                                                                                                                   | Yes (RF,<br>SVM,<br>Adaboost,<br>Perceptron,<br>NB)                                                                                                                                                                                                                                                                                                         | Yes                                              | Yes                                          | Application                                                                             | Yes            | AES &<br>Clefia                               |

| Zhang et al<br>[137]     | Signature<br>Based<br>Co-location<br>Detection | P+P                                                                   | 85%                                                    | N/A                                                      | < 4.6%                                                                                                                | No                                                                                                                                                                                                                                                                                                                                                          | Yes                                              | Yes                                          | MV                                                                                      | Yes            |                                               |

| Inci et al<br>[138]      | Signature<br>Based<br>Co-location<br>Detection | P+P, F+R                                                              | 93% &                                                  | N/A                                                      | 6.1x                                                                                                                  | No                                                                                                                                                                                                                                                                                                                                                          | No                                               | No                                           | commercial<br>clouds<br>(Amazon<br>EC2,Google<br>Cloud<br>engine,<br>Microsoft<br>Azure | N/A            | RSA &<br>AES                                  |

| Wang et al<br>[148]      | Signature<br>Based                             | F+R, F+F                                                              | N/A                                                    | N/A                                                      | 4.7%                                                                                                                  | No                                                                                                                                                                                                                                                                                                                                                          | Yes                                              | Yes                                          | Application                                                                             | Yes            |                                               |

|                          | Note<br>F+1<br>M                               | te: N/A: Not Available<br>+F: Flush+Flush, E+1<br>ML: Machine Learnii | ilable/Applical<br>t, E+T: Evict+1<br>earning. Also, 1 | ble, HPC: Har<br>Time, VM: Vir<br>note that the m<br>mea | Hardware Performace Count<br>Virtual Machine, CVM: Cro<br>ne mentioned detection accur<br>measures for each technique | Note: N/A: Not Available/Applicable, HPC: Hardware Performace Counter, P+P: Prime+Probe, F+R: Flush+Reload, F+F: Flush+Flush, E+T: Evict+Time, VM: Virtual Machine, CVM: Cross Virtual Machine, Impl:Implementation ML: Machine Learning. Also, note that the mentioned detection accuracy,speed and overhead are the best-case measures for each technique | 2+P: Prime+Pr<br>Trtual Machin<br>speed and over | cobe, F+R: F<br>e, Impl:Impl<br>rhead are th | lush+Reload,<br>lementation<br>e best-case                                              |                |                                               |

# IEEE Access

FIGURE 8. Classification of CSCA detection techniques.

The proposed machine learning (ML) based detection technique relies on performance counters which are sampled at regular intervals and used as input feature vectors to ML models/classifiers. The particular ML classifiers used in this work include: K-Nearest Neighbor (KNN) [87], Decision Trees [88], Random Forest and Artificial Neural Networks (ANN) [89]. Demme et al. [77] used a case study of Prime+Probe (P+P) type of side channel attacks to evaluate their proposed CSCA detection mechanism. Importantly, their proposed detection mechanism is able to detect the attack process as well. Their experiments relied on OpenSSL as a victim process and a set of benign processes from different benchmark suites SPEC-CPU2006 [90], PARSEC [91] and other applications like games, web browsers and graphics editors. They used variants of Prime+Probe attack to generate training and evaluation data for ML algorithms. Results show that all of the used ML models (KNN, Decision Trees, Random Forest and ANN) are able to detect all of the attack threads without any false positives. The authors also presented a possible hardware implementation of their detector which would consist of four basic blocks: Data Collector, Data Analyzer, Action System and Secure Updater. The possible design choices to implement the detector module in hardware include: separate cores, accelerators,  $\mu$ -controller, FPGA or a coprocessor [77]. This is the only work out of the surveyed research works that proposed a possible hardware implementation of their detection module.

Another approach named *SCADET* [92] is a signaturebased detection tool, which detects Prime+Probe attack. Instead of using HPCs (hardware performance counters), this approach uses high-level semantics and invariant patterns of attack (targeting I-cache, D-cache and LLC). Results show that *SCADET* provides high accuracy but they lack discussion on detection speed and performance overhead of the mechanism. Authors report that, in some cases, system provides false alarms under load conditions. Moreover, the trace analysis time in this approach is very long (notable irregularities when trace exceeds a certain size), which renders the solution not suitable for run-time detection.

Allaf et al. [78] also presented a signature based CSCA detection mechanism that uses Machine Learning (ML) to generate signatures which are representative of attacks. Allaf et al. [78] used three ML algorithms namely Neural Networks [89], Decision Trees [88] and K-Nearest Neighbor (KNN) [87] to detect cache based side channel attack specifically on AES crypto-system. The particular side channel attacks used in their work are Flush+Reload (F+R) and Prime+Probe (P+P). A data set containing values of seven different hardware performance counters which include core cycles, reference cycles, core instructions and other four features having the best effect on classification of attack and no-attack scenarios for the used attacks is collected during execution of processes (attacks and benign processes). This data set is used for both training and validation of machine learning algorithms. The data set covers two scenarios: with and without any noise in the background when attacks and victim programs are running. Integer and Floating-point categories of SPEC-CPU2006 benchmarks (SPEC-int and SPEC-fp) [90] are executed in the background to simulate noise/load conditions.

Allaf *et al.* [78] also processed training data before using it to train ML classifiers. The dimensions of training data are first reduced using a technique of Principal Component Analysis (PCA) [93]. The data is then passed through a well-known optimization algorithm called L-DFGS [94], which is known for its affinity towards smaller data sets. The particular decision tree used in their work is C4.5 [95] which is a famous tree-based statistical classifier. Evaluation of the proposed technique on an Intel Xeon (X5650) processor shows that the best classification success rate is shown by Decision Tree which is 0.97% for F+R and 0.98% for P+P attacks in case of no SPEC benchmarks in the background. The accuracy is reduced in case of background SPEC benchmarks (specially in case of SPECfp benchmarks, which according to authors' claim make heavier use of CPU components specially caches compared to the integer benchmarks). However, decision trees still have better accuracy compared to other methods under noisy conditions. Results further show that the detection framework (which learns at run-time) is able to learn the behaviour of malicious process in less than 1 second in worst case, which authors claim is very fast in comparison to 50 seconds required for retrieval of entire key bits by an F+R attack implementation done by [96] on the used machine. Results also show that decision trees are less efficient (have low detection speed) compared to the other methods but show better accuracy.

Later, Allaf et al. [79] used Machine Learning to generate signatures of malicious loops of attack processes to detect them at run-time. Allaf et al. [79] specifically used K-Nearest Neighbor (KNN) classifier to detect malicious loop activity within Flush+Reload (F+R) attack do detect attacks without the need of observing any synchronization between attacker and victim process as some other techniques [75], [76] do. The used machine learning model is trained using three features of L1, L2 and last-level cache (LLC) misses. Selected benchmarks (bzip2, gcc, bwaves, dealII) from SPEC-CPU2006 [90] benchmark suite are executed in the background to create realistic system conditions. Programs are profiled by reading performance counters at time intervals of  $0.02\mu$ s, which is the time that a single run of malicious loop of F+R attack takes. N number of profiled samples are grouped together and are represented by the average of those samples. These representative samples are fed to K-NN classifier to make classification decision. The experimental evaluation of the presented model on an Intel Xeon system shows that it can achieve an accuracy of 99% on native system and 96% on a cloud system, without any extra overhead on cloud system. However, authors declare that this mechanism would not work for other attacks like Prime+Probe considering the differences in working of malicious loop in the attack. Moreover, authors claim that the trained classifier does not need to be re-trained to detect hostile processes in a new environment.

Some of the research works belonging to the category of signature-based detection that have been done recently include: [85], [97]–[99]. One of these works done by Mushtaq *et al.* [85] targets stealthier CSCAs like Flush+Flush (F+F). Mushtaq *et al.* [85] proposed *NIGHTs-WATCH* to detect cache-based side-channel attacks at run-time using ML models (LDA, LR, SVM). Different hardware performance counters are used to profile victim cryptosystems RSA and AES under attack and no-attack scenarios to train ML models. *NIGHTs-WATCH* is embedded into the cryptosystems to profile them at run-time using HPCs and apply trained ML models to detect presence of any side-channel attacks. The particular case studies used to evaluate *NIGHTs-WATCH* include Flush+Reload and Flush+Flush attacks. *NIGHTs-WATCH* being a run-time detection mechanism is evaluated using a variety of metrics like detection accuracy, speed and overhead. Evaluation of the proposed detection technique shows that it can achieve a high detection accuracy with little performance overhead for both attacks even under noisy conditions. Specifically, it is shown to have a detection accuracy of 99.51%, 99.50% and 99.44% for Flush+Reload attack under no, medium and high noise at very high detection speed (within 1% completion of a single RSA encryptions). For Flush+Flush attack, the detection accuracy is shown to be 99.97%, 98.74% and 95.20% for no, medium and high noise at high detection speed (within 12.5% completion of 400 AES encryptions which is the minimum number of encryptions required for a successful attack). Performance overhead of the detection module is less than 2% in both cases. Later on, this work was extended by Mushtaq et al. [97], [98] to include Prime+Probe and other variant attacks under both RSA and AES cryptosystems. These approaches also use ML models (LDA, LR, SVM, QDA) and HPCs to detect different variants of these attacks at run-time. Reference [98] shows a high detection accuracy of up to 99.51% for Flush+Reload attack on RSA, incurring a performance overhead of 1.63% and 99.99% accuracy on AES while incurring a maximum performance overhead of 8.28%. The experimental results show consistency for Flush+Flush attack on different implementations of AES as well. Reference [97] show detection accuracy of > 99% for Prime+Probe attack and their variants running on AES crypto-system with performance overhead of 3 - 4% at the highest detection speed.

Some of the signature based detection techniques don't rely on Machine Learning to learn attack signatures. Rather they use thresholds of particular hardware events to determine if an attack is in place. Examples of such works include: [80]-[82], [84]. One of these works, done by Mathias Payer [80], utilizes the values of cache miss rates and page faults of processes to detect an attack. Mathias Payer [80] proposed an attack detection framework HexPADS which can detect cache based side channel attacks along-with Rowhammer [100] and CAIN [101] attacks. HexPADS reads status of different performance counters like total executed instructions, total LLC accesses and total LLC misses. It also uses kernel information of processes like total page faults. Same type of detection technique is used for both row-hammer and cache side channel attacks and does not distinguish between the two. The proposed detection mechanism basically continuously monitors the cache accesses and misses of all processes. If cache miss rate of a process is found to be higher than 70% i.e. greater than 70% of cache accesses results into misses, and the same process has a low number of page-faults, the process is detected to be an attack. The evaluation of the proposed detection technique is done using following attacks: cache template attacks [15] based on Flush+Reload (F+R) and an enhanced version of C5 [102] based on Prime+Probe (P+P) attack. Performance overhead of the detection framework is measured by executing SPEC-CPU2006 [90] and PARSEC [91] benchmark suites when

detection framework is active, indicating that the mean of overhead (loss in performance of executed benchmarks) is less than 2%. Experiments show that *HexPADS* can detect both attacks successfully. However, it is not evaluated using any realistic load/noise conditions.

Another threshold based technique which is similar to the one proposed by Mathias Payer [80] has been presented by Peng et al. [81]. Peng et al. [81] used cache miss rates and data-TLB miss rates to recognize cache side-channel attacks. They showed that cache side channel attacks like Flush+Reload (F+R) have high cache miss rates but low dTLB (Data Translation Lookaside Buffer) miss rates. The detection mechanism scans all running processes on a system and observe the values of performance events specifically cache and dTLB miss rates for these processes. A detection flag is raised if the cache miss rate is found to be above and dTLB miss rate below a particular threshold. Variants [5], [15], [102] of Flush+Reload type of CSCA are used for evaluation of the proposed technique. Experimental results show that this technique is able to discriminate cache based side channel attacks from benign processes and other timing attacks accurately. Experimental analysis does not present other run-time detection evaluation metrics like speed and overhead.

The work of Briongos et al. [82] also depends on the comparison (of encryption times) with set thresholds to determine the occurrence of CSCA. Briongos et al. [82] built a timing model to discriminate if a process is being attacked or not. Cache based side channel attacks on AES encryption system are considered in this work. As shown in [82], the distribution of AES encryption times under attack and no-attack cases shows an observable distinction when no other processes are executing on the CPU. Authors conclude that in such a case encryption times above a threshold would be highly indicative of an attack. To create a realistic scenario, authors experimented with running of other workloads in the background along-with an attack. The first case involves running Lookbusy program [103] in the background, which is a CPU-centric workload designed to stress computational capability of a processor. The distribution of encryption times in this case shows that the peak heights indicating non-attack cases rise. In the second case, a memory benchmark Rand-Mem2 [104] is used to stress memory system by performing random accesses to memory. The results in this case showed that this process only caused a single cache miss for one encryption at maximum and affects lower than 1% of encryption rounds. This infers that the CPU consumption will have more effect on time distribution (which is to be used in the detection process). Based on these observations, the proposed cache side channel attack detection algorithm uses the time distribution of encryption algorithm. The method uses last 200 samples of encryption times at any time instance. From these samples, a histogram is created (using time intervals of 20 cycles). Peaks of this histogram are found using a windowing operation. The height of these peaks are used to decide if an attack is active or not. Experimental results show

that the proposed detection algorithm achieves a detection accuracy greater than 96% (false positive rate of 5%). It is shown that the false positive rate can be further reduced to 0% if initializing stage of victim process is ignored.

Raj and Dharanipragada [84] presented PokerFace to identify and mitigate cache attacks which compares the memory bus bandwidth with a threshold level to detect a CSCA. The proposed framework consists of two components: Poker and Face (both are implemented as single threads in guest VM). Poker is responsible for detection of attacks which triggers Face upon an attack detection. Face then performs cache obfuscation to make the attack unsuccessful. The attacks are detected at the level of VM. Poker works by observing memory bus bandwidth to obtain information regarding cache accesses. The working of Poker is based on the fact that during a cache attack the victim VM suffers from significant degradation in memory bus bandwidth. The evaluation of the proposed framework is done using Prime+Probe and Flush+Reload types of cache side channel attacks. Performance overhead of *PokerFace* using STREAM [105], Sysbench [106] and PARSEC [91] benchmark suites is found to be less than 8%.

Intel introduced an extension to their instruction set architecture (ISA) named Intel Software Gaurd Extension (SGX) to protect the execution of unprivileged programs inside secure enclaves. Still the privileged programs with malicious intent can perform side channel attacks on programs inside a secure enclave. The work of Chen et al. [107] employs a threshold based design to detect a special case of cache side channel attacks. Chen et al. [107] proposed Deja-Vu to detect side channel attacks on programs guarded by SGX. Privileged attacker regularly preempts the shielded execution of victim process which is executing inside an enclave. This leads to unanticipated enclave exits which are known as Asynchronous Enclave Exits (AEXs). These preemptions can be observed by the operating system (OS) and a higher frequency of such preemptions indicate the presence of an attack. Deja-Vu detects the existence of AEXs to identify the presence of an attack. *Deja-Vu* needs a reference clock, that cannot be compromised, to measure the execution time of SGX application to be protected. The execution time of the application at run-time when detection mechanism is active is compared with the normal run-time (run-time of the process when no-attack is in place). A time difference above a threshold indicates the possibility of enclave exits and a possible attack. To make sure that the used reference clock is trust-worthy, it is protected by Intel's hardware transactional memory (TSX) support. The run-time overhead of Deja-Vu is found to be less than 5% using nbench [108] benchmark suite. However, the required instrumentation can increase the size of enclave binaries by approximately 64%.

An example of the signature based CSCA detection approaches that uses special data structures (like bloom filters) is the work of Chouhan and Hasbullah [83]. Chouhan and Hasbullah [83] used bloom filters [109] to propose a detection for cache based side channel attacks in cloud systems. The use of bloom filters is motivated by the need to reduce the performance overhead of the detection mechanism. Chouhan and Hasbullah [83] fed cache miss time mean values read from performance counters to bloom filters which detect if the values belong to an attack condition or not. Bloom filters, due to their fundamental nature, do not lead to any false negatives. For readers not familiar with bloom filters, bloom filters are used to decide if a certain element is a member of a particular set. Once, certain index values are generated after an hash function is computed on elements of set under consideration, bits in bloom filter corresponding to those index values are set to true. For any new element (for which decision about its membership to the set under consideration is to be made), it is passed to the hash functions and it's seen if bit indexes corresponding to hash functions' outputs are set to 1 (membership would be true if outputs are set to 1 and false otherwise). Bloom filters prevent false negatives, but can lead to cases of false positives. Bloom filters are supposed to be very efficient to find memberships of elements in a set as they don't rely on actual comparisons, rather use hash functions.

The proposed detection technique of Chouhan and Hasbullah [83] first records the cache miss patterns of processes with the help of performance profiling tools like perf. Cache miss times (CMT) for these patterns are also calculated with the help of a timer. Mean of the differences of each successive CMT is calculated and formed signatures are stored in a bloom filter. At run-time, the detection mechanism calculates such signatures again and pass them to bloom filter to check membership of the signatures under consideration. If set membership is found to be true, it indicates a high probability of an attack. The methodology is evaluated with the help of a cache simulator. Experimental results indicate that the proposed solution takes around 6 seconds to execute on the used machine in comparison to 17-25 seconds required to execute the Flush+Reload attack. The authors claim that the proposed mechanism should also work for the detection of unknown cache based side channel attacks.

Signatures based on KVM (kernel virtual machine) events have also been used in the detection of CSCA. Paundu et al. [110] proposed a CSCA detection technique in a virtualized environment using the information of KVM (Kernel Virtual Machine) events. These events (collected using ftrace utility [111]) provide information about the host kernel operations when a guest system is running on it (i.e. they monitor the guest activity). A machine learning model SVM (with RBF kernel) is trained using the KVM events data for specific time sequences. A set of normal applications (including idle VM, web and mail server applications) forms the no-attack data set needed to train the SVM. Experimental evaluation shows a performance overhead of 0.7% for a host system based on Intel Xeon processor (set up with 8 VMs). All three classes of CSCA techniques (Prime+Probe, Flush+Reload and Flush+Flush) are used to evaluate the proposed CSCA detection technique. ROC (Receiver Operating Characteristic) curve of the trained classifier shows an AUC (Area Under the Curve) value of 0.99 while classifying attack and no-attack scenarios.