# EMC Conducted Emission Analysis of a 3D Multilayer Printed Circuit Board with Kron's Method

Z. Xu, Y. Liu, B. Ravelo, O Maurice, J Gantet, N Marier, B. Agnus, S. Carras

## ► To cite this version:

Z. Xu, Y. Liu, B. Ravelo, O Maurice, J Gantet, et al.. EMC Conducted Emission Analysis of a 3D Multilayer Printed Circuit Board with Kron's Method. EuMC 2019, Sep 2019, Paris, France. hal-02485759

## HAL Id: hal-02485759 https://hal.science/hal-02485759

Submitted on 24 Feb 2020

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# EMC Conducted Emission Analysis of a 3D Multilayer Printed Circuit Board with Kron's Method

Z. Xu, Y. Liu and B. Ravelo

Normandy University UNIROUEN, ESIGELEC, IRSEEM, EA 4353, 76000 Rouen, France

O. Maurice

ARIANE GROUP 51-61, route de Verneuil, 78133 Les Mureaux Cedex, France

J. Gantet and N. Marier VALEO – GEEDS (Group Electronic Expertise and Development Services), 76, rue Auguste Perret, 94000 Créteil, France

> B. Agnus SCIENTEAMA, 27 rue des Glengarrians, 14610 Villons Les Buissons, France

### S. Carras

FILIX SAS, Rue Saint-Aventin, F-10150 Creney-prés-Troyes, France

E-mail: zhifei.xu@esigelec.fr

Abstract-This paper introduces a fast analysis of signal integrity (SI) and electromagnetic compatibility (EMC) conducted emission (CE) for a multilayer printed circuit board (PCB). The analysis consists in elaborating the ICEM of PCB constituted by electrical interconnect and integrated circuits (ICs) presenting digital and RF/microwave effects. The 3D multilayer PCB including the IC components are modelling with the Kron's formalism using the tensorial analysis of networks (TAN). The equivalent graph topology of the EMC model and the transfer impedance analytical formulation are introduced. The EMC CEs emanated in the PCB are defined from the IC-EMC standardized internal activities. The overall system is modeled in the Kron's equivalent graph. Then, the problem solution is determined from the mesh impedance metric and current calculation. is elaborated in order to establish the metric of the problem. The effectiveness of the developed EMC CE modelling is verified with comparison of frequency domain computations from the TAN method and simulations with a commercial tool. Less computation time of EMC CE voltage noise and transfer impedance spectrums from DC to 1 GHz was pointed out.

Keywords—Signal integrity (SI); Electromagnetic compatibility (EMC); Conducted emission (CE); IC-EMC model; Kron's method; Multilayer PCB; Transfer impedance.

#### I. INTRODUCTION

The electromagnetic compatibility (EMC) issue constitutes a major concern of electronic system designers with the increase

of the integration density [1-2]. In addition, to meet the user requirements, the printed circuit board (PCB) must operate with higher data speed and generating parasitic effects of undesirable EMC emission up to microwave frequencies. The EMC perturbations influence onto the PCB performance [3] must be investigated with improved techniques. Therefore, the PCB EMC and signal integrity (SI) compliances are still an open challenge to the electronic and microwave circuit designers [4-5]. Different characterization and modelling techniques of electronic components and PCBs were developed for both conducted and radiated EMC aspects [6]. Nevertheless, the EMC experimental characterization techniques are usually time-cost and expensive. Alternative analytical methods [8-9] and computational commercial tools [10-12] have been deployed for the EMC analyses. However, more adequate predictive EMC model is still needed notably for the packaged structures [1,8]. A standard ICEM IC-EMC model referenced IEC 62433 has been developed to qualify the IC printed circuit boards (PCBs) [3,9,13]. Nevertheless, this ICEM model is generally implemented in SPICE circuit. But the SPICE environment is not appropriated to the simulations of PCBs including the 3D multilayer structures analysis. For this reason, in the present paper, an EMC conducted emission (CE) modelling is developed by exploiting the unfamiliar Kron's method. Before the exploration of this unfamiliar and fascinating model, it is worth to describe briefly the state-of-the-art about the tensorial analysis of networks (TAN). Historically, the TAN was initiated in the 1930s by G. Kron to treat problems of electrical machine [14]. Since 1990s, the Kron's concept has been extended and combined with the Branin's method by Maurice and his group for the EMC of complex electronic systems [15]. More recently, the Kron-Branin's method was explored to the modelling of planar [16] and multilayer [17] PCB interconnects for the high-speed SI analysis. In the present paper, the Kron's method is originally used to the EMC CE modelling of a multilayer PCB composed of multilayer interconnects and ICs.

#### II. METHODOLOGY OF THE PCB CONDUCTED EMC KRON'S METHOD ANALYSIS

The present paragraph describes the methodology of the Kron's model development. After the problem formulation, the graph description and the tensorial expressions of EMC CE transfer impedance will be introduced.

#### A. Formulation of the Considered PCB EMC CE Problem

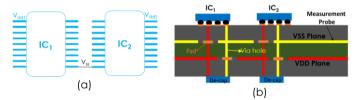

For the better understanding the Kron's modelling, a proof of concept (PoC) having block diagram and the 3D profile view of the circuit under study represented in Fig. 1 is studied in this paper. This PCB is constituted by ICs IC<sub>1</sub> and IC<sub>2</sub> and decoupling capacitors ("de-cap") implemented on four-layer structure. This circuit will be considered to study the EMC CE when there are two ICs operating in coordination. A 1  $\Omega$  EMC test probe can be envisaged for the EMC CE measurement. The bias voltage references are represented by  $V_{ss}$  and  $V_{dd}$ planes. The via elements constituting the PCB is modeled as  $LC \pi$ -networks [18-19].

Fig. 1. (a) Block diagram and (b) configuration of the 3D multilayer PCB.

#### B. Graph Topology

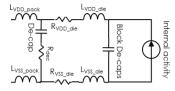

The EMC CE circuit model between the power supply nodes  $V_{dd}$  and  $V_{ss}$  of IC<sub>1</sub> and IC<sub>2</sub> are depicted in Fig. 2. In addition to the internal activity source current, the presented passive component parameters represent the bias, die, via, decoupling ("dec") and packaging ("pack") elements [9].

Fig. 2. EMC CE model between the nodes  $V_{dd}$  and  $V_{ss}$  of the utilized ICs [9].

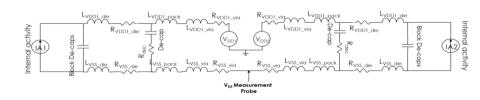

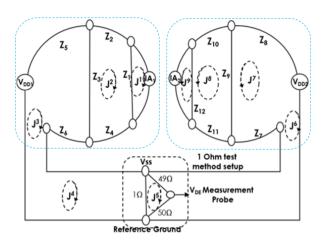

The classical schematic of the overall PCB circuit EMC CE introduced in Fig. 1 is shown in Fig. 3. The determination of the CE voltage noise across the reference ground plane of the ICs  $IC_1$  and  $IC_2$  constitutes the posed-problem. The CE is analyzed by integrating ICs' ICEM-CE models essentially built with the decoupling capacitors, RC-network, die RLnetwork and packaging RL-network models. The EMC CE generator of the ICs is represented by the current source internal activities  $IA_1$  and  $IA_2$ . Table I indicates the main parameters of the constituting network passive elements [9]. Then, the Kron's formalism of the considered electronic system is constructed with the equivalent graph introduced in Fig. 4. This graph is composed of B=18 branches and M=9meshes. The IC1 and IC2 IC-EMC models are implemented in left and right parts of the graph, respectively. The model of the test probe for the CE voltage noise monitoring is integrated into the bottom part of the graph. The right part is composed of the ICEM - CE model of IC2. The branch and mesh contravariable currents are denoted by  $I^b$  ( $b=\{1,2,\ldots,18\}$ ) and  $J^m$  (m={1,2,...,9}) respectively.

TABLE I. ICEM CE MODEL PARAMETERS

| Network description | Impedance       | Detailed parameters                                                    |

|---------------------|-----------------|------------------------------------------------------------------------|

|                     | name            |                                                                        |

| Bias                | Z <sub>1</sub>  | C <sub>b1</sub>                                                        |

| Die                 | $Z_2$           | $R_{vdd1\_die}, L_{vdd1\_die}$                                         |

| Decoupling          | Z <sub>3</sub>  | $R_{dec1}, C_{d1}$                                                     |

| Die                 | $Z_4$           | R <sub>vss1_die</sub> , L <sub>vss1_die</sub>                          |

| Via and packaging   | Z5              | L <sub>vdd1_pack</sub> , L <sub>vdd1_via</sub> , R <sub>vdd1_via</sub> |

|                     | Z <sub>6</sub>  | L <sub>vss1_pack</sub> , L <sub>vss1_via</sub> , R <sub>vss1_via</sub> |

|                     | Z <sub>7</sub>  | L <sub>vss2_pack</sub> , L <sub>vss2_via</sub> , R <sub>vss2_via</sub> |

|                     | $Z_8$           | L <sub>vdd2_pack</sub> , L <sub>vdd2_via</sub> , R <sub>vdd2_via</sub> |

| Decoupling          | $Z_9$           | $C_{d2}$ , $R_{dec1}$                                                  |

| Die                 | Z <sub>10</sub> | L <sub>vdd2_die</sub> , R <sub>vdd2_die</sub>                          |

| Die                 | Z <sub>11</sub> | L <sub>vss2_die</sub> , R <sub>vss2_die</sub>                          |

| Bias                | Z <sub>12</sub> | C <sub>b2</sub>                                                        |

Fig. 3. IC-EMC CE circuit model of the PCB introduced in Fig. 1.

Fig. 4. Kron's equivalent graph topology of the circuit shown in Fig. 3.

#### C. Tensorial Analysis

To establish the Kron's mathematical analysis, the current and voltage can be represented by other sources and flux respectively.

#### 1) Branch Space Analysis

All the impedance functions on the branches composed the diagonal of the branch space matrix. The size of the square matrix is equal to the number of branches. The branch impedance metric and the voltage source covariable can be defined in the following equations respectively:

$$\begin{bmatrix} Z_{bb}(j\omega) \end{bmatrix} = \begin{bmatrix} Z_1 & 0 & \cdots & \cdots & 0 & 0 \\ 0 & Z_2 & 0 & \cdots & 0 & 0 \\ \vdots & 0 & \ddots & \ddots & \vdots & \vdots \\ \vdots & \vdots & \ddots & \ddots & 0 & 0 \\ 0 & 0 & \cdots & 0 & Z_{B-1} & 0 \\ 0 & 0 & \cdots & 0 & 0 & Z_B \end{bmatrix},$$

(1)

$$\begin{bmatrix} E_b \end{bmatrix} = \begin{bmatrix} V_1 & 0 & \cdots & \cdots & 0 & V_2 \end{bmatrix}.$$

(2)

For the sake of the analytical simplification, the Kron's formalism allows the transformation from branch space to mesh space, the connection matrix  $C_m^b$  is established based on the relation between the branch current and mesh current.

#### 2) Mesh Space Analysis

The mesh fictive current  $J^{1,...,9}$  is considered as the expected results which can be determined systematically by the following equations:

$$E_m = C_m^b E_b, \quad (3) \qquad \text{and} \qquad Z_{mn} = C_m^a Z_{ab} C_n^b. \quad (3)$$

The expected frequency domain results for the mesh current can be obtained merely with the global Ohm's law:

$$J^{n} = Y^{nm}E_{m}, \quad (5) \quad \text{with} \quad \left[Y^{nm}\right] = \left[Z_{mn}\right]^{-1}. \quad (6)$$

*3)* EMC CE Transfer Impedances

By denoting  $j\omega$  and  $k=\{1,2\}$ , the angular frequency complex variable, the transfer impedance associated to the IC<sub>1</sub> and IC<sub>2</sub> internal activities can be defined respectively as:

$$Z_{t_k}(j\omega) = V_{nCE_k}(j\omega) / IA_k(j\omega).$$

(7)

(4)

The total transfer impedance can be written as:

$$Z_t(j\omega) = Z_t(j\omega) + Z_t(j\omega).$$

(8)

In order to highlight the relevance of this theoretical approach, EMC CE analysis in the frequency domain will be discussed in the next section.

#### III. VALIDATION RESULTS

To validate the proposed Kron's transfer impedance model, comparison between Matlab computations and SIwave® [12] from ANSYS® is performed. The PoC 3D multilayer PCB is built with conductor layers made of copper metallization and FR4 dielectric substrate.

#### A. Description of the PoC Parameters

The two ICs constituting the PCB PoC are IC<sub>1</sub> is a  $\mu$ P component from STMicroelectronics Technology® and IC<sub>2</sub> is a Flash component from Micron®. These ICs share the same reference voltage  $V_{SS}=0$  V with different core supplies  $V_{DD1}=1.1$  V and  $V_{DD2}=3.3$  V. Based on the fabrication technology specifications, the CE model parameters of IC<sub>1</sub> and IC<sub>2</sub> are generated by the IC-EMC tool developed by the INSA Toulouse laboratory [9,13]. The characteristics of the internal activities, low and high current levels  $I_l$  and  $I_h$ , and the time domain parameters, rise and fall times  $t_r$  and  $t_f$ , time width  $T_w$  and signal period T are summarized in Table II. By injecting the spectrums of  $IA_1(j\omega)$  and  $IA_2(j\omega)$  into the inputs of the Kron's graph developed in the previous section, the CE ground noise  $V_{nCE}(j\omega)$  is computed. The model and simulation were performed in Python® programming.

| TABLE II. | IC INTERNAL ACTIVITY ELECTRICAL AND TIME- |  |

|-----------|-------------------------------------------|--|

|           | DOMAIN CHARACTERISTICS.                   |  |

| IA    | Ilow/Ihigh      | Rise/fall times | Pulse width/<br>Period |

|-------|-----------------|-----------------|------------------------|

| μΡ    | 0.113 A/1.125 A | 0.12 ns         | 18 ps/2.25 ns          |

| FLASH | 0.095 A/0.945 A | 0.15 ns         | 22 ps/7.85 ns          |

#### B. Discussion on the Frequency Domain Results

Fig. 5(a) plots the transient signals corresponding to  $IA_1$  and IA<sub>2</sub>. These perturbations are characterized from the IC EMC standards. Fig. 5(b) and Fig. 5(c) display respectively the magnitudes of  $V_{nCE}$  and transfer impedance  $Z_t$  from DC to 1 GHz related to  $IA_1$  and  $IA_2$  from the Kron's model and the commercial tool SIWave® from ANSYS®. It can be emphasized these frequency results are globally wellcorrelated. The discrepancies appearing especially at low frequencies are mainly due to the numerical accuracies and the errors from the IA1 and IA2 FFTs. Table III describes the different advantages and drawbacks of the TAN modelling compared to the familiar computational methods as SPICE and full wave approaches. Despite the mentioned disadvantages, our future work is aimed to develop an improved method enabling to increase the Kron's model accuracy in function of the specific application cases.

Fig. 5. Comparison of the simulated and Kron's modeled spectrums of (a) Internal activity of  $IC_1$  and  $IC_2$  (b) the CE noise voltage and (c) the ICs transfer impedance.

TABLE III.

COMPARISON OF THE TAN MODEL ADVANTAGES AND

DRAWBACKS WITH THE FAMILIAR CIRCUIT SIMULATION SOLVER.

| Method | Advantage                         | Drawback                      |

|--------|-----------------------------------|-------------------------------|

| SPICE  | Based on the nodal analysis       | Hard to analyze coupling and  |

|        | which is very good for the        | EM fields                     |

|        | lumped linear circuit analysis    |                               |

| Full   | Numerical simulator based on      | Cannot be used for the        |

| wave   | solving Maxwell equations         | lumped circuit analysis and   |

|        | which is very good for 3D         | particularly long time        |

|        | basic structure analysis          | consuming                     |

| Kron's | The fast solution for complex     | Sensitive to the inaccuracies |

| method | circuits with less pre- and post- | related to the constituting   |

|        | processing and good for           | hybrid elements               |

|        | analyzing entire hybrid system    |                               |

#### IV. CONCLUSION

An unfamiliar EMC CE model of multilayer PCB is developed. The proposed model is based on the Kron's method. The modeling methodology is highlighted with a PoC four-layer PCB built with  $\mu$ P and Flash components. The different steps from the problem parametrization, circuit representation, graph topology elaboration and tensorial expression are described. The relevance of the EMC CE Kron's model is approved with comparison between Python® computation and commercial tool simulations. The computed results of the CE voltage spectrums are in good correlation with the commercial tool simulation.

#### ACKNOWLEDGMENT

This research work was supported by Euripides<sup>2</sup>-Eureka Program funded by the project no. 14-0303 "Embedded Die Design Environment & Methodology for Automotive Applications (EDDEMA, http://www.eurekanetwork.org/project/id/14-0303)", 2015-2018.

#### REFERENCES

- B. Archambeault, C. Brench and S. Connor, "Review of printed-circuitboard level EMI/EMC issues and tools," IEEE Trans. Electromag. Comp., vol. 52, no. 2, 2010, pp. 455-461.

- [2] J. Kim, and E. Li, "Special issue on PCB level signal integrity, power Integrity, and EMC," IEEE Trans. Electromagnetic Compatibility, vol. 52, no. 2, pp. 246-247, May 2010.

- [3] E. Sicard, A. Boyer, P. Fernandez-Lopez, A. Zhou, N. Marier and F. Lafon, "EMC performance analysis of a Processor/Memory System using PCB and Package-On-Package," Proc. of 10th International Workshop on the Electromagnetic Compatibility of Integrated Circuits (EMC Compo) 2015, Edinburgh, UK, 10-13 Nov. 2015, pp. 238-243.

- [4] M. I. Montrose, Printed Circuit Board Design Techniques for EMC Compliance: A Handbook for Designers, 2nd Edition, Wiley-IEEE Press, New York, USA, June 2000.

- [5] B. R. Archambeault, O. M. Ramahi and C. Brench, EMI/EMC Computational Modeling Handbook, Ed. Springer-Verlag, New York Inc., USA, 2013.

- [6] G. Antonini, S. Cristina and A. Orlandi, "EMC Characterization of SMPS Devices: Circuit and Radiated Emissions," IEEE Trans. Electromagnetic Compatibility, vol. 38, no. 3, Aug. 1996, pp. 300-309.

- [7] K. Aunchaleevarapan, K. Paithoonwatanakij, W. Khan-ngern and S. Nitta, "Novel method for predicting PCB configurations for near-field and far-field radiated EMI using a neural network," IEICE Trans. Commun., Vol. E86-B, No. 4, pp. 1364–1376, Apr. 2003.

- [8] A. E. Ruehli and A. C. Cangellaris, "Progress in the methodologies for the electrical modeling of interconnects and electronic packages," Proc. of the IEEE, 2001, vol. 89, no. 5, pp. 740-771.

- [9] A. Boyer, M. A. Gonzalez Sentis, C. Ghfiri and A. Durier, "Modeling methodology of the conducted emission of a DC-DC converter board," Proc. of 11th International Workshop on the Electromagnetic Compatibility of Integrated Circuits (EMC Compo) 2017, St. Petersburg, Russia, 4-8 July 2017, pp. 73-78.

- [10] Design platform for power integrity, signal integrity and EMI analysis of IC packages and PCBs, https://www.ansys.com/frfr/products/electronics/ansys-siwave, accessed 2019.

- [11] https://www.cst.com/solutions/article/designing-automotive-ethernetwith-electromagnetic-simulation, accessed 2019.

- [12] EM/EMC Simulation Software, https://www.emcos.com/?producttypes=em-simulation-software, accessed 2019.

- [13] IC-EMC software, http://www.ic-emc.org/, accessed 2019.

- [14] W. Givens, "Review: Gabriel Kron, Tensor Analysis of Networks," Bull. Amer. Math. Soc., vol. 47, no. 7, 1941, pp. 536-538.

- [15] O. Maurice, A. Reineix, P. Durand and F. Dubois, "Kron's method and cell complexes for magnetomotive and electromotive forces," Int. J. Applied Mathematics, vol. 44, no. 4, 2014, pp. 183-191.

- [16] B. Ravelo and O. Maurice, "Kron-Branin Modeling of Y-Y-Tree Interconnects for the PCB Signal Integrity Analysis", IEEE Trans. Electromag. Comp., vol. 59, no. 2, Apr. 2017, pp. 411-420.

- [17] Z. Xu, Y. Liu, B. Ravelo, J. Gantet, N. Marier and O. Maurice, "Direct Time-Domain TAN Model of 3D Multilayer Hybrid PCB: Experimental Validation," IEEE Access, vol. 6, no. 1, Dec. 2018, pp. 60645-60654.

- [18] T. V. Nguyen, A. Morales and S. Agili, "Characterization of differential via holes using equivalent circuit extraction technique," Int. J. RF MCAE, 2007, vol. 17, no. 6, pp. 552–559.

- [19] G. Antonio, M. Lai, A. Orlandi and V. Ricchiuti, "Characterization of via holes on printed circuit boards," Proc. 8th Workshop on Signal and Propagation Interconnects (SPI), 9-12 May 2004, Heidelberg, Germany, pp. 211-214.