# A 4H-SiC high-power-density VJFET as controlled current limiter

Dominique Tournier, Philippe Godignon, Josep Montserrat, Dominique Planson, Christophe Raynaud, Jean-Pierre P Chante, Franck Sarrus, Christian Bonhomme, Jean-François F de Palma

# ▶ To cite this version:

Dominique Tournier, Philippe Godignon, Josep Montserrat, Dominique Planson, Christophe Raynaud, et al.. A 4H-SiC high-power-density VJFET as controlled current limiter. Industry Applications Society (IAS'02), Oct 2002, Pittsburgh (Pennsylvania), United States. pp.2248-2251. hal-02477074

HAL Id: hal-02477074

https://hal.science/hal-02477074

Submitted on 13 Feb 2020

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# A 4H-SiC High Power Density VJFET as Controlled Current Limiter

D. Tournier, Ph. Godignon J. Montserrat Centro Nacional de Microelectronica (CNM) Campus UAB - Bellatera, Spain tournier@cnm.es D. Planson, C. Raynaud, J.P. Chante Centre de Génie Electrique de Lyon (CEGELY) Villeurbanne, France

F.Sarrus, C. Bonhomme, J.F. de Palma Ferraz Shawmut Newburyport – MA, USA

Abstract — Considering fault current limiters for serial protection, a lot of structures exist, from regulation to other complex systems such as circuit breakers, mechanical switches or more conventional fuses. Up to now, only few semiconductor current limiter structures have been described in the litterature [1]. Although Current Regulative Diode components already exist [2, 3], the voltage and current capabilities (V<sub>BR</sub>=100 V, I<sub>max</sub>=10 mA), do not allow to use them in power systems. This paper presents both simulation study and experimental results of a bi-directional current limiter structure based on a vertical SiC VJFET. This device was designed for serial protection in order to limit I2t value. Finiteelement simulations were performed with ISE-TCAD [4] to design the device and evaluate static electrical characteristics of the VJFET. Then, dynamic simulations were performed to underline current reduction ability and power losses adjustment by gate resistance value optimization. Finally, electrical characterization for an unidirectional and a bi-directional devices have been done up to 400 V. The measured specific resistance is in the range of 176 m $\Omega$ ·cm<sup>2</sup>. Limiting capabilities have also been measured for a bi-directional device made of two unidirectional device connected head to tail. Highest breakdown voltage value in "current limiting state" were measured to be around to 811 V, corresponding to a high power density of 140 kW/cm<sup>2</sup>.

**Keywords** — Current limiter, JFET, serial protection device, high voltage, command integration.

# I. INTRODUCTION

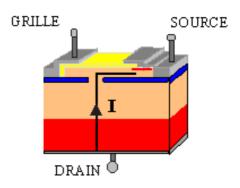

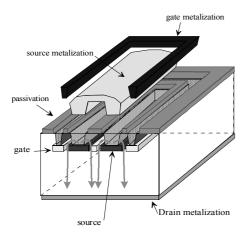

SiC semiconductor based devices are suitable for high current and high voltage applications [5,6]. A promising application of SiC-based devices is current limitation for power system protection [2,3], which benefits from its high thermal conductivity and wide band gap. Most of silicon components realized in SiC, Schottky diode, MOSFET, MESFET, show good electrical and thermal characteristics [6]. Few SiC-current limiter were presented [1,7]. This work is targeting the design, manufacturing and characterization of a new VJFET [9] (fig.1), which implement both gate and source

Fig.1. Cross section of the VJFET.

in buried layers. In the steady state, the voltage drop across the component must be as low as possible. In the active state, (limiting phase), the current limiter must sustain a high current, under high voltage bias. The resulting high power density must not cause component failure. We will describe the structure, the behavior of the component and the adjustable parameters. Then, dynamic simulations are discussed. Finally experimental electrical characteristics of both unidirectional and bi-directional are presented.

# II. SIC VJFET CONTROLLED CURRENT LIMITER

# A. Structure description

The novelty of this device consists in the design of the gate, which is formed by a buried layer. Fig. 1 shows the cross section of the  $\alpha\textsc{-SiC}$  VJFET. This device has a channel divided in two parts: a vertical one and a lateral one. The source is grounded and current flows from drain to source. Pburied layers are designed so that the VJFET is a normally-on and presents a low specific resistance. When the drain voltage rises, the current saturates at a voltage corresponding to the pinch-off of both vertical and horizontal channels. In the saturation mode, the device presents an important on resistance ( $R_{\rm ON}$ ), resulting from the serial resistance of both

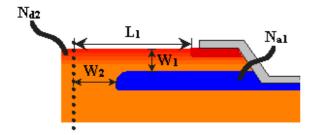

Fig.2. VJFET parameters to be optimized.

parts of the channel and the drift resistance of the epitaxial layer. Due to self heating, current decreases as the voltage increases (since electron mobility decreases and induces a current reduction). This effect is amplified while increasing limiting current density. When a negative bias is applied between gate and source, the PN junction formed by the Pwell and the epitaxial layer is reverse biased leading to current modulation. A trade off between specific resistance and blocking capabilities was investigated by simulations.

#### B. Static simulations

A global optimal parameter (eq.1) taking into account both doping concentration and geometrical dimensions (detailed in eq. 2) allow to get a range of parameters to be investigate by fine simulations.

$$Opt(W,Nd,L) = \max \left( \frac{g_0 \cdot g_{ms}}{V_p \cdot I_p} \right)_{(W,Nd,L)}$$

(1)

$$g_{ms} = \frac{Z.\mu}{L} (2.\varepsilon.q.N_d)^{1/2} \left[ V_p^{1/2} - (V_{di} - V_g)^{1/2} \right], g_o = \frac{Z.\mu.q.N_{d.a}}{L}$$

$$V_p = \frac{q.N_{d.a}^2}{2.\varepsilon} , I_p = \frac{Z.\mu.q^2.N_{d.a}^2}{6.\varepsilon.L}$$

(2)

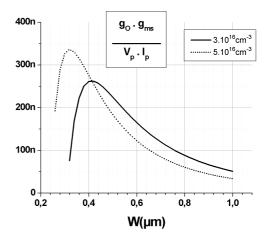

As an example, considering a channel doping concentration of  $3.10^{16}$  Atoms/ cm<sup>-3</sup>, the optimal channel thickness is assumed to be around  $0.4\mu m$  (Fig. 3). To estimate peripheral effect on the electrical characteristics, finite element simulations are useful. In that case, different models are used, taking into account physical properties of silicon carbide. As the dissipated power can reach high values, the mobility temperature dependence is taken into account Tab.1 . Most of parameters were given by Ruff [8] or are extracted from experimental results [9].

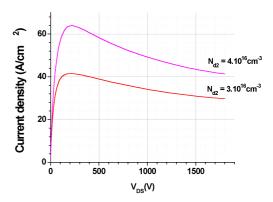

Main parameters to be adjusted are presented in Fig. 2. As an example, channel parameter  $N_{d2}$  has been investigated. Current density dependence and self heating effect are presented on Fig. 4 (both increasing while rising doping concentration). The simulated specific resistance  $R_d$  in the linear mode is in the range of 150  $m\Omega\cdot cm^2$  @  $V_{DS}$  = 1V.

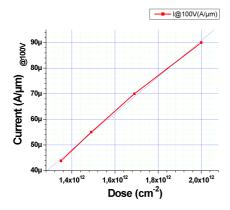

Finite simulations allows to stand a current dependence versus channel implanted doses. This let us choose a set of fabrication parameters considering for example the desired current saturation value (Fig. 5). Additional parameters such as device breakdown voltage have been taken into account for the design of the final demonstrator.

Fig.3. Optimal channel thickness estimation.

TABLE I. MOBILITY MODEL AND PARAMETERS USED FOR SIMULATION (CAUGEY THOMAS MODEL)

$$\mu_{n,p} = \mu_{\min 1} + \frac{\mu_{\max} \left(\frac{T}{300}\right)^{-\xi} - \mu_{\min 2}}{1 + \left(\frac{N_i}{C_r}\right)^{\xi}}, \quad N_i = N_A$$

| Param ètres                                                                 | 4 H -S iC |                    |

|-----------------------------------------------------------------------------|-----------|--------------------|

|                                                                             | μn        | μр                 |

| μ <sub>max</sub> (cm <sup>2</sup> .V <sup>-1</sup> .cm <sup>-1</sup> )      | 870       | 120                |

| μ <sub>m in 1</sub> (c m <sup>2</sup> .V <sup>-1</sup> .c m <sup>-1</sup> ) | 0         | 0                  |

| μ <sub>m in 2</sub> (c m <sup>2</sup> .V <sup>-1</sup> .c m <sup>-1</sup> ) | 0         | 0                  |

| Cr (cm <sup>-3</sup> )                                                      | 2.1017    | 5.10 <sup>19</sup> |

| α                                                                           | 0,55      | 0,3                |

| ξ                                                                           | 2         | 2                  |

Fig.4. Influence of the surface channel doping on the current density and self heating effect.

Fig.5. Saturation current dependence versus channel dosis.

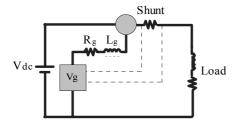

Fig.6. Electrical circuit for switching.

# C. Dynamic simulations

Mixed-mode simulations using a spice circuit and finite element for the VJFET were done to evaluate switching performances of the circuit described on Fig. 6. Parasitic wiring inductance has been taken into account. Using a shunt for current sensing and an appropriate electronic command block allows to modulate the VJFET gate voltage to thereby reduce the current in the circuit. The simulated electrical circuit is presented in Fig. 7. Switching simulations were performed with a two step gate bias.

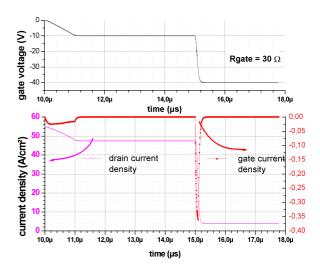

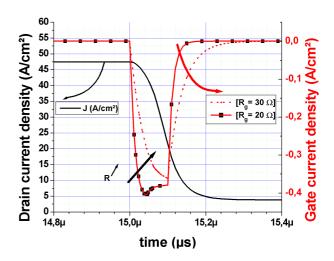

The first gate bias step underlines the current reduction ability ( $V_{GS} =$  -10 V @ t = 10 µs). Then, applying a gate bias  $V_{GS} =$  -40 V @ t = 15 µs allows to shut down the current in the circuit as presented in Fig. 7. The switch off gate current is function of the gate resistance value and voltage rise time. Adjusting resistance value allow to control the gate switch off power losses, without effect on drain current value and switch off time, as shown in Fig. 8. Consequently, gate power losses and peak current are reduced of around 10% as resumed in table I.

TABLE II. COMMUTATION LOSSES AS FUNCTION OF RG

| $R_G$ | I <sub>Gmax (A/cm²)</sub> | $P_{off(W/cm^2)}$ |

|-------|---------------------------|-------------------|

| 20    | - 0.41                    | 0.146             |

| 30    | -0.36                     | 0.133             |

Fig.7. Current reduction and switch off waveform.

Fig.8.Switching off characteristics details for 2 R<sub>gate</sub> values.

# III. DEVICE FABRICATION AND CHARACTERIZATION

Various device layouts have been implemented (such as an interdigitated device presented in Fig. 9), to validate both the process technology, parameters adjustments and the device performances.

Key points of the device fabrication are high energy implantation, annealing activation and ohmic contact formation. State of arts values [6] of ohmic contact were measured on the first batch of VJFET fabricated ( $\approx 10 \mu\Omega$ .cm<sup>2</sup>).

Fig.9a. Interdigitated structure cross-section.

Fig.9b. Fabricated interdigitated VJFET.

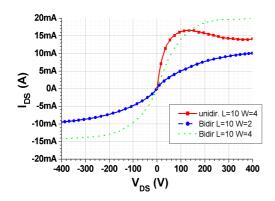

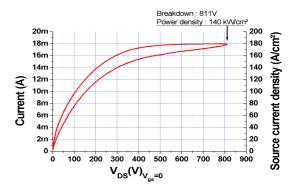

Fig. 10 presents the measured electrical characteristics for an unidirectional VJFET. Unidirectional measurements were done with 0,5 s pulse (f = 2Hz), with drain bias up to 400 V. The specific resistance varie from 176 m $\Omega$ ·cm² up to 237 m $\Omega$ ·cm² for the matrix structures. The maximum pulsed power density dissipated in the limiting mode is 160 kW/cm². Limiting capabilities have also been measured for a bidirectional device made of two unidirectional device connected head to tail (i.e. drain connected). This one exhibits a specific resistance of 700 m $\Omega$ ·cm². Highest breakdown in "current limiting state" were measured to be around to 811 V (Fig. 11), corresponding to a high pulsed power density of 140 kW/cm².

Fig.10. Electrical measured characteristics for unidirectional and bidirectional limiter.

Fig.11 Unidirectional current limiter characteristics

#### IV. CONCLUSION

This work has demonstrated the feasibility of a SiC current limiter with high power density. The design was made using the ISE software with respect to the technological limitations. The first demonstrator measurements exhibit optimistic results. Bi-directional components were measured by associating two devices head to tail. SiC VJFET manufacturing process is compatible with SiC MESFET manufacturing process [10]. This allows to foreseen the integration of a self controlled current limiter by an appropriated association of FET transistors. This device could be used in application such as current limitation in case of a short circuit of an electrical system. It could permits an elevation of the current ratings of classical mechanical device. Switching measurements will be made to validate both current sensing and gate bias voltage generation using the electronic control card.

#### ACKNOWLEDGMENT

We would like to thank Ferraz-Shawmut Company for their financial support of this work and the European Community for the Access to Research Infrastructure action of the improving Human Potential Program. The realization of this device has been achieved at the CNM (Barcelona).

### REFERENCES

- [1] Siemens Corp. « Current limiter circuit » , Patent n°W09727657, 30/07/97

- [2] Sze, « Physics of semiconductors », p351-353, 2<sup>nd</sup> Edition Wiley.

- [3] Semitec Corp. Current Regulative Diode Distributor.

- [4] ISE Software Manual.

- [5] Y.Sugawara, «12 19kV 4H-SiC pin Diodes with Low Power Loss», ISPSD'01, Osaka, pp27-30.

- [6] H.Matsunami, « Progress in Wide Bandgap Semiconductor SiC for Power Devices », invited paper, ISPSD'00 22-25 May 2000, Toulouse

- [7] F. Nallet « Electrical and Electrothermal 2D simulation of a 4H-SiC High Voltage Current limiting Device for serial protection application », pp287-290, ISPSD'00 22-25 May 2000, Toulouse.

- [8] M. Ruff, « SiC devices : Physics and Numerical Simulation» , IEEE Trans. Electron Devices ED-41 n°6 June 1994.

- [9] M.Lades., « Modeling and Simulation of Wide Bandgap Semiconductor Devices: 4H/6H-SiC», Tesis of Technischen Universität Munchen 15/05/2000.

- [10] Tournier & al. «Compatibility of VJFET technology to MESFET fabrication and its interst to system integration, ... », Materials Science Forum Vols. 389-393 (2002) pp. 1403-1406