# Les machines: architecture des ordinateurs - d'une introduction historique à la définition d'une machine virtuelle universelle -

Olivier Cogis, Jérôme Palaysi, Richard Terrat

#### ▶ To cite this version:

Olivier Cogis, Jérôme Palaysi, Richard Terrat. Les machines: architecture des ordinateurs - d'une introduction historique à la définition d'une machine virtuelle universelle -. 2020. hal-02457380

HAL Id: hal-02457380

https://hal.science/hal-02457380

Preprint submitted on 28 Jan 2020

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Les machines : architecture des ordinateurs

d'une introduction historique à la définition d'une machine virtuelle universelle

Olivier Cogis

Jérôme Palaysi

Richard Terrat

olivier.cogis@umontpellier.fr palaysi@lirmm.fr

richard.terrat@umontpellier.fr

4

28 janvier 2020

#### Résumé

Cet article est une présentation de ce qu'on appelle communément l'architecture des ordinateurs en Informatique. Il est destiné aux étudiants de niveau Licence ou Master en Informatique, notamment à ceux préparant un CAPES d'informatique, comme aux enseignants du secondaire qui souhaitent accompagner l'apparition de la discipline Informatique au lycée. Il suit un plan en 5 parties :

- La genèse des ordinateurs où l'on introduit progressivement et en suivant la voie historique les étapes qui ont conduit aux fondements de l'architecture que l'on connaît actuellement

- L'architecture de base des ordinateurs en exposant les grands principes communs à toutes les réalisations

- La présentation d'un Ordinateur Réduit Facile Évolutif Universel (que nous appelons ORFEU) illustrant ce type d'architecture et son langage d'assemblage (LAMOR). Cet ordinateur et ce langage pouvant également servir de base à l'élaboration de séances d'enseignement.

- Quelques extensions facilitant la programmation d'un ordinateur de base

- Les architectures évoluées du processeur et des mémoires

Il est suivi d'une brève conclusion et de quelques annexes

### Table des matières

1 La genèse

|          | 1.1  | Étymologie                                                    |

|----------|------|---------------------------------------------------------------|

|          | 1.2  | Quelques définitions                                          |

|          | 1.3  | Bref historique                                               |

|          | 1.4  | Les premières machines à calculer mécaniques                  |

|          | 1.5  | L'introduction de la mémoire                                  |

|          | 1.6  | Le codage binaire                                             |

|          | 1.7  | Le calcul logique                                             |

|          | 1.8  | La programmation                                              |

|          | 1.0  | 1 0                                                           |

|          |      | 1                                                             |

|          |      | <u> </u>                                                      |

|          |      | Le microordinateur                                            |

|          | 1.12 | L'ordinateur quantique                                        |

| <b>2</b> | Arc  | hitecture de base dite de "Von Neumann"                       |

|          | 2.1  | Introduction                                                  |

|          | 2.2  | La mémoire                                                    |

|          | 2.3  | L'unité arithmétique et logique (UAL)                         |

|          | 2.4  | L'unité de commande                                           |

|          |      | 2.4.1 Description                                             |

|          |      | 2.4.2 Fonctionnement                                          |

|          |      | 2.4.3 Contrôle de séquence                                    |

|          | 2.5  | Les instructions                                              |

|          |      | Les instructions                                              |

|          |      | 2.5.2 Exécution                                               |

| 0        | ODI  | DDI                                                           |

| 3        |      | FEU                                                           |

|          | 3.1  | L'unité arithmétique et logique                               |

|          | 3.2  | La mémoire                                                    |

|          | 3.3  | Les instructions                                              |

|          | 3.4  | 1 1 0                                                         |

|          | 3.5  | LAMOR                                                         |

|          |      | 3.5.1 Codes opération symboliques                             |

|          |      | 3.5.2 Étiquettes et identificateurs symboliques d'un opérande |

|          |      | opérande                                                      |

|          |      | 3.5.3 Un exemple de programme LAMOR                           |

|          | 3.6  | Dix exemples de programmes LAMOR                              |

| 4        | Exte | ensions de l'architecture de base                             |

| _        | 4.1  | Ajout de registres                                            |

|          | 4.2  | Le code condition                                             |

|          | 4.3  | Adressage                                                     |

|          | 1.0  | 4.3.1 Adressage indexé                                        |

|          |      | 4.3.2 Adressage basé                                          |

|          |      | 4.3.3 Adressage indirect                                      |

|          |      | T.U.U 11414BBBE HIGHEUU                                       |

| 4.4       Pile d'exécution       43         4.4.1       Sous-programmes       43         4.4.2       Coroutines       44         4.5       Interruptions       45         4.6       Exceptions       45         4.7       Modes et sécurité       46         5       Architectures évoluées       47         5.1       Le processeur       47         5.1.1       Microprogrammation       47         5.1.2       Jeu réduit d'instructions       48         5.1.2       Jeu réduit d'instructions       48         5.1.3       Ensemble d'UAL spécialisées       48         5.1.4       Chaînes de calcul       48         5.1.5       Architectures multicœurs       49         5.1.6       Architectures parallèles       49         5.2       Les Mémoires       51         5.2.1       L'antémémoire       52         5.2.2       La mémoire centrale       52         5.2.3       La mémoire morte       53         5.2.4       Les mémoires de masse       54         5.2.5       Organisation des informations       54         5.2.6       La mémoire virtuelle       60         <                                                                                                                               |              |      | 4.3.4   | Composition de modes d'adressage          | 42 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------|---------|-------------------------------------------|----|

| 4.4.1       Sous-programmes       43         4.4.2       Coroutines       44         4.5       Interruptions       44         4.6       Exceptions       45         4.7       Modes et sécurité       46         5       Architectures évoluées       47         5.1       Le processeur       47         5.1.1       Microprogrammation       47         5.1.2       Jeu réduit d'instructions       48         5.1.3       Ensemble d'UAL spécialisées       48         5.1.4       Chaînes de calcul       48         5.1.5       Architectures multicœurs       49         5.1.6       Architectures parallèles       49         5.2       Les Mémoires       51         5.2.1       L'antémémoire       52         5.2.2       La mémoire centrale       52         5.2.2       La mémoire morte       53         5.2.2       La mémoires de masse       54         5.2.5       Organisation des informations       54         5.2.6       La mémoire virtuelle       60         7.1       L'arithmétique et la logique d'ORFEU       60         7.1.1       Division euclidienne, modulo et congruence <t< td=""><td colspan="3"></td><td></td><td>43</td></t<>                                                     |              |      |         |                                           | 43 |

| 4.4.2 Coroutines       44         4.5 Interruptions       44         4.6 Exceptions       45         4.7 Modes et sécurité       46         5 Architectures évoluées       47         5.1 Le processeur       47         5.1.1 Microprogrammation       47         5.1.2 Jeu réduit d'instructions       48         5.1.3 Ensemble d'UAL spécialisées       48         5.1.4 Chaînes de calcul       48         5.1.5 Architectures multicœurs       49         5.1.6 Architectures parallèles       49         5.2 Les Mémoires       51         5.2.1 L'antémémoire       52         5.2.2 La mémoire centrale       52         5.2.3 La mémoire morte       53         5.2.4 Les mémoires de masse       54         5.2.5 Organisation des informations       54         5.2.6 La mémoire virtuelle       56         6 Conclusion       59         ANNEXES       60         7 L'arithmétique et la logique d'ORFEU       60         7.1.1 Division euclidienne, modulo et congruence       60         7.1.2 Représentation des nombres       61         7.1.3 Addition : instruction ADD       62         7.1.4 Soustraction : instruction SUB       63                                                                |              |      |         |                                           | 43 |

| 4.5 Interruptions       44         4.6 Exceptions       45         4.7 Modes et sécurité       46         5 Architectures évoluées       47         5.1 Le processeur       47         5.1.1 Microprogrammation       47         5.1.2 Jeu réduit d'instructions       48         5.1.3 Ensemble d'UAL spécialisées       48         5.1.4 Chaînes de calcul       48         5.1.5 Architectures multicœurs       49         5.1.6 Architectures parallèles       49         5.2 Les Mémoires       51         5.2.1 L'antémémoire       52         5.2.2 La mémoire morte       52         5.2.3 La mémoire morte       53         5.2.4 Les mémoires de masse       54         5.2.5 Organisation des informations       54         5.2.6 La mémoire virtuelle       56         6 Conclusion       59         ANNEXES       60         7 L'arithmétique et la logique d'ORFEU       60         7.1.1 Division euclidienne, modulo et congruence       60         7.1.2 Représentation des nombres       61         7.1.3 Addition : instruction ADD       62         7.1.4 Soustraction : instruction SUB       63         7.2 La logique       64 <t< th=""><th></th><th></th><th>4.4.2</th><th></th><th>44</th></t<> |              |      | 4.4.2   |                                           | 44 |

| 4.6       Exceptions       45         4.7       Modes et sécurité       46         5       Architectures évoluées       47         5.1       Le processeur       47         5.1.1       Microprogrammation       47         5.1.2       Jeu réduit d'instructions       48         5.1.3       Ensemble d'UAL spécialisées       48         5.1.4       Chaînes de calcul       48         5.1.5       Architectures multicœurs       49         5.1.6       Architectures parallèles       49         5.2.1       L'antémémoire       52         5.2.2       La mémoire centrale       52         5.2.3       La mémoire morte       53         5.2.4       Les mémoires de masse       54         5.2.5       Organisation des informations       54         5.2.6       La mémoire virtuelle       60         7.1.1       Division euclid                                                                                                |              | 4.5  | Interr  |                                           | 44 |

| 4.7 Modes et sécurité       46         5 Architectures évoluées       47         5.1 Le processeur       47         5.1.1 Microprogrammation       47         5.1.2 Jeu réduit d'instructions       48         5.1.3 Ensemble d'UAL spécialisées       48         5.1.4 Chaînes de calcul       48         5.1.5 Architectures multicœurs       49         5.1.6 Architectures parallèles       49         5.2 Les Mémoires       51         5.2.1 L'antémémoire       52         5.2.2 La mémoire centrale       52         5.2.3 La mémoire morte       53         5.2.4 Les mémoires de masse       54         5.2.5 Organisation des informations       54         5.2.6 La mémoire virtuelle       56         6 Conclusion       59         ANNEXES       60         7 L'arithmétique et la logique d'ORFEU       60         7.1.1 Division euclidienne, modulo et congruence       60         7.1.2 Représentation des nombres       61         7.1.3 Addition : instruction ADD       62         7.1.4 Soustraction : instruction SUB       63         7.2 La logique       64         7.2.2 Opérations booléennes élémentaires       64         7.3 Arithmétique et Logique<                                      |              | 4.6  |         | •                                         | 45 |

| 5.1 Le processeur       47         5.1.1 Microprogrammation       47         5.1.2 Jeu réduit d'instructions       48         5.1.3 Ensemble d'UAL spécialisées       48         5.1.4 Chaînes de calcul       48         5.1.5 Architectures multicœurs       49         5.1.6 Architectures parallèles       49         5.2 Les Mémoires       51         5.2.1 L'antémémoire       52         5.2.2 La mémoire centrale       52         5.2.3 La mémoire morte       53         5.2.4 Les mémoires de masse       54         5.2.5 Organisation des informations       54         5.2.6 La mémoire virtuelle       56         6 Conclusion       59         ANNEXES       60         7 L'arithmétique et la logique d'ORFEU       60         7.1.1 Division euclidienne, modulo et congruence       60         7.1.2 Représentation des nombres       61         7.1.3 Addition : instruction ADD       62         7.1.4 Soustraction : instruction SUB       63         7.2 La logique       64         7.2.1 Opérations booléennes élémentaires       64         7.2.2 Opérations logiques       64         7.3 Arithmétique et Logique       65         7.3.1 Inverses arithm                                      |              | 4.7  | _       |                                           | 46 |

| 5.1.1       Microprogrammation       47         5.1.2       Jeu réduit d'instructions       48         5.1.3       Ensemble d'UAL spécialisées       48         5.1.4       Chaînes de calcul       48         5.1.5       Architectures multicœurs       49         5.1.6       Architectures parallèles       49         5.1.6       Architectures parallèles       49         5.2       Les Mémoires       51         5.2.1       L'antémémoire       52         5.2.2       La mémoire centrale       52         5.2.3       La mémoire morte       53         5.2.4       Les mémoires de masse       54         5.2.5       Organisation des informations       54         5.2.6       La mémoire virtuelle       56         6       Conclusion       59         ANNEXES       60         7.1       L'arithmétique et la logique d'ORFEU       60         7.1.1       Division euclidienne, modulo et congruence       60         7.1.2       Représentation des nombres       61         7.1.3       Addition : instruction ADD       62         7.1.4       Soustraction : instruction SUB       63         7.2       La lo                                                                                       | 5            | Arc  | hitecti | ures évoluées                             | 47 |

| 5.1.2       Jeu réduit d'instructions       48         5.1.3       Ensemble d'UAL spécialisées       48         5.1.4       Chaînes de calcul       48         5.1.5       Architectures multicœurs       49         5.1.6       Architectures parallèles       49         5.2       Les Mémoires       51         5.2.1       L'antémémoire       52         5.2.2       La mémoire centrale       52         5.2.3       La mémoire morte       53         5.2.4       Les mémoires de masse       54         5.2.5       Organisation des informations       54         5.2.6       La mémoire virtuelle       56         6       Conclusion       59         ANNEXES       60         7       L'arithmétique et la logique d'ORFEU       60         7.1.1       Division euclidienne, modulo et congruence       60         7.1.2       Représentation des nombres       61         7.1.3       Addition : instruction ADD       62         7.1.4       Soustraction : instruction SUB       63         7.2       La logique       64         7.2.1       Opérations booléennes élémentaires       64         7.2.2       Opéra                                                                                       |              | 5.1  | Le pro  | ocesseur                                  | 47 |

| 5.1.3       Ensemble d'UAL spécialisées       48         5.1.4       Chaînes de calcul       48         5.1.5       Architectures multicœurs       49         5.1.6       Architectures parallèles       49         5.2       Les Mémoires       51         5.2.1       L'antémémoire       52         5.2.2       La mémoire centrale       52         5.2.3       La mémoire morte       53         5.2.4       Les mémoires de masse       54         5.2.5       Organisation des informations       54         5.2.6       La mémoire virtuelle       56         6       Conclusion       59         ANNEXES       60         7       L'arithmétique et la logique d'ORFEU       60         7.1.1       Division euclidienne, modulo et congruence       60         7.1.2       Représentation des nombres       61         7.1.3       Addition : instruction ADD       62         7.1.4       Soustraction : instruction SUB       63         7.2       La logique       64         7.2.1       Opérations booléennes élémentaires       64         7.2.2       Opérations logiques       64         7.3       Arithmétique                                                                                        |              |      | 5.1.1   |                                           | 47 |

| 5.1.4 Chaînes de calcul       48         5.1.5 Architectures multicœurs       49         5.1.6 Architectures parallèles       49         5.1.6 Architectures parallèles       49         5.1.6 Architectures multicœurs       49         5.1.6 Architectures parallèles       49         5.1.1 L'antémémoires       51         5.2 Les Mémoires       52         5.2.2 La mémoire centrale       52         5.2.3 La mémoire morte       53         5.2.4 Les mémoires de masse       54         5.2.5 Organisation des informations       54         5.2.6 La mémoire virtuelle       56         6 Conclusion       59         ANNEXES       60         7 L'arithmétique et la logique d'ORFEU       60         7.1.1 Division euclidienne, modulo et congruence       60         7.1.2 Représentation des nombres       61         7.1.3 Addition : instruction ADD       62         7.1.4 Soustraction : instruction SUB       63         7.2 La logique       64         7.2.1 Opérations booléennes élémentaires       64         7.2.2 Opérations logiques       64         7.3 Arithmétique et Logique       65         7.3.1 Inverses arithmétiques et logiques       65     <                                    |              |      | 5.1.2   | Jeu réduit d'instructions                 | 48 |

| 5.1.5       Architectures multicœurs       49         5.1.6       Architectures parallèles       49         5.2       Les Mémoires       51         5.2.1       L'antémémoire       52         5.2.2       La mémoire centrale       52         5.2.3       La mémoire morte       53         5.2.4       Les mémoires de masse       54         5.2.5       Organisation des informations       54         5.2.6       La mémoire virtuelle       56         6       Conclusion       59         ANNEXES       60         7       L'arithmétique et la logique d'ORFEU       60         7.1       L'arithmétique et la logique d'ORFEU       60         7.1.1       Division euclidienne, modulo et congruence       60         7.1.2       Représentation des nombres       61         7.1.3       Addition: instruction ADD       62         7.1.4       Soustraction: instruction SUB       63         7.2       La logique       64         7.2.1       Opérations booléennes élémentaires       64         7.2.2       Opérations logiques       64         7.3       Arithmétique et Logique       65         7.3.1       In                                                                                       |              |      | 5.1.3   | Ensemble d'UAL spécialisées               | 48 |

| 5.1.6 Architectures parallèles       49         5.2 Les Mémoires       51         5.2.1 L'antémémoire       52         5.2.2 La mémoire centrale       52         5.2.3 La mémoire morte       53         5.2.4 Les mémoires de masse       54         5.2.5 Organisation des informations       54         5.2.6 La mémoire virtuelle       56         6 Conclusion       59         ANNEXES       60         7 L'arithmétique et la logique d'ORFEU       60         7.1 L'arithmétique       60         7.1.1 Division euclidienne, modulo et congruence       60         7.1.2 Représentation des nombres       61         7.1.3 Addition : instruction ADD       62         7.1.4 Soustraction : instruction SUB       63         7.2 La logique       64         7.2.1 Opérations booléennes élémentaires       64         7.2.2 Opérations logiques       64         7.3 Arithmétique et Logique       65         7.3.1 Inverses arithmétiques et logiques       65                                                                                                                                                                                                                                                |              |      | 5.1.4   | Chaînes de calcul                         | 48 |

| 5.2       Les Mémoires       51         5.2.1       L'antémémoire       52         5.2.2       La mémoire centrale       52         5.2.3       La mémoire morte       53         5.2.4       Les mémoires de masse       54         5.2.5       Organisation des informations       54         5.2.6       La mémoire virtuelle       56         6       Conclusion       59         ANNEXES       60         7.1       L'arithmétique et la logique d'ORFEU       60         7.1       L'arithmétique       60         7.1.1       Division euclidienne, modulo et congruence       60         7.1.2       Représentation des nombres       61         7.1.3       Addition : instruction ADD       62         7.1.4       Soustraction : instruction SUB       63         7.2       La logique       64         7.2.1       Opérations booléennes élémentaires       64         7.2.2       Opérations logiques       64         7.3       Arithmétique et Logique       65         7.3.1       Inverses arithmétiques et logiques       65                                                                                                                                                                            |              |      | 5.1.5   | Architectures multicœurs                  | 49 |

| 5.2.1       L'antémémoire       52         5.2.2       La mémoire centrale       52         5.2.3       La mémoire morte       53         5.2.4       Les mémoires de masse       54         5.2.5       Organisation des informations       54         5.2.6       La mémoire virtuelle       56         6       Conclusion       59         ANNEXES       60         7       L'arithmétique et la logique d'ORFEU       60         7.1       L'arithmétique       60         7.1.1       Division euclidienne, modulo et congruence       60         7.1.2       Représentation des nombres       61         7.1.3       Addition : instruction ADD       62         7.1.4       Soustraction : instruction SUB       63         7.2       La logique       64         7.2.1       Opérations booléennes élémentaires       64         7.2.2       Opérations logiques       64         7.3       Arithmétique et Logique       65         7.3.1       Inverses arithmétiques et logiques       65                                                                                                                                                                                                                      |              |      | 5.1.6   | Architectures parallèles                  | 49 |

| 5.2.2       La mémoire centrale       52         5.2.3       La mémoire morte       53         5.2.4       Les mémoires de masse       54         5.2.5       Organisation des informations       54         5.2.6       La mémoire virtuelle       56         6       Conclusion       59         ANNEXES       60         7       L'arithmétique et la logique d'ORFEU       60         7.1       L'arithmétique       60         7.1.1       Division euclidienne, modulo et congruence       60         7.1.2       Représentation des nombres       61         7.1.3       Addition: instruction ADD       62         7.1.4       Soustraction: instruction SUB       63         7.2       La logique       64         7.2.1       Opérations booléennes élémentaires       64         7.2.2       Opérations logiques       64         7.3       Arithmétique et Logique       65         7.3.1       Inverses arithmétiques et logiques       65                                                                                                                                                                                                                                                                   |              | 5.2  | Les M   | lémoires                                  | 51 |

| 5.2.3       La mémoire morte       53         5.2.4       Les mémoires de masse       54         5.2.5       Organisation des informations       54         5.2.6       La mémoire virtuelle       56         6       Conclusion       59         ANNEXES       60         7       L'arithmétique et la logique d'ORFEU       60         7.1       L'arithmétique       60         7.1.1       Division euclidienne, modulo et congruence       60         7.1.2       Représentation des nombres       61         7.1.3       Addition : instruction ADD       62         7.1.4       Soustraction : instruction SUB       63         7.2       La logique       64         7.2.1       Opérations booléennes élémentaires       64         7.2.2       Opérations logiques       64         7.3       Arithmétique et Logique       65         7.3.1       Inverses arithmétiques et logiques       65                                                                                                                                                                                                                                                                                                                  |              |      | 5.2.1   | L'antémémoire                             | 52 |

| 5.2.4       Les mémoires de masse       54         5.2.5       Organisation des informations       54         5.2.6       La mémoire virtuelle       56         6       Conclusion       59         ANNEXES       60         7       L'arithmétique et la logique d'ORFEU       60         7.1       L'arithmétique       60         7.1.1       Division euclidienne, modulo et congruence       60         7.1.2       Représentation des nombres       61         7.1.3       Addition : instruction ADD       62         7.1.4       Soustraction : instruction SUB       63         7.2       La logique       64         7.2.1       Opérations booléennes élémentaires       64         7.2.2       Opérations logiques       64         7.3       Arithmétique et Logique       65         7.3.1       Inverses arithmétiques et logiques       65                                                                                                                                                                                                                                                                                                                                                                |              |      | 5.2.2   | La mémoire centrale                       | 52 |

| 5.2.5       Organisation des informations       54         5.2.6       La mémoire virtuelle       56         6       Conclusion       59         ANNEXES       60         7       L'arithmétique et la logique d'ORFEU       60         7.1       L'arithmétique       60         7.1.1       Division euclidienne, modulo et congruence       60         7.1.2       Représentation des nombres       61         7.1.3       Addition : instruction ADD       62         7.1.4       Soustraction : instruction SUB       63         7.2       La logique       64         7.2.1       Opérations booléennes élémentaires       64         7.2.2       Opérations logiques       64         7.3       Arithmétique et Logique       65         7.3.1       Inverses arithmétiques et logiques       65                                                                                                                                                                                                                                                                                                                                                                                                                   |              |      | 5.2.3   |                                           | 53 |

| 5.2.6       La mémoire virtuelle       56         6       Conclusion       59         ANNEXES       60         7       L'arithmétique et la logique d'ORFEU       60         7.1       L'arithmétique       60         7.1.1       Division euclidienne, modulo et congruence       60         7.1.2       Représentation des nombres       61         7.1.3       Addition : instruction ADD       62         7.1.4       Soustraction : instruction SUB       63         7.2       La logique       64         7.2.1       Opérations booléennes élémentaires       64         7.2.2       Opérations logiques       64         7.3       Arithmétique et Logique       65         7.3.1       Inverses arithmétiques et logiques       65                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |              |      | 5.2.4   | Les mémoires de masse                     | 54 |

| 6 Conclusion       59         ANNEXES       60         7 L'arithmétique et la logique d'ORFEU       60         7.1 L'arithmétique       60         7.1.1 Division euclidienne, modulo et congruence       60         7.1.2 Représentation des nombres       61         7.1.3 Addition : instruction ADD       62         7.1.4 Soustraction : instruction SUB       63         7.2 La logique       64         7.2.1 Opérations booléennes élémentaires       64         7.2.2 Opérations logiques       64         7.3 Arithmétique et Logique       65         7.3.1 Inverses arithmétiques et logiques       65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              |      | 5.2.5   | Organisation des informations             | 54 |

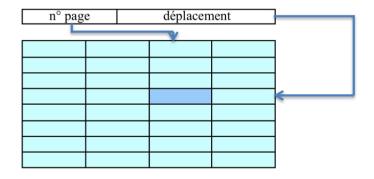

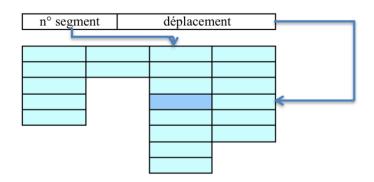

| ANNEXES       60         7 L'arithmétique et la logique d'ORFEU       60         7.1 L'arithmétique                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |              |      | 5.2.6   | La mémoire virtuelle                      | 56 |

| 7       L'arithmétique et la logique d'ORFEU       60         7.1       L'arithmétique       60         7.1.1       Division euclidienne, modulo et congruence       60         7.1.2       Représentation des nombres       61         7.1.3       Addition : instruction ADD       62         7.1.4       Soustraction : instruction SUB       63         7.2       La logique       64         7.2.1       Opérations booléennes élémentaires       64         7.2.2       Opérations logiques       64         7.3       Arithmétique et Logique       65         7.3.1       Inverses arithmétiques et logiques       65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6            | Cor  | nclusio | n                                         | 59 |

| 7.1       L'arithmétique       60         7.1.1       Division euclidienne, modulo et congruence       60         7.1.2       Représentation des nombres       61         7.1.3       Addition : instruction ADD       62         7.1.4       Soustraction : instruction SUB       63         7.2       La logique       64         7.2.1       Opérations booléennes élémentaires       64         7.2.2       Opérations logiques       64         7.3       Arithmétique et Logique       65         7.3.1       Inverses arithmétiques et logiques       65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | $\mathbf{A}$ | NNE  | EXES    |                                           | 60 |

| 7.1       L'arithmétique       60         7.1.1       Division euclidienne, modulo et congruence       60         7.1.2       Représentation des nombres       61         7.1.3       Addition : instruction ADD       62         7.1.4       Soustraction : instruction SUB       63         7.2       La logique       64         7.2.1       Opérations booléennes élémentaires       64         7.2.2       Opérations logiques       64         7.3       Arithmétique et Logique       65         7.3.1       Inverses arithmétiques et logiques       65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 7            | L'ai | rithmé  | tique et la logique d'ORFEU               | 60 |

| 7.1.1 Division euclidienne, modulo et congruence       60         7.1.2 Représentation des nombres       61         7.1.3 Addition : instruction ADD       62         7.1.4 Soustraction : instruction SUB       63         7.2 La logique       64         7.2.1 Opérations booléennes élémentaires       64         7.2.2 Opérations logiques       64         7.3 Arithmétique et Logique       65         7.3.1 Inverses arithmétiques et logiques       65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | •            |      |         |                                           |    |

| 7.1.2       Représentation des nombres       61         7.1.3       Addition : instruction ADD       62         7.1.4       Soustraction : instruction SUB       63         7.2       La logique       64         7.2.1       Opérations booléennes élémentaires       64         7.2.2       Opérations logiques       64         7.3       Arithmétique et Logique       65         7.3.1       Inverses arithmétiques et logiques       65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |              |      |         | -                                         |    |

| 7.1.3 Addition : instruction ADD       62         7.1.4 Soustraction : instruction SUB       63         7.2 La logique       64         7.2.1 Opérations booléennes élémentaires       64         7.2.2 Opérations logiques       64         7.3 Arithmétique et Logique       65         7.3.1 Inverses arithmétiques et logiques       65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |              |      |         | · · · · · · · · · · · · · · · · · · ·     |    |

| 7.1.4 Soustraction : instruction SUB       63         7.2 La logique       64         7.2.1 Opérations booléennes élémentaires       64         7.2.2 Opérations logiques       64         7.3 Arithmétique et Logique       65         7.3.1 Inverses arithmétiques et logiques       65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |              |      |         |                                           |    |

| 7.2       La logique       64         7.2.1       Opérations booléennes élémentaires       64         7.2.2       Opérations logiques       64         7.3       Arithmétique et Logique       65         7.3.1       Inverses arithmétiques et logiques       65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |              |      |         |                                           |    |

| 7.2.1 Opérations booléennes élémentaires                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |              | 7.2  |         |                                           |    |

| 7.2.2 Opérations logiques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |              |      |         |                                           |    |

| 7.3 Arithmétique et Logique                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |              |      |         |                                           |    |

| 7.3.1 Inverses arithmétiques et logiques 65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |              | 7.3  |         |                                           |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |              |      |         |                                           |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |              |      | 7.3.2   | Décalages arithmétiques : instruction DAR | 66 |

| 8  | $\mathbf{Exe}$ | mples de programmes                         | 68 |

|----|----------------|---------------------------------------------|----|

|    | 8.1            | Expression arithmétique                     | 68 |

|    | 8.2            | Instruction conditionnelle                  | 68 |

|    | 8.3            | Instruction alternative                     | 69 |

|    | 8.4            | Itération                                   | 69 |

|    | 8.5            | Algorithme d'Ahmès                          | 70 |

|    | 8.6            | Adressage indexé                            | 70 |

|    | 8.7            | Appel et retour de sous programme           | 71 |

|    | 8.8            | Adressage indirect et pointeurs             | 72 |

|    | 8.9            | Pile                                        | 72 |

|    | 8.10           | Sous programme récursif                     | 74 |

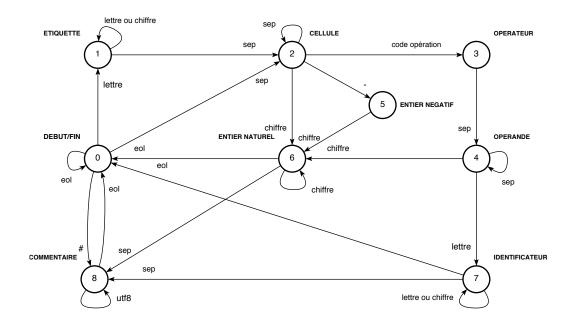

| 9  | La g           | grammaire de LAMOR                          | 76 |

|    | 9.1            | La Forme de Backus-Naur (BNF)               | 76 |

|    | 9.2            | L'automate                                  | 78 |

| 10 | ORI            | FEU et la calculabilité                     | 78 |

|    | 10.1           | Modèles de calcul                           | 79 |

|    |                | Réduction du jeu d'instructions             | 80 |

|    |                | 10.2.1 Instructions de contrôle de séquence | 80 |

|    |                | 10.2.2 Instructions arithmétiques           | 81 |

|    |                | 10.2.3 Instructions logiques                | 82 |

|    |                | 10.2.4 Instruction de décalage arithmétique | 83 |

|    |                | 10 2 5 Conclusion                           | 84 |

# 1 La genèse

# 1.1 Étymologie

Le Dictionnaire historique de la langue française <sup>1</sup> précise que le mot Ordinateur fut d'abord employé pour « celui qui institue (en parlant du Christ) ». Entre le XIe et le XVIIe siècle, il désigne celui qui est chargé de « régler les affaires publiques », puis au XIXe siècle, « celui qui met de l'ordre ».

De son côté, le *Dictionnaire des sciences* <sup>2</sup> dirigé par Michel Serres et Nayla Farouki évoque « un vieux mot de latin d'église qui désignait, dans le rituel chrétien, celui qui procède à des ordinations et règle le cérémonial ».

<sup>1.</sup> Dictionnaire historique de la langue française 2 volumes - NE - Alain Rey - 2016 -Le Robert

$<sup>2.\ {\</sup>rm Le}\ {\rm Tr\'{e}sor}$ : dictionnaire des sciences - Michel Serres, Nayla Farouki - 1997 - Flammarion

C'est l'idée de mise en ordre qui semble prévaloir. Ordinateur apparaît dans les dictionnaires du XIXe siècle comme synonyme peu usuel de ordonnateur : celui qui met en ordre.

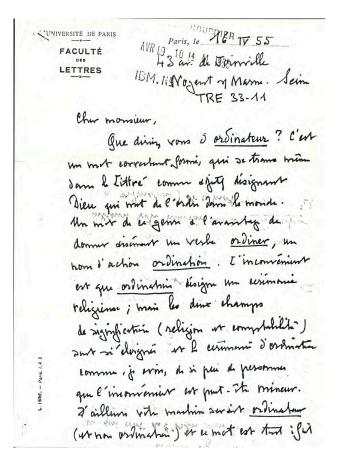

Le sens nouveau a été proposé par le professeur de philologie Jacques Perret dans une lettre datée du 16 avril 1955 en réponse à une demande de François Girard, responsable du service de publicité d'IBM France, dont les dirigeants estimaient le mot calculateur (computer) bien trop restrictif en regard des possibilités de ces machines.

C'est un exemple très rare de la création d'un néologisme authentifiée par une lettre manuscrite et datée (cf. Figure 1 *Lettre de Jacques Perret à François Girard (1955)* page 5)

FIGURE 1: Lettre de Jacques Perret à François Girard (1955)

# 1.2 Quelques définitions

« Équipement informatique comprenant les organes nécessaires à son fonctionnement autonome, qui assure, en exécutant les instructions d'un ensemble structuré de programmes, le traitement rapide de données codées sous forme numérique qui peuvent être conservées et transmises. »

Académie française neuvième édition<sup>3</sup>

« Machine automatique de traitement de l'information, obéissant à des programmes formés par des suites d'opérations arithmétiques et logiques. »

Dictionnaire Larousse 4

« Système de traitement de l'information programmable tel que défini par Turing et qui fonctionne par la lecture séquentielle d'un ensemble d'instructions, organisées en programmes, qui lui font exécuter des opérations logiques et arithmétiques. »

$Wikipedia^5$

« Machine électronique possédant une grande capacité de mémoire, capable de traiter automatiquement l'information grâce à des programmes codés enregistrés dans sa mémoire. »

Dictionnaire Reverso<sup>6</sup>

## 1.3 Bref historique

Si l'on met à part les outils antiques de calcul comme les bouliers et les abaques, on peut établir une chronologie de l'architecture des calculateurs, de la renaissance à nos jours et même rêver un peu au futur avec les ordinateurs quantiques :

— Les premières machines à calculer mécaniques

<sup>3.</sup> https://www.dictionnaire-academie.fr/article/A900665

<sup>4.</sup> https://www.larousse.fr/dictionnaires/francais/ordinateur/56358

<sup>5.</sup> https://fr.wikipedia.org/wiki/Ordinateur

<sup>6.</sup> https://dictionnaire.reverso.net/francais-definition/ordinateur

- L'introduction de la mémoire

- Le codage binaire

- Le calcul logique

- La programmation

- Les machines électromécaniques

- L'ordinateur : machine électronique universelle

- Le micro-ordinateur

- L'ordinateur quantique

# 1.4 Les premières machines à calculer mécaniques

C'est au XVIIème siècle que deux inventions vont se disputer la palme de la première machine à calculer mécanique :

- celle de l'allemand SCHICKARD $^7$  en 1623

- et la PASCALINE française en 1642 (Figure 2, page 7).

FIGURE 2: La pascaline (1642)

Si la première est sujette à controverse, car seuls des plans en font état et aucune machine de cette époque n'a jamais été retrouvée, la seconde est indiscutable comme en témoigne la quelque dizaine de modèles d'origine existant encore de nos jours.

Ces machines étaient essentiellement capables de faire des additions. Cependant, Blaise PASCAL avait déjà trouvé le moyen de faire des soustractions en utilisant le codage du complément à 10.

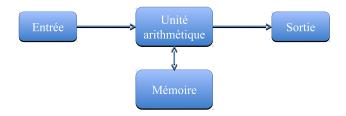

Dans cette première approche, le schéma peut se résumer comme celui de la Figure 3, page 8.

<sup>7.</sup> https://fr.wikipedia.org/wiki/Wilhelm\_Schickard

FIGURE 3: Machine à calculer numérique

#### 1.5 L'introduction de la mémoire

Les machines précédentes mériteraient plutôt le nom de machines à cumuler.

En effet, il n'est possible de visualiser qu'un seul nombre, résultant du cumul des additions et soustractions précédentes. Les opérandes sont oubliés.

Faire un produit ou une division nécessite de coucher sur le papier l'ensemble des résultats intermédiaires qu'il est nécessaire d'effectuer.

L'étape suivante va donc consister à conserver ces résultats intermédiaires pour que le calcul puisse s'effectuer sans passer par une intervention humaine de mémorisation.

C'est l'apparition des mémoires.

On peut alors effectuer les 4 opérations arithmétiques habituelles, ce que feront la machine de LEIBNIZ en 1673, l'Arithmomètre de THO-MAS en 1820 (Figure 4, page 8) . . . et bien d'autres!

La machine de Leibnitz (1704)

L'arithmomètre de Thomas (1820)

FIGURE 4: Machines à calculer avec mémoires

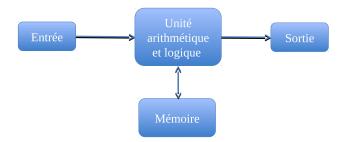

Le schéma se complète alors ainsi (Figure 5, page 9).

# 1.6 Le codage binaire

L'idée d'une représentation binaire des nombres entiers n'est pas récente. Elle est évoquée pour la première fois en Europe par Leibniz

FIGURE 5: Introduction de la mémoire

qui la découvre dans les travaux de Francis Bacon (alphabet bilitère <sup>8</sup>) et surtout dans les documents de la Chine antique. Il fut initié à cette culture par des jésuites qu'il rencontra lors de son séjour en France de 1672 à 1676, et retrouva la structure du système binaire et des hexagrammes <sup>9</sup> dans le « Hi-King » traité philosophique basé sur l'opposition du Yin et du Yang et attribué à l'époque au légendaire empereur Fou-Hi (3ème millénaire avant JC).

Ses travaux sur la logique binaire attestés par une communication en 1703 à l'Académie des Sciences  $^{10}$  annoncent avec 150 ans d'avance ceux de Boole!

À la fin de sa vie, il aura l'idée de construire une machine à calculer binaire, mais ne pourra mener à bien ce projet de son vivant.

## 1.7 Le calcul logique

En 1847 George Boole publie « Mathematical Analysis of Logic <sup>11</sup>», puis en 1854 « an Investigation Into the Laws of Thought, on Which are Founded the Mathematical Theories of Logic and Probabilities <sup>12</sup> » et fonde ce qui est connu comme l'algèbre de Boole ou le calcul booléen, dans lequel il expose que les valeurs de vérité (Vrai ou Faux) des propositions peuvent se calculer comme des expressions proches des expressions arithmétiques.

Le calcul logique devient alors un cousin du calcul arithmétique en utilisant des opérateurs spécifiques tels que OU (qui se calcule *presque* comme une somme) ET (qui se calcule comme un produit) et NON (qui se calcule comme un changement de signe).

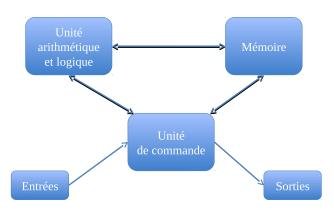

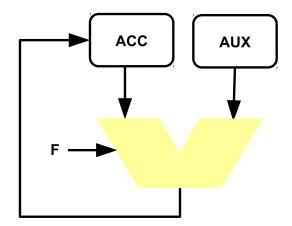

Il en résulte un schéma plus complet (Figure 6, page 10).

$<sup>8.\ \</sup>mathtt{https://www.apprendre-en-ligne.net/crypto/stegano/bilitere.html}$

<sup>9.</sup> https://fr.wikipedia.org/wiki/Hexagramme\_Yi\_Jing

<sup>10.</sup> https://gallica.bnf.fr/ark:/12148/bpt6k3483p/f247

<sup>11.</sup> http://www.gutenberg.org/files/36884/36884-pdf.pdf

<sup>12.</sup> http://www.gutenberg.org/files/15114/15114-pdf.pdf

FIGURE 6: Introduction du calcul logique

#### 1.8 La programmation

Même en mémorisant les résultats intermédiaires dans la machine à calculer, la suite des calculs doit néanmoins être mémorisée indépendamment.

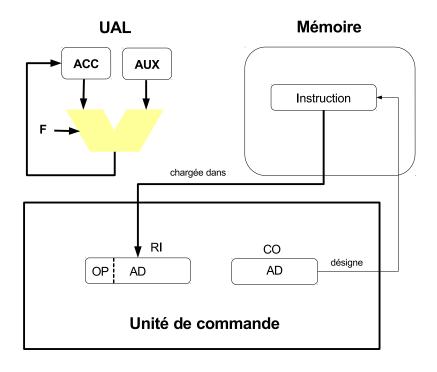

L'étape suivante est d'une importance capitale : elle va consister à introduire un nouvel élément qui va se charger de l'enchaînement automatique de la suite des calculs intermédiaires : l'unité de commande.

La mémoire va alors jouer un nouveau rôle : non seulement elle enregistre les résultat des calculs intermédiaires mais elle va aussi devoir enregistrer la suite des opérations à effectuer.

Cette suite d'opérations va être codée de façon à ce que l'unité de commande puisse les réaliser.

C'est la naissance de la programmation.

C'est en 1834, que Charles Babbage <sup>13</sup> pendant le développement d'une machine à calculer destinée au calcul et à l'impression de tables mathématiques (machine à différences) eut l'idée d'y incorporer des cartes du métier Jacquard, dont la lecture séquentielle donnerait des instructions et des données à sa machine.

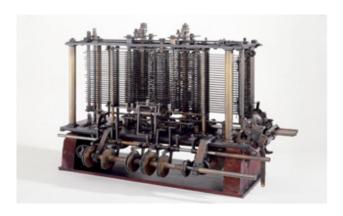

Par la suite il conçut une machine plus générale : la machine analytique <sup>14</sup> (Figure 7, page 11) qu'il ne put jamais réaliser faute de crédits, mais il passera le reste de sa vie à la concevoir dans les moindres détails et à en construire un prototype. Un de ses fils en construira l'unité centrale (appelée le moulin) et l'imprimante en 1888 et fit une démonstration réussie de calcul de tables à l'académie royale d'astronomie en 1908.

#### Le premier programme informatique

En octobre 1842, paraît en français, dans un journal suisse, une des-

<sup>13.</sup> https://fr.wikipedia.org/wiki/Charles\_Babbage

<sup>14.</sup> https://fr.wikipedia.org/wiki/Machine\_analytique

FIGURE 7: La machine analytique (1871)

cription de la machine analytique de Babbage <sup>15</sup> réalisée par le général mathématicien italien Federico Luigi Ménabréa <sup>16</sup>, en collaboration avec Ada Lovelace <sup>17</sup>, qui a un bon niveau de français.

Elle ajouta à cet article plusieurs notes, l'une d'elle mentionnant un véritable algorithme très détaillé pour calculer les nombres de Bernoulli avec la machine. Ce programme est considéré comme le premier véritable programme informatique au monde.

Elle a également émis, pour la première fois, l'idée que des machines à calculer pouvaient traiter des informations autres que des nombres :

« Beaucoup de personnes [...] s'imaginent que parce que la Machine fournit des résultats sous une forme numérique, alors la nature de ses processus doit être forcément arithmétique et numérique, plutôt qu'algébrique ou analytique. Ceci est une erreur

La Machine peut arranger et combiner les quantités numériques exactement comme si elles étaient des lettres, ou tout autre symbole général; en fait elle peut donner des résultats en notation algébrique, avec des conventions appropriées »

#### Et même composer de la musique :

« La machine pourrait composer de manière scientifique et élaborée des morceaux de musique de n'importe quelle longueur ou degré de complexité »

$<sup>15. \ \, \</sup>text{http://www.bibnum.education.fr/sites/default/files/babage-menabrea-texte-final.pdf}$

<sup>16.</sup> https://fr.wikipedia.org/wiki/Luigi\_Federico\_Menabrea

<sup>17.</sup> https://fr.wikipedia.org/wiki/Ada\_Lovelace

Un nouveau schéma voit alors le jour, qui va servir de modèle à tous les développements ultérieurs (Figure 8, page 12).

FIGURE 8: L'ordinateur

#### 1.9 Les machines électromécaniques

On n'observera pas de modifications du schéma précédent, mais la fabrication des machines y gagnera en simplicité, en efficacité, en fiabilité et surtout en puissance de calcul.

On attribue généralement à l'ingénieur allemand Konrad Zuse <sup>18</sup> le premier calculateur conçu en 1936 avec mémoire et unité de commande, utilisant l'énergie électrique et le système binaire : le Z1. Par la suite, en 1937 il conçoit le Z3 utilisant pour la première fois la représentation des nombres réels en virgule flottante. Enfin, il fonde aussi le premier langage de haut niveau nommé Plankalkül <sup>19</sup> qu'il ne put utiliser faute de spécifications précises et d'une machine capable de le supporter. Ce langage resta ignoré de tous jusqu'à sa publication en 1972, plus de vingt ans après la sortie du Fortran <sup>20</sup> en 1954. Il ne fut opérationnel qu'en 2000 lorsqu'une équipe de l'université libre de Berlin développa une implémentation à titre historique.

A la même époque, en 1938, l'américain Claude Shannon <sup>21</sup> soutient son mémoire de maîtrise à l'Université du Michigan. Il y expose comment utiliser l'algèbre de Boole pour y construire des machines à calculer à base de commutateurs et de relais. Suivront alors de nombreuses réalisations fondées sur ces principes.

<sup>18.</sup> https://fr.wikipedia.org/wiki/Konrad\_Zuse

<sup>19.</sup> https://fr.wikipedia.org/wiki/Plankalkul

<sup>20.</sup> https://fr.wikipedia.org/wiki/Fortran

<sup>21.</sup> https://fr.wikipedia.org/wiki/Claude\_Shannon

# 1.10 L'ordinateur : machine électronique universelle

L'apparition de l'électronique va conduire à un développement spectaculaire, non sur le plan des principes, mais sur celui de la technologie; l'ensemble des calculs pouvant être effectués par ces machines s'étend au fur et à mesure de la croissance de leur complexité. La question posée est alors celle-ci : peut on perfectionner les machines à calculer au point de pouvoir TOUT calculer avec elles? C'est à cette question nouvelle et essentielle que vont répondre, la même année (1936) deux chercheurs : l'anglais Alan Turing <sup>22</sup> et l'américain Alonzo Church <sup>23</sup> son directeur de thèse à l'université de Princeton <sup>24</sup>.

La réponse tient en deux propositions simples :

- 1. On peut montrer qu'il existe des nombres et des fonctions NON calculables.

- 2. Il est possible de construire des machines calculant TOUT ce qui est calculable et ces machines ont toutes une puissance de calcul équivalente <sup>25</sup>: cette proposition est une thèse appelée « thèse de Church-Turing » <sup>26</sup> qui ne peut être démontrée, dans la mesure où on ne peut pas prouver la non existence de machines de puissance supérieure.

Le premier ordinateur fonctionnant en langage binaire fut le  $Colossus^{27}$ , conçu lors de la Seconde Guerre Mondiale; il n'était pas Turing-complet bien qu'Alan Turing ait travaillé au projet. À la fin de la guerre, il fut démonté et caché à cause de son importance stratégique.

L'ENIAC  $^{28}$ , mis en service en 1946, est le premier ordinateur entièrement électronique construit pour être Turing-complet.

Pendant ce projet (en juin 1945 un an avant la démonstration de l'ENIAC) est publié un article fondateur : First Draft of a Report on the  $EDVAC^{29}$  par John von Neumann donnant les bases de l'architecture utilisée dans la quasi totalité des ordinateurs depuis lors. Dans

<sup>22.</sup> https://fr.wikipedia.org/wiki/Alan\_Turing

<sup>23.</sup> https://fr.wikipedia.org/wiki/Alonzo\_Church

<sup>24.</sup> https://fr.wikipedia.org/wiki/Universit%C3%A9\_de\_Princeton

<sup>25.</sup> Dans le sens où toute fonction calculable par l'une est calculable par les autres. On qualifie alors ces machines de «Turing-complète» (https://fr.wikipedia.org/wiki/Turing-complet).

<sup>26.</sup> https://journals.openedition.org/philosophiascientiae/769

<sup>27.</sup> https://fr.wikipedia.org/wiki/Colossus\_(ordinateur)

<sup>28.</sup> https://fr.wikipedia.org/wiki/ENIAC

$<sup>29. \ \</sup>mathtt{https://www.wiley.com/legacy/wileychi/wang\_archi/supp/appendix\_a.pdf}$

cet article Von Neumann veut concevoir un programme enregistré et programmé dans la machine.

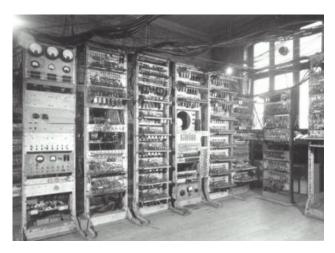

La première machine correspondant à cette architecture, dite depuis architecture de von Neumann, ne fut pas l'EDVAC <sup>30</sup> (Figure 9, page 14) qui ne sera livré qu'en Aout 1949, mais une machine expérimentale la *Small-Scale Experimental Machine* (SSEM ou "baby") construite à Manchester en juillet 1948 <sup>31</sup>.

Il est intéressant de noter que l'ENIAC fut conçue à l'IAS <sup>32</sup> contre l'avis entre autres d'Albert Einstein et de Kurt Gödel, ces deux éminents membres de l'institut considérant que cette coûteuse réalisation n'apporterait aucune contribution à la science <sup>33</sup>. L'obstination de John von Neumann puisa son énergie dans un anticommunisme fortement encouragé par le gouvernement américain, en pleine période de guère froide, son principal argument en faveur de la construction de la machine étant de gagner la course engagée entre russes et américains pour la fabrication de la future arme nucléaire.

FIGURE 9: L'EDVAC (1949)

#### 1.11 Le microordinateur

L'ENIAC et ses successeurs étaient fabriqués avec des circuits électroniques à base de lampes à vide, de taille importante, à forte consommation d'énergie et compte tenu de leur grand nombre le TMBF  $^{34}$  de

<sup>30.</sup> https://fr.wikipedia.org/wiki/Electronic\_Discrete\_Variable\_Automatic\_Computer

$<sup>31.\ \</sup>mathtt{https://fr.wikipedia.org/wiki/Small-Scale\_Experimental\_Machine}$

<sup>32.</sup> https://fr.wikipedia.org/wiki/Institute\_for\_Advanced\_Study

<sup>33.</sup> Le vrai paradis de Platon - John L. Casti - 2005 - Le Pommier

<sup>34.</sup> Temps Moyen de Bon Fonctionnement

l'ordinateur ne dépassait pas quelques heures.

Ce type d'ordinateur constitue ce qu'on appelle généralement la première génération (1946-1956).

L'arrivée du transistor en 1947 va considérablement modifier la donne. Tout comme les lampes à vide il va se comporter comme un interrupteur, mais à moindres coût, taille et consommation d'énergie. Les ordinateurs de ce type constituent la seconde génération (1956-1963).

D'abord utilisé comme simple composant sur des circuits imprimés dans les années 60, il va se miniaturiser pour se fondre au sein de circuits intégrés (dont le premier fut conçu en 1958) de taille de plus en plus réduite au point d'être appelé « puce électronique ». Au début, ce sont les mémoires qui constituent les premières puces. Elles sont d'abord utilisées au sein de mécanismes électroniques classiques. Ces ordinateurs constituent la troisième génération (1963-1971).

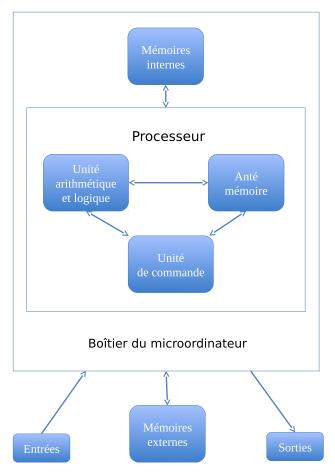

Puis, ce sera au tour de l'unité arithmétique et logique et de l'unité de commande de se fondre dans un circuit intégré qu'on appellera le microprocesseur dont le premier exemplaire fut créé en 1971 par la société Intel.

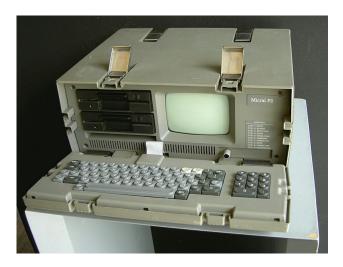

Enfin l'intégration de cet ensemble et des composants permettant de lui connecter des dispositifs d'entrée et de sortie dans un seul boîtier donnera naissance au microordinateur (Figure 10, page 16).

La question de savoir qui a créé le premier micro-ordinateur est source de controverse et dépend du degré d'intégration choisi. Selon certaines sources la première machine vendue toute assemblée prête à l'emploi, serait le Micral  $^{35}$  conçu en 1972 par l'entreprise française R2E  $^{36}$  (Figure 11, page 17).

Il s'agit d'un des tous premiers ordinateurs de la quatrième génération (depuis 1971).

## 1.12 L'ordinateur quantique

Selon la loi de Moore <sup>37</sup> la densité des composants électroniques sur une puce suivrait une croissance exponentielle à raison d'un doublement tous les 2 ans. Cette conjecture énoncée en 1965 a été confirmée dans les faits entre 1970 et 2000.

Cependant depuis cette dernière date des limites infranchissables semblent être atteintes dues à des phénomènes physiques telles que la sensibilité aux rayonnements extérieurs et en dernier ressort à des effets quantiques.

<sup>35.</sup> https://fr.wikipedia.org/wiki/Micral

<sup>36.</sup> https://fr.wikipedia.org/wiki/R2E

<sup>37.</sup> https://fr.wikipedia.org/wiki/Loi\_de\_Moore

FIGURE 10: Le microordinateur

En effet, lorsque la taille des composants de base atteint l'échelle atomique, ceux ci ne se comportent plus comme le prévoient les lois de la physique classique mais obéissent à celles plus surprenantes de la physique quantique.

L'idée vient alors de construire des ordinateurs avec des composants quantiques  $^{38}$ . L'un des premiers prototypes a été construit à l'université d'Innsbruck en 2011  $^{39}$  (cf. Figure 12 *Prototype d'ordinateur quantique* page 18).

Outre l'avantage de l'extrême densité que l'on peut en tirer, le comportement quantique de ces composants permet de tirer parti de

<sup>38.</sup> cf. Leçons sur l'informatique - Richard Feynman - Odile Jacob Sciences 1966 - Leçon n°6 p251-284

<sup>39.</sup> https://www.futura-sciences.com/sciences/dossiers/physique-ordinateur-quantique-552/page/7/

FIGURE 11: Le Micral (1972)

propriétés fort intéressantes telles que la superposition d'états <sup>40</sup>.

On conçoit alors qu'un ordinateur quantique puisse posséder une puissance bien supérieure au plus puissant des ordinateurs classiques. On a pu se demander si une telle puissance ne permettrait pas de calculer des fonctions non calculables au sens de la thèse de Church-Turing. La réponse à cette question est négative.

En revanche, il existe des problèmes pour lesquels nous ne connaissons pas d'algorithme polynomial pour machine classique mais des algorithmes polynomiaux pour machines quantiques : c'est par exemple le cas de la factorisation entière en nombre premiers (algorithme de Shor <sup>41</sup>)

Deux grands obstacles restent encore à franchir avant de disposer chez soi de son ordinateur quantique :

- La taille gigantesque et le coût exorbitant estimé actuellement à plusieurs millions d'Euros pour quelques qu-octets (octets quantiques : ensemble de huit qu-bits)

- La conception d'algorithmes quantiques dont on ne connaît aujourd'hui que quelques rares exemples

<sup>40.</sup> https://fr.wikipedia.org/wiki/Qubit

<sup>41.</sup> https://fr.wikipedia.org/wiki/Algorithme\_de\_Shor

FIGURE 12: Prototype d'ordinateur quantique

# 2 Architecture de base dite de "Von Neumann"

#### 2.1 Introduction

Le schéma (cf. Figure 8 L'ordinateur page 12) nous fournit les éléments centraux de l'architecture générale des ordinateurs, définie en 1945 par John Von Neumann.

Actuellement <sup>42</sup>, c'est toujours avec cette architecture que sont construits tous les ordinateurs, du nano-processeur (que l'on trouve par exemple dans une machine à laver) au super-ordinateur (calcul intensif).

#### Osons un parallèle

Tout comme le cycle de Carnot <sup>43</sup> fut le premier modèle des moteurs à explosion, la machine de Turing fut le premier modèle des ordinateurs.

Tout comme le cycle de Carnot a donné naissance au modèle des moteurs à explosion actuels, (via le cycle de Beau de Rochas pour les moteurs à essence 44 et au cycle Diesel 45 pour les moteurs ... Diesel), l'architecture de Von Neumann a donné naissance au modèle des ordinateurs actuels.

Aujourd'hui, malgré toutes les avancées techniques indéniables, ces modèles sont toujours d'actualité!

<sup>42.</sup> en 2020

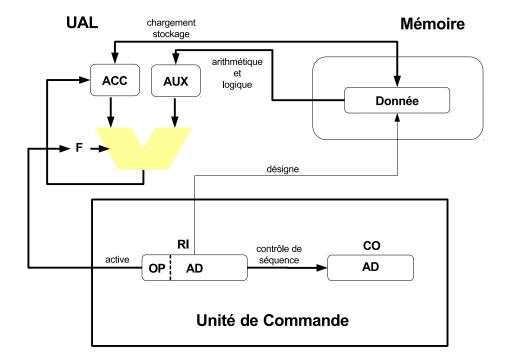

On retiendra les composants suivants :

La mémoire réalisant la fonction de stockage L'Unité Arithmétique et Logique réalisant les calculs élémentaires L'Unité de Commande réalisant l'enchaînement des instructions

On désigne généralement par *processeur* l'ensemble de l'unité arithmétique et logique et de l'unité de commande.

#### 2.2 La mémoire

Elle est composée de cellules.

Une cellule est référencé par son *adresse*, qui est en général un entier représentant le rang de son emplacement dans la mémoire. Il en résulte qu'il est assez naturel d'organiser l'ensemble de ces cellules comme un grand tableau. Si l'on désigne par M le nom de ce tableau, l'adresse X d'une cellule peut être vue comme l'indice de cette cellule dans le tableau M (cf. Figure 13 *La mémoire* page 21).

M[X] est alors l'identifiant de cette cellule dans ce tableau.

Par la suite on utilisera la notation abrégée [X] pour désigner cet identifiant.

Généralement la taille de ce tableau est une puissance de deux. Une adresse est alors constituée d'une suite fixe d'éléments binaires. La longueur de cette suite est appelé le *champ d'adressage* de la mémoire.

Le contenu d'une cellule est exprimé par une chaîne de bits qui peut représenter :

- une donnée : nombre, caractère, couleur, son, etc ...

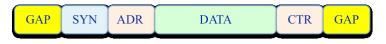

- une instruction élémentaire du processeur