# Scaling of AlN/GaN HEMT for millimeter-wave power applications

K. Harrouche, Riad Kabouche, Malek Zegaoui, F Medjdoub

## ▶ To cite this version:

K. Harrouche, Riad Kabouche, Malek Zegaoui, F Medjdoub. Scaling of AlN/GaN HEMT for millimeter-wave power applications. 43rd Workshop on Compound Semiconductor Devices and Integrated Circuits, WOCSDICE 2019, Jun 2019, Cabourg, France. hal-02356889

# HAL Id: hal-02356889 https://hal.science/hal-02356889v1

Submitted on 9 Nov 2019

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Scaling of AlN/GaN HEMT for millimeter-wave power applications

K. Harrouche<sup>1\*</sup>, R. Kabouche<sup>1</sup>, M. Zegaoui <sup>1</sup> and F. Medjdoub<sup>1\*</sup>

<sup>1</sup> CNRS-IEMN, UMR8520, Av. Poincaré, 59650 Villeneuve d'Ascq, France \* kathia.harrouche.etu@univ-lille.fr farid.medjdoub@univ-lille.fr

#### **Abstract**

In this paper, we report on AlN/GaN HEMTs for high frequency applications. Various gate lengths have been studied as a function of the gate-drain distance in order to analyze the impact on the DC, RF and power performances. Electrical characteristics of this structure for 110 nm gate length show a maximum drain current of 1.2 A/mm, an extrinsic transconductance Gm of 400 mS/mm and a F<sub>T</sub>/F<sub>max</sub> of 63/300 GHz at a drain bias voltage  $V_{DS}$  = 20V. An excellent electron confinement with a low leakage current below 10 µA/mm is achieved. Furthermore, a breakdown voltage of 55 V for GD0.5 and up to 140 V for GD2.5 are observed when using a 110 nm short gate length. Large signal characteristics at 40 GHz reveal a state-of-the-art combination of power added efficiency (PAE) (50%) with an output power density (Pout) of 3.6 W/mm at  $V_{DS} = 20 \text{ V}$  in continuous wave mode (CW) and PAE of 50% associated with a Pout of 8.3 W/mm at 40V in pulsed mode. It can be noticed that the 110 nm gate length GD0.5 showed no degradation after semi-on robustness tests and large signal measurements up-to  $V_{DS}$  = 20V.

#### Introduction

Gallium Nitride (GaN)-based RF power devices have made substantial progress in the last decade, which will enable new applications such as military wireless communication and SATCOM. Indeed, applications operating at high frequency need compact systems, for which the power-added-efficiency (PAE) is a critical parameter. That is why, achieving both high PAE and output power density (Pout) in the millimetrewave range represents currently one of the key goals for the GaN technology. High Electron Mobility Transistors (HEMT) on SiC have already demonstrated attractive efficiencies up to Ka band [1]-[3] but limited data have been reported so far in the Q band [4] and above. To obtain very high frequency performance, it is necessary to optimize wisely the structure configuration especially the barrier thickness [5]. In this paper, we used an ultrathin barrier layer and investigated the impact of the gate-drain distance and the gate length with the aim of reaching high RF performances in the Q band and above.

#### **Experimental**

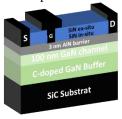

The epitaxial layer structure is based on an AlN/GaN heterostructure grown by metal organic chemical vapor deposition (MOCVD) on 4 in. SiC substrates. Figure 1 shows the cross section of the HEMT structure consisting in an AlN transition layer, a C-doped GaN buffer layer followed by a 100 nm GaN channel and a 3.0 nm ultrathin AlN barrier layer. The HEMT was capped with an in-situ SiN layer both as early passivation as well as to reduce trapping effects. Room-temperature Hall measurements showed a high electron sheet concentration of  $1.9x10^{13}~\text{cm}^{-2}$  with a mobility of 965 cm²/Vs. A Ti/Al/Ni/Au metal stack annealed at 850°C

has been used to form the source-drain ohmic contacts directly on top of the barrier by etching the in-situ  $Si_3N_4$  layer. Then, Ni/Au T-gates with various lengths were defined by e-beam lithography. The SiN underneath the gate was fully removed by SF6 plasma etching through the e-beam lithography. Finally, 200 nm PECVD  $Si_3N_4$  was deposited as final passivation.

**Figure 1.** Schematic cross section of the fabricated AlN/GaN-on-SiC HEMTs (left) and FIB view of a 110 nm T-gate (right)

#### Results and discussion

#### DC characteristics:

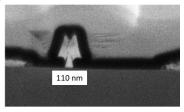

DC measurements have been carried out with a Keysight A2902A static modular and source monitor. Figures 2 and 3 show the output and transfer characteristics as well as the extrinsic transconductance.

The gate source voltage was swept from -4 V to +2 V with a step of 1 V. A maximum drain current  $I_{Dmax}$  is about 1.2 A/mm and 1.1 A/mm for GD0.5 = 0.5  $\mu$ m and GD1.5 = 1.5  $\mu$ m respectively.

**Figure 2**. Output characteristics of an AlN/GaN HEMT with  $L_g = 110 \text{ nm } 2x25 \text{ } \mu\text{m}$  devices with GD0.5 (a) and GD1.5 (b).

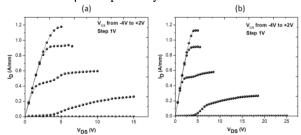

**Figure 3.** Transfer characteristics (a) and extrinsic transconductance (b) of an AlN/GaN HEMT  $2x25~\mu m$  devices with a gate-drain distance of  $0.5~\mu m$  (gd0.5) as a function of various gate lengths

A pinch-off voltage  $V_{TH}=$  -2 V (shown in Figure 3) is observed for the different gate lengths with a drain leakage current below 20  $\mu\text{A/mm}$  which reflects the absence of short channel effects. Furthermore, a decrease of the extrinsic transconductance as a function of the gate length has been observed from 400 mS/mm for  $L_g=110$  nm to 360 mS/mm for  $L_g=270$  nm. The transconductance can be significantly optimized by reducing the access resistances as the contact resistance is as high as 0.45  $\Omega$ .mm for these devices.

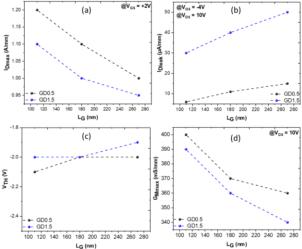

Figure 4 shows some basic DC parameters as a function of the gate length for GD0.5 and GD1.5. As expected, a drop of  $I_{\rm Dmax}$  and  $G_{\rm Mmax}$  are observed due to the increase of the gate-drain distance and the gate length. As mention earlier, the leakage current shown in Figure 4.b, is still below 50  $\mu A/mm$  for all gate lengths and GD, which reflects the high material and processing quality.

**Figure 4.** I<sub>Dmax</sub> (a), I<sub>Dleak</sub> (b), V<sub>TH</sub> (c), and G<sub>Mmax</sub> (d) as a function of gate length for GD0.5 and GD1.5

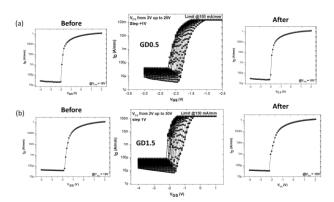

**Figure 5.** Semi-On robustness test up to  $V_{DS} = 20V$  of a 2x25  $\mu$ m GD0.5 (a) and up to  $V_{DS} = 30V$  GD1.5 (b) with  $L_G = 110$  nm.

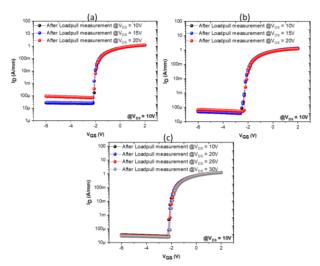

A semi-on robustness test has been performed on GD0.5 and GD1.5 with  $L_{\rm g}=110$  nm. The maximum current density is limited to 150 mA/mm and the  $I_{\rm D}V_{\rm D}$  transfer characteristics are swept from  $V_{\rm DS}=2$  V up to 20V for GD0.5 and up to 30V for GD1.5. The initial transfer characteristic is then compared to the one after the stress. Even for the short gate length of 110 nm, we observed a good electron confinement and no degradation during

and after the semi-on robustness test as shown Figure 5. The excellent robustness can be attributed to the absence of parasitic surface leakage resulting from the in-situ SiN cap layer.

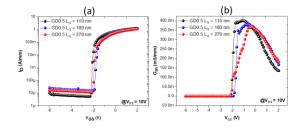

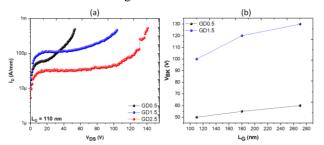

The breakdown voltage at  $V_{GS} = -4V$  is shown in Figure 6 for various GD and  $L_g$ . It can be noticed that a leakage current still below 500  $\mu$ A/mm is observed (figure 6.a) for short GD. The breakdown voltage scales well versus GD with for instance 50V for GD0.5 to more than 100V for GD1.5 as shown figure 6.b.

**Figure 6.** Breakdown Voltage characteristics of an AlN/GaN HEMT  $2x50 \mu m$  for various GD with  $L_g = 110 \text{ nm}$  (a), and for various  $L_g$  with GD0.5 and GD1.5 (b).

#### **Small signal characteristics:**

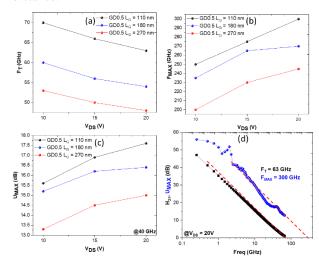

The S-parameters have been measured from 250 MHz to 67 GHz with a Rhode and Schwarz ZVA67GHz network analyser as shown in Figure 7. As expected, the current gain extrinsic cut-off frequency (F<sub>T</sub>) decreases as a function of V<sub>DS</sub> and L<sub>g</sub> (shown in figure 7a). There is a large room for improvement by both reducing the contact resistances and the gate length. The maximum oscillation frequency (F<sub>max</sub>) and unilateral power gain (U<sub>max</sub>) increase as function of V<sub>DS</sub> (figure 7b and 7c), which in turn confirm the absence of short channel effects for the designs that have been used. F<sub>T</sub>/F<sub>max</sub> of 63/300 GHz are achieved at V<sub>DS</sub>= 20V for a GD0.5 with L<sub>g</sub>=110 nm (figure 7d). It can be pointed out that the power gain is in excess of 17 dB at 40 GHz for the shortest design. The F<sub>max</sub>/F<sub>T</sub> ratio close to 5 is explained by the highly favourable aspect ratio: gate length / gate-to-channel distance.

**Figure 7.** Small signal characteristics of an AlN/GaN HEMT  $2x25 \mu m$  GD0.5 for various gate lengths:  $F_T(a)$ ,  $F_{max}(b)$ ,  $U_{max}(c)$  and  $F_T/F_{max}$  at 20V with  $L_g$ = 110 nm (d)

#### Large signal characteristics:

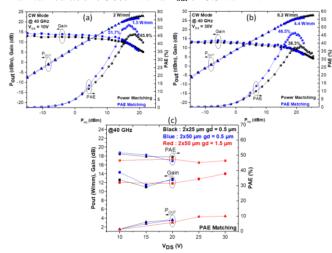

Large signal characterizations have been carried out at 40 GHz on a nonlinear vector network analyzer system (Keysight Network Analyser: PNA-X, N5245A-NVNA) capable of on-wafer large signal device characterization up to the Q-band in continuous and pulsed mode. Further details of this specific power bench can be found in [6]. Figures 8a and 8b show CW power performances of 2x50  $\mu$ m with L<sub>g</sub> = 110 nm for GD0.5 at V<sub>DS</sub> = 10V and GD1.5 at V<sub>DS</sub> = 30V, respectively. A high saturated power (P<sub>out</sub>) of 1.5 W/mm associated to power added efficiency (PAE) of 51.7% at V<sub>DS</sub> = 10V for GD0.5. For GD1.5 and at V<sub>DS</sub> = 30V, a P<sub>out</sub> of 4.4 W/mm associated to a PAE of 46.3% has been achieved. It can be stressed out that in power matching a P<sub>out</sub> of 6.2 W/mm is reached.

Figure 8c depicts the PAE,  $P_{out}$  and gain of  $2x25~\mu m$  GD0.5,  $2x50~\mu m$  GD0.5 and GD1.5 as a function of  $V_{DS}$  (PAE matching) at 40 GHz. For all device design, the PAE remains above 45 % up to  $V_{DS}=20V$  and up to 30V when using a gate-drain distance of 1.5  $\mu m$ . This capability of maintaining a high PAE above 45% up to  $V_{DS}=30V$  under high power density sets a new performance benchmark at this frequency band.

An increasing evolution of  $P_{OUT}$  is observed up to 3.5 W/mm at  $V_{DS} = 20V$  for GD0.5 devices and 4.4 W/mm at  $V_{DS} = 30V$  for GD1.5 devices. Furthermore, the power gain is maintained above 11 dB in all cases up to  $V_{DS} = 30V$ . In pulsed mode a PAE of 58% combined to a  $P_{out}$  of 3.8 W/mm at 20V is reached. At  $V_{DS} = 40V$  the PAE is maintained above 50% with a  $P_{out}$  of 8.3W/mm.

**Figure 8.** CW power performances of an AlN/GaN HEMT  $2x50~\mu m$  with  $L_g=110~nm$  for GD0.5 at  $V_{DS}=10~V$  (a), GD1.5 at  $V_{DS}=30~V$  (b) and CW output power density (triangle), PAE (circle) and Small signal Gain (square) vs.  $V_{DS}$  at 40 GHz (c).

Despite the short gate length and GD, we observed no degradation of the devices up to  $V_{DS} = 20V$  for GD0.5 and  $V_{DS} = 30V$  for GD1.5 as seen in Figure 9. The excellent robustness is attributed to the high quality of the epitaxial structure and the optimized processing.

**Figure 9.** Transfer characteristics after large signal measurements with Lg = 110 nm for an AlN/GaN HEMT 2x25  $\mu$ m GD0.5 (a) 2x50  $\mu$ m GD0.5 (b) and 2x50  $\mu$ m GD1.5 (c).

#### **Conclusions**

We have developed high frequency AlN/GaN HEMTs grown on SiC substrate. We showed that with a 110 nm gate length, high frequency performance ( $F_T/F_{max}$  of 63/300 GHz) can be reached at  $V_{DS}=20V$ . The optimized AlN/GaN HEMT structure enabled to deliver high power density together with state-of-the-art PAE > 50% at  $V_{DS}=10V$  and > 45% at  $V_{DS}=30V$  in CW mode at 40 GHz. This achievement is mainly attributed to the optimization of both material, design as well as processing quality enabling namely a high electron confinement together with reduced short channel effects under high electric field.

Preliminary CW results at 94 GHz on the same devices already demonstrated a combination of PAE about 14.5% and an outstanding  $P_{out}$  of 4 W/mm at  $V_{DS} = 20 \text{ V}$ .

#### Acknowledgments

This work was supported by the French RENATECH network, and the French Defense Procurement Agency (DGA) under Project EDA-EuGaNiC and Contract FUI-VeGaN.

## References

- [1]. P. Saad, H. M. Nemati, M. Thorsell, K. Andersson, and C. Fager, "An inverse class-F GaN HEMT power amplifier with 78% PAE at 3.5 GHz," Eur. Microw. Week 2009, EuMW 2009 Sci. Prog. Qual. Radiofreq. Conf. Proc. - 39th Eur. Microw. Conf. EuMC 2009, no. October, pp. 496–499, 2009.

- [2]. J. S. Moon et al., ">70% power-added-efficiency dual-gate, cascode GaN HEMTs without harmonic tuning," IEEE Electron Device Lett., vol. 37, no. 3, pp. 272–275, 2016.

- [3]. K. Takagi, S. Takatsuka, Y. Kashiwabara, and S. Teramoto, "Ku-Band AlGaN / GaN-HEMT with over 30 % of PAE," Engineering, pp. 457–460, 2009.

- [4]. Comparison of C-doped AlN/GaN HEMTs and AlN/GaN/AlGaN double heterostructure for mmW applications" R. Kabouche, J. Derluyn, R. Püsche, S. Degroote, M. Germain, R. Pecheux, E. Okada, M. Zegaoui, and F. Medjdoub, European Microwave Week, Madrid, 2018.

- [5]. F. Medjdoub et al., "Low on-resistance high-breakdown normally off AlN/GaN/AlGaN DHFET on si substrate," *IEEE Electron Device Lett.*, vol. 31, no. 2, pp. 111–113, 2010.

- [6]. R. Kabouche, E. Okada, E. Dogmus, A. Linge, M. Zegaoui, and F. Medjdoub, "Power Measurement Setup for On-Wafer Large Signal Characterization Up to Q-Band," IEEE Microw. Wirel. Components Lett, vol. 27, no. 4, pp. 419–421, 2017.