# Superlattice GaN-on-silicon heterostructures with low trapping in 1200 V

Alaleh Tajalli, Matteo Meneghini, Gaudenzio Meneghesso, Riad Kabouche, Idriss Abid, Malek Zegaoui, Roland Püsche, Joff Derluyn, Stefan Degroote, Marie Germain, et al.

## ▶ To cite this version:

Alaleh Tajalli, Matteo Meneghini, Gaudenzio Meneghesso, Riad Kabouche, Idriss Abid, et al.. Superlattice GaN-on-silicon heterostructures with low trapping in 1200 V. 43rd Workshop on Compound Semiconductor Devices and Integrated Circuits, WOCSDICE 2019, Jun 2019, cabourg, France. hal-02356881

# HAL Id: hal-02356881 https://hal.science/hal-02356881

Submitted on 9 Nov 2019

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### Superlattice GaN-on-silicon heterostructures with low trapping in 1200 V

<u>A. Tajalli</u><sup>1</sup>\*, M. Meneghini<sup>1</sup>, R. Kabouche<sup>2</sup>, I. Abid<sup>2</sup>, M. Zegaoui<sup>2</sup>, R. Püsche<sup>3</sup>, J. Derluyn<sup>3</sup>, S. Degroote<sup>3</sup>, M. Germain<sup>3</sup>, F. Medjdoub<sup>2</sup>, G. Meneghesso<sup>1</sup>

<sup>1</sup> Department of Information Engineering, University of Padova, Italy

<sup>2</sup> IEMN - CNRS, UMR8520, Av. Poincaré, 59650 Villeneuve d'Ascq, France

<sup>3</sup>EpiGaN, Kempische Steenweg 293, 3500 Hasselt, Belgium

\* tajalli@dei.unipd.it

#### Abstract

The aim of this work is to investigate the role of the epitaxial structure on the low trapping effects of GaN-on-silicon heterostructures use for power application. Structures with and without superlattices (SL) are analysed. In particular, it is shown that the insertion of SL into the buffer layers allows pushing the vertical breakdown voltage above 1200 V without generating additional trapping effects as compared to a more standard GaN-based epi-structure using similar total buffer thickness. A low trapping effect down to -1.2 kV has been observed with substrate ramp measurements. Indeed, we demonstrated that a structure with SL shows a reduction in the trapping effects with high vertical breakdown.

#### Introduction

GaN high-electron-mobility transistors (HEMTs) on silicon (Si) substrate has been proved as excellent materials for power applications due to the large bandgap, high breakdown field strength, and high electron saturation velocity [1][2]. Recently significant efforts have been developed in order to find optimum GaN-on-silicon epitaxial structures enabling outstanding DC performances beyond 1 kV with low trapping effects [3][4]. Toward this end, in this work we demonstrate a vertical breakdown voltage above 1200 V based on superlattice buffer layers without generating additional trapping effects as compared to a more standard step-graded GaN-based epi-structure. Substrate ramp measurements are used to obtain the charge trapping effect into the buffer structure and the results are compared to a reference device at various temperature (up to  $T=150^{\circ}C$ )[5].

#### Experimental

For this study, the GaN-on-silicon heterostructures are manufactured by EpiGaN targeting 1200 V power applications. The step-graded buffer structure has a 5.5  $\mu$ m total thickness (**process B**) while the structure based on superlattices (SL) has a total thickness of 5  $\mu$ m (**process A**). The breakdown voltage and the trapping effects in the buffer have been studied through a series of substrate bias ramp measurements. The analyses have been done also at different temperature in order to understand the different leakage current level.

#### **Results and discussion**

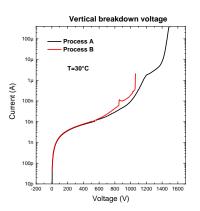

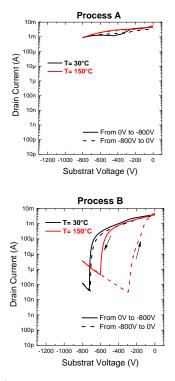

Vertical breakdown voltages measurements have been performed on both devices. A vertical breakdown of a 1300 V at 1  $\mu$ A is reached for the structure with SL as compared to a 1000 V for the more standard structure (Fig. 1). Furthermore, it can be noticed that a low vertical leakage current is observed up to a temperature of 150°C for the SL heterostructure. The leakage current increase, up to a 150°C, is significantly lower than the reference heterostructure without SL. Fig. 2 shows the leakage current on process A, B at different temperature from 30°C to 150°C, in which the vertical leakage current increases with temperature.[6][7].

Figure 1. Vertical breakdown voltage at room temperature for heterostructure with (process A) and without (process B) SL.

Substrate ramp analysis is a technique to get the buffer traps information in the off-state condition. In order to study the buffer trapping effects, substrate ramp measurements have been carried out on both devices by ramping the bulk from 0 V down to -800 V in the off-state condition.

Figure 2. Vertical leakage current at different temperature for heterostructure with (process A) and without (process B) SL.

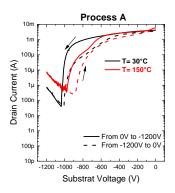

Fig. 3 reports the measurement at room and high temperature  $(T=150^{\circ}C)$  for process A and B. The reference heterostructure without SL shows low trapping effect down to a -800 V with a strong trapping activation starting from -900 V. However, the optimized SL buffer uniformly delivers state-of-the-art low trapping effects all the way down to -1200 V as shown in Fig. 4.

Moreover, electrical characterizations have been realized on  $2x50 \ \mu m$  transistors with a gate length of  $2 \ \mu m$  for several gate-drain distances (GD) for both structures. DC characteristics ID-VD and ID-VG reveal a low leakage current and an excellent pinch-off behaviour reflecting the absence of parasitic punch-through effect or gate leakage current.

Figure 3. Substrate ramp measurement on process A and B at room and high temperature.

Figure 4. Substrate ramp measurement on process A at room temperature and high temperature, down to -1.2 kV

#### Conclusion

In conclusion, it has been shown that a heterostructure with superlattices (SL) shows no temperature dependency to a substrate ramp and a low trapping effect even at high temperature. The measured results indicate that a proper buffer optimization along with the insertion of SL clears a way to GaN-on-silicon lateral power transistors operating at 1200 V with very low trapping effects.

#### Acknowledgments

Part of this work is funded by the Horizon2020 project Innovative Reliable Nitride based Power Devices and Applications (InRel-NPower).

#### References

- [1] H. Amano, Y. Baines, E. Beam, M. Borga, T. Bouchet, P. R. Chalker, M. Charles, K. J. Chen, N. Chowdhury, R. Chu, C. De Santi, M. M. De Souza, S. Decoutere, L. Di Cioccio, B. Eckardt, T. Egawa, P. Fay, J. J. Freedsman, L. Guido, O. Häberlen, G. Haynes, T. Heckel, D. Hemakumara, P. Houston, J. Hu, M. Hua, Q. Huang, A. Huang, S. Jiang, H. Kawai, D. Kinzer, M. Kuball, A. Kumar, K. B. Lee, X. Li, D. Marcon, M. März, R. McCarthy, G. Meneghesso, M. Meneghini, E. Morvan, A. Nakajima, E. M. S. Narayanan, S. Oliver, T. Palacios, D. Piedra, M. Plissonnier, R. Reddy, M. Sun, I. Thayne, A. Torres, N. Trivellin, V. Unni, M. J. Uren, M. Van Hove, D. J. Wallis, J. Wang, J. Xie, S. Yagi, S. Yang, C. Youtsey, R. Yu, E. Zanoni, S. Zeltner, and Y. Zhang, "The 2018 GaN power electronics roadmap," J. Phys. D. Appl. Phys., vol. 51, no. 16, p. 163001, Apr. 2018.

- [2] M. Meneghini, G. Meneghesso, and E. Zanoni, GaN Power Devices Materials, Applications and Reliability, Springer. 2017.

- [3] E. Dogmus, M. Zegaoui, and F. Medjdoub, "GaN-onsilicon high-electron-mobility transistor technology with ultra-low leakage up to 3000 V using local substrate removal and AlN ultra-wide bandgap," *Appl. Phys. Express*, vol. 11, no. 3, p. 034102, Mar. 2018.

- [4] A. Tajalli, A. Stockman, M. Meneghini, S. Mouhoubi, A. Banerjee, S. Gerardin, M. Bagatin, A. Paccagnella, E. Zanoni, M. Tack, B. Bakeroot, P. Moens, and G. Meneghesso, "Dynamic-ron control via proton irradiation in AlGaN/GaN transistors," in 2018 IEEE 30th International Symposium on Power Semiconductor Devices and ICs (ISPSD), 2018, pp. 92–95.

- [5] A. Stockman, M. Uren, A. Tajalli, M. Meneghini, B. Bakeroot, and P. Moens, "Temperature dependent substrate trapping in AlGaN/GaN power devices and the impact on dynamic ron," in 2017 47th European Solid-State Device Research Conference (ESSDERC), 2017, pp. 130–133.

- [6] M. Meneghini, P. Vanmeerbeek, R. Silvestri, S. Dalcanale, A. Banerjee, D. Bisi, G. Zanoni, Enrico. Meneghesso, and P. Moens, "Temperature-Dependent Dynamic RON in GaN-Based MIS-HEMTs: Role of Surface Traps and Buffer Leakage," *TED*, vol. 62, no. 3, 2015.

- [7] M. Meneghini, A. Tajalli, P. Moens, A. Banerjee, E. Zanoni, and G. Meneghesso, "Trapping phenomena and degradation mechanisms in GaN-based power HEMTs," *Mater. Sci. Semicond. Process.*, vol. 78, no. October, pp. 118–126, 2018.