# High Efficiency AlN/GaN HEMTs for Q-Band Applications with an Improved Thermal Dissipation

Riad Kabouche, Romain Pecheux, Kathia Harrouche, Etienne Okada, F Medjdoub, Joff Derluyn, Stefan Degroote, Marianne Germain, Filip Gucmann, Callum Middleton, et al.

# ▶ To cite this version:

Riad Kabouche, Romain Pecheux, Kathia Harrouche, Etienne Okada, F Medjdoub, et al.. High Efficiency AlN/GaN HEMTs for Q-Band Applications with an Improved Thermal Dissipation. International Journal of High Speed Electronics and Systems, 2019, 28 (01n02), pp.1940003. 10.1142/S0129156419400032. hal-02356733

HAL Id: hal-02356733

https://hal.science/hal-02356733

Submitted on 8 Dec 2020

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# HIGH EFFICIENCY ALN/GAN HEMTS FOR Q-BAND APPLICATIONS WITH AN IMPROVED THERMAL DISSIPATION $^{\ast}$

Riad Kabouche\*, Romain Pecheux, Kathia Harrouche, Etienne Okada, and Farid Medjdoub†

Institut d'Electronique, de Microélectronique et de Nanotechnologie, University Lille, Avenue Poincaré,

Villeneuve d'Ascq, France

\*riad.kabouche@ed.univ-lille1.fr; ‡farid.medjdoub@univ-lille.fr

Joff Derluyn, Stefan Degroote, Marianne Germain

EpiGaN company, Kempische Steenweg 293

Hasselt, Belgique

Filip Gucmann, Callum Middleton, James W. Pomeroy, Martin Kuball

H. H Wills Physics Laboratory, University of Bristol, BS8 1TL Bristol, United Kingdom

> Received Day Month Year Revised Day Month Year

In this paper, we demonstrate Q-band power performance of carbon doped AlN/GaN high electron mobility transistors (HEMTs) using a deep sub-micrometer gate length (120 nm). With a maximum drain current density  $I_D$  of 1.5 A/mm associated to a high electron confinement and an extrinsic transconductance  $g_m$  of 500 mS/mm, this structure shows excellent electrical characteristics. A maximum oscillation frequency  $f_{max}$  of 242 GHz has been observed As a result, a state-of-the-art combination at 40 GHz of output power density ( $P_{OUT} = 7$  W/mm) and power added efficiency (PAE) of 52% up to  $V_{DS} = 25V$  has been obtained. The achievement of such outstanding performance is attributed to the reduced thermal resistance ( $R_{TH}$ ) as compared to the commonly used double heterostructure by means of Raman thermography.

*Keywords*: High electron mobility transistors (HEMTs), Double heterostructure field effect transistor (DHFET), GaN, Raman thermography, output power density (P<sub>OUT</sub>), power added efficiency (PAE).

#### 1. Introduction

The requirements for the emerging wireless communication systems such as 5G significantly increases the need for compact solid-state high power amplification based on gallium nitride (GaN) material. Achieving both high power-added-efficiency (PAE) and output-power-density ( $P_{OUT}$ ) in the millimeter-wave range represents currently one of the key goals for the GaN technology. Indeed, higher PAE not only saves electrical power usage but also can reduce the size and cost of high power amplifiers (HPAs), due to the lower amount of heat dissipated. For instance, in space applications, the traveling wave tube amplifiers (TWTA) are still commonly used, because of the high PAE while delivering high  $P_{OUT}$ . Despite excellent PAE demonstrated so far with GaN devices up to

Ka band [1]-[5], a limited set of data in the Q band (40 GHz) and above are available. As shown by HRL laboratory [6],[7] the double heterostructure field effect transistor (DHFET) using an AlGaN back barrier allowed combining a high electron confinement with high frequency performance together with low trapping effects [8]-[14]. However, AlGaN alloys have the drawback to provide much lower thermal conductivity than the binaries GaN or AlN [15], which in turn causes an increase in the peak channel temperature during operation [16]. Compared to Fe doped GaN buffers, carbon-doped HEMT structures show lower memory effects [17], lower risk of diffusion and the elimination of contamination risks when used in Si CMOS-based foundries. That is why, this structure is widely used for high voltage power applications. In this work, a carbon-doped HEMT structure [19], using a 0.12 μm gate technology has been evaluated and compared to a DHFET [20] with the aim of pushing the bias operation in the millimeter-wave range while maintaining a reduced junction temperature.

#### 2. Device Fabrication

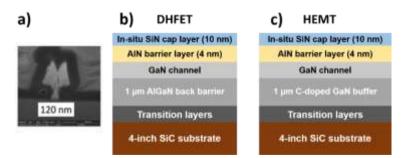

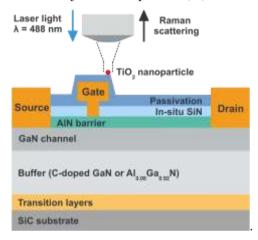

The AlN/GaN heterostructures were grown by metal organic chemical vapor deposition (MOCVD) on 4 in. SiC substrates. The HEMT structure consists of a transition layer to GaN, a 1  $\mu$ m-thick carbon-doped GaN buffer layer followed by a 150 nm thick un-doped GaN channel, a 4 nm ultrathin AlN barrier layer and a 10-nm-thick in situ  $S_{i3}N_4$  cap layer (Fig. 1). The in-situ SiN layer is used both as early passivation as well as to prevent strain relaxation [21]-[23]. The channel thickness has been chosen with respect to the trade-off between the electron confinement and the trapping effects. In the second structure called DHFET, the GaN buffer layer is replaced by a 1  $\mu$ m-thick  $Al_{0.08}Ga_{0.92}N$  layer as shown in Figure 1. Room temperature Hall measurements showed high electron sheet concentrations of  $1.8\times10^{13}$  and  $1.6\times10^{13}$  cm<sup>-2</sup> with an electron mobility of about 1100 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> in the HEMT and DHFET heterostructures, respectively. The device fabrication details can be found in [20]. Ohmic contact resistance (Rc) extracted from linear transmission line method (TLM) was as low as  $0.3~\Omega$ .mm for both heterostructures. A  $0.12~\mu$ m Ni/Au T-gate length was defined by e-beam lithography (see Fig. 1). The gate-source and gate drain spacing were  $0.3~\text{and}~2~\mu$ m, respectively, and the unit device width was 50  $\mu$ m.

Fig. 1. a) FIB view of the 0.12  $\mu m$  T-gate and schematic cross section of b) DHFET and c) C-doped HEMT.

# 3. DC AND SMALL SIGNAL CHARACTERIZATIONS

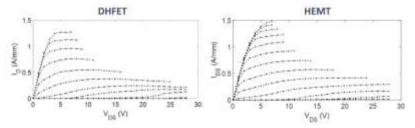

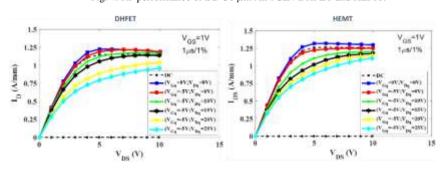

DC characterizations have been performed with a Keysight A2902A parameter analyzer. Fig. 2 shows some typical  $I_D$ - $V_{DS}$  characteristics for both structures. The gate source voltage was swept from -6V to +2V with a step of 0.5 V. For the DHFET, a maximum drain current density ( $I_{Dmax}$ ) of 1.3 A/mm is observed. The devices based on the HEMT structure deliver a higher  $I_{Dmax}$  of 1.5 A/mm under the same conditions reflecting the higher carrier concentration.

Fig. 2. Output characteristics of a  $2\times50~\mu m$  AlN/GaN DHFET and HEMT.

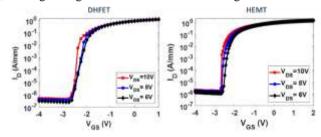

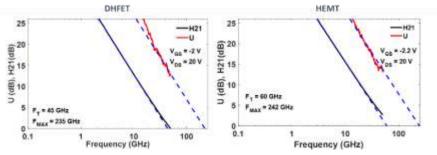

The transfer characteristics of both structures at  $V_{DS} = 6$ , 8 and 10 V appear in Fig. 3. Excellent device pinch-off behavior was obtained, which is illustrated by the low off-state leakage current below 10 µA/mm and the high breakdown voltages of 80V and 110V for the HEMT and DHFET structures, respectively. A low threshold voltage shift as a function of V<sub>DS</sub> is also observed in both cases. This confirms that a good electron confinement can be also obtained without the insertion of an AlGaN back barrier, despite the use of short gate lengths (< 150 nm). In addition, a slightly higher extrinsic transconductance is observed for the HEMT structure with a g<sub>m</sub> around 500 mS/mm at V<sub>DS</sub>=10V against 470 mS/mm at  $V_{DS} = 10V$  for the DHFET. The current-gain and power-gain cut-off frequencies are extracted from the scattering (S) parameters using Rhode and Schwarz ZVA67GHz network analyzer at V<sub>DS</sub> = 20V. The quiescent current bias point has been varied around the peak transconductance so that the maximum frequency performances are extracted. The DHFET yields a  $f_T = 45$  GHz and  $f_{max} = 235$  GHz, while slightly better RF performances are achieved for the HEMT with  $f_T = 60$  GHz and  $f_{max} = 242$  GHz (see Fig. 4). This indicates that we may benefit from a shorter effective gate length with the HEMT structure at such high bias. Fig. 5 show the pulsed I-V characteristics performed with a quiescent drain voltage  $(V_{Q,DS})$  up to 25V at  $V_{GS} = +1V$  (all pulse conditions are described on Fig. 5). For both structures, a low gate-lag and a rather similar drain-lag of about 20% are observed.

Fig. 3. Transfer characteristics at  $V_{DS}$  = 6, 8, 10 V of a 2×50  $\mu m$  AlN/GaN DHFET and HEMT.

Fig. 4. RF performance of a 2×50 µm AlN/GaN DHFET and HEMT.

Fig. 5. Pulsed I-V characteristics of a  $2\times50~\mu m$  AlN/GaN DHFET and HEMT.

# 4. LARGE SIGNAL CHARACTERIZATION AT 40 GHZ

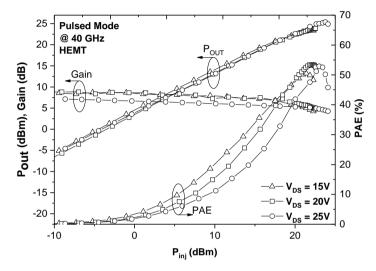

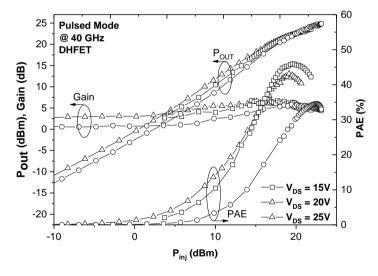

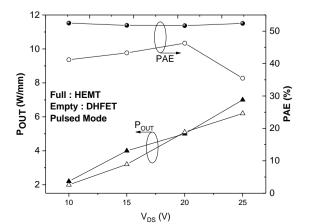

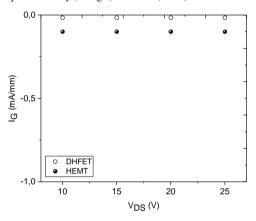

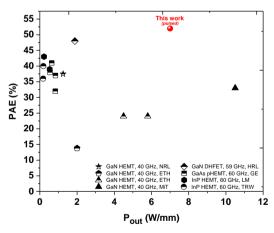

Large signal characterizations have been realized on a nonlinear vector network analyzer system (Keysight Network Analyser PNA-X, N5245A-NVNA) capable of on-wafer large signal device characterization up to the Q-band in continuous and pulsed mode. Further details can be found in [24]. On both structures, load-pull measurements have been carried out in pulsed mode (1 µs width and 1% duty cycle). It can be stressed that the same measurement conditions with a drain current density of 100 mA/mm has been used for the HEMTs and DHFETs. Fig. 6 shows the pulsed power performance of a 2×25 μm AlN/GaN HEMT at 40 GHz with  $V_{DS} = 15V$ , 20V, and 25 V. The rather low gain is due to the biasing conditions in deep class AB. A high saturated Pout of 7 W/mm was achieved with a peak PAE of 52% (corresponding to a drain efficiency of 74%) associated to a linear power gain above 8 dB. Furthermore, at  $V_{DS} = 10 \text{ V}$  a PAE as high as 56% (corresponding to a drain efficiency of 75%) combined with an output power density of 1.6 W/mm have been reached. Similarly, the pulsed power performance of a 2×25 µm DHFET structure at 40 GHz is shown in Fig. 7. The output power density evolves linearly as a function of the drain bias (see Figure 8) up to  $V_{DS} = 25V$  for both structures reflecting the high material quality and associated processing. It is worth noting that the HEMT structure shows the ability to deliver a PAE above 50% up to  $V_{DS} = 25V$ .

For the DHFET, an increasing evolution of the PAE up to  $V_{DS} = 20V$  is observed, reaching more than 45% associated to an output power density of 5.1 W/mm at  $V_{DS} = 20V$ . Nevertheless, at  $V_{DS} = 25V$  a strong degradation is observed with a PAE decreasing to 35%. It can be noticed that no device degradation (Fig. 9) is observed in both cases (such as an eventual gate leakage current increase) subsequent to the number of pulsed power

sweeps. Thus, the significant drop of the PAE at  $V_{DS} = 25 \text{V}$  is attributed to the self-heating, despite the pulsed mode. In turn, the 1 $\mu$ s pulse width is large enough to allow the increase of the junction temperature at such a high voltage within the DHFET structure. As can be seen from the benchmark in Fig. 10, the achieved PAE /  $P_{OUT}$  combination at 40 GHz compares favorably to the state-of-the-art, especially for power densities above 5 W/mm.

Fig. 6. Pulsed power performance of a  $2\times25~\mu m$  AlN/GaN HEMT at 40 GHz with  $V_{DS}=15, 20, 25V$ .

Fig. 7. Pulsed power performance of a 2×25  $\mu m$  AlN/GaN DHFET at 40 GHz with  $V_{DS}$  = 15, 20, 25 V.

Fig. 8. Pulsed output power density (triangle) and PAE (circle) of both structures versus  $V_{DS}$  at 40 GHz.

Fig. 9 Evolution of the gate leakage for the HEMTs (filled) and DHFETs (empty) at  $40~\mathrm{GHz}$ .

Fig. 10. Benchmark of peak PAE vs output RF power density for Q and V band [12], [15], [25]-[30].

# 5. RAMAN THERMOGRAPHY MEASUREMENT

The performance enhancement observed on the carbon-doped GaN HEMTs was attributed to a better thermal dissipation. To verify this statement, we assessed the channel temperature of these devices using Raman thermography [31]-[35]. These measurements

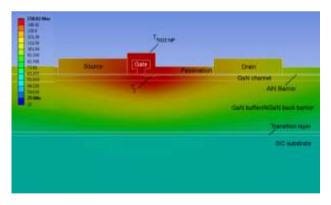

were carried out on same dimensions  $2\times50~\mu m$  DHFET and HEMT GaN/SiC devices. Thermal shift of  $E_g$  Raman peak of TiO<sub>2</sub> nanoparticles (NP) [36] deposited on the device surface, with respect to a reference value at the device pinch-off, was used to determine device surface temperature. This was measured by confocal Renishaw InVia Raman microscope in backscattering configuration under 488 nm laser excitation. A schematic representation of Raman TiO<sub>2</sub> NP temperature measurement location, on top of the passivation at the drain edge of the gate is displayed in Fig. 11. A finite elements steady-state thermal model (Fig. 12) was subsequently calibrated with the measured surface temperature data and used for the junction temperature ( $T_J$ ) extraction.

Fig. 11. Schematic representation of Raman TiO<sub>2</sub> NP temperature measurement.

Fig. 12. Device thermal modeling fitted to the experimental data.

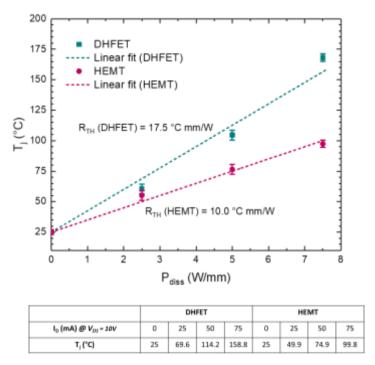

The determined peak junction temperatures are shown in Fig. 13. We note that the temperature rise difference between  $T_{TiO2}$  NP and  $T_J$  was ~3.5% and ~5.5% for the DHFET and the HEMT, respectively as the device surface is close to the highest temperature location in the device. As expected, the DHFET reached much higher  $T_J$  (approaching ~60%) than the HEMT for  $P_{diss} > 5$  W/mm. The thermal resistance  $R_{TH} = \Delta T/P_{diss}$  was extracted from the slope of fitted trend lines of  $T_J$  vs  $P_{diss}$ . Overall, the results showed that

R<sub>TH</sub> of the HEMT (10°C mm/W) was ~43% lower as compared to the DHFET (17.5°C mm/W) and comparable to reported values of GaN on SiC devices of similar dimensions [37], confirming the results we obtained from the electrical measurements.

Fig. 13. Peak channel temperature of the HEMTs and DHFETs as a function of the dissipated power density.

The table specifies the current used for each extracted junction temperature.

#### 6. Conclusion

This work shows that a careful architecture of buffer layers should be employed in order to perform high performance millimeter-wave GaN devices. The use of higher bias operation ( $V_{DS} \geq 20~V$ ) is possible when using deep sub-micrometer gate lengths only if the thermal resistance induced by the buffer layers is reduced. In particular, it is shown that a thick AlGaN back barrier (DHFET structure) with 8% Al into the buffer results in a significant drop of the PAE at  $V_{DS} > 20V$  even in pulsed mode. This is illustrated by a much higher thermal resistance (obtained by Raman Thermography measurements) as compared to the HEMT structure. The optimized AlN/GaN HEMT structure enabled to deliver a state-of-the-art combination of PAE (> 50%) and an output power density of 7 W/mm at 40 GHz and  $V_{DS} = 25V$ .

### Acknowledgments

This research was funded and supported by the French RENATECH network and the French Defense Procurement Agency (DGA) under Project EDA-EuGaNiC and Contract FUI-VeGaN.

#### References

- P. Saad, H. M. Nemati, M. Thorsell, K. Andersson, and C. Fager, "An inverse class-F GaN HEMT power amplifier with 78% PAE at 3.5 GHz," Eur. Microw. Week 2009, EuMW 2009 Sci. Prog. Qual. Radiofreq. Conf. Proc. 39th Eur. Microw. Conf. EuMC 2009, no. October, pp. 496–499, 2009, doi: 10.23919/EUMC.2009.5296560

- J. S. Moon, R. Grabar, D. Brown, I. Alvarado-Rodriguez, D. Wong, A. Schmitz, H. Fung, P. Chen, J.-C. Kang, S. Kim, T. Oh, and C. Mcguire, ">70% power-added-efficiency dual-gate, cascode GaN HEMTs without harmonic tuning," *IEEE Electron Device Lett.*, vol. 37, no. 3, pp. 272–275, 2016, doi: 10.1109/LED.2016.2520488

- 3. B. Romanczyk, Steven Wienecke, Matthew Guidry, Haoran Li, Elaheh Ahmadi, Xun Zheng, Stacia Keller, and Umesh K. Mishra, "Demonstration of Constant 8 W/mm Power Density at 10, 30, and 94 GHz in State-of-the-Art Millimeter-Wave N-Polar GaN MISHEMTs," IEEE Trans. Electron Devices, vol. 65, no. 1, pp. 45–50, 2018, doi: 10.1109/TED.2017.2770087

- 4. K. Takagi, S. Takatsuka, Y. Kashiwabara, and S. Teramoto, "Ku-Band AlGaN/GaN-HEMT with over 30 % of PAE," *Engineering*, pp. 457–460, 2009.

- J. S. Moon, J. S. Moon, D. Wong, M. Hu, P. Hashimoto, M. Antcliffe, C. McGuire, M. Micovic, and P. Willadson, "55% PAE and high power Ka-band GaN HEMTs with linearized transconductance via n+ GaN source contact ledge," *IEEE Electron Device Lett.*, vol. 29, no. 8, pp. 834–837, 2008, doi: 10.1109/LED.2008.2000792

- A. Crespo, M. M. Bellot, K. D. Chabak, J. K. Gillespie, G. H. Jessen, V. Miller, M. Trejo, G. D. Via, D. E. Walker, Jr., B. W. Winningham, H. E. Smith, T. A. Cooper, X. Gao, and S. Guo, "High-power Ka-band performance of AlInN/GaN HEMT with 9.8-nm-thin barrier," *IEEE Electron Device Lett.*, vol. 31, no. 1, pp. 2–4, 2010, doi: 10.1109/LED.2009.2034875

- M. Micovic, , D. F. Brown, A. Kurdoghlian, D. Santos, B. Grabar, J. Magadia, I. Khalaf, H. Y. Tai, E. Prophet, S. D. Burnham, J. C. Wong, D. Regan, H. H. Fung, and Y. Tang, "GaN DHFETs Having 48% Power Added Efficiency and 57% Drain Efficiency at V-band," *IEEE Electron Device Lett.*, vol. 38, no. 12, pp. 1708–1711, 2017, doi: 10.1109/LED.2017.2763940

- 8. Y. Tang, K. Shinohara, D. Regan, A. Corrion, D. Brown, J. Wong, A. Schmitz, H. Fung, S. Kim, and M. Micovic., "Ultrahigh-Speed GaN High-Electron-Mobility Transistors With fT/fmax of 454/444 GHz," *IEEE Electron Device Lett.*, vol. 36, no. 6, pp. 549–551, 2015, doi: 10.1109/LED.2015.2421311

- 9. F. Medjdoub, M. Zegaoui, B. Grimbert, N. Rolland, and P.-A. Rolland, "Effects of AlGaN Back Barrier on AlN/GaN-on-Silicon High-Electron-Mobility Transistors," *Appl. Phys. Express*, vol. 4, no. 12, p. 124101, Nov. 2011, doi: 10.1143/APEX.4.124101

- D. F. Brown, A. Williams, K. Shinohara, A. Kurdoghlian, I. Milosavljevic, P. Hashimoto, R. Grabar, S. Burnham, C. Butler, P. Willadsen, and M. Micovic, "W-Band Power Performance of AlGaN/GaN DHFETs with Regrown n+ GaN Ohmic Contacts by MBE," pp. 461–464, 2011, doi: 10.1109/IEDM.2011.6131584

- F. Medjdoub, M. Zegaoui, B. Grimbert, D. Ducatteau, N. Rolland, and P. A. Rolland, "First demonstration of high-power GaN-on-silicon transistors at 40 GHz," *IEEE Electron Device Lett.*, vol. 33, no. 8, pp. 1168–1170, 2012, doi: <u>10.1109/LED.2012.2198192</u>

- E. Dogmus, R. Kabouche, A. Linge, E. Okada, M. Zegaoui, and F. Medjdoub, "High power, high PAE Q-band sub-10 barrier thickness AlN/GaN HEMTs," *Phys. Status Solid (a)*, 2017, doi: 10.1002/pssa.201600797

- 13. T. Palacios, A. Chakraborty, S. Rajan, C. Poblenz, S. Keller, S. P. DenBaars, J. S. Speck, and U. K. Mishra, "High-power AlGaN/GaN HEMTs for Ka-band applications," *IEEE Electron Device Lett.*, vol. 26, no. 11, pp. 781–783, 2005, doi: 10.1109/LED.2005.857701

- 14. M. Micovic, P. Hashimoto, M. Hu, I. Milosavljevic, J. Duvall, P. J. Willadsen, W.- S. Wong, A. M. Conway, A. Kurdoghlian, P. W. Deelman, J.-S. Moon, A. Schmitz, and M. J. Delaney, "GaN Double Heterojunction Field Effect Transistor For Microwave and Millimeterwave Power Applications," *IEEE International Electron Devices Meeting*, pp. 807–810. 2004, doi: 10.1109/IEDM.2004.1419298

- F. Medjdoub, B. Grimbert, D. Ducatteau, and N. Rolland, "Record Combination of Power-Gain Cut-Off Frequency and Three-Terminal Breakdown Voltage for GaN-on-Silicon Devices," *Appl. Phys. Express*, vol. 6, no. 4, p. 44001, Apr. 2013.

- 16. W. Liu and A. A. Balandin, "Thermal conduction in AlxGa1-xN alloys and thin films," *J. Appl. Phys.*, vol. 97, no. 7, pp. 1–6, 2005.

- 17. P. Moens, P. Vanmeerbeek, A. Banerjee, J. Guo, C. Liu, P. Coppens, A. Salih, M. Tack "On the Impact of Carbon-Doping on the Dynamic Ron and Off-state Leakage Current of 650V GaN Power Devices," *IEEE 27th International Symposium on Power Semiconductor Devices & IC's*, pp. 37–40, 2015, doi: 10.1109/ISPSD.2015.7123383

- M. J. Uren, J. Moreke, and M. Kuball, "Buffer design to minimize current collapse in GaN/AlGaN HFETs," *IEEE Trans. Electron Devices*, vol. 59, no. 12, pp. 3327–3333, 2012, doi: 10.1109/TED.2012.2216535

- M. Kuball, J. M. Hayes, M. J. Uren, T. Martin, J. C. H. Birbeck, R. S. Balmer, and B. T. Hughes, "Measurement of Temperature in Active High-Power AlGaN/GaN HFETs Using Raman Spectroscopy," *IEEE Electron Device Lett.*, vol. 23, no. 1, pp. 10–12, 2002, doi: 10.1109/55.974795

- R. Pecheux, R. Kabouche, E. Okada, M. Zegaoui, and F. Medjdoub, "C-doped AlN/GaN HEMTs for High efficiency mmW applications," *International Workshop on Integrated Nonlinear Microwave and Millimetre-wave Circuits (INMMIC)* pp. 31–33, 2018. doi: 10.1109/INMMIC.2018.8430021

- 21. R. Pecheux, R. Kabouche, E. Dogmus, A. Linge, E. Okada, M. Zegaoui, and F. Medjdoub "Importance of buffer configuration in GaN HEMTs for high microwave performance and robustness," *ESSDERC*, pp. 4–7, 2017, doi: 10.1109/ESSDERC.2017.8066633

- 22. J. Derluyn, S. Boeykens, K. Cheng, R. Vandersmissen, J. Das, W. Ruythooren, S. Degroote, M. R. Leys, M. Germain, and G. Borghs "Improvement of AlGaNGaN high electron mobility transistor structures by *in situ* deposition of a Si<sub>3</sub>N<sub>4</sub> surface layer," *J. Appl. Phys.*, vol. 98, no. 5, p. 54501, 2005, doi: https://doi.org/10.1063/1.2008388

- 23. D. Marcon, M. V. Hove, D. Visalli, J. Derluyn, J. Das, F. Medjdoub, S. Degroote, M. Leys, K. Cheng and R. Mertens, "Excellent Stability of GaN-on-Si High Electron Mobility Transistors with 5 μm Gate–Drain Spacing Tested in Off-State at a Record Drain Voltage of 200 V and 200 °C," *Jpn. J. Appl. Phys.*, vol. 49, no. 4, p. 04DF07, Apr. 2010,

- 24. D. Marcon, F. Medjdoub, D. Visalli, M. V. Hove, J. Derluyn, J. Das, S. Degroote, M. Leys, K. Cheng, S. Decoutere, R. Mertens, M. Germain, and G. Borghs "High temperature on- and offstate stress of GaN-on-Si HEMTs with in-situ Si<sub>3</sub>N<sub>4</sub> cap layer," *IEEE Int. Reliab. Phys. Symp. Proc.*, pp. 146–151, 2010, doi: 10.1109/IRPS.2010.5488836

- R. Kabouche, E. Okada, E. Dogmus, A. Linge, M. Zegaoui, and F. Medjdoub, "Power Measurement Setup for On-Wafer Large Signal Characterization Up to Q-Band," IEEE Microw. Wirel. Components Lett., vol. 27, no. 4, pp. 419–421, 2017. doi: 10.1109/LMWC.2017.2678424

- 26. B. P. Downey, D. J. Meyer, D. S. Katzer, and J. A. Roussos, "SiN<sub>x</sub>/InAlN/AlN/GaN MIS-HEMTs With 10.8 THz ·V Johnson Figure of Merit," *IEEE Electron Device Lett.*, vol. 35, no. 5, pp. 527–529, 2014, doi: 10.1109/LED.2014.2313023

- D. Marti, S. Tirelli, A. R. Alt, J. Roberts, and C. R. Bolognesi, "150-GHz cutoff frequencies and 2-W/mm output power at 40 GHz in a millimeter-wave AlGaN/GaN HEMT technology on silicon," *IEEE Electron Device Lett.*, vol. 33, no. 10, pp. 1372–1374, 2012, doi: 10.1109/LED.2012.2204855

- 28. S. Tirelli, L. Lugani, D. Marti, J. F. Carlin, N. Grandjean, and C. R. Bolognesi, "AlInN-based HEMTs for large-signal operation at 40 GHz," *IEEE Trans. Electron Devices*, vol. 60, no. 10, pp. 3091–3098, 2013, doi: 10.1109/TED.2013.2262136

- 29. M. Kao, P. M. Smith, P. Ho,P.-C. Chao,K.H.G. Duh, A.A. Jabra and J.M. Ballingall "Very High Power-Added Efficiency and Low-Noise 0.15-μm Gate-Length Pseudomorphic HEMT's" *IEEE Electron Device Lett.*, vol. I, no. 12, pp. 580–582, 1989, doi: 10.1109/55.43146

- W. M. T. Kong, Sujane C. Wang, Pane-Chane Chao, Der-Wei Tu, Kuichul Hwang, O. S. A. Tang, Shih-Ming Liu, Pin Ho, Kirby Nichols, and John Heaton "Very high efficiency V-band power InP HEMT MMICs," *IEEE Electron Device Lett.*, vol. 21, no. 11, pp. 521–523, 2000, doi: 10.1109/55.877196

- R. Grundbacher, , R. Lai, M. Nishimoto, T. P. Chin, Y. C. Chen, M. Barsky, T. Block, and D. Streit "Pseudomorphic InP HEMT's with dry-etched source vias having 190 mW output power and 40% PAE at V-band," *IEEE Electron Device Lett.*, vol. 20, no. 10, pp. 517–519, 1999, doi: 10.1109/55.791928

- M. Kuball, and J. W. Pomeroy, "A Review of Raman Thermography for Electronic and Opto-Electronic Device Measurement With Submicron Spatial and Nanosecond Temporal Resolution," *IEEE Transactions on Device and Materials Reliability*, vol. 16, no. 4, pp. 667– 684, 2016, doi: 10.1109/TDMR.2016.2617458

- 33. D. M. Risbud, K. Pedrotti, M. Power, J. W. Pomeroy, and M. Kuball, "Thermal characterization of high voltage GaN-on-Si Schottky Barrier Diodes (SBD) for designing an on-chip thermal shutdown circuit for a power HEMT," *WiPDA*, pp. 156–161, 2015, doi: 10.1109/WiPDA.2015.7369293

- J. Pomeroy, M. Bernardonia, A. Saruaa, A. Manoia, D.C. Dumkab, D.M. Fanningb and M. Kuballa "Achieving the Best Thermal Performance for GaN-on-Diamond," 2013 IEEE Compound Semiconductor Integrated Circuit Symposium (CSICS), pp. 1–4, 2013, doi: 10.1109/CSICS.2013.6659210

- M. Power, James W. Pomeroy, Yohei Otoki, Takeshi Tanaka, Jiro Wada, Masaaki Kuzuhara, Wolfgang Jantz, Andrew Souzis, Martin Kuball "Measuring the thermal conductivity of the GaN buffer layer in AlGaN/GaN HEMTs," *Phys. Status Solidi*, 2015, vol. 212, no. 8, pp. 1742– 1745, doi: 10.1002/pssa.201431788

- Y.L. Du, Y. Deng, M. S. Zhang, "Variable-temperature Raman scattering study on anatase titanium dioxide nanocrystal," *Journal of Physics and Chemistry of Solids*, Volume 67, Issue 11, 2006, Pages 2405-2408, ISSN 0022-3697

- S Garcia, I Íñiguez-de-la-Torre, J Mateos, T González and S Pérez "Impact of substrate and thermal boundary resistance on the performance of AlGaN/GaN HEMTs analyzed by means of electro-thermal Monte Carlo simulations" *Semicond. SCi. Technol.* 2016 31 065005 doi:10.1088/0268-1242/31/6/065005

- 38. J. Joh, J.A. del Alamo, U. Chowdhury, T. Chou, H. Tserng and J. L. Jimenez, "Measurement of Channel Temperature in GaN High-Electron Mobility Transistor," *IEEE Transactions on Electron Devices*, Volume 56, Issue 12, 2009, Pages 2895-2901, doi: 10.1109/TED.2009.2032614