# Halide perovskite high-k field-effect transistors with dynamically reconfigurable ambipolarity

Noelia Devesa Canicoba, Nicolò Zagni, Fangze Liu, Gary Mccuistian, Kasun Fernando, Hugo Bellezza, Boubacar Traore, Régis Rogel, Hsinhan Tsai, Laurent Le Brizoual, et al.

### ▶ To cite this version:

Noelia Devesa Canicoba, Nicolò Zagni, Fangze Liu, Gary Mccuistian, Kasun Fernando, et al.. Halide perovskite high-k field-effect transistors with dynamically reconfigurable ambipolarity. ACS Materials Letters, 2019, 1 (6), pp.633-640. 10.1021/acsmaterialslett.9b00357. hal-02338097

HAL Id: hal-02338097

https://hal.science/hal-02338097

Submitted on 3 Jul 2024

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Halide perovskite high-k field-effect transistors with dynamically reconfigurable ambipolarity

Noelia Devesa Canicoba<sup>1,2#</sup>, Nicolò Zagni<sup>3,4#</sup>, Fangze Liu<sup>1</sup>, Gary McQuistian<sup>9</sup>, Kasun Fernando<sup>5</sup>, Hugo Bellezza<sup>1</sup>, Boubacar Traoré<sup>6</sup>, Hsinhan Tsai<sup>1,8</sup>, Regis Rogel<sup>2</sup>, Laurent Le Brizoual<sup>2</sup>, Wanyi Nie<sup>1</sup>, Sergei Tretiak<sup>1</sup>, Claudine Katan<sup>7</sup>, Jacky Even<sup>6</sup>, Mercouri G. Kanatzidis<sup>8</sup>, Bruce W. Alphenaar<sup>5</sup>, Jean-Christophe Blancon<sup>9</sup>, Muhammad A. Alam<sup>3</sup> and Aditya D. Mohite<sup>9\*</sup>

<sup>1</sup>Los Alamos National Laboratory, Los Alamos NM, 87545, USA

<sup>2</sup>Institute of Electronics and Telecommunications of Rennes (IETR), UMR CNRS 6164, University of Rennes 1, 35042 Rennes, France

<sup>3</sup>School of Electrical and Computer Engineering, Purdue University, West Lafayette, Indiana 47907, USA

<sup>4</sup>Department of Engineering "Enzo Ferrari", University of Modena and Reggio Emilia, Modena, 41125, Italy

<sup>5</sup>Department of Electrical Engineering, University of Louisville, Louisville, KY 40292, USA

<sup>6</sup>Univ Rennes, INSA Rennes, CNRS, Institut FOTON - UMR 6082, F-35000 Rennes, France

<sup>7</sup>Univ Rennes, ENSCR, INSA Rennes, CNRS, ISCR (Institut des Sciences Chimiques de Rennes) - UMR 6226, F-35000 Rennes, France

<sup>8</sup>Department of Chemistry, Northwestern University, Evanston, Illinois 60208, United States

<sup>9</sup>Department of Chemical and Biomolecular Engineering and Department of Material Science and Nanoengineering Rice University, Houston, Texas 77005, USA.

Correspondence: adm4@rice.edu

Despite the remarkable optoelectronic properties of halide perovskites, achieving reproducible field effect transistor (FET) action in polycrystalline films at room temperature has been challenging and represents a fundamental bottleneck for understanding electronic charge transport in these materials. In this work, we report halide perovskite-based FET operation at room temperature with negligible hysteresis. Extensive measurements and device modeling reveal that incorporating high-k dielectrics enables modulation of the channel conductance. Furthermore, continuous bias cycling or resting allows dynamical reconfiguration of the FETs between p-type behavior and ambipolar FET with balanced electron and hole transport and an ON/OFF ratio up to 10<sup>4</sup> and negligible degradation in transport characteristics over 100 cycles. These results elucidate the path for achieving gate modulation in perovskite thin-films and provide a platform to understand the interplay between the perovskite structure, and external

stimuli such as photons, fields and functional substrates, which will lead to novel and emergent properties.

The field effect transistor (FET) is a fundamental component for realizing modern digital integrated circuits. It is also often utilized as a platform to evaluate lateral charge transport and (opto-)electronic transport properties in isotropic materials and for the investigation of new emergent properties by electrostatically doping the material, which are otherwise not easily accessible. Halide (or organic-inorganic) perovskites (HaP) have emerged as solutionprocessed semiconductors with outstanding properties for optoelectronics including low effective mass, high carrier mobility-lifetime product, weak exciton binding energy at room temperature, unusually high defect tolerance, and low trap density. 1-12 These characteristics have raised widespread interest in their exploration for optoelectronic devices, such as solar cells leading to high power conversion efficiency values exceeding 24%, <sup>13–16</sup> radiation detectors (Gamma and X-rays) and optically pumped lasers.<sup>7,17–22</sup> Despite such unprecedented progress, several riddles remain to be solved including fundamental details of charge transport mechanisms in halide perovskite thin-films. 10,23 Additionally, recent discoveries have highlighted the important role of external stimuli such as electromagnetic radiation and electric field on the structural dynamics, 11,23,24 which in turn strongly impacts the disorder and charge transport in hybrid perovskites. The dynamic nature of the material also provides opportunities to understand and unravel new physical phenomena that couple charge transport, structural dynamics, electric field and light. FETs are an excellent platform for the elucidation of new physical properties such as electric-field induced Rashba splitting and for the realization of novel perovskite devices, spin transistors and in general gate-induced doping of the soft perovskite lattice.

While there has been some pioneering previous works on using 2D HaP as an active material for FETs<sup>25,26</sup>, there exist limited reports on 3D HaP-based FETs and attest to the

challenges of building a FET that operates at room temperature (RT). Recent work on 3D HaP FETs is summarized below. Chin et al.<sup>27</sup> reported methyl ammonium lead triiodide (MAPbI<sub>3</sub>) hybrid perovskite-based FETs that had to be operated at low temperature to overcome screening of carriers due to ionic impurities, which otherwise prevented FET operation at RT. Other reports on perovskite FETs have revealed a processing dependent n- or p-type doping of perovskites thus making it difficult to probe the intrinsic properties and charge transport. 23,28 Moreover, halide perovskite-based FETs have also been reported to exhibit significant hysteresis in the current-voltage transfer characteristics during device operation, with rapid degradation, which can strongly compromise their transport properties.<sup>27–30</sup> Zeidell et al shows that FETs with mobilities approaching 10 cm<sup>2</sup>/V-sec can be obtained by using a solvent vapor approach to passivate the grain boundaries in Methyl ammonium lead iodide (MAPbI<sub>3</sub>) based HaP FETs. More recently, Yusoff et al, demonstrated ambipolar FETs using triple cation 3D perovskites, although the origin of ambipolarity was not described. Ambipolar FET behavior was also observed by Amassian and co-workers<sup>31</sup>, in FET devices made with few microns thick MAPbI<sub>3</sub>/Br<sub>3</sub> single crystals. However, the observation of ambipolarity for a large band-gap semiconductor (perovskite bandgap is larger than 1.55 eV) with symmetric source and drain gold contacts is surprising for the choice of dielectrics (PMMA and SiO<sub>2</sub>) as the applied gate field is not large enough to tune the Fermi energy across the large band-gap and thereby switch from p- to n-type conduction. Moreover, in the work by Yusoff et al, the output characteristics appear to be anomalous as they show a square-law drain current scaling with gate overdrive (typical of long channel FETs) for the p-type curves and, at the same time, a linear scaling (typical of short channel FETs) for the n-type. Such scaling typically spans different generations of FETs technologies and there is no discussion on the physical origin of the PFET and NFET behavior. All of these recent reports on demonstrating a working 3D halide perovskite FET use a wide range of device designs and configurations, which further motivates the investigation of

3D HaP based FET studies to understand the working mechanism. Furthermore, the near intrinsic doping density<sup>4,6,32</sup>(~10<sup>16</sup>/cm³) should facilitate either p-type or n-type transport with the appropriate choice of metal contacts and therefore energy band alignment with respect to the valence or the conduction band. However, in most cases, interface traps pin the Fermi-level and prevent the effective modulation of the conductance by means of a capacitively coupled gate electrode. Therefore, the ability to modulate the conductance in halide perovskites using an FET geometry remains challenge depending on a carefully designed architecture. Moreover, there has been no report on using high-K dielectrics such as hafnium oxide (HfO<sub>2</sub>) or silicon nitride (Si<sub>3</sub>N<sub>4</sub>), for HaP FETs. Such a study is important for both the elucidation of the charge transport properties in complex perovskite device architectures and to enable the discovery of novel and emergent physical phenomena, which may lead to multifunctional devices.

In this paper, we report halide perovskite-based FETs with good gate modulation at room temperature without the need of preconditioning steps such as light soaking. We demonstrate reproducible electrostatic gating with p-type modulation of the channel conductance with negligible hysteresis. Furthermore, a novel aspect of the FETs is that after continuous bias cycling, the as fabricated p-type devices progressively transform into ambipolar FETs, where the perovskite Fermi energy can be successfully modulated by the gate voltage allowing the balanced transport of both electrons and holes with greater than four orders of magnitude gate modulation in the channel conductance. Analysis with different dielectrics such SiO<sub>2</sub>, Si<sub>3</sub>N<sub>4</sub> and HfO<sub>2</sub> reveals that the fundamental challenge for the demonstration of perovskite-based FETs operation at RT is the screening of the gate electric field by ionic vacancies. Density functional theory simulations show that the MAPbI<sub>3</sub>/HfO<sub>2</sub> interface corresponds to the ideal band alignment configuration for a gate/channel interface in a FET device. Through device characterization coupled with quantitative device modeling, we show that such effects can be overcome by combining high-quality perovskite thin films with high-

K dielectrics, thus allowing for the complete inversion of the channel. Our results elucidate the demonstration of hybrid perovskite-based FETs, enabled by the presence of high-K dielectrics and pave the path towards the understanding of transport mechanisms in hybrid perovskites-based FETs as a platform.

### **Results**

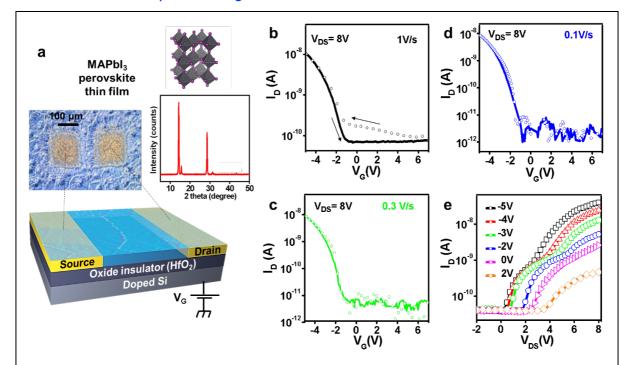

**Perovskite-based FET operation at room temperature.** The FETs were fabricated using the architecture illustrated in Fig. 1a where the main conduction channel is composed of methylammonium lead iodide (MAPbI<sub>3</sub>) organic-inorganic (hybrid) perovskite. Briefly, we used the previously developed hot-casting method<sup>5,33,34</sup> to grow large grain-sized crystalline thin-films (400 nm thick) on top of a heavily doped Si wafer with a 30-nm thick layer of hafnium oxide film (HfO<sub>2</sub>, dielectric constant ~23, experimental details are given in the Supplementary Note 1) and pre-evaporated gold contact electrodes. The characteristics of the FETs measured in the dark at room temperature and all measurements are performed using a DC bias and are reported in Fig. 1b-e. The gate voltage ( $V_G$  or gate bias) dependent drain current ( $I_D$ ) shows field effect modulation with p-type behavior (Fig. 1b-d), i.e. the FET turns ON only for negative  $V_G$  in the operating range of gate bias without failure of the device.

Figure 1. Characteristics of hybrid perovskite-based high-k field effect transistors. a, Optical image of a typical 400-nm perovskite thin film spin coated onto a heavily doped silicon substrate with pre-patterned source and drain contacts (20 nm Ti /180 nm Au) separated by 70 micrometers and 100-μm wide. Here, a 30-nm layer of HfO<sub>2</sub> was used to insulate the films from the back gate. A single grain boundary is present in the conduction channel of the transistor. (inset) Structure and diffraction pattern of the main perovskite phase MAPbI<sub>3</sub>. See details in the Supplementary Figures 1 and 2. b-d, Gate dependence of drain current (I<sub>D</sub>-V<sub>G</sub>) measured at different scan rate. Solid and symbol lines in the I<sub>D</sub>-V<sub>G</sub> curves illustrate the forward and reverse scans. e, Current-voltage (I<sub>D</sub>-V<sub>DS</sub>) characteristics for different applied gate voltage measured at 1V/s scan rate.

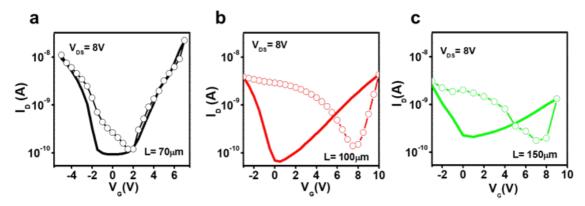

To confirm that our devices are truly hysteresis-free we measured the FET device performances as a function of V<sub>G</sub> scan speed and observed that the forward and reverse gate bias scan overlap with one another (Fig. 1b-d). The gate leakage current was dynamically monitored during the measurements and remained two orders of magnitude or more below the current when the channel is ON under the normal operating conditions, with an average value of about 30 pA (Supplementary Figure 1). The lack of hysteresis observed here for the large-grain thin films is consistent with previous results demonstrating that reducing the number of grain boundaries (here we have only one, Fig. 1a) results in a reduction of ionic transient motions and hysteresis effects.<sup>5,35</sup> We verified the detrimental effect of grain boundaries by first, studying the perovskite FET as a function of channel length (Supplementary Figure 2)

which has a strong impact on the device performances. This is mainly due to the dimension of the channel length being strongly correlated to the number of grain boundaries across the channel, which results in higher charge decay rate inside the perovskite channel and thus lower device performances.

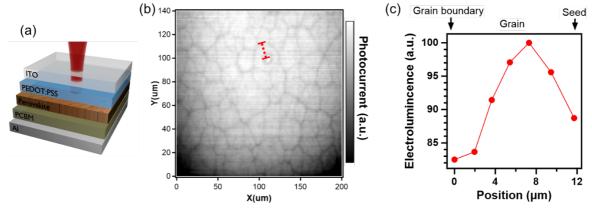

Second, we used a planar p-i-n junction architecture to measure the spatial distribution of the photocurrent and electroluminescence in the perovskite thin films (Supplementary Figure 3). We observe a dramatic reduction of both the photocurrent and electroluminescence at the grain boundaries as compared to inside the grain which can only be explained by defect-induced charge losses at boundaries, under the reasonable assumption that grains and grain boundaries have similar optical absorption.<sup>4</sup> Recent studies have also reported that ionic motion which is believed to be at the origin of part of hysteresis in perovskite solar cells, is enhanced at grain boundaries.<sup>36,37</sup> These results demonstrate that the presence of a single grain boundary in the conduction channel of our perovskite FET devices is advantageous to minimize hysteresis effects and to achieve gate field effect at room temperature.

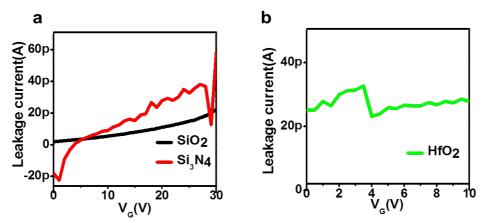

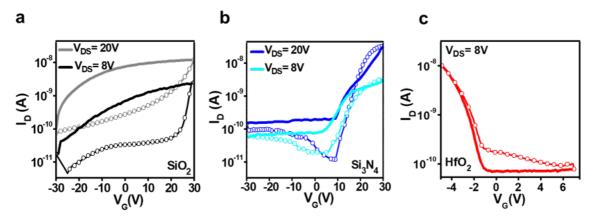

We attributed our ability to obtain reproducible thin-film perovskite FET devices operating at room temperature not only to the reduction of the number of grain boundaries in the conduction channel to one as discussed above, but also to the use of a high dielectric constant material (HfO<sub>2</sub> dielectric constant  $\epsilon$  is 23.5) as oxide insulator in our metal-oxide-FET architecture. Indeed, FETs using low dielectric constant materials such as SiO<sub>2</sub> ( $\epsilon \sim 3.9$ ) or Si<sub>3</sub>N<sub>4</sub> ( $\epsilon \sim 7.5$ ) constantly yield devices with lower performances and larger hysteresis (Supplementary Figure 4 and Table 1). We observe both a smaller gate modulation of the current and a n-type FET characteristic for devices made with SiO<sub>2</sub> or Si<sub>3</sub>N<sub>4</sub> suggesting that the technique used to deposit gate insulator may play an important role in terms of interface defects leading to a defect-induced carrier transport (details on the preparation of the FETs are given in Supplementary Table 5 to 8).

Table 1. Performances of MAPbI<sub>3</sub> perovskite FETs using different oxide layers. The  $I_D$ - $V_G$  characteristics are plotted in the Supplementary Figure 4.  $\epsilon$  is the oxide layer dielectric constant and EOT stands for the equivalent oxide thicknesses indicating the equivalent  $SiO_2$  layer needed to produce the same effect as the high-k oxide materials.

| Oxide layer                    | 3    | EOT (nm) | Conductance (nA/V) | ON/OFF<br>ratio              | Threshold field (V/cm) | Hysteresis<br>area (a.u.) |  |

|--------------------------------|------|----------|--------------------|------------------------------|------------------------|---------------------------|--|

| SiO <sub>2</sub>               | 7.5  | 100      | 0.02               | $\sim 10^2  (\text{n-type})$ | 3                      | 1                         |  |

| Si <sub>3</sub> N <sub>4</sub> | 3.9  | 52       | 0.05               | $10^2$ - $10^3$ (n-type)     | 1                      | 0.4                       |  |

| HfO <sub>2</sub>               | 23.5 | 5        | 4.90               | $10^2$ - $10^4$ (p-type)     | 0.5                    | 0.1                       |  |

Next, the current-voltage characteristics ( $I_D$ - $V_{DS}$ ) as a function of applied gate bias was measured (Fig. 1e) exhibiting a typical exponential response<sup>38</sup>, which is indicative of a Schottky barrier in our FET. Consistent with the p-type behavior observed from the  $I_D$ - $V_G$  characteristics described above (Fig. 1b),  $I_D$  increases from 0.4 nA to 40 nA for gate bias varying between 2V to -5V. Surprisingly, we observe a decrease of the turn-on voltage from about 3V to 0V while reducing the applied gate bias from 2V to -5V. This behavior indicates that the gate bias is able to modify the built-in voltage via electrostatic modulation of the doping of the perovskite layer. Specifically, the gate bias in the perovskite FETs can fully deplete the conduction channel by reducing and almost suppressing the charge doping at the barriers between the contacts and perovskite. In order to understand the results described in Fig. 1 we performed extensive modeling using first principles calculations and device modeling, which are described in Fig. 2 and Fig. 3 respectively.

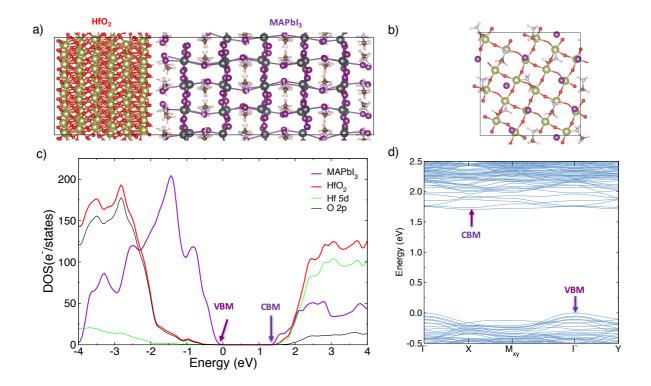

#### DFT calculations illustrating MAPbI<sub>3</sub>/HfO<sub>2</sub> interface

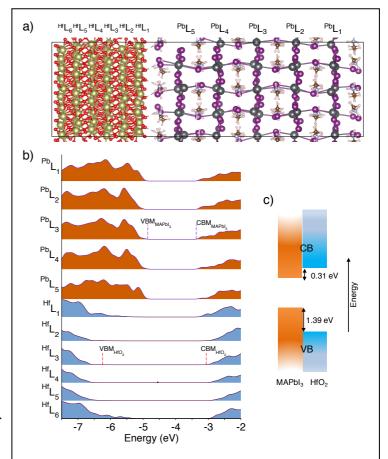

A high-performance gate oxide in a FET device presents a very low-leakage current (*vide supra*), which requires high energy barriers for both holes and electrons across the gate/channel interface. These barriers are generally referred to as the valence band offset (VBO) and the conduction band offset (CBO) for holes and electron, respectively. Hence, to compute these band offsets and thus gain a more fundamental understanding on the performance of the high-k dielectric as the gate oxide, we built a MAPbI<sub>3</sub>/HfO<sub>2</sub> interface model and studied its

properties using first-principles based modeling. The detailed procedure of the model construction along with the adopted computational approach are described in the supplementary material (Supplementary note 3). Fig. 2a shows the relaxed structure of the interface system with I atoms pointing to those of Hf at the interface region. Regarding the electronic structure of the system, the band edge states are formed by Pb-I states of MAPbI<sub>3</sub> while those of HfO<sub>2</sub> are either lower in energy at the valence band or higher at the conduction band (Supplementary Figure 6)). From layer by layer resolved projected density of states (PDOS) shown in Fig. 2b, we calculated the band offsets between MAPbI<sub>3</sub> and HfO<sub>2</sub>. Here, VBO (CBO) is defined as the difference between VBM<sub>HfO2</sub> (CBM<sub>HfO2</sub>) and VBM<sub>MAPbI3</sub> (CBM<sub>MAPbI3</sub>) from their bulk-like layers<sup>39</sup>, which are emulated in Fig. 2a by the two bulk-like layers PbL<sub>3</sub> and HfL<sub>3</sub> for MAPbI<sub>3</sub> and HfO<sub>2</sub>, respectively. We calculated a VBO of 1.39 eV and a CBO 0.31 as summarized in the band diagram of Fig. 2c. Interestingly, the latter corresponds to the ideal band alignment configuration for a gate/channel interface in a FET device and this is consistent with the improved FET characteristics measured with MAPbI<sub>3</sub>/HfO<sub>2</sub> interface. The calculated CBO presents a lower barrier as compared to VBO, which may hint to a possible electron tunneling across MAPbI<sub>3</sub>/HfO<sub>2</sub>. We stress, however, that our DFT calculations underestimate the calculated band gaps. The computations of proper many-body band gap corrections for both bulk materials and for the MAPbI<sub>3</sub>/HfO<sub>2</sub> superlattice (over 900 atoms) is computationally unaffordable. Hence, our calculated band offsets only yield a qualitative prediction, which

highlight the suitability and performance of using HfO<sub>2</sub> as a gate dielectric in MAPbI<sub>3</sub> based FET devices.

FET device modelling. In order to validate the observed p-type FET behavior with Au as the source-drain electrode and further understand the underlying mechanisms the perovskite FETs, we simulated the transfer characteristics (I<sub>D</sub>-V<sub>G</sub>) and analyzed the band diagrams of perovskite-based FETs using HfO<sub>2</sub> as gate dielectric (Fig. 3). Briefly, the numerical simulations involved the self-consistent finite element modeling of electron and hole transport in the two-dimensional device geometry, with appropriate potential barriers for the gate oxide

Figure 2. DFT modeling of MAPbI<sub>3</sub>/HfO<sub>2</sub> interface lattice structure. a, Relaxed MAPbI<sub>3</sub>/HfO<sub>2</sub> interface model from DFT calculations showing the labeling of the different layers. Here, Pb, I, Hf, O, N, C and H are atoms depicted in dark, gray, purple, maroon, red, light blue, brown and pale pink colors respectively. b, Layer-by-layer project density of states (PDOS) of relaxed interface model affording valence and conduction band alignments from the bulk-like parts of the MAPbI<sub>3</sub> and HfO<sub>2</sub>. c, Band alignment between MAPbI<sub>3</sub> and HfO<sub>2</sub> extracted from the PDOS shown in b for the two bulk-like layers PbL<sub>3</sub> and HfL<sub>3</sub> for MAPbI<sub>3</sub> and HfO<sub>2</sub>, respectively.

as well as source drain contacts (see details of the numerical simulations in Supplementary Note 2 and Supplementary Table 1 to 4). A single set of parameters allowed to predictably reproduce the I-V characteristics for a variety of device geometry (film thickness, source/drain separation, etc.), operating conditions (e.g. gate and drain voltages), different types of gate dielectrics

(HfO<sub>2</sub>, Si<sub>3</sub>N<sub>4</sub>, and so on). The analysis suggests that the key features of these transistors can be underststood at the same level of sophistication as of Silicon MOSFETs.

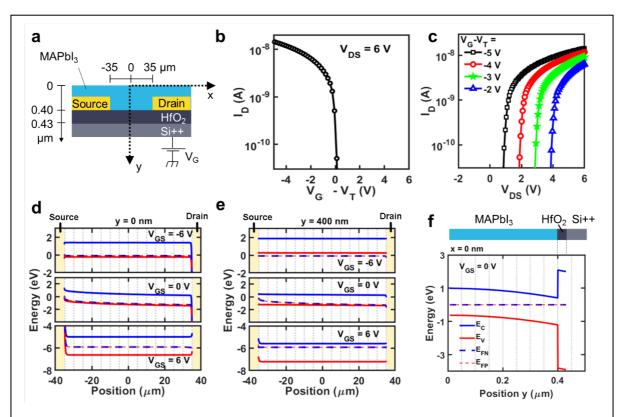

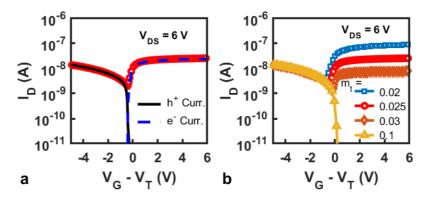

The device structure implemented in the simulator is schematically represented in Fig. 3a where the model device dimensions are also indicated (see also Supplementary Table 2). Fig. 3b shows the  $I_D$ - $V_G$  transfer characteristic for the device with a constant drain bias  $V_{DS}$  set to 6 V. The simulations predict a dominant hole current in the channel with device performance comparable to the experimental ones illustrated in Fig. 1b. The  $I_D$ - $V_{DS}$  output characteristics for the device with four different gate bias  $V_G$  is illustrated in Fig. 3c. The output characteristics

Figure 3. Device modeling of HaP field effect transistors fabricated using HfO<sub>2</sub> as gate insulator layer. a, Device schematic cross-section implemented in the simulations. b, Simulated  $I_D$  vs. gate overdrive, i.e.,  $V_G$ - $V_T$  ( $V_T$  being the threshold voltage). c, Simulated output ( $I_D$ - $V_{DS}$ ) characteristics as a function of  $V_G$ . d, Band-diagrams in the MaPbI<sub>3</sub> close to the source and drain contacts (opposite side to the gate) for three different gate bias conditions. e, Band diagram close to the interface between the perovskite and the HfO<sub>2</sub> layer. f, Band diagram at equilibrium in the middle of the device. Details of the simulations and discussion of the results can be found in the Supplementary Information. On the band-diagrams the notations are as followed: valence ( $E_V$ ) and conduction ( $E_C$ ) band edges and corresponding hole ( $E_{FP}$ ) and electron ( $E_{FN}$ ) quasi-Fermi energy levels.

are in agreement with the previous transfer characteristics (Fig. 1e), predicting no considerable change in the device behavior because the gate bias are all well below threshold.

To better understand the previous results, we analyzed the spatial distributions of the valence and conduction band edges as well as of the corresponding hole and electron quasi-Fermi energy levels (Fig. 3d-f). Figure 3d and 3e depict for three gate voltages the band diagrams along the source-drain direction at, respectively, the top and the bottom of the FET channel. We observe that the hole quasi-Fermi level is below or very close to the valence band edge at V<sub>G</sub> set to -6 V and 0 V. Conversely, when V<sub>G</sub> is set to 6 V, the hole quasi-Fermi level is well above the valence band thereby impeding the flow of holes in the channel. Although in this latter case the electron quasi-Fermi level is close to the conduction band edge, there is a relative high Schottky barrier (about 0.6 eV) at the source contact which precludes the flow of electrons in the channel even at high positive gate bias. Fig. 3f sketches the corresponding band diagram normal to the source-drain direction in the middle of the channel (vertical dashed line in inset schematics of Fig. 3f), crossing both the perovskite and oxide dielectric layers. We observe a decrease of the energy of the valence and conduction band edges by about 0.6 eV across the perovskite layer starting from the free surface. At the interface between the perovskite and oxide layers we observe large barriers for both electrons and holes that prevents leakage, assuming an idealized situation with no ionic vacancies in the perovskite material at this interface (see discussion below). Given the relatively thin perovskite layer (400 nm), the gate can fully deplete the semiconductor (as shown in Fig. 3f, for V<sub>GS</sub> = V<sub>DS</sub> = 0 V), as confirmed by the low free hole density ( $\sim 10^7$  cm<sup>-3</sup>) compared to the doping ( $10^{16}$  cm<sup>-3</sup>).

Our device simulations demonstrate that a high- $\kappa$  dielectric oxide layer such as HfO<sub>2</sub> is required to obtain perovskite-based FETs with a strong gate dependence for p-type carriers at room temperature, confirming the experimental results. We hypothesize that the key to obtain such operational FETs using polycrystalline perovskite thin-films is to reduce the screening of

the gate electric-field by charged ionic vacancies located supposedly at the interface between the perovskite and oxide dielectric which would otherwise hinder the complete inversion of the channel.

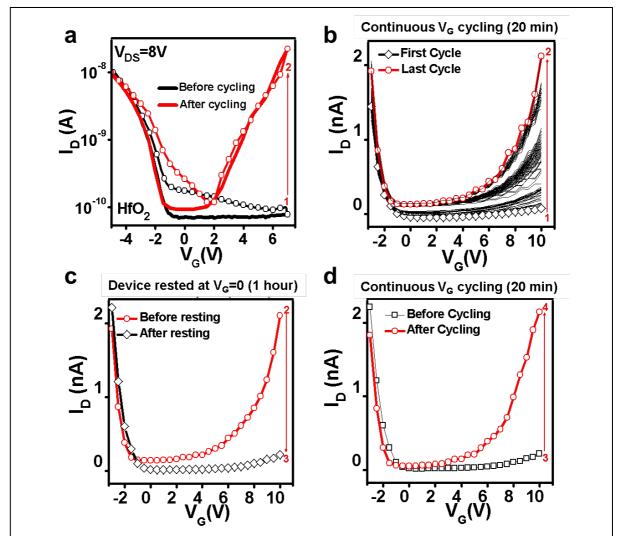

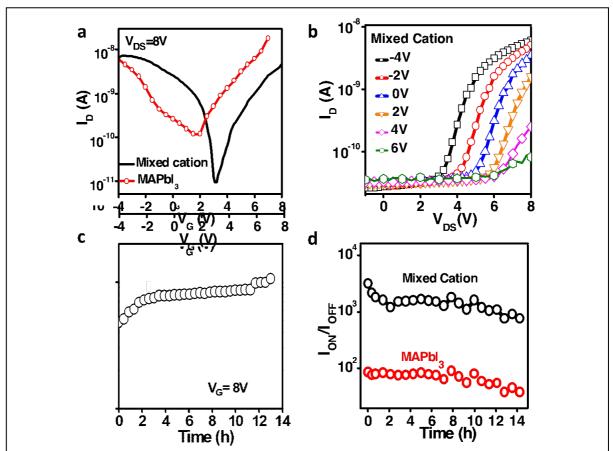

Dynamically reconfigurable perovskite FETs (experiment). We experimentally tested the stability and reliability of the gate field effect in the perovskite FETs (HfO<sub>2</sub> as oxide insulator) described in Fig. 1 by measuring the evolution of the I<sub>D</sub>-V<sub>G</sub> characteristics over several consecutive cycling of the gate bias (Fig. 4). We observed that cycling the gate voltage several times from negative to positive and back to negative at a scan speed of 1V/s resulted in a dramatic enhancement in the gate modulation for the n-type carriers. This operation resulted after 20 minutes in a transient I<sub>D</sub>-V<sub>G</sub> characteristic typical of ambipolar FETs with a negligible hysteresis and a comparable gate modulation for both the n- and p-type carriers (Fig. 4a). As illustrated in Fig. 4b, this transient effect provides control via the number of gate bias cycle over the modulation of the n-type carriers, i.e. the ON current and ON/OFF ratio. Interestingly, by resting the FET devices at zero gate bias for about 1hour the original (before gate bias cycling) p-type behavior is recovered (Fig. 4c). After that, performing the gate bias cycling operation reproduced the progressive increase of the n-type gate modulation to reach after several minutes the same ambipolar behavior as the first cycling operation (Fig. 4d). This unique and reversible reconfigurable behavior of FET operation via gate sweeping has not been reported in perovskite based FETs and could pontentially be used for short-term, reconfigurable logic circuits, where the signals are dynamically reprogrammed<sup>36–38</sup>.

The remarkable reproducibility of this transient behavior suggests that it takes its origin in a dynamical effect in hybrid perovskites which can be activated by carrier doping in the dark. We hypothesize that the transformation from a p-type FET to an ambipolar FET after continuous gate voltage cycling results from local redistribution of the ions within the channels with gate bias cycling, which leads to the creation of stacks of n-type and p-type doped regions

Figure 4. Dynamic reconfiguration between p-type and ambipolar operation in high-k MAPbI<sub>3</sub> perovskite FETs. a, Transfer characteristics before (1. black line) and after 20 minutes of continuous gate voltage cycling (2. red line).  $V_G$  was scanned with a scan speed of 1V/s. b, Consecutive  $I_D$ - $V_G$  cycles (forward direction) of lead iodide perovskite-based FETs performed continuously for 20 minutes. c, Transfer characteristics of an ambipolar perovskite-based FETs (2. symbol red line) after the device is rested at  $V_G$ =1V for 1 hour (3. symbol black line). d, Comparison of FET transfer characteristics after resting (3. symbol black line) and after a second 20-minute long gate voltage continuous cycling at 1V/s (4. symbol red line).

in the channel of the perovskite FETs. This is analogous to work by Dodabalapur et al.<sup>43</sup> which demonstrated a polarity tunable ambipolar FET by fabricating a channel with stacked p and n doped layers (achieved by using polymer and C<sub>60</sub>). Another possibility involves changes in the energy diagram of the perovskite layer that modifies the contribution of n-type carriers during gate bias modulation. In the simulations, we have qualitatively reproduced the ambipolar behavior by considering possible electron tunneling from the source/drain contacts (see

Supplementary Fig. 6). While the exact mechanism for the observed ambipolarity is not clear, our simulations suggest that the redistribution of the electric field due to ion movement could enhance the field close to the contact and enhance the tunneling current from the source/drain contacts.

Finally based on the understanding gained through our measurements (Fig. 1-4), we proceed to demonstrate a high-performance FET operating at RT by replacing the MAPbI<sub>3</sub> with the recently discovered mixed cation perovskites, which exhibits higher intrinsic electronic

Figure 5. Performance and stability of mixed cation hybrid perovskite FETs using  $HfO_2$  as back gate oxide insulator. a, Comparison of the transfer characteristics of FETs based on mixed cation perovskite and MAPbI<sub>3</sub>. Measurement were acquired after continuous gate voltage cycling according to Fig. 3. b,  $I_D$ - $V_{DS}$  output characteristics of FET based on mixed cation perovskite. c, Time evolution of  $I_D$  (measured at  $V_G$ =8 V and  $V_{DS}$ =8 V) in a mixed cation perovskite FET while the device is under continuous operation for 14 hours. d, Corresponding time evolution of the ON/OFF ratio.

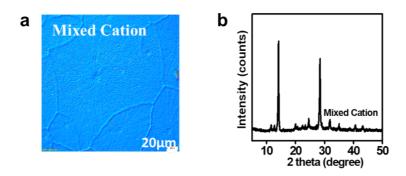

conductivity.<sup>11,14,44</sup> We used a composition of FA<sub>0.5</sub> MA<sub>0.25</sub> Cs<sub>0.25</sub> PbI<sub>3</sub> (details for the materials preparation and characteristics are given in Supplementary Note 1 and Supplementary Figure 5) as the active channel in FETs using HfO<sub>2</sub> as the gate insulator with the same device geometry

as illustrated in Fig. 1a. The corresponding I<sub>D</sub>-V<sub>DS</sub> and I<sub>D</sub>-V<sub>G</sub> characteristics are shown in Fig. 5a and 5b, where the measurement were performed after gate bias cycling under the same conditions as in Fig. 4. In comparison with the MAPbI<sub>3</sub>, the ON/OFF ratio is nearly one order of magnitude higher (~10<sup>3</sup>) in the mixed cation due to a significant reduction of the OFF current to about 10 pA. We also note an improvement in the mobility and subthreshold swing in the mixed cation-based FETs as compared to their MAPbI<sub>3</sub> counterparts. We note that the overall mobility is still on the lower end of what has been reported and we believe that this is probably related to the presence of traps at the interface of HfO<sub>2</sub>/HaP. The I<sub>D</sub>-V<sub>DS</sub> characteristics at different applied gate bias yield a typical diode behavior but with gate field dependent threshold voltage, analogous to MAPbI<sub>3</sub> based devices. We attribute the improvement of performances to the better film quality of the mixed cation perovskites as compared to MAPbI<sub>3</sub> (Supplementary Information Figure 5) and a reduction of the diode barriers.

We also evaluated the reliability of both MAPbI<sub>3</sub> and FA<sub>0.5</sub> MA<sub>0.25</sub> Cs<sub>0.25</sub> PbI<sub>3</sub> based perovskite FETs by scanning  $I_D$ -V<sub>G</sub> characteristics continuously over 14 hours. Fig. 5c and 5d show the time evolution of, respectively, the drain current at a fixed gate voltage (V<sub>G</sub> = 8V) and the ON/OFF current ratio, for both the MAPbI<sub>3</sub> and the mixed cation perovskite FETs. The results show that both types of FETs exhibit stable current output over 14 hours with little degradation in the ON current and ON/OFF ration (factor of 4). These results are the first to address the long-standing problem of reliability and stability of hybrid perovskite-based FETs operating at room temperature.

In summary, we report the first demonstration of a perovskite thin-film FET with strong gate dependence at room temperature and negligible hysteresis and good durability during the device operation. Moreover, we show that persistent electrical cycling of the gate voltage leads to a FET, which can be dynamically reconfigured between p-type and ambipolar operation states. This behavior opens new opportunities for hybrid perovskite FETs towards applications

in reprogrammable electronics including for example short and mid-term memory devices. These devices exhibit a high (10<sup>4</sup>) ON/OFF ratios and a charge carrier mobility of 10<sup>-3</sup>cm<sup>2</sup>/V.s. Further improvements in the device figures of merit are expected to arise from improvements in the contacts and mitigating charge carrier scattering at the gate oxide/perovskite interface. These results pave the path for using perovskite-based FETs as a platform for the understanding and realization of new and emergent device concepts and for the elucidation of several predicted mechanisms that couple charge, lattice, electric field and light.

Acknowledgments: The work at Rice University was supported by start-up funds under the molecular nanotechnology initiative. Work at Northwestern was supported by the U.S. Department of Energy, Office of Science (Grant No. SC0012541, structure characterization). The work at Los Alamos National Laboratory (LANL) was supported by LDRD program. J.E. acknowledges financial support from the Institute Universitaire de France. The work at University of Louisville was supported by the National Science Foundation CBET-1512106.

Authors contributions: A.D.M, conceived the idea, designed experiments, analyzed the data and co-wrote the manuscript along with J.-C.B and M.A.A. N. D.C, K. F and F. L, performed FET device fabrication. H.B performed photocurrent and electroluminescence under the supervision of J.-C.B. N. Z performed device modeling simulations and analyzed simulation data with M.A.A, who conceived the device modeling and supervised the device modeling. R. R and L.L.B analyzed the data and supervised the project along with A.D.M. J.E and M.G.K discussed the results and provided inputs on the choice of material compositions along with H.T, W.N, and S.T. B.W.A helped in optimizing experiments and helped with analysis of the data. All authors have read the manuscript.

Authors N. D.C and N. Z contributed equally to the work and will serve as joint first co-authors.

### **Additional Information**

Data availability: The data that support the findings of this study are available from the corresponding authors upon reasonable request.

Competing interests: The authors declare no competing interests.

### References

- (1) Hardin, B. E.; Snaith, H. J.; McGehee, M. D. The Renaissance of Dye-Sensitized Solar Cells. *Nature photonics* **2012**, *6* (3), 162.

- (2) Burschka, J.; Pellet, N.; Moon, S.-J.; Humphry-Baker, R.; Gao, P.; Nazeeruddin, M. K.; Grätzel, M. Sequential Deposition as a Route to High-Performance Perovskite-Sensitized Solar Cells. *Nature* **2013**, *499* (7458), 316.

- (3) Stranks, S. D.; Eperon, G. E.; Grancini, G.; Menelaou, C.; Alcocer, M. J.; Leijtens, T.; Herz, L. M.; Petrozza, A.; Snaith, H. J. Electron-Hole Diffusion Lengths Exceeding 1 Micrometer in an Organometal Trihalide Perovskite Absorber. *Science* **2013**, *342* (6156), 341–344.

- (4) Blancon, J.-C.; Nie, W.; Neukirch, A. J.; Gupta, G.; Tretiak, S.; Cognet, L.; Mohite, A. D.; Crochet, J. J. The Effects of Electronic Impurities and Electron–Hole Recombination Dynamics on Large-Grain Organic–Inorganic Perovskite Photovoltaic Efficiencies. *Advanced Functional Materials* **2016**, *26* (24), 4283–4292.

- (5) Nie, W.; Tsai, H.; Asadpour, R.; Blancon, J.-C.; Neukirch, A. J.; Gupta, G.; Crochet, J. J.; Chhowalla, M.; Tretiak, S.; Alam, M. A.; et al. High-Efficiency Solution-Processed Perovskite Solar Cells with Millimeter-Scale Grains. *Science* **2015**, *347* (6221), 522–525.

- (6) Shi, D.; Adinolfi, V.; Comin, R.; Yuan, M.; Alarousu, E.; Buin, A.; Chen, Y.; Hoogland, S.; Rothenberger, A.; Katsiev, K.; et al. Low Trap-State Density and Long Carrier Diffusion in Organolead Trihalide Perovskite Single Crystals. *Science* **2015**, 347 (6221), 519–522.

- (7) He, Y.; Matei, L.; Jung, H. J.; McCall, K. M.; Chen, M.; Stoumpos, C. C.; Liu, Z.; Peters, J. A.; Chung, D. Y.; Wessels, B. W.; et al. High Spectral Resolution of Gamma-Rays at Room Temperature by Perovskite CsPbBr 3 Single Crystals. *Nature communications* **2018**, *9* (1), 1609.

- (8) Stranks, S. D.; Snaith, H. J. Metal-Halide Perovskites for Photovoltaic and Light-Emitting Devices. *Nature nanotechnology* **2015**, *10* (5), 391.

- (9) Miyata, A.; Mitioglu, A.; Plochocka, P.; Portugall, O.; Wang, J. T.-W.; Stranks, S. D.; Snaith, H. J.; Nicholas, R. J. Direct Measurement of the Exciton Binding Energy and Effective Masses for Charge Carriers in Organic–Inorganic Tri-Halide Perovskites. *Nature Physics* **2015**, *11* (7), 582.

- (10) Egger, D. A.; Bera, A.; Cahen, D.; Hodes, G.; Kirchartz, T.; Kronik, L.; Lovrincic, R.; Rappe, A. M.; Reichman, D. R.; Yaffe, O. What Remains Unexplained about the Properties of Halide Perovskites? *Advanced Materials* **2018**, *30* (20), 1800691.

- (11) Tsai, H.; Asadpour, R.; Blancon, J.-C.; Stoumpos, C. C.; Durand, O.; Strzalka, J. W.; Chen, B.; Verduzco, R.; Ajayan, P. M.; Tretiak, S.; et al. Light-Induced Lattice Expansion Leads to High-Efficiency Perovskite Solar Cells. *Science* **2018**, *360* (6384), 67–70. https://doi.org/10.1126/science.aap8671.

- (12) Snaith, H. J. Present Status and Future Prospects of Perovskite Photovoltaics. *Nature materials* **2018**, *17* (5), 372.

- (13) Green, M. A.; Hishikawa, Y.; Warta, W.; Dunlop, E. D.; Levi, D. H.; Hohl-Ebinger, J.; Ho-Baillie, A. W. Solar Cell Efficiency Tables (Version 50). *Progress in Photovoltaics* **2017**, *25* (NREL/JA-5J00-68932).

- (14) Saliba, M.; Matsui, T.; Seo, J.-Y.; Domanski, K.; Correa-Baena, J.-P.; Nazeeruddin, M. K.; Zakeeruddin, S. M.; Tress, W.; Abate, A.; Hagfeldt, A.; et al. Cesium-Containing Triple Cation Perovskite Solar Cells: Improved Stability, Reproducibility and High Efficiency. *Energy & environmental science* **2016**, *9* (6), 1989–1997.

- (15) Yang, W. S.; Park, B.-W.; Jung, E. H.; Jeon, N. J.; Kim, Y. C.; Lee, D. U.; Shin, S. S.; Seo, J.; Kim, E. K.; Noh, J. H.; et al. Iodide Management in Formamidinium-Lead-Halide–Based Perovskite Layers for Efficient Solar Cells. *Science* **2017**, *356* (6345), 1376–1379

- (16) National Renewable Energy Laboratory, Best ResearchCell Efficiencies; Https://Www.Nrel.Gov/Pv/Assets/Pdfs/Best-Reserch-Cell-Efficiencies.Pdf.

- (17) Ling, Y.; Yuan, Z.; Tian, Y.; Wang, X.; Wang, J. C.; Xin, Y.; Hanson, K.; Ma, B.; Gao, H. Bright Light-Emitting Diodes Based on Organometal Halide Perovskite Nanoplatelets. *Advanced Materials* **2016**, *28* (2), 305–311.

- (18) Veldhuis, S. A.; Boix, P. P.; Yantara, N.; Li, M.; Sum, T. C.; Mathews, N.; Mhaisalkar, S. G. Perovskite Materials for Light-Emitting Diodes and Lasers. *Advanced Materials* **2016**, *28* (32), 6804–6834.

- (19) Tsai, H.; Nie, W.; Blancon, J.-C.; Stoumpos, C. C.; Soe, C. M. M.; Yoo, J.; Crochet, J.; Tretiak, S.; Even, J.; Sadhanala, A.; et al. Stable Light-Emitting Diodes Using Phase-Pure Ruddlesden–Popper Layered Perovskites. *Advanced Materials* **2018**, *30* (6), 1704217.

- (20) Yakunin, S.; Dirin, D. N.; Shynkarenko, Y.; Morad, V.; Cherniukh, I.; Nazarenko, O.; Kreil, D.; Nauser, T.; Kovalenko, M. V. Detection of Gamma Photons Using Solution-Grown Single Crystals of Hybrid Lead Halide Perovskites. *Nature Photonics* **2016**, *10* (9), 585.

- (21) Kim, Y. C.; Kim, K. H.; Son, D.-Y.; Jeong, D.-N.; Seo, J.-Y.; Choi, Y. S.; Han, I. T.; Lee, S. Y.; Park, N.-G. Printable Organometallic Perovskite Enables Large-Area, Low-Dose X-Ray Imaging. *Nature* **2017**, *550* (7674), 87.

- (22) Xing, J.; Zhao, Y.; Askerka, M.; Quan, L. N.; Gong, X.; Zhao, W.; Zhao, J.; Tan, H.; Long, G.; Gao, L.; et al. Color-Stable Highly Luminescent Sky-Blue Perovskite Light-Emitting Diodes. *Nature communications* **2018**, *9* (1), 3541.

- (23) Katan, C.; Mohite, A. D.; Even, J. Entropy in Halide Perovskites. *Nature Materials* **2018**, *17* (5), 377–379. https://doi.org/10.1038/s41563-018-0070-0.

- (24) Wu, X.; Tan, L. Z.; Shen, X.; Hu, T.; Miyata, K.; Trinh, M. T.; Li, R.; Coffee, R.; Liu, S.; Egger, D. A.; et al. Light-Induced Picosecond Rotational Disordering of the Inorganic Sublattice in Hybrid Perovskites. *Science advances* **2017**, *3* (7), e1602388.

- (25) Matsushima, T.; Hwang, S.; Sandanayaka, A. S.; Qin, C.; Terakawa, S.; Fujihara, T.; Yahiro, M.; Adachi, C. Solution-Processed Organic–Inorganic Perovskite Field-Effect Transistors with High Hole Mobilities. *Advanced Materials* **2016**, *28* (46), 10275–10281

- (26) Kagan, C. R.; Mitzi, D. B.; Dimitrakopoulos, C. D. Organic-Inorganic Hybrid Materials as Semiconducting Channels in Thin-Film Field-Effect Transistors. *Science* **1999**, *286* (5441), 945–947. https://doi.org/10.1126/science.286.5441.945.

- (27) Chin, X. Y.; Cortecchia, D.; Yin, J.; Bruno, A.; Soci, C. Lead Iodide Perovskite Light-Emitting Field-Effect Transistor. *Nature communications* **2015**, *6*, 7383.

- (28) Senanayak, S. P.; Yang, B.; Thomas, T. H.; Giesbrecht, N.; Huang, W.; Gann, E.; Nair, B.; Goedel, K.; Guha, S.; Moya, X.; et al. Understanding Charge Transport in Lead

- Iodide Perovskite Thin-Film Field-Effect Transistors. *Science Advances* **2017**, *3* (1), e1601935.

- (29) Li, F.; Ma, C.; Wang, H.; Hu, W.; Yu, W.; Sheikh, A. D.; Wu, T. Ambipolar Solution-Processed Hybrid Perovskite Phototransistors. *Nature communications* **2015**, *6*, 8238.

- (30) Mei, Y.; Zhang, C.; Vardeny, Z.; Jurchescu, O. Electrostatic Gating of Hybrid Halide Perovskite Field-Effect Transistors: Balanced Ambipolar Transport at Room-Temperature. *MRS Communications* **2015**, *5* (2), 297–301.

- (31) Yu, W.; Li, F.; Yu, L.; Niazi, M. R.; Zou, Y.; Corzo, D.; Basu, A.; Ma, C.; Dey, S.; Tietze, M. L.; et al. Single Crystal Hybrid Perovskite Field-Effect Transistors. *Nature communications* **2018**, *9* (1), 5354.

- (32) Edri, E.; Kirmayer, S.; Henning, A.; Mukhopadhyay, S.; Gartsman, K.; Rosenwaks, Y.; Hodes, G.; Cahen, D. Why Lead Methylammonium Tri-Iodide Perovskite-Based Solar Cells Require a Mesoporous Electron Transporting Scaffold (but Not Necessarily a Hole Conductor). *Nano letters* **2014**, *14* (2), 1000–1004.

- (33) Tsai, H.; Nie, W.; Lin, Y.-H.; Blancon, J. C.; Tretiak, S.; Even, J.; Gupta, G.; Ajayan, P. M.; Mohite, A. D. Effect of Precursor Solution Aging on the Crystallinity and Photovoltaic Performance of Perovskite Solar Cells. *Advanced Energy Materials* **2017**, 7 (11), 1602159.

- (34) Nie, W.; Tsai, H.; Blancon, J.-C.; Liu, F.; Stoumpos, C. C.; Traore, B.; Kepenekian, M.; Durand, O.; Katan, C.; Tretiak, S.; et al. Critical Role of Interface and Crystallinity on the Performance and Photostability of Perovskite Solar Cell on Nickel Oxide. *Advanced Materials* **2018**, *30* (5), 1703879.

- (35) Nie, W.; Blancon, J.-C.; Neukirch, A. J.; Appavoo, K.; Tsai, H.; Chhowalla, M.; Alam, M. A.; Sfeir, M. Y.; Katan, C.; Even, J.; et al. Light-Activated Photocurrent Degradation and Self-Healing in Perovskite Solar Cells. *Nature communications* **2016**, 7, 11574.

- (36) Li, C.; Tscheuschner, S.; Paulus, F.; Hopkinson, P. E.; Kie\s sling, J.; Köhler, A.; Vaynzof, Y.; Huettner, S. Iodine Migration and Its Effect on Hysteresis in Perovskite Solar Cells. *Advanced Materials* **2016**, *28* (12), 2446–2454.

- (37) Li, C.; Guerrero, A.; Zhong, Y.; Gräser, A.; Luna, C. A. M.; Köhler, J.; Bisquert, J.; Hildner, R.; Huettner, S. Real-Time Observation of Iodide Ion Migration in Methylammonium Lead Halide Perovskites. *Small* **2017**, *13* (42), 1701711.

- (38) Sze, S. M.; Ng, K. K. *Physics of Semiconductor Devices*; John wiley & sons, 2006.

- (39) Junquera, J.; Zimmer, M.; Ordejón, P.; Ghosez, P. First-Principles Calculation of the Band Offset at B a O/B a T i O 3 and S r O/S r T i O 3 Interfaces. *Physical Review B* **2003**, *67* (15), 155327.

- (40) Stoica, A.; Zebulum, R.; Keymeulen, D.; Tawel, R.; Daud, T.; Thakoor, A. Reconfigurable VLSI Architectures for Evolvable Hardware: From Experimental Field Programmable Transistor Arrays to Evolution-Oriented Chips. *IEEE Transactions on Very Large Scale Integration (VLSI) Systems* **2001**, *9* (1), 227–232.

- (41) Trommer, J.; Heinzig, A.; Baldauf, T.; Mikolajick, T.; Weber, W. M.; Raitza, M.; Völp, M. Reconfigurable Nanowire Transistors with Multiple Independent Gates for Efficient and Programmable Combinational Circuits. In *2016 Design, Automation & Test in Europe Conference & Exhibition (DATE)*; IEEE, 2016; pp 169–174.

- (42) Heinzig, A.; Slesazeck, S.; Kreupl, F.; Mikolajick, T.; Weber, W. M. Reconfigurable Silicon Nanowire Transistors. *Nano letters* **2011**, *12* (1), 119–124.

- (43) Dodabalapur, A.; Katz, H.; Torsi, L.; Haddon, R. Organic Heterostructure Field-Effect Transistors. *Science* **1995**, *269* (5230), 1560–1562.

- (44) McMeekin, D. P.; Sadoughi, G.; Rehman, W.; Eperon, G. E.; Saliba, M.; Hörantner, M. T.; Haghighirad, A.; Sakai, N.; Korte, L.; Rech, B.; et al. A Mixed-Cation Lead Mixed-

Halide Perovskite Absorber for Tandem Solar Cells. *Science* **2016**, *351* (6269), 151–155.

## Supplementary Materials

# Halide perovskite high-k field-effect transistors with dynamically reconfigurable ambipolarity

Noelia Devesa Canicoba<sup>1,2#</sup>, Nicolò Zagni<sup>3,4#</sup>, Fangze Liu<sup>1</sup>, Gary McQuistian<sup>9</sup>, Kasun Fernando<sup>5</sup>, Hugo Bellezza<sup>1</sup>, Boubacar Traoré<sup>6</sup>, Hsinhan Tsai<sup>1,8</sup>, Regis Rogel<sup>2</sup>, Laurent Le Brizoual<sup>2</sup>, Wanyi Nie<sup>1</sup>, Sergei Tretiak<sup>1</sup>, Claudine Katan<sup>7</sup>, Jacky Even<sup>6</sup>, Mercouri G. Kanatzidis<sup>8</sup>, Bruce W. Alphenaar<sup>5</sup>, Jean-Christophe Blancon<sup>9</sup>, Muhammad A. Alam<sup>3</sup> and Aditya D. Mohite<sup>9\*</sup>

<sup>1</sup>Los Alamos National Laboratory, Los Alamos NM, 87545, USA

<sup>2</sup>Institute of Electronics and Telecommunications of Rennes (IETR), UMR CNRS 6164, University of Rennes 1, 35042 Rennes, France

<sup>3</sup>School of Electrical and Computer Engineering, Purdue University, West Lafayette, Indiana 47907, USA

<sup>4</sup>Department of Engineering "Enzo Ferrari", University of Modena and Reggio Emilia, Modena, 41125, Italy

<sup>5</sup>Department of Electrical Engineering, University of Louisville, Louisville, KY 40292, USA

<sup>6</sup>Univ Rennes, INSA Rennes, CNRS, Institut FOTON - UMR 6082, F-35000 Rennes, France

<sup>7</sup>Univ Rennes, ENSCR, INSA Rennes, CNRS, ISCR (Institut des Sciences Chimiques de Rennes) - UMR 6226, F-35000 Rennes, France

<sup>8</sup>Department of Chemistry, Northwestern University, Evanston, Illinois 60208, United States

<sup>9</sup>Department of Chemical and Biomolecular Engineering and Department of Material Science and Nanoengineering Rice University, Houston, Texas 77005, USA.

Correspondence: <u>adm4@rice.edu</u>

## **Supplementary Note 1**

### **Materials**

Methylammonium iodide (MAI), lead iodide (PbI<sub>2</sub>), formamidinium iodide (FAI), cesium iodide (CsI), dimethylsulfoxide (DMSO), dimethylformamide (DMF), Methylammonium chloride (MACI) were all purchased from Sigma Aldrich.

### Perovskite precursor

Lead iodide perovskite solution was mix of PbI<sub>2</sub> and MAI (1:1) in anhydrous DMSO and DMF (1:1) solvent. The prepared solution was stirred for at least 48 hours at 70 °C before using. Mixed Cation perovskite solution was mix of PbI<sub>2</sub>, FAI, MACl, and CsI (1: 0.5:0.25:0.25) in anhydrous DMSO and DMF solvent (1:1). The prepared solution was stirred for at least 24 hours at 70 °C before using.

#### **Optical microscope measurement**

The optical microscope images of perovskite films were collected using an optical bright-field microscope (Model: Olympus BX51M) with 5X and 10X focal lengths under Olympus U-DICR prism at room temperature.

### **FET fabrication**

Field effect transistors used in this study were performed following bottom-gate bottom-contact structure as illustrated in Fig.1a of the main text. Heavily n-doped Si wafer with 100nm thick thermally silicon dioxide layer (SiO<sub>2</sub>,  $\epsilon_r \sim 3.9$ ) / 100 nm thick silicon nitride (Si<sub>3</sub>N<sub>4</sub>,  $\epsilon_r \sim 7.5$ ) deposited by PECVD (plasma-enhanced chemical vapor deposition) and 30nm Hafnium oxide (HfO<sub>2</sub>,  $\epsilon_r \sim 23.4$ ) deposited by ALD (atomic layer deposition) were used as substrates in this work.

The substrates were cleaned by three times of sonication in acetone and isopropyl alcohol for 10 min respectively and subsequently dried under nitrogen air flow followed by baking on hotplate in air for 20 min. Subsequently, electrodes of 20 nm titanium and 180 nm-thick gold (100um x 100um) were deposited by electron bean deposition using a shadow mask to define a channel area of W=100um and L=70um. Subsequently, the patterned-substrates were exposed to oxygen-plasma cleaning treatment for 6 minutes to improve the wetting of the surface and obtain uniform perovskite layers; otherwise perovskite solution does not stick on the silicon substrates after its deposition. Then, the perovskite thin-films were deposited by using the previously develop hot –casting method to grow high quality perovskite films (See Supplementary Fig. 1-2).

For this approach we used a hot (70°C) perovskite precursor ink (MAI: Pbl<sub>2</sub> (1:1),) casted onto a preheated and spinning (180 °C) substrates (rotation time 30 seconds). After perovskite spin coating (thickness ~ 400nm), the substrates were placed on the hot plate at 100°C for 10 minutes to fully convert the perovskite precursor into the CH<sub>3</sub>NH<sub>3</sub>PbI<sub>3</sub> perovskite films.

### **FETs characterization**

After perovskite deposition, the devices were immediately loaded into a ST500-1-4CXKEL-TR vacuum probe station to proceed with the electrical measurements. These measurements were carried out at high vacuum (10<sup>-7</sup> torr level) by using a turbo molecular pump before the characterization. The characteristics of perovskites field effect transistors were analyzed by using YOKOGAWA 7562 Digital Multimeters along with a current amplifier (Yokogawa 7561 multimeter).

## **Supplementary Note 2**

Charged carrier transport was modeled adopting the drift-diffusion formalism (see Supplementary Tab. 1 for the equations set). With this approach Poisson equation and continuity equations are solved self-consistently to obtain the electrostatic potential and the carriers' concentration. Numerical simulations are carried out with a commercial software<sup>1</sup>.

| Poisson Equation          | $\nabla \cdot (\varepsilon \nabla \psi) = -q(p - n + N_D - N_A)$                          |

|---------------------------|-------------------------------------------------------------------------------------------|

| Continuity Equation.      | $\mp \nabla J_{n,p} = q(G_{n,p} - R_{n,p})$                                               |

| Drift-Diffusion Equations | $J_n = \mu_n n(-\nabla \psi) + D_n \nabla n$ $J_p = \mu_p p(-\nabla \psi) - D_p \nabla p$ |

| Recombination Equation    | $R_{n,p} = \frac{np - n_i^2}{\tau_n(p + p_1) + \tau_p(n + n_1)}$                          |

Supplementary Table 1. Equations for Carrier Transport used for the device simulations.

The device structure implemented in the simulator is schematically represented in Fig. 2 of the main text, with indication of the device dimensions. The geometrical parameters and device dimensions adopted in the simulations are collected in Supplementary Tab. 2.

| Symbol            | Description                     | Parameter value    |  |  |

|-------------------|---------------------------------|--------------------|--|--|

|                   |                                 |                    |  |  |

| $L_G$ Gate Length |                                 | 70 μm              |  |  |

| $W_G$             | Gate Width                      | 100 μm             |  |  |

| $t_{ox}$          | Gate Oxide Thickness            | 30 nm (EOT ~ 5 nm) |  |  |

| $t_{chan}$        | Semiconductor Channel Thickness | 400 nm             |  |  |

**Supplementary Table 2.** Geometrical Dimensions adopted in the device simulations.

Supplementary Tab. 3 collects the MaPbI<sub>3</sub> electrical parameters; Supplementary Tab. 4 includes other relevant parameters used in the simulations. Schottky barriers are considered at the boundaries of the MAPbI<sub>3</sub> layer with the gold source and drain contacts. SHR recombination (with lifetime found from literature<sup>2</sup>) in the perovskite semiconductor layer is also taken into account. We consider HfO<sub>2</sub> as the gate oxide layer ( $\varepsilon_r \sim 23.5$ ).

| Symbol          | Description                                        | Parameter value                        |

|-----------------|----------------------------------------------------|----------------------------------------|

| $E_G$           | Band Gap                                           | 1.62 eV                                |

| χ               | Electron Affinity                                  | 3.73 eV                                |

| $\varepsilon_r$ | Relative Dielectric Constant                       | 25                                     |

| $N_C$           | Effective Density of States in the Conduction Band | 6.98×10 <sup>18</sup> cm <sup>-3</sup> |

| $N_C$           | Effective Density of States in the Valence Band    | 2.49×10 <sup>18</sup> cm <sup>-3</sup> |

| $n_i$           | Intrinsic Carrier Concentration                    | 1.03×10 <sup>5</sup> cm <sup>-3</sup>  |

| $N_A$           | Doping Concentration (p-type)                      | 1.0×10 <sup>16</sup> cm <sup>-3</sup>  |

| $\mu_{n,p}$     | Carriers' Mobility                                 | 0.4 cm <sup>2</sup> /V.s               |

| $	au_{n,p}$     | Carriers' Lifetime                                 | 10 ns                                  |

**Supplementary Table 3.** MaPbI<sub>3</sub> Parameters (Perovskite)<sup>2,3</sup>.

| Symbol          | Description                                      | Parameter value   |

|-----------------|--------------------------------------------------|-------------------|

| $\varepsilon_r$ | Relative Dielectric Constant (HfO <sub>2</sub> ) | 23.5              |

| $\Phi_G$        | Gate Contact Work-Function                       | 4.05 eV (Silicon) |

| $\Phi_{S,D}$    | Source, Drain Contacts Work-Function             | 5 eV (Gold)       |

**Supplementary Table 4.** Other Relevant Simulation Parameters.

## **Supplementary Figures**

**Supplementary Figure 1.** Leakage current (Ig-Vg) in perovskite-based field effect transistor using SiO<sub>2</sub>, Si<sub>3</sub>N<sub>4</sub> and HfO<sub>2</sub> as insulators.

Supplementary Figure 2. Transfer characteristics of MAPbI<sub>3</sub> perovskite FETs with different channel length. The devices were operated in the ambipolar regime after continuous gate cycling during 1 hour, which allows us to probe channel length dependence of both electron and hole transport. Solid and dotted lines in the  $I_D\text{-}V_G$  curves illustrate the forward and reverse scans for channel length a) 70  $\mu m$ , b) 100  $\mu m$ , and c) 150  $\mu m$ , all with channel width 100  $\mu m$ .

**Supplementary Figure 3.** Surface photocurrent intensity (b) and electroluminescence intensity (c) of the MAPbI<sub>3</sub> thin films demonstrating the detrimental role of grain boundaries to charge transport. A planar solar-cell architecture (a) was used for these measurements. The electroluminescence intensity profile in (b) correspond to the dashed red line in (a).

Supplementary Figure 4. MAPbI<sub>3</sub> perovskite FETs using different dielectric as insulators. Dielectric constant-dependent transfer characteristics of a perovskite field effect transistor using (a) SiO<sub>2</sub>, (b) Si<sub>3</sub>N<sub>4</sub> and (c) HfO<sub>2</sub>. Voltages are scanned in both the forward (lines) and reverse (symbols) directions.

Supplementary Figure 5. Characteristics of the mixed cation perovskite  $FA_{0.5}$   $MA_{0.25}$   $Cs_{0.25}$   $PbI_3$ . a, Optical micrographs illustrating the microstructure for MAPbI<sub>3</sub> and Mixed Cation perovskite thin films deposited on  $HfO_2$  using hot-casting method. b, X-ray diffraction pattern of the thin films on glass substrates deposited using the hot casting technique.

Supplementary Figure 6. Simulations of ambipolar  $I_D$ - $V_G$  characteristics. a, Electron current flows for  $V_G - V_T > 0$  V when the tunneling at the source/drain contacts is active. b, Varying the electron tunneling mass (i.e., the tunneling probability) varies the current flow in the device.

## ACS Materials Lett. 2019, 1, 6, 633–640

https://doi.org/10.1021/acsmaterialslett.9b00357

| PEROVSKI   | TE PRECURSOR INK                                                        |                                                                          |  |  |  |

|------------|-------------------------------------------------------------------------|--------------------------------------------------------------------------|--|--|--|

|            | DMF                                                                     | × No operational devices                                                 |  |  |  |

| Solvent    | DMSO                                                                    | Low coverage perovskite thin films on the dielectric                     |  |  |  |

|            | Mixture DMSO:DMF                                                        | ✓ Operational devices                                                    |  |  |  |

|            | at a molar ratio of 1:1                                                 | Good coverage and high-quality perovskite films on the dielectric layer  |  |  |  |

|            | MAI:PbCl <sub>2</sub>                                                   |                                                                          |  |  |  |

| Precursors | at a molar ratio of 1:1                                                 | × No operational devices                                                 |  |  |  |

|            | PbI <sub>2:</sub> FAI:MAI:CsI<br>at a molar ratio of<br>1:0.7:0.25:0.05 | Bad quality and bad adhesion of perovskite films on the dielectric layer |  |  |  |

|            | MAI:Pbl <sub>2</sub> at a molar ratio of 1:1                            | ✓ Operational devices                                                    |  |  |  |

|            | PbI <sub>2:</sub> FAI:MAI:CsI<br>at a molar ratio of<br>1:0.5:0.25:0.25 | High quality perovskite films on the insulator layer                     |  |  |  |

**Supplementary Table 5.** Iterations performed in this work related to the perovskite precursor ink to obtain reproducible perovskite-based field effect transistors operational at room temperature.

| PEROVSKITE DEPOSITION |                                  |                                                                                                    |  |  |  |

|-----------------------|----------------------------------|----------------------------------------------------------------------------------------------------|--|--|--|

| Perovskite            | < 400nm × No operational devices |                                                                                                    |  |  |  |

| thickness<br>(d)      |                                  | Need to dilute the solution to obtain thinner layer which leads to a decrease on the film quality. |  |  |  |

|                       | 400 nm                           | ✓ Operational devices  Good coverage and high-quality perovskite films  on the dielectric layer    |  |  |  |

| Pre-<br>treatment     | No treatment                     | × No operational devices  No adherence of perovskite on the dielectric                             |  |  |  |

|                       | O <sub>2</sub> plasma            | ✓ Operational devices  Good perovskite adherence on the dielectric                                 |  |  |  |

**Supplementary Table 6.** Iterations performed in this work related to the perovskite deposition to obtain reproducible perovskite-based FETs operational at room temperature.

|                    | Without any protection                                                   | × No operational devices                                                |  |  |

|--------------------|--------------------------------------------------------------------------|-------------------------------------------------------------------------|--|--|

| Leakage<br>problem | Protection on the borders of the substrate by using an organic insulator | Leakage too high due to current paths on the edge of the silicon wafer. |  |  |

|                    | Protection on the edge of the substrates by using kapton tape            | ✓ Operational devices                                                   |  |  |

| Insulator          | SiO <sub>2</sub> (100-300nm) obtained by<br>thermal growth/ PECVD        | Huge hysteresis Weak gate modulation                                    |  |  |

|                    | Si <sub>3</sub> N <sub>4</sub> (100-300nm)deposited by PECVD             | Small hysteresis Weak gate modulation                                   |  |  |

|                    | HfO <sub>2</sub>                                                         | ✓ Operational devices                                                   |  |  |

**Supplementary Table 7.** Iterations performed in this work related to the gate dielectric to obtain reproducible perovskite-based FETs operational at room temperature.

| Channel dimensions | Square mask (100um*100um) | L<70 μm<br>W= 100μm         | × No operational devices No adherence of perovskite on small channel lengths. |  |  |

|--------------------|---------------------------|-----------------------------|-------------------------------------------------------------------------------|--|--|

|                    |                           | 150 μm >L>70 μm<br>W= 100μm | ✓ Operational devices                                                         |  |  |

**Supplementary Table 8.** Iterations performed in this work related to the device geometry to obtain reproducible perovskite-based FETs operational at room temperature.

## **Supplementary Note 3**

### First principles study of the MAPbI<sub>3</sub>/HfO<sub>2</sub> interface

The interface construction is based on the orthorhombic crystal structure of MAPbI<sub>3</sub> where the MA (methyl ammonium) molecules have well-defined positions within the inorganic Pnma lattice. Using the (001) surface of monoclinic HfO<sub>2</sub> rotated to about 90°, the MAPbI<sub>3</sub> (010) surface affords appropriate lattice matching for a MAPbI<sub>3</sub>/HfO<sub>2</sub> interface (Supplementary Table 9).

|                                                             | a (Å)      |                         | b (Å)              |                            | c (Å)      |       | β                  |       |

|-------------------------------------------------------------|------------|-------------------------|--------------------|----------------------------|------------|-------|--------------------|-------|

|                                                             | exp.       | calc.                   | exp.               | calc.                      | exp.       | calc. | exp.               | calc. |

| HfO2                                                        | 5.125      | 5.09                    | $5.18^{5}$         | 5.22                       | $5.29^{5}$ | 5.21  | 99.22 <sup>5</sup> | 99.05 |

| MAPbI <sub>3</sub>                                          | $8.84^{6}$ | 8.74                    | 12.58 <sup>6</sup> | 12.58                      | $8.56^{6}$ | 8.40  |                    |       |

|                                                             |            |                         |                    |                            |            |       |                    |       |

|                                                             |            | a <sub>interf</sub> (Å) |                    | b <sub>interf</sub><br>(Å) |            |       |                    |       |

|                                                             |            | 16.13                   |                    | 16.46                      |            |       |                    |       |

| Lateral<br>mismatch<br>wrt. relaxed<br>HfO <sub>2</sub> (%) |            | 4.1%                    |                    | 6.3%                       |            |       |                    |       |

**Supplementary Table 9.** Lattice constants of bulk HfO<sub>2</sub>, MAPbI<sub>3</sub> and the heterostructure MAPbI<sub>3</sub>/HfO<sub>2</sub> interface model. For the heterostructure, the lattice constants of MAPbI<sub>3</sub> are rotated such that b becomes c that is:  $abc \rightarrow cab$ . We note that the interface being constructed along c, the lattice mismatch along c for the heterostructure is irrelevant.

Since MAPbI<sub>3</sub> is deposited on top HfO<sub>2</sub>, we used the latter as the substrate. Therefore, we lattice matched the parameters of MAI-terminated MAPbI<sub>3</sub> to those of HfO<sub>2</sub>. This is reasonable as HfO<sub>2</sub> is much stiffer than MAPbI<sub>3</sub> from the comparison of their Young moduli. Therefore, we obtained the following lattice mismatch: 4.1% along **a** and 6.3% along **b**. These values are relatively acceptable given the differences in their crystallographic structures. The constructed interface model contained 912 atoms and was allowed to relax along the stacking **c** direction while the lateral in-plane parameters (**a** and **b**) were kept constant as obtained from bulk HfO<sub>2</sub> full relaxation (Supplementary Figure 6a). The interface relaxed such that I atoms point to those of Hf at the interface region, which is chemically consistent since Iodine is an anion that points to Hf which is a cation (Supplementary Figure 6b). The projected density of states of Supplementary Figure 6c shows the contribution of MAPbI<sub>3</sub> and HfO<sub>2</sub>. From this, one can see that the band gap edge states are MAPbI<sub>3</sub> states with HfO<sub>2</sub> presenting barriers for both holes and electrons coming from MAPbI<sub>3</sub>. Finally, the band structure of the interface is shown in Supplementary Figure 6d. The band gap appears to be indirect due to band folding from Γ to X at the conduction band as a result of MAPbI<sub>3</sub> cell doubling during the course of the interface construction.

**Supplementary Figure 6. Structural and electronic properties of MAPbI3/HfO2 interface model. a,** Relaxed MAPbI<sub>3</sub>/HfO<sub>2</sub> interface model from DFT calculations showing the labeling of the different layers. Here Pb, I, Hf, O, N, C and H atoms are depicted in dark, gray, purple, maroon, red, light blue, brown and pale pink colors, respectively. **b,** Interface configuration after relaxation with I atoms mostly pointing to Hf. **c,** Projected density of states of the interface system showing the contributions of MAPbI<sub>3</sub>, HfO<sub>2</sub>, Hf 5d and O 2p states. **d,** Band structure of the interface system.

### First principles simulations method

The calculations were performed within the Density Functional Theory (DFT)<sup>6-7</sup> as implemented in SIESTA package<sup>8</sup> with a basis set of finite-range of numerical atomic orbitals. We used the van der Waals density functional with C09 exchange<sup>9</sup> to describe the exchange-correlation term. This functional has proven to provide superior description of experimental lattice constants similar to those obtained with optimized GGA based PBEsol functional in solids<sup>10</sup>. Norm-conserving Troullier-Martins pseudopotentials were used for each atomic species to account for the core electrons.<sup>11</sup> 1s<sup>1</sup>, 2s<sup>2</sup>2p<sup>2</sup>, 2s<sup>2</sup>2p<sup>3</sup>, 5s<sup>2</sup>5p<sup>5</sup>, 5d<sup>10</sup>6s<sup>2</sup>6p<sup>2</sup>, 2s<sup>2</sup>2p<sup>4</sup> and 6s<sup>2</sup>5d<sup>2</sup> were used as valence electrons for H, C, N, I, Pb, O and Hf respectively. Polarized Double-Zeta (DZP) basis set with an energy shift of 200 meV were used for the calculations. For the real space mesh grids, energy cutoffs of 200 and at least 400 Rydberg were respectively used for MAPbI<sub>3</sub> bulk and systems including HfO<sub>2</sub> (bulk HfO<sub>2</sub> and interface with HfO<sub>2</sub>).

### References

<sup>&</sup>lt;sup>1</sup> Synopsys, (2016).

<sup>&</sup>lt;sup>2</sup> H. Tsai, R. Asadpour, J.-C. Blancon, C.C. Stoumpos, J. Even, P.M. Ajayan, M.G. Kanatzidis, M.A. Alam, A.D. Mohite, and W. Nie, Nat. Commun. **9**, 2130 (2018).

<sup>&</sup>lt;sup>3</sup> Y. Zh ou and G. Long, J. Phys. Chem. C **121**, 1455 (2017).