## Validation of Thermal Resistance Extracted From Measurements on Stripe Geometry SiGe HBTs

Suresh Balanethiram, Rosario d'Esposito, Sebastien Fregonese, Anjan Chakravorty, Thomas Zimmer

### ► To cite this version:

Suresh Balanethiram, Rosario d'Esposito, Sebastien Fregonese, Anjan Chakravorty, Thomas Zimmer. Validation of Thermal Resistance Extracted From Measurements on Stripe Geometry SiGe HBTs. IEEE Transactions on Electron Devices, 2019, 66 (10), pp.4151-4155. 10.1109/TED.2019.2935012 . hal-02277502

## HAL Id: hal-02277502 https://hal.science/hal-02277502

Submitted on 3 Sep 2019

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Validation of Thermal Resistance Extracted from Measurements on Stripe Geometry SiGe HBTs

Suresh Balanethiram, Rosario D'Esposito, Sebastien Fregonese, Anjan Chakravorty, Member, IEEE, Thomas Zimmer, Senior Member, IEEE

Abstract—In this paper, we present a straightforward methodology to validate the consistency of thermal resistance  $(R_{TH})$ measurements for a set of stripe geometry silicon-germanium (SiGe) heterojunction bipolar transistors (HBTs). The proposed approach is based on the behavior of frequency-dependent thermal impedance  $(Z_{TH})$  of HBTs. The key advantage of this method is its simplicity and ease of applicability because it requires no additional measurements than the conventional approaches to extract the electrothermal parameters. First we provide a physics based formulation to extract  $Z_{TH}$  as a function of  $R_{TH}$ . As a next step, we propose different normalization methods for  $Z_{TH}$  in stripe emitter SiGe HBTs to validate the  $R_{TH}$  used in our  $Z_{TH}$  formulation. Finally, we substantiate our validation technique across stripe emitter SiGe HBTs having different emitter dimensions corresponding to STMicroelectronics B55 technology.

Index Terms—SiGe HBTs, self-heating, thermal resistance, thermal impedance, electrothermal effect.

#### I. INTRODUCTION

**S** INCE direct measurement of thermal resistance  $(R_{TH})$  or the operating temperature is not possible in bipolar transistors, researchers attempted to extract  $R_{TH}$  [1]–[3] and its temperature dependence [4]-[7] from electrical measurements using the base-emitter voltage  $(V_{BE})$  as a thermometer. In our recent extraction work [8], we demonstrated the superior accuracy of our approach over the existing state-of-the-art  $R_{TH}$ extraction techniques with the help of compact model simulations. However, as pointed out in [8], such extraction methods can be verified only by simulations. Apparently, accuracy level based on compact model simulations serves as a benchmark to substantiate the  $R_{TH}$  obtained from measurements. Therefore, the validity of the  $R_{TH}$  extracted from measurements is still questionable. On the other hand, establishing a benchmark based on an innate thermal behaviour of transistors will be highly beneficial to verify the consistency of the measured  $R_{TH}$  across different transistor geometries. Besides, such an approach is better than TCAD validation due to the complexity involved in calibrating the electrothermal simulator for dopingdependence, temperature-dependence, and Ge-composition dependence of thermal conductivity of Si [9]. Moreover,  $R_{TH}$ obtained from such TCAD simulations can also be different from the on-wafer  $R_{TH}$  measurements of HBTs as reported in [10].

S. Balanethiram and A. Chakravorty are with the Department of Electrical Engineering, IIT Madras, Chennai 600036 India. email: ee12d007@ee.iitm.ac.in.

R. D'Esposito is with Intel, Germany. email: rosario.desposito@gmail.com.

S. Fregonese and T. Zimmer are with IMS Laboratory, University of Bordeaux, 33400 Talence, France. email: thomas.zimmer@ims-bordeaux.fr.

Interestingly, in [11] we studied the frequency-dependent thermal behavior of silicon-germanium (SiGe) heterojunction bipolar transistors (HBTs) to facilitate accurate thermal model development. The study was done with the help of 3D simulations and dedicated test structure measurements in two different state-of-the-art technology nodes (B11HFC of Infineon and B55 of STMicroelectronics). Thermal impedances  $(Z_{TH})$  measured for the devices under test (DUTs) were found to be identical at high frequencies due to identical thermal penetration depth. Since this penetration depth is inversely proportional to the operating frequency, heat flow at high frequencies is limited only within the intrinsic transistor. Therefore, the resulting heat flow volumes are almost identical for the DUTs. On the other hand, measured  $Z_{TH}$  values of the DUTs differ at low frequencies due to differences in their heat flow volumes and eventually their  $R_{TH}$  values. This observation was found to be true across different emitter finger configurations, different back-end-of-line metallization layers, and different transistor layouts. In principle, one can use this frequency-dependent trend of  $Z_{TH}$  among the DUTs to validate the  $R_{TH}$  measurements. However, the analysis based on high-frequency  $Z_{TH}$  overlap reported in [11] is limited only to the DUTs of same emitter area  $(A_E)$ .

In this work, we propose different normalization techniques for  $Z_{TH}$  to extend the idea of [11] to a set of SiGe HBTs with different  $A_E$  and eventually show that high-frequency overlap of normalized versions of  $Z_{TH}$  is possible if and only if the measured  $R_{TH}$  of all the transistors are consistent. All the  $Z_{TH}$  normalization methods proposed in this work hold true for transistors with shallow trench isolation (STI) technology and stripe emitter geometry with an emitter length  $(L_E)$  at least five times the emitter width  $(W_E)$ . The proposed approach serves as a reference to validate the measured  $R_{TH}$ during on-wafer thermal characterization of stripe geometry SiGe HBTs across different  $A_E$ . Section II elaborates the proposed methodology to extract  $Z_{TH}$  as a function of  $R_{TH}$ . In section III we discuss low-frequency S-parameter measurements of SiGe HBTs from STMicroelectronics B55 technology [12]. The  $Z_{TH}$  normalization methods resulting in the experimental validation of  $R_{TH}$  is presented in section IV. Finally, we conclude in section V.

#### II. EXTRACTION OF THERMAL IMPEDANCE

Consider an HBT biased with base emitter voltage  $(V_{BE})$ and collector emitter voltage  $(V_{CE})$ , where  $V_{CE}$  is sufficient to observe self-heating but not high enough to cause avalanche multiplication. Let  $I_C(V_{BE}, V_{CE}, T)$  and  $I_B(V_{BE}, V_{CE}, T)$ be the collector and base current components in the said DC bias condition. Here T is the operating temperature given as  $T = T_{amb} + \Delta T$ . Note that the rise in temperature above the ambient temperature  $(T_{amb})$  under DC operation is given as  $\Delta T = P_{DC}R_{TH}$ . Neglecting the series resistance effect for typical values of operating  $I_C$  in most high speed HBTs, the electrical power dissipation can be calculated as  $P_{DC} = I_C V_{CE} + I_B V_{BE}$  [5], [13].

On the other hand, for small signal excitation over the DC bias point, the total collector (base) current is given as  $I_C + \Delta i_c (I_B + \Delta i_b)$  and the total collector (base) voltage is given as  $V_{CE} + \Delta v_{ce} (V_{BE} + \Delta v_{be})$ . Here  $\Delta i_c, \Delta i_b, \Delta v_{ce}$  and  $\Delta v_{be}$  are the small-signal increments to their corresponding DC values. Ignoring the temperature dependence of small-signal capacitances,  $\Delta i_b$  and  $\Delta i_c$  can be expressed as

$$\Delta i_b = Y_{11}|_{V_{CE},T} \Delta v_{be} + Y_{12}|_{V_{BE,T}} \Delta v_{ce} + \frac{\partial I_B}{\partial T}\Big|_{V_{CE},V_{BE}} \Delta t$$

$$\Delta i_c = Y_{21}|_{V_{CE},T} \Delta v_{be} + Y_{22}|_{V_{BE,T}} \Delta v_{ce} + \frac{\partial I_C}{\partial T}\Big|_{V_{CE},V_{BE}} \Delta t.$$

(1)

$Y_{11}, Y_{12}, Y_{21}, Y_{22}$  in (1) denote the isothermal values of the *Y*-parameters evaluated at fixed DC bias.  $\Delta t$  is the change in the operating temperature of the device under small-signal operation and is given as [14]

$$\Delta t = Z_{TH}(\omega)\Delta p \tag{2}$$

where  $Z_{TH}$  is the thermal impedance,  $\omega$  is the angular frequency of the small-signal excitation, and  $\Delta p$  is the smallsignal increment to  $P_{DC}$ . Now it is important to note that the small-signal current components from the energy storage elements like capacitors do not contribute to power dissipation [14], [15]. Therefore, we calculate the overall  $P_{diss}$  as

$$P_{diss} = (I_C + \operatorname{Re}\{\Delta i_c\})(V_{CE} + \Delta v_{ce}) + (I_B + \operatorname{Re}\{\Delta i_b\})(V_{BE} + \Delta v_{be})$$

(3)

=  $P_{DC} + \Delta p$

where

$$\Delta p = I_C \Delta v_{ce} + I_B \Delta v_{be} + V_{CE} \operatorname{Re}\{\Delta i_c\} + V_{BE} \operatorname{Re}\{\Delta i_b\}$$

(4)

with

$$\operatorname{Re}\{\Delta i_{b}\} = \frac{\partial I_{B}}{\partial V_{BE}} \Delta v_{be} + \frac{\partial I_{B}}{\partial V_{CE}} \Delta v_{ce} + \frac{\partial I_{B}}{\partial T} \Delta t$$

$$\operatorname{Re}\{\Delta i_{c}\} = \frac{\partial I_{C}}{\partial V_{BE}} \Delta v_{be} + \frac{\partial I_{C}}{\partial V_{CE}} \Delta v_{ce} + \frac{\partial I_{C}}{\partial T} \Delta t.$$

(5)

The products  $\operatorname{Re}\{\Delta i_b\}\Delta v_{be}$  and  $\operatorname{Re}\{\Delta i_c\}\Delta v_{ce}$  in (3) are ignored as their contribution to (4) is insignificant. As illustrated in (5), the definition of  $\operatorname{Re}\{\Delta i\}$  corresponds to the small-signal conductance current component alone. Knowing  $P_{DC}$  and  $\Delta p$ , the total junction temperature can be obtained as

$$T_j = T + \Delta t = T_{amb} + P_{DC}R_{TH} + \Delta p Z_{TH}(\omega).$$

(6)

$Z_{TH}(\omega)$  can be extracted directly from Y-parameters measurement, in particular from  $Y_{22}$  since it is most affected

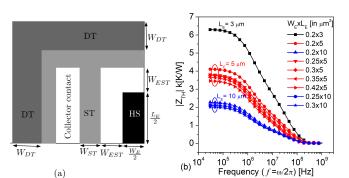

Fig. 1. (a) Top view of one quarter of a SiGe HBT of STMicroelectronics B55 technology considered in our study. z-cut taken at the heat source location. (b)  $|Z_{TH}(\omega)|$  extracted from S-parameter measurements following (9) for devices with different emitter geometries corresponding to STMicroelectronics B55 technology [12].  $R_{TH}$  used in (9) is obtained following [8].

by self-heating and also provide reliable extraction at high frequencies [16]. From (1)  $Y_{22}$  can be written as

$$\frac{\Delta_{i_c}}{\Delta_{v_{ce}}}\Big|_{\Delta v_{be}=0} = Y_{22}(\omega) = Y_{22}|_{V_{BE},T} + \frac{\partial I_C}{\partial T}\Big|_{V_{CE},V_{BE}} \frac{\Delta t}{\Delta v_{ce}}.$$

(7)

Now  $\Delta t / \Delta v_{ce}$  in (7) can be obtained by substituting (5) in (4) and the resulting expression for  $\Delta p$  in (2) with  $\Delta v_{be} = 0$ . Eventually, thermal admittance  $Y_{TH}(\omega) = 1/Z_{TH}(\omega)$  is obtained as

$$Y_{TH}(\omega) = \frac{\frac{\partial I_C}{\partial T} [I_C + V_{CE} \frac{\partial I_C}{\partial V_{CE}} + V_{BE} \frac{\partial I_B}{\partial V_{CE}}]}{Y_{22}(\omega) - Y_{22}|_{V_{BE},T}} + \frac{\partial I_B}{\partial T} V_{BE} + \frac{\partial I_C}{\partial T} V_{CE}.$$

(8)

At this stage one can obtain  $Z_{TH}$  from (8) using the DC operating point information and the Y-parameter measurements. At high frequencies, the isothermal component  $Y_{22}|_{VBE,T}$ can be obtained from  $Y_{22}$  measurements where the capacitive currents start to dominate. In order obtain  $Y_{22}|_{VBE,T}$  at low frequencies, the minimum of  $|Y_{22}|$  is extrapolated as the low-frequency value as detailed in [16] and [17].  $\partial I_B / \partial T$  $(\partial I_C / \partial T)$  can be obtained from measuring the  $I_B$  ( $I_C$ ) variation with temperature at a fixed electrical bias. Note that the formulation in (8) is consistent with the one reported in [16]. However, as reported in [18]–[20], one can neglect the last two terms in (8) to obtain a simplified relation for  $Y_{TH}(\omega)$ . Also, since we know that as  $\omega \to 0$ ,  $1/Y_{TH}(\omega) = Z_{TH}(\omega) \to R_{TH}$ , we rewrite (8) as

$$Z_{TH}(\omega) = \frac{\frac{Y_{22}(\omega) - Y_{22}|_{V_{BE},T}}{\frac{\partial I_C}{\partial T} \left[ I_C + V_{CE} \frac{\partial I_C}{\partial V_{CE}} + V_{BE} \frac{\partial I_B}{\partial V_{CE}} \right]}{\lim_{\omega \to 0} \frac{Y_{22}(\omega) - Y_{22}|_{V_{BE},T}}{\frac{\partial I_C}{\partial T} \left[ I_C + V_{CE} \frac{\partial I_C}{\partial V_{CE}} + V_{BE} \frac{\partial I_B}{\partial V_{CE}} \right]} R_{TH}.$$

(9)

At high frequencies,  $Z_{TH} \rightarrow 0$  since the thermal response of the device is comparatively slow and the output admittance is also purely electrical. Denominator of (9) is obtained by extrapolating the low-frequency  $Z_{TH}$  data. On the other hand,  $R_{TH}$  can be obtained from any conventional extraction techniques.

#### **III. LOW-FREQUENCY S-PARAMETER MEASUREMENT**

All the DUTs considered in our study are stripe geometry SiGe HBTs with different  $A_E$  corresponding to STMicroelectronics B55 technology [12]. Top view (at the plane of heat source) of one quarter of a trench isolated SiGe HBT considered in our study is shown in Fig. 1(a). The measurements are performed on-wafer on dedicated test structures in which the transistors are connected in common emitter configuration. The base and collector are accessible through the pads in GSG (ground-signal-ground) configuration. The S-parameters are measured in the range of 30 kHz to 3 GHz at  $T_{amb} = 300$ K and de-embedding is performed with the help of dedicated open and short test structures. Fig. 1(b) shows the operating frequency  $(f = \omega/2\pi)$  dependent magnitude of  $Z_{TH}$  for a set of nine SiGe HBTs extracted from their corresponding Y-parameter data following (9). To obtain the  $Z_{TH}$  curve of each transistor, the corresponding  $R_{TH}$  value at  $T_{amb} = 300$ K extracted following [8] is used in (9). Note that this  $R_{TH}$ is obtained from temperature-controlled DC measurements as detailed in [8] which is independent of the low-frequency Sparameter measurements. It is observed that  $|Z_{TH}(\omega)|$  of each HBT is unique due to the difference in their emitter area  $(A_E)$ and aspect ratios [7]. However, one can visibly distinguish three sets of curves in Fig. 1(b) based on the emitter length  $(L_E)$  of DUTs. Furthermore, for a given  $L_E$ , devices with different emitter widths  $(W_E)$  show slight differences in their  $Z_{TH}$  values. By default, HBTs with smaller emitter area  $(A_E)$ exhibits a higher  $|Z_{TH}(\omega)|$  due to its smaller heat dissipation volume compared to the larger ones.

#### IV. EXPERIMENTAL VALIDATION OF THERMAL RESISTANCE IN MULTI-GEOMETRY TRANSISTOR SET

At a given bias condition, HBTs with larger  $A_E$  drain more  $I_C$  than the smaller ones. This results in differences among the electrical power dissipation of HBTs with different  $A_E$ . Therefore, for a fare comparison,  $Z_{TH}$  in (2) should be reformulated with power density instead of power as

$$Z_{TH,pd}(\omega) = \frac{\Delta t}{\Delta p/A_E} = Z_{TH}(\omega)A_E.$$

(10)

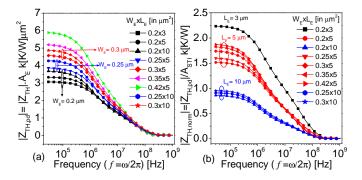

Here  $Z_{TH,pd}$  signifies a specific thermal impedance obtained under constant power density condition. The frequency dependent  $|Z_{TH,pd}|$  obtained for the same set of nine HBTs is shown in Fig. 2(a). One can evidently locate three sets of frequency overlap for non-zero  $|Z_{TH,pd}|$  as illustrated in Fig. 2(a). Each set of overlap corresponds to the family of  $|Z_{TH,pd}|$  curves with fixed  $W_E$  but different  $L_E$ . Apparently this confirms that for f > 3 MHz, HBTs with fixed  $W_E$  show equivalent thermal penetration depth despite their differences in  $L_E$ . This frequency value beyond which the  $|Z_{TH,pd}|$  curves are identical depends on the doping and transistor layout [11]. However, for any change in  $W_E$  there is no corresponding high-frequency overlap at non-zero  $|Z_{TH,pd}|$  in Fig. 2(a). Reason for this behavior is detailed below. First of all, B55

Fig. 2. (a)  $|Z_{TH,pd}(\omega)|$  extracted from measurements following (10) and (b)  $|Z_{TH,norm}(\omega)| = |Z_{TH,pd}(\omega)|/A_{STI}$  for HBTs with different emitter geometries corresponding to STMicroelectronics B55 technology [12].  $R_{TH}$ used in (9) is obtained following [8].

technology dictates a constant width  $(W_{EST})$  between the emitter edge and the nearest shallow trench isolation (STI) boundary for all HBTs (see Fig. 1(a)). Therefore, the total cross-section area enclosed by STI is given as

$$A_{STI} = (W_E + 2W_{EST})(L_E + 2W_{EST}) = A_E \left( 1 + W_{EST} \frac{P_E}{A_E} + \frac{4W_{EST}^2}{A_E} \right)$$

(11)

where  $P_E = 2(W_E + L_E)$  and  $A_E = W_E L_E$  are the perimeter and the area component of the heat source, respectively. It is important to note that all the HBTs used in our study have stripe emitter geometry. The aspect ratio of stripe emitter, defined as  $L_E/W_E$ , is very high. Apparently, for HBTs with higher aspect ratio, the perimeter to area  $(P_E/A_E)$  component of the heat source remains almost constant with any change in  $L_E$  but differs significantly even for a small change in  $W_E$ . For example, 30% increase in  $W_E$  reduces  $P_E/A_E$ component by 20% whereas 30% increase in  $L_E$  reduces  $P_E/A_E$  component by just 1%. Therefore, from (11) it is clear that the effect of  $L_E$  on STI enclosed area  $(A_{STI})$  is insignificant. At high frequencies, when the thermal oscillations are in close proximity to the heat source within STI [11],  $Z_{TH,pd}$  is governed by the percentage of the heat source area enclosed by STI ( $A_E/A_{STI}$ ). This ratio remains almost constant for any change in  $L_E$  but not for the change in  $W_E$ . Hence only those  $|Z_{TH,pd}|$  curves corresponding to different  $L_E$  and constant  $W_E$  show overlap at non-zero  $|Z_{TH,pd}|$  as shown in Fig. 2(a). Note that our motive is to obtain this high-frequency overlap even for HBTs with different  $W_E$ . Therefore, if we know the actual value of the STI enclosed area, based on the above discussion, we can normalize  $Z_{TH,pd}$ in (10) with  $A_{STI}$  as  $|Z_{TH,norm}(\omega)| = |Z_{TH,pd}(\omega)|/A_{STI}$ . Fig. 2(b) shows the frequency dependent  $|Z_{TH,norm}|$  obtained for all the nine HBTs. Similar to Fig. 1(b), one can observe three sets of curves, with each set corresponding to a constant  $L_E$ . However, unlike Fig. 1(b), Fig. 2(b) shows an evident overlap of curves at non-zero  $|Z_{TH,norm}|$  for HBTs with fixed  $L_E$ .

At this stage, it is important to highlight that if the  $R_{TH}$  value used in (9) for a given HBT is inconsistent compared to other HBTs of the measured set, we will not observe an

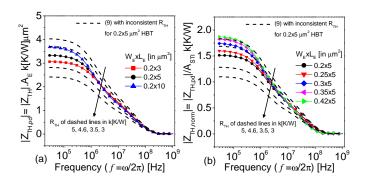

Fig. 3. (a)  $|Z_{TH,pd}(\omega)|$  and (b)  $|Z_{TH,norm}(\omega)|$  extracted from measurements for devices with fixed  $W_E = 0.2 \ \mu m$  and fixed  $L_E = 5 \ \mu m$ , respectively. Symbols correspond to the  $R_{TH}$  values used in (9) that are obtained following [8]. Dashed lines represent a chosen range of inconsistent  $R_{TH}$  values being used in (9) for the 0.2x5  $\mu$ m<sup>2</sup> device.

overlap at non-zero values of its  $Z_{TH,pd}$  or  $Z_{TH,norm}$  curves. Because, it is evident from (9) that any percentage deviation in  $R_{TH}$  will be exactly reflected across all the frequencies for that device thereby affecting its entire  $Z_{TH}(\omega)$  curve. This point is illustrated in Figs. 3(a) and (b) using  $Z_{TH,pd}$ of HBTs with fixed  $W_E$  and  $Z_{TH,norm}$  of HBTs with fixed  $L_E$ , respectively. Symbols represent  $Z_{TH,pd}$  and  $Z_{TH,norm}$ obtained when  $R_{TH}$  used in (9) is extracted following [8]. In addition, we deliberately used different values of  $R_{TH}$ in (9), than the actually extracted  $R_{TH}$ , to obtain  $Z_{TH,pd}$ and  $Z_{TH,norm}$  particularly for 0.2x5  $\mu$ m<sup>2</sup> HBT. These results are shown as dashed lines in Figs. 3(a) and (b). While the actual  $R_{TH}$  value extracted for the device is 4.1 k[K/W], we chose four other values of  $R_{TH}$  (3, 3.5, 4.6, 5, in k[K/W]) to study the  $Z_{TH}$  trend. One observes that for all the randomly chosen  $R_{TH}$  values for 0.2x5  $\mu$ m<sup>2</sup> transistor, the corresponding  $|Z_{TH,pd}|$  and  $|Z_{TH,norm}|$  (dashed lines in Figs. 3(a) and (b)) are not overlapping at non-zero values with those of all other HBTs (symbols) even at high frequencies. Illustration of this behavior substantiates our claim that if one extracts  $Z_{TH}$  following (9) in a set of stripe geometry SiGe HBTs with different  $A_E$  and obtain high-frequency overlap among them using the proposed normalized versions of  $Z_{TH}$ , then their  $R_{TH}$  values used in (9) are certainly consistent.

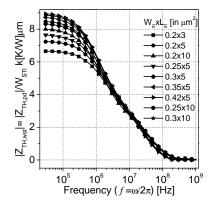

Note that the  $R_{TH}$  validation technique demonstrated so far is dependent on the high-frequency overlap of  $Z_{TH,pd}$ at fixed  $W_E$  or  $Z_{TH,norm}$  at fixed  $L_E$ . However, there can be a situation where none of the characterized HBTs share either a common  $L_E$  or a common  $W_E$ . Nevertheless, one can still use our approach by normalizing  $Z_{TH,pd}$  with the width of STI ( $W_{STI} = W_E + 2W_{EST}$ ), instead of  $A_{STI}$ , as  $|Z_{TH,wst}(\omega)| = |Z_{TH,pd}(\omega)|/W_{STI}$ . As explained earlier, high-frequency behavior of  $Z_{TH,pd}$  is predominantly affected by the variation in  $W_E$  and thus  $W_{STI}$ . Therefore, by this normalization we compensate for the differences in  $Z_{TH,pd}$ due to  $W_E$  while retaining its high-frequency behaviour with  $L_E$  as in Fig. 2(a). Results of this normalization for all the nine HBTs are shown in Fig. 4. An evident high-frequency overlap at non-zero  $|Z_{TH,wst}|$  is observed for all the HBTs,

Although it is possible to check the  $R_{TH}$  accuracy for

Fig. 4.  $|Z_{TH,wst}(\omega)| = |Z_{TH,pd}(\omega)| / W_{STI}$  extracted from measurements for devices with different emitter geometries corresponding to STMicroelectronics B55 technology [12].  $R_{TH}$  used in (9) is obtained following [8].

thereby validating the  $R_{TH}$  used in (9) across all the devices. individual devices by comparing (8) and (9), consistency of the extracted  $R_{TH}$  in a measured set of transistors can be verified through the proposed non-zero overlap method without involving (8) altogether. However, if none of the normalized versions of  $Z_{TH}$  in a measured set of devices overlaps, it would mean that all  $R_{TH}$  values used in (9) are inconsistent. In that case, the proposed approach does not identify the correct  $R_{TH}$  values. On the other hand, if we consider at least three or more data sets in our analysis, it is highly unlikely to not observe any overlap. Therefore, one can discard such extraction approaches that yield highly inconsistent  $R_{TH}$  values in a set of devices since they are unreliable.

#### V. CONCLUSION

We presented a straightforward approach to validate the consistency of  $R_{TH}$  measurements in stripe emitter SiGe HBTs across different dimensions. This method requires no additional measurements than the conventional approaches to extract the electrothermal parameters. At the outset, we gave a physics based formulation to extract  $Z_{TH}$  as a function of  $R_{TH}$  form the S-parameter measurements. Subsequently, we proposed different methods to normalize the effect of frequency-dependent thermal penetration depth on  $Z_{TH}$  curves of stripe emitter HBTs with different  $A_E$ . All the normalization methods proposed in this work are valid for stripe geometry transistors with STI technologies, where  $L_E$  is at least five times the  $W_E$ . We found that these normalized  $Z_{TH}$ of the DUTs show overlap at high frequencies if and only if their  $R_{TH}$  values are consistent. We use this behavior of the normalized  $Z_{TH}$  in a set of DUTs to validate the  $R_{TH}$ extracted from any conventional approach. The proposed validation approach is substantiated with measured data of different emitter geometries fabricated in STMicroelectronics B55 technology. This approach is based on an innate frequencydependent thermal behaviour of HBTs and in principle, can be useful across different HBT technologies during on-wafer electrothermal characterization [17].

#### VI. ACKNOWLEDGEMENT

The authors acknowledge financial support in part from the EU under Project Taranto (No. 737454) and in part from DST, India, project EMR/2016/004726. The authors would like to thank STMicroelectronics for supplying Silicon wafer.

#### REFERENCES

- J.-S. Rieh, J. Johnson, S. Furkay, D. Greenberg, G. Freeman, and S. Subbanna, "Structural dependence of the thermal resistance of trenchisolated bipolar transistors," in *Proc. Bipolar/BiCMOS Circuits and Technology Meeting (BCTM)*, 2002, pp. 100–103.

- [2] D. E. Dawson, A. K. Gupta, and M. L. Salib, "CW measurement of HBT thermal resistance," *IEEE Trans. Electron Devices*, vol. 39, no. 10, pp. 2235–2239, 1992.

- [3] M. Reisch, "Self-heating in BJT circuit parameter extraction," Solid-State Electronics, vol. 35, no. 5, pp. 677–679, 1992.

- [4] S. P. Marsh, "Direct extraction technique to derive the junction temperature of HBTs under high self-heating bias conditions," *IEEE Trans. Electron Devices*, vol. 47, no. 2, pp. 288–291, 2000.

- [5] M. Pfost, V. Kubrak, and P. Brenner, "A practical method to extract the thermal resistance for heterojunction bipolar transistors," in *Proc. 33rd Conference on European Solid-State Device Research (ESSDERC)*, 2003, pp. 335–338.

- [6] J. Berkner, "Extraction of thermal reistance and its temperature dependence using DC methods," in *HICUM workshop*, 2007.

- [7] V. d'Alessandro, G. Sasso, N. Rinaldi, and K. Aufinger, "Influence of scaling and emitter layout on the thermal behavior of toward-THz SiGe: C HBTs," *IEEE Trans. Electron Devices*, vol. 61, no. 10, pp. 3386–3394, 2014.

- [8] S. Balanethiram, J. Berkner, R. D'Esposito, S. Fregonese, D. Celi, and T. Zimmer, "Extracting the temperature dependence of thermal resistance from temperature-controlled DC measurements in SiGe HBTs," in *Proc. Bipolar/BiCMOS Circuits and Technology Meeting (BCTM)*, 2017, pp. 94–97.

- [9] H. Kamrani, D. Jabs, V. d'Alessandro, N. Rinaldi, K. Aufinger, and C. Jungemann, "A deterministic and self-consistent solver for the coupled carrier-phonon system in SiGe HBTs," *IEEE Trans. Electron Devices*, vol. 64, no. 2, pp. 361–367, 2017.

- [10] V. d'Alessandro, A. Magnani, L. Codecasa, N. Rinaldi, and K. Aufinger, "Advanced thermal simulation of SiGe: C HBTs including back-end-ofline," *Microelectronics Reliability*, vol. 67, pp. 38–45, 2016.

- [11] R. D'Esposito, S. Balanethiram, J.-L. Battaglia, S. Fregonese, and T. Zimmer, "Thermal penetration depth analysis and impact of the BEOL metals on the thermal impedance of SiGe HBTs," *IEEE Electron Device Lett.*, vol. 38, no. 10, pp. 1457–1460, 2017.

- [12] P. Chevalier, G. Avenier, G. Ribes, A. Montagné, E. Canderle, D. Céli, N. Derrier, C. Deglise, C. Durand, T. Quémerais *et al.*, "A 55 nm triple gate oxide 9 metal layers SiGe BiCMOS technology featuring 320 GHz f<sub>T</sub>/370 GHz f<sub>max</sub> HBT and high-Q millimeter-wave passives," in *IEDM Tech. Dig.*, 2014, pp. 3.9.1–3.9.3.

- [13] N. Rinaldi and V. d'Alessandro, "Theory of electrothermal behavior of bipolar transistors: Part III–Impact ionization," *IEEE Trans. Electron Devices*, vol. 53, no. 7, pp. 1683–1697, 2006.

- [14] M. Schröter and A. Chakravorty, Compact Hierarchical Bipolar Transistor Modeling with HICUM. World Scientific, 2010.

- [15] C. C. McAndrew, "A complete and consistent electrical/thermal HBT model," in *Proc. Bipolar/BiCMOS Circuits and Technology Meeting* (BCTM), 1992, pp. 200–203.

- [16] S. F. Shams, C. C. McAndrew, I.-S. Lim, and A. Zlotnicka, "SiGe HBT self-heating modeling and characterization from AC data," in *Proc. Bipolar/BiCMOS Circuits and Technology Meeting (BCTM)*, 2002, pp. 92–95.

- [17] R. D'Esposito, S. Frégonèse, and T. Zimmer, "Electrothermal Characterization, TCAD Simulations, and Physical Modeling of Advanced SiGe HBTs," in *Nanoelectronics*. Elsevier, 2019, pp. 27–94.

- [18] O. Mueller, "Internal thermal feedback in four-poles especially in transistors," *Proceedings of the IEEE*, vol. 52, no. 8, pp. 924–930, 1964.

- [19] N. Rinaldi, "Small-signal operation of semiconductor devices including self-heating, with application to thermal characterization and instability analysis," *IEEE Trans. Electron Devices*, vol. 48, no. 2, pp. 323–331, 2001

- [20] A. K. Sahoo, "Electro-thermal characterizations, compact modeling and TCAD based device simulations of advanced SiGe: C BiCMOS HBTs and of nanometric CMOS FET," *Doctoral dissertation, Univ. of Bordeaux, Talence, France*, 2012.