# Study based on the numerical simulation of a 5 kV asymmetrical 4H-SiC thyristor for high power pulses application

N. Arssi, M.L. Locatelli, Dominique Planson, J.P. Chante, V. Zorngiebel, E. Spahn, S. Scharnholz

# ▶ To cite this version:

N. Arssi, M.L. Locatelli, Dominique Planson, J.P. Chante, V. Zorngiebel, et al.. Study based on the numerical simulation of a 5 kV asymmetrical 4H-SiC thyristor for high power pulses application. CAS 2001 International Semiconductor Conference, Oct 2001, Sinaia, Romania. pp.341-344, 10.1109/SMICND.2001.967479. hal-02145398

HAL Id: hal-02145398

https://hal.science/hal-02145398

Submitted on 2 Jun 2019

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Study based on the Numerical Simulation of a 5 kV Asymmetrical 4H-SiC Thyristor for High Power Pulses Application

N. Arssi<sup>1</sup>, M. L. Locatelli, D. Planson<sup>1</sup>, J.P. Chante<sup>1</sup>, V. Zorngiebel<sup>2</sup>, E. Spahn<sup>2</sup>, S. Scharnholz<sup>2</sup>.

<sup>1</sup>CEGELY(UMR CNRS n°5005), Bât. Leonard de Vinci, INSA de Lyon, 20,Av. A. Einstein, F-69621 Villeurbanne Cedex France

Fax: (+33) (0) 4.72.43.85.30, Tel: (+33) (0) 4.72.43.82.38 E-mail: arssi@cegely.insa-lyon.fr

<sup>2</sup>ISL, Div. IV. Grp. EHI, 5 rue du Générale Cassagnou F-68 301 St. Louis FRANCE

Abstract— This paper focuses on the study of a 5 kV Asymmetrical 4H-SiC thyristor and on its Junction edge termination protection. Based on a numerical semiconductor simulator, doping level and thickness of the different layers that constitute the device will be proposed. Several techniques of periphery protection such as Mesa structure, Junction Termination Extension (JTE) and Epitaxial Guard Rings (EGR<sub>s</sub>) have been studied. Furthermore we report on the simulation of the finite element thyristor inserted in a circuit for an Electromagnetic Launching (EML) application.

Index Terms—SiC, Numerical Simulation, Thyristor, Junction Edge Termination, Mesa, JTE, EGRs, Power Pulse.

### I. INTRODUCTION

The feasibility of using silicon power thyristor for electric gun application has been established [1]. But a series array of a large number of devices is needed to achieve the required performance. The resulting size and weight of the pulser is non-optimal. The material properties of silicon carbide (SiC) indicate the potentiality of reducing the size and the power losses of the power devices [2]. SiC has a bandgap three times wider than that of silicon, high critical electric field of 2-4.10<sup>6</sup> V/cm, high thermal conductivity of 4.9 w/cm.K and high electron saturation velocity of 2.10<sup>7</sup> cm/s. This paper investigates the design and the performance of a 5 kV Asymmetrical 4H-SiC thyristor as main switch in EML applications where high power pulses are needed.

Based on the simulation result, the evaluation of a 4H-SiC thyristor is carried out with regard to the electrothermal effect. A two dimensional (2D) finite element simulation package ISE is used [3]. The numerical simulator solves coupled, non-linear partial differential semiconductor equations and predicts the electrical characteristics that are associated with specified physical structure and bias conditions.

The study of the peripheral protection, that is an important issue in the design of SiC power devices is considered and the optimal breakdown voltage for each technique (Mesa, JTE and EGR<sub>s</sub>) will be presented to terminate this static study.

In the dynamic simulation we investigate the thyristor in a circuit to estimate the switching performance and to predict the minimum area for a 20 kA current pulse.

# II. SIMULATION PARAMETERS AND MODELS

### A. Models used for the simulation

The physical models installed in the simulator are used with the material parameters tuned for 4H-SiC. The most important physical models used are for bandgap, mobility, SRH recombination, impact ionization.

1) Bandgap Energy: The variation of the intrinsic SiC bandgap with temperature is expressed by:  $E_{g}(T) = E_{g}(0) - \frac{\alpha.T^{2}}{(T + \beta)} \quad (1)$

Where T is the lattice temperature, and  $E_g(0)$  is the bandgap at 0 K (Eg(0)= 3.26 eV). The values of

the parameters  $\alpha$  and  $\beta$  are respectively  $33x10^{\text{-}5}$  eV.K  $^{\text{-}1}$  and 0 K.

2) Carrier mobility: The electron mobility  $\mu_n$  and hole mobility  $\mu_p$  are modeled by the Caughey-Thomas's equation:

$$\mu_{\rm n} = \frac{700}{1 + \left(\frac{N_{\rm A} + N_{\rm D}}{1.94 \times 10^{17}}\right)^{0.61}} \left(\frac{T}{300}\right)^{-2.15}$$

(2)

$$\mu_{p} = 15.9 + \frac{170}{1 + \left(\frac{N_{A} + N_{D}}{1.76 \times 10^{19}}\right)^{0.34}} \left(\frac{T}{300}\right)^{-2.15}$$

(3)

Where  $N_A$  and  $N_D$  are local impurity concentrations. The  $\mu_p max$  and  $\mu_n max$  are fitted from the literature data [6].

3) Generation and recombination: The Shockley-Read-Hall (SRH) recombination-generation rate  $R_{SRH}$  is used. The lifetime of electrons and holes  $\tau_n$  and  $\tau_n$  are modeled as doping level dependent

$$\tau_{n,p} = \frac{\tau_{n0,p0}}{1 + \frac{\left(N_A + N_D\right)}{10^{16}}} \tag{4}$$

In the simulation,  $\tau_{n0} = \tau_{p0} = 10^{-7}$  s is assumed.

3) Impact ionization: The generation rate of electron-hole pairs due to impact ionization is modeled by:

$$\alpha = \gamma \operatorname{ae}^{\frac{-\gamma b}{|E|}} \quad \text{with } \gamma = \frac{\tanh\left(\frac{1000\pi}{kT_0}\right)}{\tanh\left(\frac{1000\pi}{kT}\right)}$$

(5)

The impact ionization coefficients a and b used are given by Konstantinov [4].

# III. SIMULATION RESULTS

# A. Ideal breakdown voltage for a PT structure

The thyristor structure envisaged is asymmetrical with the aim to improve the voltage-blocking characteristics [5]. The maximum blocked voltage in a thyristor is fixed by the thickness and the doping level of its drift layer that corresponds to a punchthrough (PT) structure. The preliminary work was to determine the parameters of a PT structure that allows to obtain a breakdown voltage superior

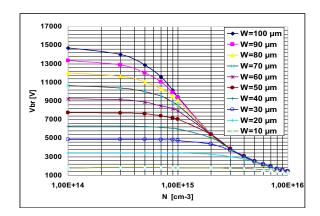

to 5 kV. We present in Fig. 1 the ideal breakdown voltage for a PT structure (N<sup>+</sup>P<sup>-</sup>P) as a function of doping and blocking layer thickness for 4H-SiC determined by simulation.

Fig. 1: Ideal breakdown voltage for a PT structure as a function of doping and blocking layer thickness.

In order to facilitate the calculation convergence the simulations are done at 600 K. The breakdown voltage is determined with the ionization integral criterion. The graph (Fig. 1) shows that a blocking voltage greater than 5 kV may be obtained with a doping of  $10^{15}$  cm<sup>-3</sup> and a thickness of only 35  $\mu$ m. To obtain a similar results with the silicon it needs more than 100  $\mu$ m with a doping inferior to  $3.10^{13}$  cm<sup>-3</sup>.

# B. The 5 kV asymmetrical thyristor

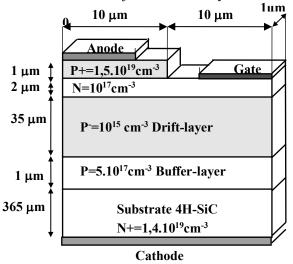

Fig. 2 shows a cross-sectional view of the structure used in the simulator and that corresponds to a half cell of an asymmetrical thyristor. Fig. 2 also shows the different technological parameters determined by simulation. Four epitaxial layers are defined on an N<sup>+</sup> 4H-SiC substrate (1,4.10<sup>19</sup> cm<sup>-3</sup>-365  $\mu$ m). The buffer P<sup>+</sup>-layer (5.10<sup>17</sup> cm<sup>-3</sup>-1  $\mu$ m) forms a punchthrough structure which blocks the spreading of the depletion layer under forward bias, thus making the device asymmetrical and improving the blocking voltage. The P-type drift layer (10<sup>15</sup> cm<sup>-3</sup>-35 µm) is fixed according to the result determined in the study of the 5 kV ideal breakdown voltage (Fig. 1). Control gate was formed on the third N-type base layer (10<sup>17</sup> cm<sup>-3</sup>-2 um) and it is designed to prevent punchthrough under forward blocking. The anode is the topmost

$P^+$  layer ( $10^{19}$  cm<sup>-3</sup>-1  $\mu$ m), its high doping level facilitates the hole injection efficiency.

Fig. 2 : Schematic cross-section of the asymmetrical 5 kV thyristor half cell.

Without considering the problems linked to the periphery, the simulation of the structure (Fig. 2) gives a theoretical forward blocking voltage of 5700 V. We obtain a voltage drop  $V_F = 6$  V for 1800 A/cm<sup>-2</sup> at 600 K. The maximal voltage in this case is limited by avalanche multiplication.

### C. Junction Edge Termination Protection

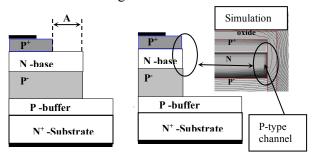

We study here different protection techniques and discuss about their results. We have first considered the Mesa protection shown in Fig. 3. The best configuration corresponds to a vertical etch that reaches the P-type buffer (Fig. 3-a) and for which the maximal voltage is 5600 V. The principal precaution for this technique is to avoid to realize the etch in the extension of the anode etch as it is shown in Fig. 3-b.

a) Mesa with A= 13  $\mu$ m b) Mesa with A = 0  $\mu$ m Fig. 3 : Description of the Mesa

Because this last case allows the creation of P-type channel due to the curving of the equipotential at the edge termination and decrease the blocking voltage down to 1500 V. To circumvent this phenomenon a minimal distance "A = 13  $\mu$ m" must be set between the anode mesa and edge termination mesa.

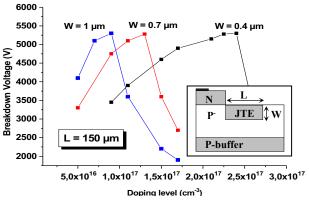

The JTE can be an other possibility for terminating the device. It can be realized by forming an N-type region in the p-type drift layer using ion-implantation of nitrogen. First, the study is done without the topmost  $P^+$  layer and the  $N^+$ -substrate in order to diminish the simulation time. Then the optimized configuration is applied to the thyristor structure.

Fig. 4: Breakdown voltage versus doping level for a depth of the JTE "W" equals to 0.4,0.7 and 1 µm

Fig. 4 shows the breakdown voltage corresponding to the N-base/P-base/P-buffer structure for three depths of the JTE with a lateral extension  $L=150~\mu m$ . The optimal result for each depth is 5300 V which corresponds to a dose of  $9.10^{12}~cm^{-2}$  of nitrogen. If we apply the optimized case for a depth of 0.4  $\mu m$  for the thyristor structure, the corresponding blocking voltage is 5500~V.

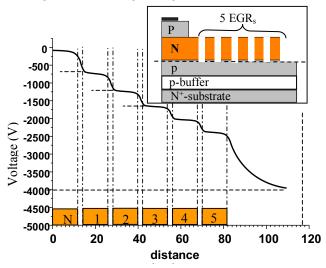

The last protection studied is called Epitaxial Guard Rings (EGR<sub>s</sub>). It consists to etch the N-base to create guard rings. The blocking voltage is sensitive mainly to the ring spacing and the etch depth. The technology we plane to use impose a minimum etch width of 2  $\mu m$ . The best results is obtained with 5 rings, the space between the ring is 2  $\mu m$ , the ring width is 12  $\mu m$  and the etch depth is 2.1  $\mu m$ . Fig. 5 shows the distribution of the

potential through the EGR<sub>s</sub> for the optimized case that gives a blocking voltage of 4100 V.

Fig. 5 Distribution of the potential through the EGRs for the optimized structure

# D. EML application

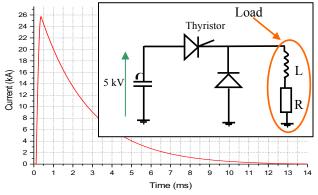

The thyristor previously designed is aimed to be used in an EML application. To predict its dynamic behavior we have inserted the finite element thyristor in a circuit (Fig. 6) for an EML application where the other components are SPICE's model defined. The typical current for this application is shaped by the inductance  $L=30~\mu H$ , the resistance  $R=10~m\Omega$  and the capacitance  $C=865~\mu F$ . Diodes are used as a crowbar switch. The schedule of condition imposed a current pulse superior to 20 kA. The charging voltage of the capacitor is 5 kV. When the thyristor is switched on the current pulse in the load (L and R in series) starts (Fig. 6).

Fig. 6: Application circuit and pulse current

The junction to ambient thermal resistance in the anode and in the cathode are set to 0.05 K/W. According to the electrothermal simulations, the current rate (di/dt) is 160 A/µs, the maximum switching current is 25.68 kA and the thyristor voltage drop (V<sub>F</sub>) is only 7.6 V for an active area of 10 cm<sup>2</sup>. The comparison with a series silicon thyristor for an identical current density (2500 A/cm<sup>2</sup>) and for a similar blocking voltage gives a voltage drop around 20 V with an active area of 20 cm<sup>2</sup>. The self heating here induces an increase of the temperature of only 25 K. We have then decreased the active area to 1.5 cm<sup>2</sup> and noticed that the maximum current is reduced to 25.5 kA with  $V_F = 35$  V. The 1.5 cm<sup>2</sup> area contributes to increase the maximum temperature in the device up to 700 K which is supported by SiC.

# CONCLUSION

We have investigated the design of a 4H-SiC asymmetrical thyristor and proposed its technological parameters for a 5 kV application. The studies of periphery protection have shown that the Mesa and JTE allow to reach  $\sim 98$  % of the ideal blocking voltage and the EGRs only  $\sim 72$  %. The evolution of the temperature with the area structure can allow to predict interest of SiC for using smaller area device operation.

## ACKNOWLEDGMENT

The authors gratefully acknowledge the French-German Research Institute of Saint Louis (ISL) for the support of this work.

# REFERENCES

- [1] E. Spahn et al., "The use of thyristors as main switches in EML application," IEEE Trans. on Magnetics, Vol. 29, no. 1, pp. 1060-1065, Jan. 1993

- [2] B. J. Baliga, "Trends in power semiconductor devices," IEEE Trans. Electron Devices, Vol. 43, pp.1717-1731, Oct. 1996.

- [3] ISE Integrated Systems Engineering AG, Zurich/CH (1998)

- [4] A. O. Konstantinov, "Ionization rates and critical field in 4H-SiC", Appl. Phys. Lett. Vol.71, no.1, pp. 90-92, Jul. 1997.

- [5] Agarwal AK et al., "700 V asymmetrical 4H-SiC gate turn-off thyristors (GTOs)". IEEE Elect. Dev. Lett. Vol. 18, no 11, pp. 518-520, Nov. 1997.

- [6] F. Nallet, "Conception, réalisation et caractérisation d'un composant limiteur de courant en carbure de silicium", Thesis INSA de Lyon, 2001