Packaging Solution for SiC Power Modules with a Fail-to-Short Capability APEC, Anaheim, USA

Ilyas DCHAR<sup>1</sup>, Cyril BUTTAY<sup>2\*</sup>, Hervé MOREL<sup>2</sup>

<sup>1</sup>SuperGrid Institute, Villeurbanne, France <sup>2</sup>Laboratoire Ampère, Villeurbanne, France

21/3/2019

Introduction

## Power Module Design & Manufacturing

Test of the Failure Mode

#### Conclusions

SuperGrid Institute

Outline

Introduction

Power Module Design & Manufacturing

Test of the Failure Mode

Conclusions

Source: I. Yaqcub PhD thesis, 2015 [1]

#### **HVDC Converters**

- Rated at 100s kV (ex 320 kV for France-Spain link)

- Series of 100s of transistors (800 for same converter)

- ► Transistors fail randomly

- Should not stop converten

- Failed device turned to short circuit

- → Need for Fail-To-Short Packaging

Source: I. Yaqcub PhD thesis, 2015 [1]

#### **HVDC Converters**

- Rated at 100s kV (ex 320 kV for France-Spain link)

- Series of 100s of transistors (800 for same converter)

- Transistors fail randomly

- Should not stop converter

- Failed device turned to short circuit

- → Need for Fail-To-Short Packaging

Source: I. Yaqcub PhD thesis, 2015 [1]

#### **HVDC Converters**

- Rated at 100s kV (ex 320 kV for France-Spain link)

- Series of 100s of transistors (800 for same converter)

- Transistors fail randomly

- Should not stop converter

- Failed device turned to short circuit

#### Need for Fail-To-Short Packaging

Source: I. Yaqcub PhD thesis, 2015 [1]

#### **HVDC Converters**

- Rated at 100s kV (ex 320 kV for France-Spain link)

- Series of 100s of transistors (800 for same converter)

- Transistors fail randomly

- Should not stop converter

- Failed device turned to short circuit

- → Need for Fail-To-Short Packaging

Wirebond

- Standard packaging: Fail-to-Open

- Wirebonds act as fuses or blown away

- → Need for massive contacts

- "Press pack"-type packages introduced

- Initially for single die, now for multichip

#### When failure occurs:

- Temperature rises

- Die and surrounding metal melt

- They form a conductive area

- Strong package contains explosion

Wirebond

- Standard packaging: Fail-to-Open

- Wirebonds act as fuses or blown away

- → Need for massive contacts

- "Press pack"-type packages introduced

- Initially for single die, now for multichip

#### When failure occurs:

- Temperature rises

- Die and surrounding metal melt

- They form a conductive area

- Strong package contains explosion

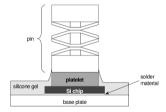

source: Gunturi, S. et al. Innovative Metal System for IGBT Press Pack Modules (ISPSD 2003) [2]

Wirebond

- Standard packaging: Fail-to-Open

- Wirebonds act as fuses or blown away

- → Need for massive contacts

- "Press pack"-type packages introduced

- Initially for single die, now for multichip

- When failure occurs:

- Temperature rises

- Die and surrounding metal melt

- They form a conductive area

- Strong package contains explosion

Wirebond

- Standard packaging: Fail-to-Open

- Wirebonds act as fuses or blown away

- → Need for massive contacts

- "Press pack"-type packages introduced

- Initially for single die, now for multichip

- When failure occurs:

SuperGrid

- Temperature rises

- Die and surrounding metal melt

- They form a conductive area

- Strong package contains explosion

#### Is a FTS package Possible for SiC?

source: Gunturi, S. *et al.* Innovative Metal System for IGBT Press Pack Modules (ISPSD 2003) [2]

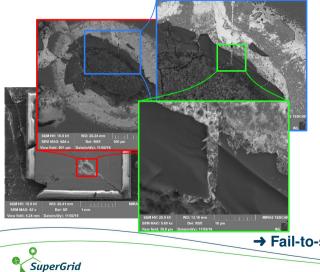

#### ► Dies fracture because of failure

SiC and metal remain separate

Tiny metal filaments form

Dies fracture because of failure

SiC and metal remain separate

Tiny metal filaments form

- ► Dies fracture because of failure

- SiC and metal remain separate

- ► Tiny metal filaments form

- Dies fracture because of failure

- SiC and metal remain separate

- ► Tiny metal filaments form

Institute

- ► Dies fracture because of failure

- SiC and metal remain separate

- ► Tiny metal filaments form

Fail-to-short behaviour possible with SiC

Outline

Introduction

# Power Module Design & Manufacturing

Test of the Failure Mode

Conclusions

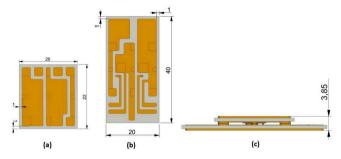

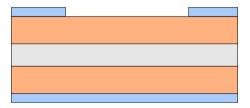

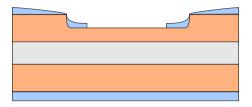

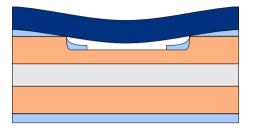

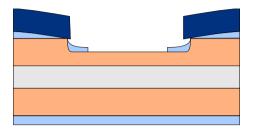

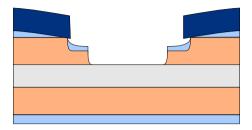

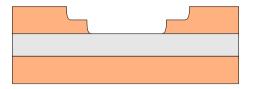

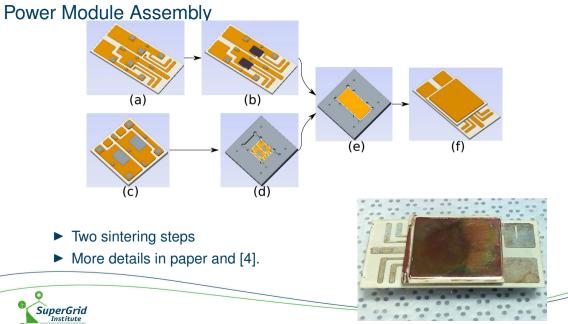

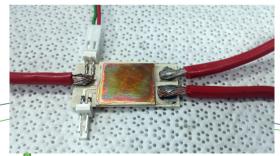

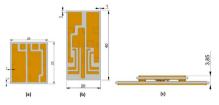

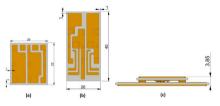

#### Module Structure

- "Sandwich structure": massive interconnects

- Silver sintering: high temperature bonding

- Salient features: for topside contact with dies

- Two SiC MOSFETs: multi-chip module (half -bridge config.)

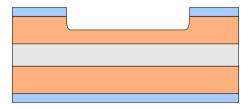

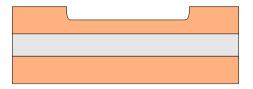

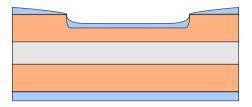

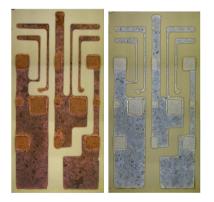

#### ► DBC with 500 µm copper, 500 µm Al<sub>2</sub>O<sub>3</sub>

- Halfway-etching to form protrusions

- Second etching step to form circuit

- ► Ag finish

- ► DBC with 500 µm copper, 500 µm Al<sub>2</sub>O<sub>3</sub>

- Halfway-etching to form protrusions

- Second etching step to form circuit

- ► Ag finish

- ► DBC with 500 µm copper, 500 µm Al<sub>2</sub>O<sub>3</sub>

- Halfway-etching to form protrusions

- Second etching step to form circuit

- ► Ag finish

- ► DBC with 500 µm copper, 500 µm Al<sub>2</sub>O<sub>3</sub>

- Halfway-etching to form protrusions

- Second etching step to form circuit

- ► Ag finish

- ► DBC with 500 µm copper, 500 µm Al<sub>2</sub>O<sub>3</sub>

- Halfway-etching to form protrusions

- Second etching step to form circuit

- ► DBC with 500 µm copper, 500 µm Al<sub>2</sub>O<sub>3</sub>

- Halfway-etching to form protrusions

- Second etching step to form circuit

- ► Ag finish

- ► DBC with 500 µm copper, 500 µm Al<sub>2</sub>O<sub>3</sub>

- Halfway-etching to form protrusions

- Second etching step to form circuit

- ► Ag finish

- ► DBC with 500 µm copper, 500 µm Al<sub>2</sub>O<sub>3</sub>

- Halfway-etching to form protrusions

- Second etching step to form circuit

- ► Ag finish

- ► DBC with 500 µm copper, 500 µm Al<sub>2</sub>O<sub>3</sub>

- Halfway-etching to form protrusions

- Second etching step to form circuit

- ► Ag finish

- DBC with 500 μm copper, 500 μm Al<sub>2</sub>O<sub>3</sub>

- Halfway-etching to form protrusions

- Second etching step to form circuit

► Ag finish

SuperGrid

- ► DBC with 500 µm copper, 500 µm Al<sub>2</sub>O<sub>3</sub>

- Halfway-etching to form protrusions

- Second etching step to form circuit

- ► Ag finish

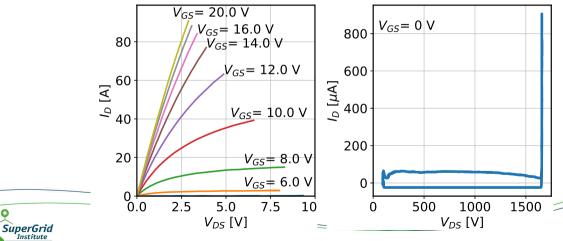

#### **Electrical Validation**

► 4 modules made (7 dies functionnal)

► 3 encapsulation schemes: none/Silicone gel/epoxy

Outline

Introduction

## Power Module Design & Manufacturing

Test of the Failure Mode

#### Conclusions

## Test Setup – 1

| Sample   | Encapsulant | Clamp | Switch |  |

|----------|-------------|-------|--------|--|

| Module A | None        | Yes   | MOS 1  |  |

| Module A | NONE        | 165   | MOS 2  |  |

| Module B | Silicone    | Yes   | MOS 1  |  |

| Module B | Silicone    | 165   | MOS 2  |  |

| Module C | Epoyu       | No    | MOS 1  |  |

| Module C | Ероху       | INU   | MOS 2  |  |

| Module D | Silicone    | Yes   | MOS 1  |  |

|          | Silicone    | 165   | —      |  |

- Dies tested individually

- "Clamp" used for modules A, B and D

- MOS 2 of module D not connected

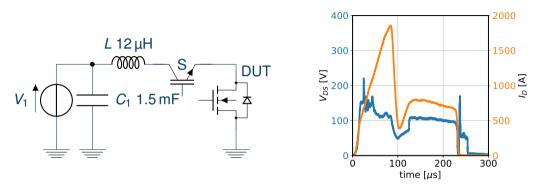

Test Setup – 2

Short circuit test for various energy levels (1 to 20 J)

- Inductance consequence of tester wiring

- Activation of protection switch S causes complex waveforms

#### Test Setup – 3

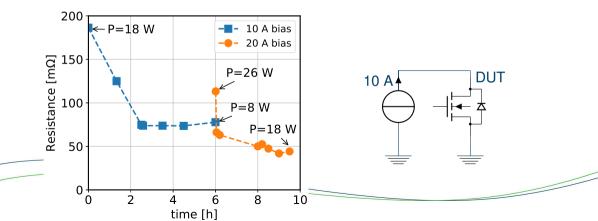

- After failure, modules are biased for 6 h at 10 A

- Short-circuit failure mode considered stable if R<sub>final</sub> < R<sub>init</sub>

- In some cases longer test, with 20 A

#### Results

|   | Encapsulant | Clamp | Switch | E<br>[J] | <b>R<sub>init</sub></b><br>[mΩ] | <b>R<sub>final</sub></b><br>[mΩ] | Failure<br>mode |

|---|-------------|-------|--------|----------|---------------------------------|----------------------------------|-----------------|

| Α | None        | Yes   | MOS 1  | —        | 186                             | 77                               | SC              |

|   |             |       | MOS 2  | 8.8      | 201                             | 128                              | SC              |

| В | Silicone    | Yes   | MOS 1  | 20       | 165                             | 120                              | SC              |

|   |             |       | MOS 2  | 1        | 188                             | 167                              | SC              |

| С | Ероху       | No    | MOS 1  | 9.7      | _                               | _                                | OC              |

|   |             |       | MOS 2  | —        | —                               | —                                | _               |

| D | Silicone    | Yes   | MOS 1  | 2.24     | 180                             | 158                              | SC              |

|   |             |       | _      | —        | _                               | —                                | _               |

Module C separated during first test, causing open circuit

All other modules exhibited stable short circuit

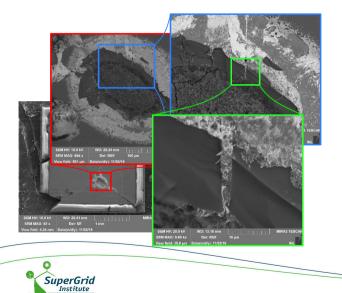

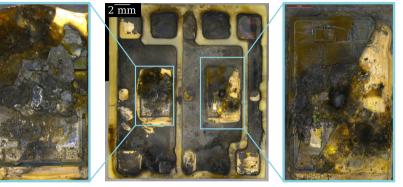

#### Analysis

- Dies largely broken because of short circuit

- Change in color, oxydation of module

- caused by high temperature during stability test

- Metal inflitrated in SiC cracks

Outline

Introduction

Power Module Design & Manufacturing

Test of the Failure Mode

#### Conclusions

#### Conclusions - 1

Sandwich module proposed for fail-to-short behaviour

- Relatively simple manufacturing process

- Silver sintering as single bonding material

- No degradation of SiC dies performance observed

- Allows for dual-side cooling

#### Short-circuit test up to 2000 A

- "Clamped" modules were found to fail in short-circuit

- Stable short-circuits observed after 6 h

- Final resistances 3-7 times higher than R<sub>pSm</sub> of SiC MOSFETs

#### Conclusions - 1

SuperGria

Sandwich module proposed for fail-to-short behaviour

- Relatively simple manufacturing process

- Silver sintering as single bonding material

- No degradation of SiC dies performance observed

- Allows for dual-side cooling

- Short-circuit test up to 2000 A

- "Clamped" modules were found to fail in short-circuit

- Stable short-circuits observed after 6 h

- ► Final resistances 3-7 times higher than *R*<sub>DSon</sub> of SiC MOSFETs

19/22

#### Conclusions – 2

Fail-to-Short behaviour with SiC dies requires:

- ► To prevent the Ceramic tiles from separating

- → Need for strong mechanical clamp/frame

- → Soft encapsulant probably better for gases to escape

- ► To provide massive interconnects:

- Wirebonds would act as fuses

- Need to supply metal to fill the cracks in the dies

- Heat dissipation at failure points help reducing the resistance

#### Conclusions – 2

Fail-to-Short behaviour with SiC dies requires:

- To prevent the Ceramic tiles from separating

- → Need for strong mechanical clamp/frame

- ➔ Soft encapsulant probably better for gases to escape

- ► To provide massive interconnects:

- Wirebonds would act as fuses

- Need to supply metal to fill the cracks in the dies

- Heat dissipation at failure points help reducing the resistance

# Bibliography I

- I. Yaqub, *Investigation into stable failure to short circuit in IGBT power modules*. Phd thesis, University of Nottingham, Nottingham, jul 2015.

- S. Gunturi, J. Assal, D. Schneider, and S. Eicher, "Innovative Metal System for IGBT Press Pack Modules," in *Proceedings of the International Symposium on Power Systems and Devices (ISPSD)*, (Cambridge, UK), p. 4, Apr. 2003.

- I. Dchar, C. Buttay, and H. Morel, "SiC power devices packaging with a short-circuit failure mode capability," *Microelectronics Reliability*, 2017.

- C. Buttay, R. Riva, B. Allard, M.-L. Locatelli, and V. Bley, "Packaging with double-side cooling capability for SiC devices, based on silver sintering," in *44th Annual Conference of the IEEE Industrial Electronics Society (IECON 2018)*, Proceedings of the 44th Annual Conference of the IEEE Industrial Electronics Society (IECON 2018), (Washington, United States), IEEE, Oct. 2018.

#### Thank you for your attention

https://www.supergrid-institute.com

This work was supported by a grant overseen by the French National Research Agency (ANR) as part of the "Investissements d'Avenir" Program (ANE-ITE-002-01).