# High-Voltage SiC-JFET Fabrication and Full Characterization

Besar Asllani, Pascal Bevilacqua, Abderrahime Zaoui, Gregory Grosset,

Dominique Planson, Hervé Morel

## ▶ To cite this version:

Besar Asllani, Pascal Bevilacqua, Abderrahime Zaoui, Gregory Grosset, Dominique Planson, et al.. High-Voltage SiC-JFET Fabrication and Full Characterization. Materials Science Forum, 2019, 963, pp.688-692. 10.4028/www.scientific.net/MSF.963.688 . hal-02060228

HAL Id: hal-02060228

https://hal.science/hal-02060228

Submitted on 7 Mar 2019

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# High-Voltage SiC-JFET Fabrication and Full Characterization

B. Asllani<sup>1, a</sup>, P. Bevilacqua<sup>1, b</sup>, A. Zaoui<sup>1, c</sup>, G. Grosset<sup>2, d</sup>, D. Planson<sup>1, e</sup> and H. Morel<sup>1, f\*</sup>

<sup>1</sup> Univ Lyon, INSA Lyon, CNRS, Ampère, F-69621 Lyon, France <sup>2</sup> ION BEAM SERVICES, F-13790 Peynier, France

<sup>a</sup> besar.asllani@gmail.com, <sup>b</sup> pascal.bevilacqua@insa-lyon.fr, <sup>c</sup> abderrahime.zaoui@insa-lyon.fr, <sup>d</sup> gregory.grosset@ion-beam-services.com,

edominique.planson@insa-lyon.fr, fherve.morel@insa-lyon.fr

**Keywords:** 4H-SiC JFET, device processing, high voltage device, device characterization, double-pulse switching

**Abstract.** 3.3 kV Power JFETs have been designed, fabricated and measured in the framework of the FilSiC project. The paper presents the main characterization results with classical static and dynamic measurements as well as double pulse tests for switching characterization. The study is completed by a data-sheet evaluation for the measured components and an evaluation of the associated safe operating area.

#### Introduction

Silicon Carbide (SiC) enables to develop high-voltage devices. While most of studies concern Power MOSFETs [1][2], the present study focuses on JFETs because of it possible better robustness particularly in short-circuit operation [3]. The targeted JFET rating was selected to 3300 V, 20 A.

The possible applications could include high voltage DC-breakers [4] or Solid State Power Controllers (SSPC) [5] as well as all applications covered by SiC-MOSFETs.

### **Device Processing**

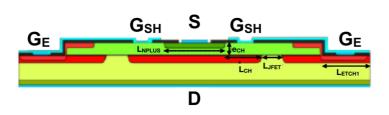

To reach the targeted characteristics a vertical structure with vertical and lateral channels were designed as shown in Fig. 1. The lateral channel enables an easy design with a low absolute value of the gate-source threshold voltage. It is easier to manufacture but yields a higher on-state resistance (R<sub>on</sub>) in comparison with a pure vertical channel. So, an optimization was achieved.

Devices were fabricated on a n-type epitaxial layer with a thickness of 32.7  $\mu$ m and a doping concentration of  $9.7 \times 10^{14}$  cm<sup>-3</sup>. 13 photolithography mask levels were used. A double gate structure was obtained through ion implantation for the buried gate and epitaxial regrowth for the surface gate. The edge termination of the JFETs includes a MESA structure and a junction termination extension (JTE). The front side and back side metalizations are in Ag. The second passivation uses polyimide.

Best dies were diced and packaged to enable high current measurements. The packaging was an optimization of Iso4 standard package made by DeepConcept Company as shown in Fig. 2. The size is the same but the internal design is optimized for SiC and for 3300 V voltage. The package can operate up to 200°C. In this case, the support is a metal one: (Cu, Al + termination Ni, Au, Ag).

#### **Standard Electrical Characteristics**

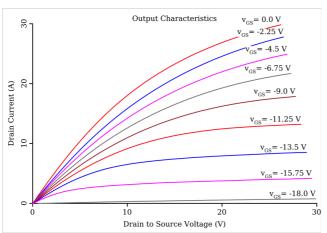

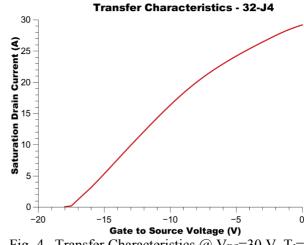

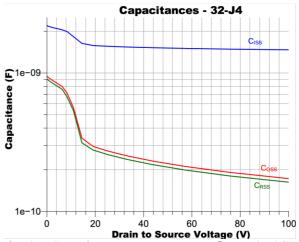

The electrical characterization includes: standard static characteristics as the output characteristic (Fig. 3), the transfer characteristic, dynamic characteristics like Crss, Ciss. For such standard characterization a Keysight B1506A curve tracer was used. Some adapted procedures were developed to fit the normally-on electrical characterization of JFETs. Fig. 3 and 4 show some typical results. The gate threshold voltage is measured in the range -17.2 V to -18.5 V (See Table). As a complement,

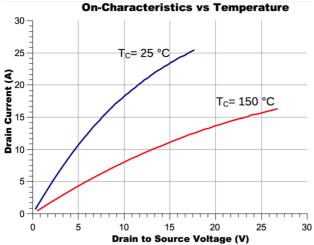

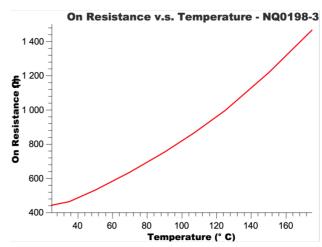

an IWATSU CS-5400 curve tracer was used for measuring the on-resistance versus the temperature. Fig. 5 and 6 show the associated results.

Fig. 1 – Schematic cross section of the JFET structure

Fig. 2 – A JFET die on its package

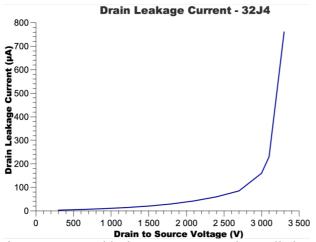

On-resistance varies from about 400 m $\Omega$  to 1.5  $\Omega$  in the range of 25 °C to 180 °C. The measurement temperature was limited to 180 °C because of the package limits, but the SiC-JFET die may operate at higher temperature [7]. The leakage current is shown in Fig. 7. The Drain-source breakdown voltage does not achieve the target value due to a higher dose of implantation of the peripheral protection compared to the aimed one. The capacitance measurements are given in Fig. 8.

Fig. 3 – Output Characteristics @  $25 \,^{\circ}\text{C} - 32\text{-J4}$ , B1506A

Fig. 4 –Transfer Characteristics @  $V_{DS}$ =30 V,  $T_{J}$ = 25 °C, 32-J4, B1506A

Fig. 5 – On Characteristics vs temperature @  $V_{GS}$ = 0 V, 32-J4, IWATSU.

Fig. 6 – On resistance vs temperature @  $V_{DS}$ =30 V,  $V_{GS}$ =0 V, 32-J4, B1506A

#### **Switching Characteristics**

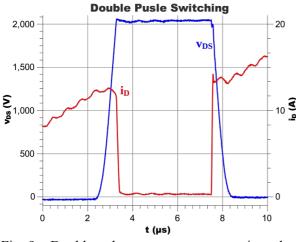

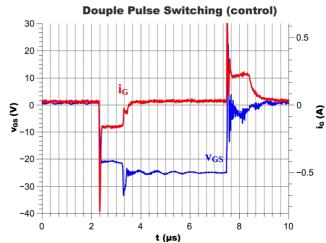

To complete the measurement obtained by industrial characterization product (B1506 and IWATSU CS 1500) Double Pulse Tests (DPT) [8][9] have been achieved. The DPT circuit was adapted to high voltage switching. Some results are shown in Fig. 9 and 10.

Fig. 7 – Measured leakage current v.s. the applied voltage @ 25 °C – 32-J4, B1506A

Fig. 8 – Capacitance measurements @  $T_J$ = 25 °C, 32-J4, B1506A

Fig. 9 – Double pulse test measurements,  $i_D$  and  $V_{DS}$  waveforms (12 A, 2 kV) @ 25 °C

Fig. 10 –Double pulse test measurements,  $i_G$  and  $VG_S$  waveforms (12 A, 2 kV) @ 25 °C

#### **Data Sheet and Safe Operating Area**

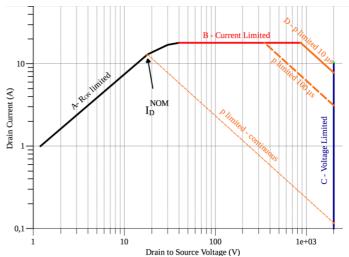

A data sheet table (Table) was built on the based on the 7 measured components. The Safe Operating Area (SOA) was estimated based on the obtained measurements and following a classical computation procedure [10]. The obtained result is shown in Fig. 11.

Acknowledgements: The authors wish to thank for their financial support: the Caisse des Dépôts et Consignations (CDC) and BPI-France (FilSiC: Convention n°O13953-410188).

#### **Summary**

3.3 kV Power JFETs have been designed, fabricated and measured in the framework of the FilSiC project. Some satisfying results have been obtained. However, building demonstrators and converters need further devices and require another founding project.

| Parameter                            | Symbol                      | Conditions                                                               | Min   | Avr      | Max   | Units |

|--------------------------------------|-----------------------------|--------------------------------------------------------------------------|-------|----------|-------|-------|

| Drain-source voltage                 | $v_{\mathrm{DS}}$           |                                                                          |       | 2000     |       | V     |

| Gate-Source voltage                  | V <sub>GS</sub>             |                                                                          |       | -20 to 2 |       | V     |

| Continuous drain current             | $i_{\mathrm{D}}$            | T <sub>J</sub> =150 °C                                                   |       | 13       |       | A     |

| Drain-source breakdown voltage       | $\mathrm{BV}_{\mathrm{DS}}$ | V <sub>GS</sub> = -20 V, T <sub>J</sub> =25 °C, i <sub>D</sub> = 1 mA    | 1950  | 2650     | 3300  | V     |

| Drain-source on-resistance           | $R_{DS}^{ON}$               | $V_{GS}$ = 0 V, $T_{J}$ =25 °C, $i_{D}$ = 5 A                            | 0.49  | 0.52     | 0.58  | Ω     |

| Gate threshold voltage               | $V_{TH}$                    | $V_{DS}$ =20 V, $i_D$ = 100 mA                                           | -18.5 | -18      | -17.2 | V     |

| Input capacitance                    | C <sub>ISS</sub>            | V <sub>GS</sub> = -20 V, V <sub>DS</sub> = 100 V, T <sub>J</sub> =25 °C, |       | 1470     |       | pF    |

| Output capacitance                   | Coss                        |                                                                          |       | 170      |       | pF    |

| Reverse transfer capacitance         | C <sub>RSS</sub>            |                                                                          |       | 160      |       | pF    |

| Thermal resistance, junction-to-case | $R_{TH}^{JC}$               | Estimated                                                                |       | 0.26     |       | °C/W  |

Table 1: Data sheet like synthetic results for the packaged devices.

#### References

- [1] BOLOTNIKOV, Alexander, LOSEE, Peter, MATOCHA, Kevin, et al. 3.3 kV SiC MOSFETs designed for low on-resistance and fast switching. In: Power Semiconductor Devices and ICs (ISPSD), 2012 24th International Symposium on. IEEE, 2012. p. 389-392.

- [2] YAMAMOTO, Shigehisa, NAKAO, Yukiyasu, TOMITA, Nobuyuki, *et al.* Development of 3.3 kV SiC-MOSFET: Suppression of forward voltage degradation of the body diode. In: *Materials Science Forum*. Trans Tech Publications, 2014. p. 951-954.

- [3] BOUGHRARA, Narjes, MOUMEN, Sabrine, LEFEBVRE, Stéphane, *et al.* Robustness of SiC JFET in short-circuit modes. *IEEE Electron device letters*, 2009, vol. 30, no 1, p. 51-53

Fig. 11: Estimated Safe Operating Area of the fabricated JFETs

- [4] KRSTIC, Slobodan, WELLNER, Edward L., BENDRE, Ashish R., *et al.* Circuit breaker technologies for advanced ship power systems. In: *Electric Ship Technologies Symposium, 2007. ESTS'07. IEEE.* IEEE, 2007. p. 201-208.

- [5] GUO, Yuan-Bo, BHAT, Krishna P., ARAVAMUDHAN, Arunkumar, et al. High current and thermal transient design of a SiC SSPC for aircraft application. In: Applied Power Electronics Conference and Exposition (APEC), 2011 Twenty-Sixth Annual IEEE. IEEE, 2011. p. 1290-1297.

- [6] Deep Concept, Tarbes, France, <a href="http://www.deepconcept.fr">http://www.deepconcept.fr</a>

- [7] FUNAKI, Tsuyoshi, BALDA, Juan Carlos, JUNGHANS, Jeremy, et al. Power conversion with SiC devices at extremely high ambient temperatures. IEEE Transactions on Power electronics, 2007, vol. 22, no 4, p. 1321-1329.

- [8] CHEN, Zheng, BOROYEVICH, Dushan, BURGOS, Rolando, *et al.* Characterization and modeling of 1.2 kv, 20 A SiC MOSFETs. In: *Energy Conversion Congress and Exposition, 2009. ECCE 2009. IEEE.* IEEE, 2009. p. 1480-1487.

- [9] Hatem Garrab, B. Allard, H. Morel, kaiçar Ammous, Sami Ghedira, Adel Amimi, Kamel Besbes, Jean-Michel Guichon, « On the Extraction Procedure of PIN diode Design Parameters for validation of Integrated Power Converter Design », special issue on integrated power electronics, IEEE Trans. On Power Electronics, Vol. 20, No. 3, pp. 660-670, 2005. [hal-00140858], doi: 10.1109/TPEL.2005.846544

- [10] Infineon OptiMOS TM Power MOSFET Datasheet Explanation, Application Note AN 2012-03 V1.1 March 2012