### Nano-Subsidence-Assisted Precise Integration of Patterned Two-Dimensional Materials for High-Performance Photodetector Arrays

Song-Lin Li, Lei Zhang, Xiaolan Zhong, Marco Gobbi, Simone Bertolazzi, Wei Guo, Bin Wu, Yunqi Liu, Ning Xu, Weiyu Niu, et al.

### ▶ To cite this version:

Song-Lin Li, Lei Zhang, Xiaolan Zhong, Marco Gobbi, Simone Bertolazzi, et al.. Nano-Subsidence-Assisted Precise Integration of Patterned Two-Dimensional Materials for High-Performance Photodetector Arrays. ACS Nano, 2019, 10.1021/acsnano.9b00889. hal-02054651

### HAL Id: hal-02054651 https://hal.science/hal-02054651

Submitted on 1 Mar 2019

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### Nano-Subsidence Assisted Precise Integration of Patterned Two-Dimensional Materials for High-Performance Photodetector Arrays

Song-Lin Li, \*,1,2,5,6 Lei Zhang,<sup>1</sup> Xiaolan Zhong,<sup>1</sup> Marco Gobbi,<sup>1</sup> Simone Bertolazzi,<sup>1</sup> Wei Guo,<sup>3</sup> Bin Wu,<sup>3</sup> Yunqi Liu,<sup>3</sup> Ning Xu,<sup>2</sup> Weiyu Niu,<sup>4</sup> Yufeng Hao,<sup>4,5,6</sup> Emanuele Orgiu, \*,1,§ Paolo Samorì \*,1

<sup>1</sup>University of Strasbourg, CNRS, ISIS UMR 7006, 8 allée Gaspard Monge, F-67000 Strasbourg, France

<sup>2</sup>School of Electronic Science and Engineering, Nanjing University, Nanjing 210023, China

<sup>3</sup>Beijing National Laboratory for Molecular Sciences, Institute of Chemistry, Chinese Academy of Science, Beijing 10086, China

<sup>4</sup>College of Engineering and Applied Sciences, Nanjing University, Nanjing 210023, China

<sup>5</sup>National Laboratory of Solid State Microstructures, Nanjing University, Nanjing 210093, China

<sup>6</sup>Collaborative Innovation Center of Advanced Microstructures, Nanjing University, Nanjing 210093, China

§ Present address: Institut national de la recherche scientifique (INRS), EMT Center, 1650 Blvd. Lionel-Boulet, J3X 1S2 Varennes, Canada

<sup>\*</sup> Address correspondence to <u>sli@nju.edu.cn</u> (S.L.L), <u>emanuele.orgiu@emt.inrs.ca</u> (E.O.), <u>samori@unistra.fr</u> (P.S.)

#### ABSTRACT

The spatially precise integration of arrays of micro-patterned two-dimensional (2D) crystals onto three-dimensionally structured Si/SiO<sub>2</sub> substrates represents an attractive, low-cost system-on-chip strategy towards realization of extended functions in silicon microelectronics. However, the reliable integration of such atomically thin arrays on planar patterned surfaces has proved challenging due to their poor adhesion to underlying substrates, as ruled by weak van der Waals interactions. Here we report on an integration method utilizing the flexibility of the atomically thin crystals and their physical subsidence in liquids, which enables reliable fabrication of the micro-patterned 2D materials/Si arrays. Our photodiode devices display peak sensitivity as high as 0.35 A/W and external quantum efficiency (EQE) of ~90%. The nano-subsidence technique represents a viable path to on-chip integration of 2D crystals onto silicon for advanced microelectronics.

#### **KEYWORDS**

Two-dimensional materials, graphene, optoelectronics, on-chip integration, photodiodes, heterojunctions, four-quadrant arrays.

With Moore's law reaching its limit,<sup>1</sup> the semiconductor industry is urgently searching for innovative strategies to go beyond standard microelectronics. One of the most intriguing strategies in modern electronics, referred to as system-on-chip (SoC) for more-than-Moore electronics,<sup>2-4</sup> aims to integrate various active modules in individual chips wherein different functional materials are combined with standard silicon technology. This hybrid approach enables the introduction of extended functionalities such as data storage, sensing, communication and self-powering to conventional logic modules, therefore expanding the current capabilities of logic microelectronics. In this context, two-dimensional (2D) atomic crystals,<sup>5-9</sup> which include a vast library of materials with each one featuring distinctive physical and electronic properties, have emerged as outstanding candidates for integration into silicon to create hybrid devices with different capabilities.<sup>10</sup>

For the purpose of SoC application, different materials are required to be heterointegrated onto silicon through direct contact or interconnection.<sup>4</sup> Previous reports revealed that 2D crystals could be directly transferred onto three-dimensionally structured silicon for energy harvesting,<sup>11-13</sup> photonics,<sup>14-17</sup> and electronics,<sup>18</sup> providing evidence for their potential as on-chip functional modules. In particular, graphene/Si heterojunctions have been employed as photodetectors, working either as photoconductors, with responsivity up to  $10^5$  A/W but unfavorably high dark current,19 or as photodiodes, with above 65% peak external quantum efficiency  $(EQE).^{20}$ However, in such experiments the cumbersome fabrication process following the 2D crystal transfer needs to be minimized, since the atomically thin 2D crystals are prone to shear from or even to come off the substrates during microfabrication processing, such as photoresist deposition and pattern development. These fabrication issues severely hamper the applicability of patterning large 2D sheets into micrometric functional arrays as active SoC components. For these reasons, to date such hybrid devices are mostly restricted to large 2D sheets forming individual active units; the precise and stable integration of arrays of micro-patterned 2D crystals for advanced electronics has been rare.

Here, we devised a nano-subsidence integration method which enables spatially precise and high-yield integration of arrays of micro-patterned 2D crystals onto threedimensional substrates, *e.g.* patterned Si/SiO<sub>2</sub> surfaces. Such method enables the fabrication of high performance arrays of photodetectors. As a proof of concept,  $2 \times 2$  type four-quadrant 2D crystal/Si diodes used as photodetectors are demonstrated. By engineering the work function of graphene and the optical antireflection, our photodetectors exhibit high peak sensitivity up to 0.35 A/W (EQE of  $\sim$ 90%) at 480 nm, as well as high spatial uniformity. Depending on the optical wavelength range, the overall system performances are comparable to or higher than those of commercial silicon diode-based photodetectors.

#### **RESULTS AND DISCUSSION**

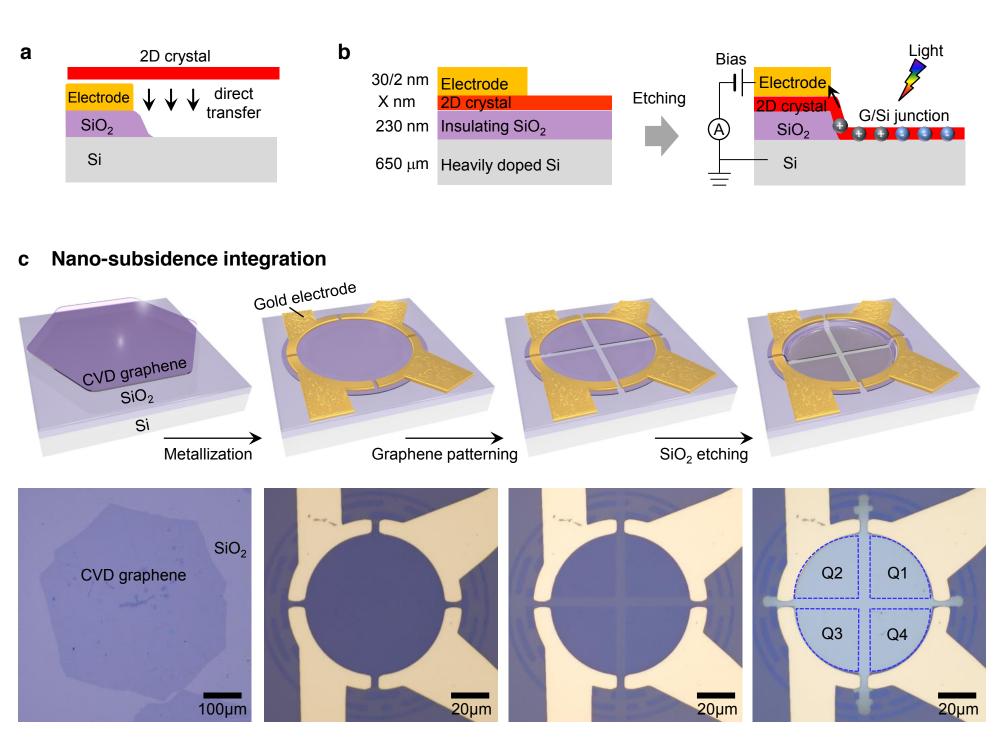

The conventional method for integrating 2D crystals into silicon-based technology consists in their direct transfer onto three-dimensionally predefined Si/SiO<sub>2</sub> substrates,<sup>11-21</sup> as portrayed in Fig. 1a. In this approach, the SiO<sub>2</sub> capping above silicon is used as both sacrificial and insulating layer. Selected SiO<sub>2</sub> sacrificial areas are pre-etched to form a cavity for conformal contact between the 2D crystals and underlying silicon, where the exposed silicon serves as active functional region and the remaining SiO<sub>2</sub> around the cavity works as insulating layer for external wiring, resulting in stepwise substrate surfaces.<sup>22</sup> When 2D crystals are transferred over patterned surfaces, they have to physically adapt to the pattern in relief. Since the large sheets of 2D crystals cannot uniformly land on the top part(s) of the relief(s) and on the surface during the mechanical transfer process, which usually results in the emergence of physical corrugations and bubbles<sup>23,24</sup> and, consequently, the poor adhesion between 2D crystals and substrates. Moreover, when transferring the 2D crystals entirely over the patterned silicon cavities, they tend to trap soluble impurities and to contaminate the junction interface after heat dry. The overall weak substrate adhesion could cause 2D crystals to slide or even to be removed in the subsequent lithography processing necessary for patterning the 2D crystals or defining the microelectrodes. As a result, it is extremely challenging to obtain clean 2D crystal/Si interfaces.

To address the above-mentioned challenges, we have conceived the nanosubsidence integration method that allows a high-yield hetero-integration (Fig. 1b). The method relies on the metallization before the 2D crystal patterning and SiO<sub>2</sub> etching, in order to use the solid electrodes as anchoring bars to prevent the 2D crystals from sliding during the following processing. The alignment among 2D crystals, electrodes, and step edges can then be accurately defined through photolithography, ensuring high spatial precision during the hetero-integration. Besides, the target substrates of transferred 2D crystals are preserved flat, which helps to expel the liquid transfer media smoothly. The third consideration is to etch the SiO<sub>2</sub> sacrificing areas in the last fabrication step and the arrays of micro-patterned 2D crystals can gently subside, taking advantage of the flexibility of the ultrathin 2D crystals, and adapt to the stepwise substrates with negligible strain and improved adhesion (Supplementary Fig. S3). An additional bonus to form the heterojunctions in the last step also includes the minimized time of air exposure of bare silicon and the preserved fresh silicon surface. Hence, such protocol offers great flexibility in further interface engineering between silicon and 2D crystals.

Figure 1c sketches the individual processing steps of the integration technique while showing corresponding optical microscopy images. First, the large-area CVD graphene is transferred onto a flat SiO<sub>2</sub>/Si substrate. Graphene adheres well to the substrate thanks to the large contact area and the superior flatness of the pristine SiO<sub>2</sub> surface. Metal electrodes with a given pattern are then deposited onto graphene through a standard photolithographic process followed by thermal evaporation of the metal and a lift-off step. Afterwards, graphene is patterned through photolithography and oxygen plasma etching. Finally, the SiO<sub>2</sub> layer in the device active region is wet etched *via* a photoresist mask, so that the graphene layers gently fall down and make contact to the exposed silicon. After thoroughly rinsing in deionized water, the samples are dried out in vacuum to expel the encapsulated water between graphene and silicon. By means of the capillary action formed during the vacuum evaporation of the found that the crystal/Si adhesion is readily wetting-enhanced and is much superior to that formed in the simple dry transfer.

As a proof of concept, we apply this method to demonstrate a four-quadrant graphene/Si photodiode detector, a typical beam position sensing module widely used as collimators and many other adjustment sensors in fiber communication and space guidance.<sup>25-27</sup> The yield of the subsidence integration of graphene to silicon was considerably high: 34 out of 36 quadrants were attained without obvious rupture or folding of graphene, thereby attesting a yield as high as 94 % (supplementary Fig. S2). We note that our approach is extremely versatile and the prototypical 2×2 array fabricated here (Fig. 1c) can be easily upgraded into more complicated arrays/devices.

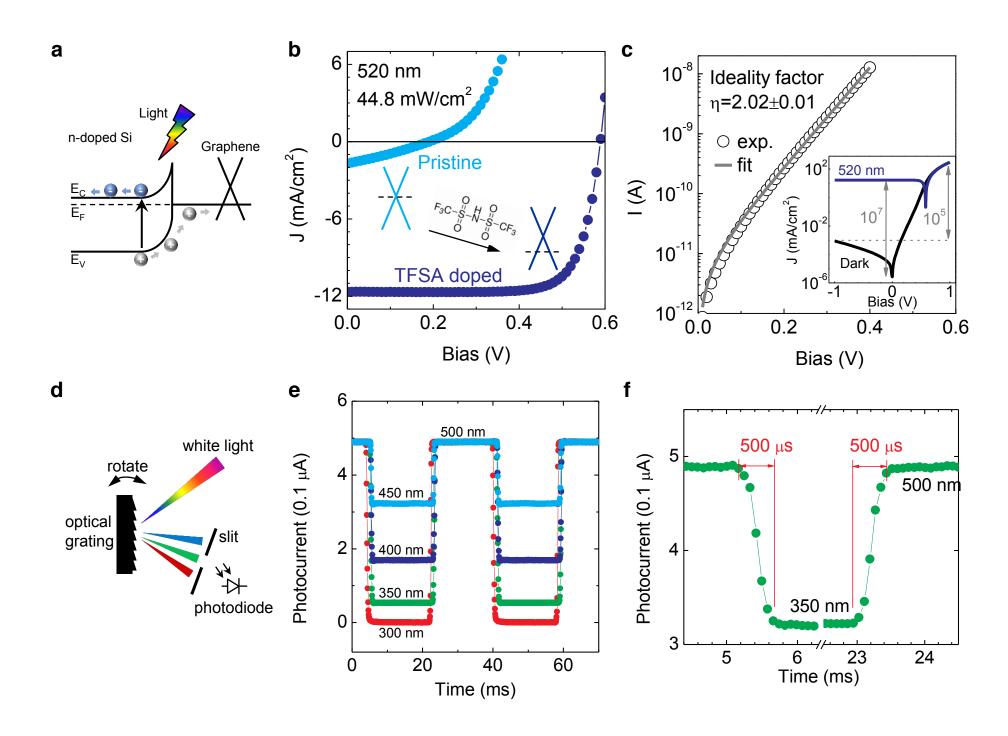

Alongside the use of the subsidence integration method, we have paid particular attention towards the engineering energy levels of graphene which is known to be essential for attaining high photosensing performance.<sup>11,13</sup> Figure 2a depicts the energy level alignment and working principle of the graphene/Si photodiodes. The electron-hole pairs are first generated by light irradiation on silicon; then holes drift into graphene assisted by the built-in electric field at the graphene/Si interface. Hence,

the built-in electric field is the driving force for carrier separation and a high built-in electric field would be favorable for this process. In addition, a large interfacial barrier helps to block the drift of electrons to graphene, reducing the carrier recombination in graphene.

A high-quality CVD graphene<sup>28</sup> with an intrinsic carrier mobility of 2800 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> (supplementary Fig. S5d) was used in this work. To increase the interfacial barrier, we implement p-type doping of graphene via spin-coating a thin layer of bis(trifluoromethanesulfonyl)amide (TFSA, [CF3SO2]2NH, inset of Fig. 2b), a strong electron-withdrawing molecule.<sup>13,29</sup> In contrast to the weak doping effect by ambient oxygen and water molecules  $^{30}$  with a shift of charge neutrality point of 17 V (supplementary Fig. S5a), the TFSA doping determines a larger shift of ~270 V (supplementary Fig. S6c). Such a large shift corresponds to a rather high surface doping concentration of  $6.5 \times 10^{13}$  cm<sup>-2</sup> and a work function increase of 0.75 eV in graphene, as estimated through the equation  $\varepsilon_{\rm F} = \hbar \cdot v_{\rm F} \cdot \sqrt{\pi n}$ , where  $\varepsilon_{\rm F}$ ,  $v_{\rm F}$ , n, and  $\hbar$ denote Fermi energy, Fermi velocity, carrier concentration, and reduced Planck constant, respectively. The strong doping caused an effective interfacial barrier of 0.79 eV (supplementary Fig. S10d). Accordingly, improved photovoltaic behavior was achieved, as confirmed in Fig. 2b by the current-voltage (I-V) characteristics of the pristine and doped devices. TFSA-doped devices exhibited highly enhanced opencircuit voltage ( $V_{OC}$ ), short-circuit current ( $I_{SC}$ ), and fill factor (FF), indicating the critical role of the interfacial barrier on the photovoltaic performance. In Fig. 2c, we analyzed the *I-V* behavior of the doped device under dark condition, which reveals a good ideality factor of  $2.02\pm0.01$  and a high rectification ratio of  $10^5$  in the bias range of  $\pm 1$  V, suggesting an excellent photodiode junction quality. The excellent junction quality is also corroborated by the photovoltaic tests. Before antireflection coating, the doped device shows high photovoltaic efficiencies of 10.1% and 9.1% under 520 nm/43.5 mW·cm<sup>-2</sup> and AM1.5 conditions, respectively (supplementary Fig. S12 a and c), consistent with the literature results.<sup>11-13</sup> The series resistance ( $R_s$ ) value was estimated to be 0.26  $\Omega/cm^2$  for the 100×100  $\mu m^2$  device, which shows a reduction of at least 57% when compared with previously reported values (from 0.61 to 1.38  $\Omega/cm^2$ ) obtained on devices fabricated by direct transfer.<sup>11</sup>

We have also measured the response speed of the photodiode under a monochromatic light source. Figure 2d shows a diagram of the piezoelectrically controlled monochromator used in our experiments. The angle of the incoming light from the Xenon lamp is fixed while the angle of reflection beam and the resulting wavelength of the outcoming beam through the slit would change upon piezoelectrical rotation of the optical grating. Since the light power varies with wavelength (the characteristic spectrum of the system is given in supplementary Fig. S13), a modulated photoelectric response would be observed with changing the optical wavelength. Figure 2e displays the modulated photocurrent modes when the incident light wavelength changes from 500 nm to 300, 350, 400 and 450 nm, respectively. At shorter time scales (Fig. 2f) both the rise and decay time are within 500 µs, which represents the fastest signal that can be detected through our experimental setup limited by the millisecond-scale piezoelectric response rate of the grating driver. Hence, the response speed of our devices, of at least 500 µs, certainly represents an underestimate. Generally, the response time would be longer if the density of interfacial states and charge trapping centers were sizeable. The fast response featured by the devices made with our nano-subsidence method suggests that the graphene/Si interface of the photodiodes is of high quality.

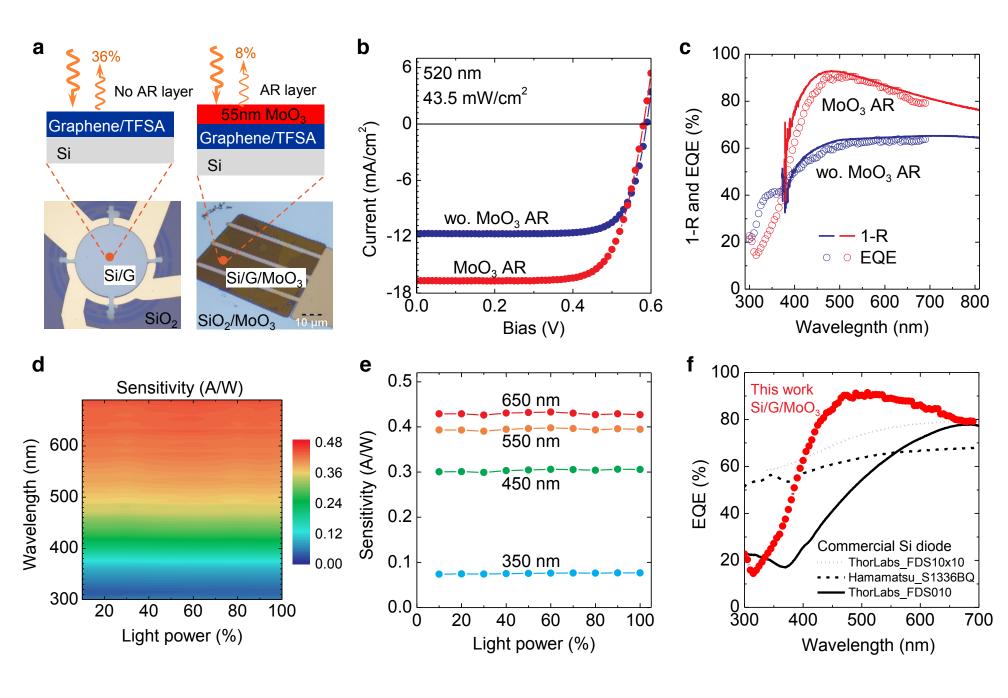

In order to further optimize the performances of our photodiodes, we have employed a surface antireflection capping. This is commonly employed to increase the optical absorption of photodiodes by depositing single or multiple optically transparent antireflection dielectrics.<sup>11,31-35</sup> According to the principle of optical destructive coherence, the reflection rate for a certain light will be minimized when a single antireflective capping layer satisfies the double conditions that  $n_{AR} = \sqrt{n_{air}n_{si}}$ and  $d_{AR} = \lambda/4n_{AR}$ ,<sup>32</sup> where  $n_{AR}$ ,  $n_{air}$ , and  $n_{si}$  are the refractive indices of the antireflective capping layer, air and silicon, respectively, and  $d_{AR}$  and  $\lambda$  are the thickness of the capping layer and the incident light wavelength. Given the atomic thickness of the 2D layers and the low formation energies of lattice defects that make them prone to damages generated by external high-energy atoms,36-38 capping layers grown via aggressive deposition methods (e.g. sputtering) should be avoided. Towards this end, we have used thermally evaporated MoO<sub>3</sub> as the capping layer,<sup>34,35</sup> and the damage to 2D layers are expected to be minimized. The values of  $n_{MoO3}$  are close to those of  $\sqrt{n_{air}n_{si}}$  in most range of visible light (supplementary Fig. S8), suggesting that it is a suitable antireflection material. By theoretical calculations, we also confirmed that the effect of graphene on optical absorption is negligible due to its atomic thickness (supplementary Fig. S9).

Figure 3a sketches the device cross section of pristine *versus* capped devices and their related optical images. Micro-area reflection measurement revealed that the

reflectivity is largely reduced from 36% to 8% at  $\lambda = 520$  nm upon the use of a capping layer of 55-nm MoO<sub>3</sub>. The reduction of the optical reflection is also corroborated by the difference in brightness of the optical images of the pristine and capped Si/graphene stacks, where a lower brightness is observed in the latter (around orange dot in the lower panels of Fig. 3a). As a result, the photoresponse of the devices is enhanced. Under 43.5 mW/cm<sup>2</sup> illumination at 520 nm, the photocurrent increases from 11.6 to 16.7 mA/cm<sup>2</sup> (Fig. 3b). The effect of the MoO<sub>3</sub> antireflective capping is further analyzed by correlating micro-area reflection spectra to the EQE of our devices. Here EQE is estimated by EQE =  $\frac{J_{ph}hC}{eP\lambda}$  where  $J_{ph}$  is the photocurrent density, C is the speed of light within vacuum, e is the elementary charge, P is the light power. The EQE data was extracted from the photocurrent spectrum recorded between 320 to 690 nm. The open blue and red circles in Fig. 3c compare the EQE before and after deposition of a 55-nm-MoO<sub>3</sub> capping layer. As expected, the capping enhances (or reduces) the EQE around  $\lambda = 480$  (or  $\lambda = 320$  nm), in agreement with the interference conditions at the corresponding wavelengths (supplementary Fig. S9c). In Fig. 3c, we also compare the EQE with device absorption rate (1-R, with R the reflectivity) as measured by micro-area reflection. The EQE lines follow closely with the absorption rates, suggesting a near-unity internal quantum efficiency (IQE) since IQE=EQE/(1-R). In the experiments, the peak IQE reaches 90% at 480 nm, approaching the ideal unitary IQE of the photodiodes.<sup>32</sup> The  $\sim 10\%$  reduction to the ideal values (supplementary Fig. S9, c and d) stems likely from local variations of refractive index in the MoO<sub>3</sub> capping layer caused by the presence of pinholes or oxygen loss. The extremely high IEQ achieved here corroborates again the high integration quality of the arrays via our nano-subsidence method.

The photocurrent properties of the capped devices were extensively characterized by varying the optical wavelength and power. Figure 3d plots the photoelectric sensitivity *versus* the two parameters of light wavelength and power. Despite of strong dependence on light wavelength, the sensitivity is basically power independent within the measurement range of optical power (from 10% to 100%) since the devices show negligible saturation in photoresponse below 100% power (Fig. 3e). To evaluate the potential of the nano-subsided photodiodes as a system-on-chip module, we also compare the EQE of our devices in Fig. 3f and Table 1 with currently commercial photodiodes based on silicon pn junctions (ThorLabs FDS010 and FDS10×10, Hamamatsu S1336BQ). Notably, our devices are superior to their commercial counterparts in the visible region from 400 to 700 nm, therefore representing a prototypical high-performance system-on-chip module for the beyond-silicon circuitry.

Table 1 Comparison of EQE performance of nano-subsidence fabricated graphene/Si photodiode with typical commercial silicon photodiodes at different wavelength values. The values in parentheses show the EQE difference of the commercial devices as compared to our graphene/Si device.

| Photodiode                            | EQE<br>@ 350 nm  | EQE<br>@ 450 nm | EQE<br>@ 500 nm | EQE<br>@ 550 nm | EQE<br>@ 650 nm |

|---------------------------------------|------------------|-----------------|-----------------|-----------------|-----------------|

| This work                             | 27.2%            | 84.2%           | 90.3%           | 89.0%           | 86.2%           |

| ThorLabs<br>FDS10×10<br>(UV enhanced) | 58.9%<br>(+117%) | 68.6%<br>(-19%) | 73.6%<br>(-18%) | 76.5%<br>(-14%) | 79.0%<br>(-18%) |

| Hamamatsu<br>S1336BQ<br>(UV enhanced) | 56.1%<br>(+106%) | 60.8%<br>(-28%) | 63.7%<br>(-29%) | 65.7%<br>(-26%) | 67.5%<br>(-22%) |

| ThorLabs<br>FDS010                    | 19.0%<br>(-30%)  | 40.8%<br>(-52%) | 54.2%<br>(-40%) | 64.5%<br>(-28%) | 76.8%<br>(-11%) |

The overall superior optoelectronic performance can be understood as follows. First, defects and surface states, though they determine the surface recombination velocity, are not the most important factors responsible for the carrier separation process during light harvest, since many defective photovoltaic materials can also afford excellent optoelectronic performance, such as polycrystalline silicon and porous perovskites. Instead, the matching of different energy levels between different electronic functional layers seems more crucial for attaining high performance, by forming appropriate built-in electric field for carrier separation and Ohmic electrode contacts for carrier extraction. As have been shown in Fig. 2b, the graphene/Si systems are extremely sensitive to the alignment of energy levels and the shape of the *I-V* curve is greatly improved after applying the dopant TFSA on graphene. Second, it has been reported that surface passivation can take place when immersing the Si substrates into HF-contained solution due to the saturation of dangling Si bonds at the surface.<sup>39</sup> Thus, the unintentional Si surface passivation in the BOE etching step may

also contribute to the high performance. Third, the high carrier mobility of the graphene electrodes helps to collect the separated carriers effectively, which is also likely one of the origins for the high performance.

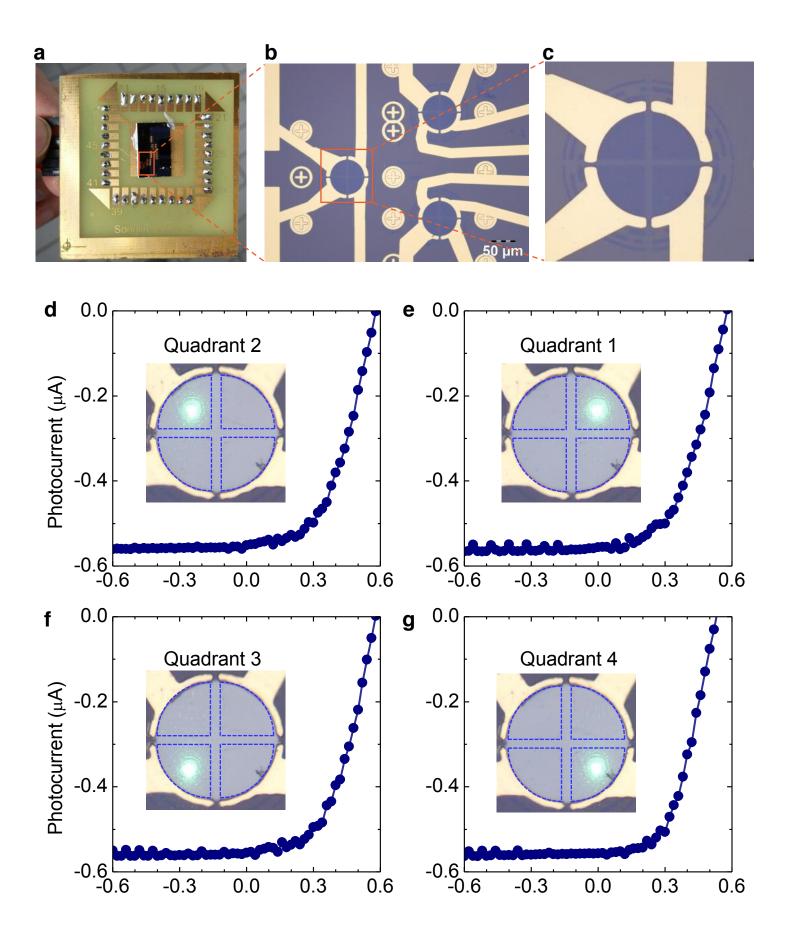

To assess the photoresponse uniformity of individual array units, we mounted our samples onto a test printed circuit board (PCB) (Fig. 4a). In order to have a reliable (wire) bonding to device electrodes, no MoO<sub>3</sub> capping layer is deposited in this test. Figures 4b and 4c show enlarged images on local arrays at different magnification ratios where multiple quadrant photodiodes were prepared. During testing, each unit was exposed to a 532-nm focused laser beam with a power of about 10 W/cm<sup>2</sup>. Figures 4d-4f show the corresponding photoelectric curves. Almost identical *I-V* curves were recorded for the four units, with  $I_{SC}$ =0.56±0.08 µA. A slight degradation of the fill factor was observed in all the four *I-V* curves, which is likely due to the effect of ambient moisture on the hygroscopic dopant TFSA during the measurements.

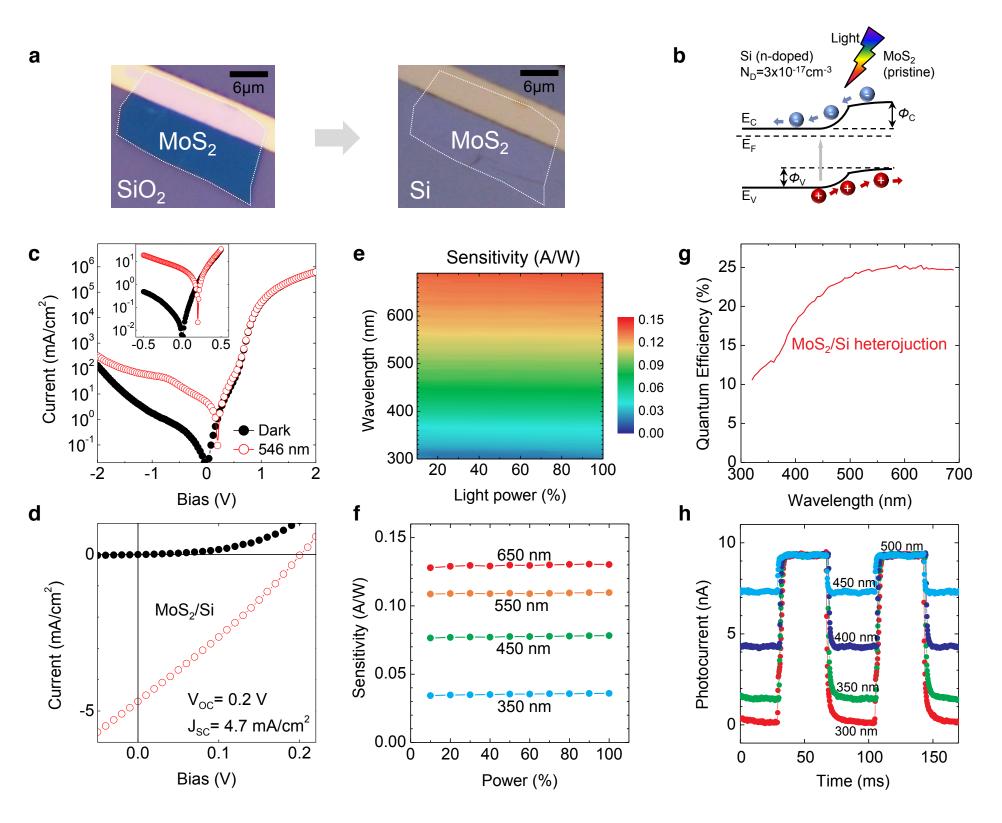

Finally, we have verified the generalization of the nano-subsidence assisted integration method by replacing graphene with another renowned 2D crystal, i.e. molybdenum disulfide (MoS<sub>2</sub>). Figure 5a shows the optical images of a MoS<sub>2</sub>/Si junction before and after SiO<sub>2</sub> etching. A mechanically exfoliated 5-layer-thick MoS<sub>2</sub> was used in this device. Since MoS<sub>2</sub> is normally slightly n-doped, the MoS<sub>2</sub>/Si stack can be regarded as an  $n/n^{++}$  homo-junction with relatively small barrier heights. <sup>32</sup> Figure 5b shows a corresponding band diagram, where  $\Phi_{\rm C}$  and  $\Phi_{\rm V}$  are the barriers for blocking the reverse motions of electrons and holes at the conduction and valence bands, respectively. Owing to smaller  $\Phi_{\rm C}$  and  $\Phi_{\rm V}$  as compared to the case of doped graphene/Si (Fig. 2a), a large number of carriers can drift and recombine, resulting in lower  $V_{OC}$  and  $J_{SC}$  (Fig. 5c) and a reduced fill factor (Fig. 5d). However, in spite of the degraded photoelectric properties with respect to graphene/Si junctions, the MoS<sub>2</sub>/Si junction still exhibited a photoelectric behavior similar to that of smallbarrier diodes in which backward current is enhanced and reasonably high other photoelectric parameters. In particular, a large rectification ratio of  $10^5$  within  $\pm 1$  V (Fig. 5c), notable photoelectric behavior (Figs. 5c and 5d), reasonably high peak EQE of ~25% (Fig. 5g), and fast photoresponse of 1 ms (Fig. 5h) are measured.

#### CONCLUSIONS

We have developed a method enabling the hetro-integration of arrays of atomically thin 2D crystals on planar patterned silicon substrates for system-on-chip electronics. Noteworthy, this integration method combines several advantages. First, the substrate was kept flat in all photolithography steps, which facilitates the subsequent microfabrication processing. Second, high-yield integration of 2D crystals into the stepwise substrate was realized *via* controlled gentle subsidence assisted by capillary forces during vacuum dry, which helps to minimize strain accumulated in the flexible 2D crystals. Third, the exposure of bare silicon surface to air is minimized, resulting in a high quality of electronic interface which, as a result, improves the junction performances. Taking graphene and MoS<sub>2</sub> as model systems, we demonstrated the general applicability of such subsidence method to integrate flexible 2D crystals onto silicon as photodiodes. The photodetector performances surpass those of commercial photodiodes after appropriate device optimization. Not limited to the photoelectric function and materials demonstrated above, the concept of subsidence integration *via* an underlying sacrificial layer could also be extended to wider applications, such as 3D interconnection, optical waveguides, and microfluidic channels, and hence it holds great potential for realizing more versatile modules for the more-than-Moore microelectronics.

#### **METHODS**

Transfer of CVD graphene on flat SiO<sub>2</sub>/Si substrates. Large-area high-quality monolayer graphene was grown on 25  $\mu$ m thick copper foils by CVD.<sup>28</sup> A 20 mg/mL PMMA/chlorobenzene solution was spin-coated on the graphene/copper foils at 3000 rpm for 30 s, which was then heated dry on a hot plate at 180 °C for 1 minute. A PDMS scaffold with a hole of ~10 mm in diameter was gently pressed down onto the PMMA/graphene/copper stacks, with the PDMS scaffold attaching to the stacks. Afterward, the whole stack was placed floating on an ammonium persulfate (0.1 M) solution with the copper face downwards to etch the copper foil. After removing the copper foils, the PDMS/PMMA/graphene stack was rinsed in distilled water for several times and was finally scooped out by a flat SiO<sub>2</sub>/Si substrate. The silicon wafers (from IPMS Fraunhofer Institute, Dresden) were capped with a 90-nm-thick thermally grown SiO<sub>2</sub> dielectric layer and were n-doped to a high level of ~3 × 10<sup>17</sup> cm<sup>-3</sup>.

#### **Device fabrication.**

Optical lithography was performed through a direct laser writing system (LW405B, Microtech Inc.). A thin positive photoresist AZ1505 was used as a mask for graphene patterning and metallization. The exposure resolution is about 1 µm. AZ 726 metal-

ion free developer and dimethyl sulfoxide were used for resist development and liftoff, respectively. To increase the adhesion ability of resist and development, the surface of silicon wafers was modified by thermally evaporated hexamethyldisilazane molecules before applying the resist. The SiO<sub>2</sub> dielectric layers were etched by standard buffered HF etchant (NH<sub>4</sub>F : HF = 6 : 1). The electrodes were realized by thermal evaporation of 1 nm of chromium and 50 nm of gold. The use of chromium adhesion layer is necessary in order to prevent the unwanted lateral etching the SiO<sub>2</sub> underneath electrodes (See also supplementary Fig. S1). The nano-subsidence technique may fail under the following two circumstances. 1) Excessive shaking of the sample during etching or rinsing which may lead to the folding or rupture of 2D crystals; 2) Incomplete SiO<sub>2</sub> surface priming and low adhesion of mask resist to substrates which can result in unwanted SiO<sub>2</sub> etching under mask resist. In case of passivation or modification of silicon interface, liquid immersion techniques are applicable for this nano-subsidence integration,<sup>39,40</sup> while the conventional thermal or gaseous treatments would fail.

#### Characterization and measurements.

All optical images of graphene and devices were taken with an Olympus BX53M microscope. The monochromatic photoelectric characterization was performed with a monochromatic source (model Polychrome V, Till Photonic Inc.) and a Cascade EPS150TRIAX Probe Station inside a nitrogen-filled glovebox. The optical spectrum and its power were calibrated by a PM100A Power Meter (Thorlab) and the related data is shown in supplementary Fig. S13. For the characterization of the integration uniformity of the four-quadrant photodetectors, the device was mounted on a homemade PCB chip carrier which was placed under a focused 532-nm laser beam ( $\sim$ 10 W/cm<sup>2</sup>) from a Renishaw Raman spectroscopy in ambient. A dual-channel sourcemeter Keithley 2636A was used for the electrical characterization.

#### **Author contributions**

S.L.L., E.O. and P.S. conceived the experiment and designed the study. S.L.L. performed the experiments and developed the fabrication method. W.N, Y.H., W.G., B.W, and Y.L. synthesized and provided the CVD graphene sample. S.L.L., E.O. and P.S. co-wrote the paper. All authors discussed the results and contributed to the interpretation of data, as well as contributing to editing the manuscript.

#### Acknowledgment

We acknowledge funding from the European Commission through the Graphene Flagship (GA- 785219), the FET project UPGRADE (GA-309056) and Marie-Curie IEF MULTI2DSWITCH (GA-700802), the M-ERA.NET project MODIGLIANI, the Agence Nationale de la Recherche through the Labex projects CSC (ANR-10-LABX-0026 CSC) and Nanostructures in Interaction with their Environment (ANR-11-LABX-0058 NIE) within the Investissement d'Avenir program (ANR-10-120 IDEX-0002-02), and the International Center for Frontier Research in Chemistry (icFRC). This project is also partially supported by the National Key R&D Program of China (2017YFA0206304) and the National Natural Science Foundation of China (61674080).

**Supporting Information Available:** Experimental details on etching rates of SiO<sub>2</sub> capped by different materials, nano-subsidence integration, intrinsic mobility and contact resistivity of pristine CVD graphene, effect of TFSA doping on CVD graphene, effect of HNO<sub>3</sub> doping on mechanically exfoliated graphene, refractive indices of candidate antireflection capping layers, design of MoO<sub>3</sub> antireflection layer, effect of barrier height ( $\Phi_B$ ) on  $V_{oc}$ , fit of series resistance in the circuit loop of photodiodes, performance as photovoltaic devices, output power and linearity of monochromatic light source. This material is available free of charge *via* the Internet at <u>http://pubs.acs.org</u>.

#### REFERENCE

(1) Waldrop, M. M., The Chips Are down for Moore's Law. *Nature* 2016, 530, 144–147.

(2) Arden, W.; Brillouët, M.; Cogez, P.; Graef, M.; Huizing, B.; Mahnkopf, R., "More-Than-Moore" White Paper. The International Technology Roadmap for Semiconductors, **2010**.

(3) Cavin, R. K.; Lugli, P.; Zhirnov, V. V., Science and Engineering beyond Moore's Law. *Proc. IEEE* 2012, *100*, 1720–1749.

(4) Zhang, G.-Q.; Roosmalen, A. V., *More Than Moore: Creating High Value Micro/nanoelectronics Systems*. Springer, **2009**.

(5) Ferrari, A. C.; Bonaccorso, F.; Fal'ko, V.; Novoselov, K. S.; Roche, S.; Boggild, P.; Borini, S.; Koppens, F. H. L.; Palermo, V.; Pugno, N.; Garrido, J. A.; Sordan, R.; Bianco, A.; Ballerini, L.; Prato, M.; Lidorikis, E.; Kivioja, J.; Marinelli, C.; Ryhanen, T.; Morpurgo, A.; *et al.*, Science and Technology Roadmap for Graphene, Related Two-Dimensional Crystals, and Hybrid Systems. *Nanoscale* **2015**, *7*, 4598–4810.

(6) Koppens, F. H. L.; Mueller, T.; Avouris, P.; Ferrari, A. C.; Vitiello, M. S.; Polini, M., Photodetectors Based on Graphene, Other Two-Dimensional Materials and Hybrid Systems. *Nat. Nanotechnol.* **2014**, *9*, 780–793.

(7) Geim, A. K.; Grigorieva, I. V., Van Der Waals Heterostructures. *Nature* 2013, 499, 419–425.

(8) Wilson, J. A.; Yoffe, A. D., The Transition Metal Dichalcogenides: Discussion and Interpretation of Observed Optical, Electrical and Structural Properties. *Adv. Phys.* **1969**, *18*, 193–335.

(9) Li, S.-L.; Tsukagoshi, K.; Orgiu, E.; Samorì, P., Charge Transport and Mobility Engineering in Two-Dimensional Transition Metal Chalcogenide Semiconductors. *Chem. Soc. Rev.* **2016**, *45*, 118–151.

(10) Sun, Z.; Martinez, A.; Wang, F., Optical Modulators with 2D Layered Materials. *Nat. Photon.* **2016**, *10*, 227–238.

(11) Shi, E.; Li, H.; Yang, L.; Zhang, L.; Li, Z.; Li, P.; Shang, Y.; Wu, S.; Li, X.; Wei, J.; Wang, K.; Zhu, H.; Wu, D.; Fang, Y.; Cao, A., Colloidal Antireflection Coating Improves Graphene-Silicon Solar Cells. *Nano Lett.* **2013**, *13*, 1776–1781.

(12) Li, X.; Zhu, H.; Wang, K.; Cao, A.; Wei, J.; Li, C.; Jia, Y.; Li, Z.; Li, X.; Wu,

D., Graphene-On-Silicon Schottky Junction Solar Cells. *Adv. Mater.* 2010, *22*, 2743–2748.

(13) Miao, X.; Tongay, S.; Petterson, M. K.; Berke, K.; Rinzler, A. G.; Appleton,

B. R.; Hebard, A. F., High Efficiency Graphene Solar Cells by Chemical Doping. *Nano Lett.* 2012, *12*, 2745–2750.

(14) Gan, X.; Shiue, R.-J.; Gao, Y.; Meric, I.; Heinz, T. F.; Shepard, K.; Hone, J.; Assefa, S.; Englund, D., Chip-Integrated Ultrafast Graphene Photodetector with High Responsivity. *Nat. Photonics* **2013**, *7*, 883–887.

(15) Wang, X.; Cheng, Z.; Xu, K.; Tsang, H. K.; Xu, J.-B., High-Responsivity Graphene/silicon-Heterostructure Waveguide Photodetectors. *Nat. Photonics* **2013**, *7*, 888–891. (16) Casalino, M.; Sassi, U.; Goykhman, I.; Eiden, A.; Lidorikis, E.; Milana, S.; De Fazio, D.; Tomarchio, F.; Iodice, M.; Coppola, G.; Ferrari, A. C., Vertically Illuminated, Resonant Cavity Enhanced, Graphene–silicon Schottky Photodetectors. *ACS Nano* **2017**, *11*, 10955–10963.

(17) Wan, X.; Xu, Y.; Guo, H.; Shehzad, K.; Ali, A.; Liu, Y.; Yang, J.; Dai, D.;

Lin, C.-T.; Liu, L.; Cheng, H.-C.; Wang, F.; Wang, X.; Lu, H.; Hu, W.; Pi, X.; Dan,

Y.; Luo, J.; Hasan, T.; Duan, X.; *et al.*, A Self-Powered High-Performance

Graphene/Silicon Ultraviolet Photodetector with Ultra-Shallow Junction: Breaking

the Limit of Silicon? *npj 2D Mater. Appl.* 2017, *1*, 4.

(18) Yang, H.; Heo, J.; Park, S.; Song, H. J.; Seo, D. H.; Byun, K.-E.; Kim, P.; Yoo, I.; Chung, H.-J.; Kim, K., Graphene Barristor, a Triode Device with a Gate-Controlled Schottky Barrier. *Science* **2012**, *336*, 1140–1143.

(19) Liu, J.; Yin, Y.; Yu, L.; Shi, Y.; Liang, D.; Dai, D., Silicon–Graphene Conductive Photodetector with Ultra-High Responsivity. *Sci. Rep.* **2017**, *7*, 40904.

(20) An, X.; Liu, F.; Jung, Y. J.; Kar, S., Tunable Graphene–Silicon Heterojunctions for Ultrasensitive Photodetection. *Nano Lett.* **2013**, *13*, 909–916.

(21) Song, Y.; Li, X.; Mackin, C.; Zhang, X.; Fang, W.; Palacios, T.; Zhu, H.; Kong, J., Role of Interfacial Oxide in High-Efficiency Graphene–silicon Schottky Barrier Solar Cells. *Nano Lett.* **2015**, *15*, 2104–2110.

(22) Xie, C.; Mak, C.; Tao, X.; Yan, F., Photodetectors Based on Two-Dimensional Layered Materials beyond Graphene. *Adv. Funct. Mater.* 2017, *27*, 1603886.

(23) Gao, L.; Ni, G.-X.; Liu, Y.; Liu, B.; Castro Neto, A. H.; Loh, K. P., Face-To-Face Transfer of Wafer-Scale Graphene Films. *Nature* **2014**, *505*, 190–194.

(24) Suk, J. W.; Kitt, A.; Magnuson, C. W.; Hao, Y.; Ahmed, S.; An, J.; Swan, A. K.; Goldberg, B. B.; Ruoff, R. S., Transfer of CVD-Grown Monolayer Graphene onto Arbitrary Substrates. *ACS Nano* **2011**, *5*, 6916–6924.

(25) Roy, S. C.; Kundu, T.; Rao, V. R.; Thundat, T., On-Chip Integration of Photodetector and Sensor: A Multimodal Photonic Device for Sensing Applications. *IEEE Sens. J.* **2017**, *17*, 4773–4780.

(26) Rafí, J.; Pellegrini, G.; Quirion, D.; Hidalgo, S.; Godignon, P.; Matilla, O.; Juanhuix, J.; Fontserè, A.; Molas, B.; Pothin, D.; Fajardo, P., 10μm-Thick Four-Quadrant Transmissive Silicon Photodiodes for Beam Position Monitor Application: Electrical Characterization and Gamma Irradiation Effects. *J. Instrum.* **2017**, *12*, C01004.

(27) Schlesinger, I.; Kuchuk, K.; Sivan, U., An Ultra-Low Noise Optical Head for Liquid Environment Atomic Force Microscopy. *Rev. Sci. Instrum.* **2015**, *86*, 083705.

(28) Guo, W.; Wu, B.; Li, Y.; Wang, L.; Chen, J.; Chen, B.; Zhang, Z.; Peng, L.; Wang, S.; Liu, Y., Governing Rule for Dynamic Formation of Grain Boundaries in Grown Graphene. *ACS Nano* **2015**, *9*, 5792–5798.

(29) Kim, D.; Lee, D.; Lee, Y.; Jeon, D. Y., Work-Function Engineering of Graphene Anode by Bis(trifluoromethanesulfonyl)amide Doping for Efficient Polymer Light-Emitting Diodes. *Adv. Funct. Mater.* **2013**, *23*, 5049–5055.

(30) Ryu, S.; Liu, L.; Berciaud, S.; Yu, Y.-J.; Liu, H.; Kim, P.; Flynn, G. W.; Brus, L. E., Atmospheric Oxygen Binding and Hole Doping in Deformed Graphene on a SiO<sub>2</sub> Substrate. *Nano Lett.* **2010**, *10*, 4944–4951.

(31) Ju, S.; Liang, B.; Wang, J.-Z.; Shi, Y.; Li, S.-L., Graphene/Silicon Schottky Solar Cells: Technical Strategies for Performance Optimization. *Opt. Commun.* **2018**, *428*, 258–268.

(32) Sze, S. M.; Ng, K. K., *Physics of Semiconductor Devices*. 3rd edn., John Wiley & Sons, New Jersey, 2007.

(33) Ho, P.-H.; Lee, W.-C.; Liou, Y.-T.; Chiu, Y.-P.; Shih, Y.-S.; Chen, C.-C.; Su, P.-Y.; Li, M.-K.; Chen, H.-L.; Liang, C.-T.; Chen, C.-W., Sunlight-Activated Graphene-Heterostructure Transparent Cathodes: Enabling High-Performance n-Graphene/p-Si Schottky Junction Photovoltaics. *Energy Environ. Sci.* **2015**, *8*, 2085–2092.

(34) Wang, F.; Kozawa, D.; Miyauchi, Y.; Hiraoka, K.; Mouri, S.; Ohno, Y.; Matsuda, K., Considerably Improved Photovoltaic Performance of Carbon Nanotube-Based Solar Cells Using Metal Oxide Layers. *Nat. Commun.* **2015**, *6*, 6305.

(35) Ding, K.; Zhang, X.; Xia, F.; Wang, R.; Kuang, Y.; Duhm, S.; Jie, J.; Zhang, X., Surface Charge Transfer Doping Induced Inversion Layer for High-Performance Graphene/Silicon Heterojunction Solar Cells. *J. Mater. Chem. A* 2017, *5*, 285–291.

(36) Yoon, K.; Rahnamoun, A.; Swett, J. L.; Iberi, V.; Cullen, D. A.; Vlassiouk, I. V.; Belianinov, A.; Jesse, S.; Sang, X.; Ovchinnikova, O. S.; Rondinone, A. J.; Unocic, R. R.; van Duin, A. C., Atomistic-Scale Simulations of Defect Formation in Graphene under Noble Gas Ion Irradiation. *ACS Nano* **2016**, *10*, 8376–8384.

(37) Komsa, H.-P.; Krasheninnikov, A. V., Native Defects in Bulk and Monolayer MoS<sub>2</sub> from First Principles. *Phys. Rev. B* **2015**, *91*, 125304.

(38) Ghorbani-Asl, M.; Kretschmer, S.; Spearot, D. E.; Krasheninnikov, A. V., Two-Dimensional MoS<sub>2</sub> under Ion Irradiation: From Controlled Defect Production to Electronic Structure Engineering. *2D Mater.* **2017**, *4*, 025078.

(39) Yablonovitch, E.; Allara, D. L.; Chang, C. C.; Gmitter, T.; Bright, T. B., Unusually Low Surface-Recombination Velocity on Silicon and Germanium Surfaces. *Phys. Rev. Lett.* **1986**, *57*, 249–252.

(40) Aberle, A. G., Surface Passivation of Crystalline Silicon Solar Cells: A Review. *Prog. Photovolt.: Res. Appl.* **2000**, *8*, 362–376.

#### **Figure Caption**

Figure 1 Schematic diagrams of hybrid integration by conventional direct transfer and our nano-subsidence techniques. a, Cross-sectional diagram for the conventional direct transfer integration, which features several risks of tearing out and sliding off when the sizes of 2D crystals are small, due to the weak stickability of 2D crystals and the presence of stepwise substrate structure. **b**, The concept of the improved hybrid integration by nano-subsidence in which the 2D crystals are fixed by using the metallic electrodes as anchoring bars and selectively etching out the sacrificial SiO<sub>2</sub> layer in the last. The hybrid integration is completed after the gentle subsidence of 2D crystals. **c**, The processing flow and corresponding images for each critical integration step for the subsidence integration. Its processing sequence is renewed to transfer-metallization-patterning-etching to ensure the precise location of 2D crystals.

Figure 2 Photoelectric properties of hybrid graphene/silicon diodes prepared by the nano-subsidence integration. **a**, Diagram of the energy level alignment and operation principle of the graphene/silicon photodiodes. **b**, Comparative photoelectric behavior of the photodiodes before and after engineering band alignment *via* TFSA doping. Inset: The molecular structure of TFSA and the change of Fermi level of graphene before and after TFSA doping. **c**, Fitting of *I-V* curve under dark condition to extract the ideality factor of the diodes. Inset: Semi-logarithmic plot of the I-*V* curves under both dark and light conditions. High rectification and zero-bias signalnoise ratios of  $10^5$  and  $10^7$  are observed. **d**, Principle of wavelength scan for characterizing photoresponse time, where the piezoelectric response time is below the order of ms that defines the lower limit of our samples. **e**, Modulation of photocurrent by varying the excitation wavelength. **f**, Enlarged figure to analyze the rise and decay times of our photodiodes which are estimated to be better than 500 µs.

Figure 3 Photoelectric properties of graphene/silicon diodes after capping antireflective MoO<sub>3</sub>. **a**, Cross-sectional diagrams and optical images of the pristine and MoO<sub>3</sub> capped devices. **b**, Comparative *I-V* behavior of the photodiodes before (blue) and after (red) capping 55 nm MoO<sub>3</sub> antireflective layers. The photocurrent increases from 12 to 17 mA/cm<sup>2</sup>. **c**, Comparison of absorption rate (1-R, lines) and external quantum efficiency (EQE, open dots) before (blue) and after (red) MoO<sub>3</sub>

capping. **d**, Contour plot of photoelectric sensitivity *versus* wavelength and light power. **e**, Sensitivity as a function of light power at different wavelength values from 350 to 650 nm. The devices show negligible saturation in photoresponse within experimental power range of ~50 mW/cm<sup>2</sup>. **f**, Comparison of EQE with three typical commercial silicon photodiodes. Our devices (red dots) rivals the counterparts in the visible regime from 400 to 700 nm after the MoO<sub>3</sub> antireflective capping.

Figure 4 Test of the uniformity of array units. **a**, Optical image of a testing module with samples mounted onto a home-made printed circuit board. **b**, Enlarged image for a local area with three quadrant arrays. **c**, Further enlarged image for an individual  $2 \times 2$  quadrant array. **d-g**, One-by-one test of the photoelectric behavior for the four array units (*i.e.*, from quadrant 1 to 4). Inset images show the illumination locations of the focused excitation laser.

Figure 5 Test of the feasibility of the subsidence integration technique to other 2D crystals. a, Optical images for a typical MoS<sub>2</sub>/silicon diode before and after SiO<sub>2</sub> etching. b, Diagram of the energy level alignment of the MoS<sub>2</sub>/silicon diode, which is actually an n/n<sup>++</sup> heterojunction with small barrier heights ( $\Phi_C$  and  $\Phi_V$ ). c, Semilogarithmic plot of the *I-V* curves under both dark (black dots) and light (red circles) conditions. d, Corresponding linear plot of the *I-V* curve. e, Contour plot of photoelectric sensitivity *versus* wavelength and light power. f, Sensitivity as a function of light power at different wavelength values from 350 to 650 nm. The devices also show negligible saturation in photoresponse within experimental power range. g, Estimated EQE for different wavelengths from 320 to 700 nm. h, Modulation of photocurrent by varying the excitation wavelength.

Figure 1 Schematic diagrams of hybrid integration by conventional direct transfer and our nano-subsidence techniques. a, Cross-sectional diagram for the conventional direct transfer integration, which features several risks of tearing out and sliding off when the sizes of 2D crystals are small, due to the weak stickability of 2D crystals and the presence of stepwise substrate structure. b, The concept of the improved hybrid integration by nano-subsidence in which the 2D crystals are fixed by using the metallic electrodes as anchoring bars and selectively etching out the sacrificial SiO<sub>2</sub> layer in the last. The hybrid integration is completed after the gentle subsidence of 2D crystals. c, The processing flow and corresponding images for each critical integration step for the subsidence integration. Its processing sequence is renewed to transfermetallization-patterning-etching to ensure the precise location of 2D crystals.

Figure 2 Photoelectric properties of hybrid graphene/silicon diodes prepared by the nanosubsidence integration. **a**, Diagram of the energy level alignment and operation principle of the graphene/silicon photodiodes. **b**, Comparative photoelectric behavior of the photodiodes before and after engineering band alignment *via* TFSA doping. Inset: The molecular structure of TFSA and the change of Fermi level of graphene before and after TFSA doping. **c**, Fitting of *I-V* curve under dark condition to extract the ideality factor of the diodes. Inset: Semi-logarithmic plot of the I-*V* curves under both dark and light conditions. High rectification and zero-bias signal-noise ratios of 10<sup>5</sup> and 10<sup>7</sup> are observed. **d**, Principle of wavelength scan for characterizing photoresponse time, where the piezoelectric response time is below the order of ms that defines the lower limit of our samples. **e**, Modulation of photocurrent by varying the excitation wavelength. **f**, Enlarged figure to analyze the rise and decay times of our photodiodes which are estimated to be better than 500 µs.

**Figure 3 Photoelectric properties of graphene/silicon diodes after capping antireflective MoO**<sub>3</sub>. **a**, Cross-sectional diagrams and optical images of the pristine and MoO<sub>3</sub> capped devices. **b**, Comparative *I-V* behavior of the photodiodes before (blue) and after (red) capping 55 nm MoO<sub>3</sub> antireflective layers. The photocurrent increases from 12 to 17 mA/cm<sup>2</sup>. **c**, Comparison of absorption rate (1-R, lines) and external quantum efficiency (EQE, open dots) before (blue) and after (red) MoO<sub>3</sub> capping. **d**, Contour plot of photoelectric sensitivity *versus* wavelength and light power. **e**, Sensitivity as a function of light power at different wavelength values from 350 to 650 nm. The devices show negligible saturation in photoresponse within experimental power range of ~50 mW/cm<sup>2</sup>. **f**, Comparison of EQE with three typical commercial silicon photodiodes. Our devices (red dots) rivals the counterparts in the visible regime from 400 to 700 nm after the MoO<sub>3</sub> antireflective capping.

**Figure 4 Test of the uniformity of array units. a**, Optical image of a testing module with samples mounted onto a home-made printed circuit board. **b**, Enlarged image for a local area with three quadrant arrays. **c**, Further enlarged image for an individual 2×2 quadrant array. **d-g**, One-by-one test of the photoelectric behavior for the four array units (*i.e.*, from quadrant 1 to 4). Inset images show the illumination locations of the focused excitation laser.

**Figure 5 Test of the feasibility of the subsidence integration technique to other 2D crystals. a**, Optical images for a typical MoS<sub>2</sub>/silicon diode before and after SiO<sub>2</sub> etching. **b**, Diagram of the energy level alignment of the MoS<sub>2</sub>/silicon diode, which is actually an n/n<sup>++</sup> heterojunction with small barrier heights ( $\Phi_{\rm C}$  and  $\Phi_{\rm V}$ ). **c**, Semi-logarithmic plot of the *I-V* curves under both dark (black dots) and light (red circles) conditions. **d**, Corresponding linear plot of the *I-V* curve. **e**, Contour plot of photoelectric sensitivity *versus* wavelength and light power. **f**, Sensitivity as a function of light power at different wavelength values from 350 to 650 nm. The devices also show negligible saturation in photoresponse within experimental power range. **g**, Estimated EQE for different wavelengths from 320 to 700 nm. **h**, Modulation of photocurrent by varying the excitation wavelength.