## Self-referenced multi-bit thermally assisted magnetic random access memories

Q. Stainer, L. Lombard, K. Mackay, D. Lee, S. Bandiera, C. Portemont, C. Creuzet, R. Sousa, B. Dieny

## ▶ To cite this version:

Q. Stainer, L. Lombard, K. Mackay, D. Lee, S. Bandiera, et al.. Self-referenced multi-bit thermally assisted magnetic random access memories. Applied Physics Letters, 2014, 105 (3), pp.032405. 10.1063/1.4885352]. hal-02042683

HAL Id: hal-02042683

https://hal.science/hal-02042683

Submitted on 20 Feb 2019

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## Self-referenced multi-bit thermally assisted magnetic random access memories

Q. Stainer, <sup>1,2,a)</sup> L. Lombard, <sup>1</sup> K. Mackay, <sup>1</sup> D. Lee, <sup>3</sup> S. Bandiera, <sup>1</sup> C. Portemont, <sup>1</sup> C. Creuzet, <sup>1</sup> R. C. Sousa, <sup>2</sup> and B. Dieny <sup>2</sup>

<sup>1</sup>Crocus Technology SA, 4 Place Robert Schuman, 38025 Grenoble, France

(Received 15 November 2013; accepted 15 June 2014; published online 22 July 2014)

The feasibility of 3-bits per cell storage in self-referenced thermally assisted magnetic random access memories is demonstrated both by macrospin simulations and experiments. The memory dot consists of a storage layer where CoFe/CoFeB magnetization direction is pinned by an IrMn layer using the ferromagnet/antiferromagnet interfacial exchange coupling, separated by an MgO tunnel barrier from a CoFeB sense layer whose magnetization direction is free to rotate. Writing is performed by heating the antiferromagnet above its blocking temperature by sending a current pulse through the magnetic tunnel junction, with the application of an in-plane field during the subsequent cooling phase, thus setting the new storage layer pinning direction. This pinning direction actually carries the information stored in the storage layer. Reading is performed by applying a rotating field, inducing a coherent rotation of the sense layer, and subsequently locating the field angle associated with the minimum measured resistance. This angle corresponds to the parallel magnetic configuration of the magnetic tunnel junction and therefore allows determining the pinning direction established during the write operation. The number of distinguishable pinning angles defines the total number of bits that can be stored in a single dot. © 2014 AIP Publishing LLC. [http://dx.doi.org/10.1063/1.4885352]

Spinelectronics, merging magnetism and electronics, has kept growing in the past 20 yr thanks to a strong synergy between fundamental research<sup>1</sup> and applied developments,<sup>2</sup> especially in the fields of magnetic storage (hard disk drives) and memories (Magnetic Random Access Memory (MRAM)). MRAMs based on magnetic tunnel junctions are nowadays receiving an increasing interest within the microelectronics industry due to their unique combination of nonvolatility, write/read speed (~30 ns or below), endurance (>10<sup>16</sup> cycles), density and radiation hardness.<sup>3</sup> In particular, spin transfer torque MRAM has been identified<sup>4</sup> in the International Technology Roadmap for Semiconductors (ITRS) as one of the two most promising technologies of non-volatile emerging memories (with RedOx RAM<sup>5</sup>) allowing down size scalability to the 22 nm technology node and beyond.

While MRAM products based on Toggle-Switching<sup>6</sup> are already available, another generation based on thermally assisted writing is under development.<sup>7</sup> Thermally-assisted MRAM (TA-MRAM) exploits the temperature dependence of ferromagnet/antiferromagnet interfacial exchange coupling to overcome the write consumption versus thermal stability dilemma usually observed in magnetic recording technologies. High stability at operating temperature is obtained by pinning the storage layer's magnetization with an antiferromagnet by the exchange bias coupling occurring at their interface. Writing occurs through a thermally assisted scheme. When heated above the antiferromagnet's blocking

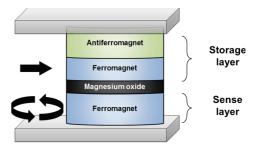

temperature, the ferromagnetic layer becomes free, and its magnetization can be set by a magnetic field. The heating (at about 250 °C) is generated by current flowing through the magnetic tunnel junction (MTJ). Simultaneously, a magnetic field switches the ferromagnetic layer in the desired direction. The heating is then stopped, the junction cools down under the applied magnetic field that maintains the storage layer magnetization in the appropriate direction. Exchange coupling is re-established, pinning the storage layer in the new direction. Selectivity is achieved in TA-MRAM by the combination of heating and magnetic field.8 In selfreferenced TA-MRAM, the pinned reference layer is replaced by a soft switchable reference layer, 9 referred as the sense layer (Figure 1). This opens wide application prospects due to their in-stack combination of memory and logic (XOR) functions, <sup>10</sup> including multi-bit storage. <sup>11</sup> The multibit storage capability gives increased storage densities

FIG. 1. Schematic of a self-referenced MRAM for multi-bit applications. The black arrows denote the sense and storage layer magnetizations during a reading operation.

<sup>&</sup>lt;sup>2</sup>SPINTEC (UMR 8191 CEA-CNRS-UJF- Grenoble INP), CEA/INAC, 38054 Grenoble Cedex 9, France

<sup>&</sup>lt;sup>3</sup>Crocus Technology INC, 2380 Walsh Ave., Santa Clara, California 95051, USA

a)qstainer@crocus-technology.com

without requiring moving to smaller and more technically challenging technology nodes.

This paper reports the demonstration of feasibility of 3-bits per cell storage obtained in self-referenced MRAM cells. The readout is based on the phase of the oscillation of resistance produced by a 360° rotation of the sense layer magnetization. The concept was explored by macrospin simulations and demonstrated experimentally on cells of various diameters down to 110 nm.

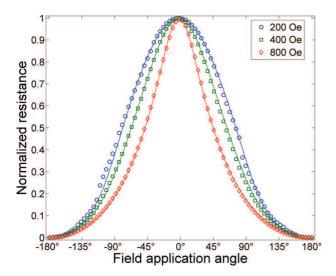

Instead of reading a resistance level, as in TA-MRAM, or a change in resistance, as in regular self-referenced MRAM, multi-bit self-referenced TA-MRAMs exploit the full resistance response obtained as the sense layer aligns itself with an external rotating field. During this field rotation, the MTJ resistance continuously varies as a function of the field angle (see Figure 2), reaching a maximum (respectively, minimum) value when the sense and storage layers moments become antiparallel (respectively, parallel). Thus, the data, stored in the storage layer magnetization direction, can be read out from the phase of this oscillatory resistance, for instance, by an external digital signal processor.

Therefore, to achieve n-bits per cell storage, the storage layer must be writable in at least 2<sup>n</sup> distinct directions. Unlike resistance-level-based multi-bit operations in MRAM reported in previous works, <sup>12</sup> this operation does not rely on a series of predefined resistance levels, but rather on the angular position of a minimum of resistance. It is therefore more tolerant to process related cell to cell variability such as size or resistance per area variations, though at the expense of a more complex readout mechanism.

3-bits per cell storage was first assessed by macrospin simulation and then confirmed by experimental results. In order to simulate the behaviour of a multi-bit self-referenced MRAM, a macrospin approach based on the Stoner-Wohlfarth<sup>13</sup> model of magnetization reversal was developed. Under the assumption that both the sense and the storage layers magnetizations behave like macrospins, the system energy E is written<sup>10</sup>

FIG. 2. Experimental (dots) and simulated (solid line) resistance responses of a 1  $\mu$ m self-referenced MRAM cell under a circular field pattern of various amplitudes. The fits were obtained using a single set of simulation parameters (H<sub>K1</sub> = H<sub>K2</sub> = 50 Oe, H<sub>exch</sub> = 700 Oe,  $\theta_{K_1} = \theta_{K_2} = 0$ , and  $\theta_P = -2.5^\circ$ ).

$$\begin{split} \mathbf{E} &= -\mathbf{H}[\mathbf{m}_{1}\cos(\theta_{1} - \theta_{H}) + \mathbf{m}_{2}\cos(\theta_{2} - \theta_{H})] \\ &- \frac{\mathbf{H}_{K_{1}}\mathbf{m}_{1}}{4}\cos(2\theta_{1} - 2\theta_{K_{1}}) - \frac{\mathbf{H}_{K_{2}}\mathbf{m}_{2}}{4}\cos(2\theta_{2} - 2\theta_{K_{2}}) \\ &+ \frac{H_{1 \to 2}\mathbf{m}_{2} + H_{2 \to 1}\mathbf{m}_{1}}{2}\cos(\theta_{1} - \theta_{2}) \\ &- H_{exch}\mathbf{m}_{1}\cos(\theta_{1} - \theta_{P}), \end{split} \tag{1}$$

where H and  $\theta_{\rm H}$  are the external field amplitude and its direction with respect to the easy axis of the layers,  $m_{1(2)}, \theta_{1(2)}, H_{K_{1(2)}}$ , and  $\theta_{K_{1(2)}}$  are the moment, moment angle with respect to the easy axis, uniaxial anisotropy field, and easy axis angle, respectively, of the storage (1) and sense layer (2).  $H_{1\rightarrow 2}$  and  $H_{2\rightarrow 1}$  are the dipolar fields generated by the storage layer on the sense layer and the other way around.  $H_{\rm exch}$  and  $\theta_{\rm P}$  are the ferromagnet/antiferromagnet exchange coupling field and the angle characterizing the pinning direction. All fields are expressed in Oe and all moments in emu. Energy minimization was performed using a conjugate-gradient based algorithm. The resistance R of the MTJ was calculated using  $^{15}$

$$R = \frac{\bar{R}}{1 + \frac{TMR}{2}\cos(\theta_1 - \theta_2)},\tag{2}$$

where TMR is the tunnel magnetoresistance. Figure 2 shows experimental data fitted with (2), the results being consistent with previous works. <sup>14,15</sup>

Simulation of the write operation is performed by applying an adequate external field profile and cancelling the exchange bias term in the energy function before minimizing it, thereby emulating a heating voltage unpinning the storage layer. Assuming that both layers have the same anisotropy amplitude and direction (i.e.,  $H_{K_1} = H_{K_2} = H_K$  and  $\theta_{K_1} = \theta_{K_2} = 0$ ), using Sylvester's criterion to infer the positive definiteness of the energy Hessian matrix, <sup>16</sup> indicating a stable configuration, it is possible to deduce the analytical expressions of the field requirement for both the read and the write operation to have the sense and storage layers aligned along the field

$$H_{\text{write}} = H_{1\to 2} + H_{2\to 1} + H_K,$$

$$H_{\text{read}} = \frac{H_{1\to 2} + H_{2\to 1} - H_{exch}}{2} + H_K$$

$$+ \sqrt{\left(\frac{H_{1\to 2} - H_{2\to 1} + H_{exch}}{2}\right)^2 + H_{1\to 2}H_{2\to 1}}. (3)$$

The experimental data were obtained on IrMn/CoFe/CoFeB/MgO/CoFeB MTJ patterned into cylindrical pillars of various diameters ranging from 110 nm to 1000 nm. Electrical characterizations were performed on an automatic wafer tester with two orthogonal field generating coils. Heating voltage pulses were applied across the MTJ under a constant field set at 8 distinct angles, and whose amplitudes were set from 100 Oe to 600 Oe. Reading was then subsequently performed using a rotating field of amplitude equal to that used for writing.

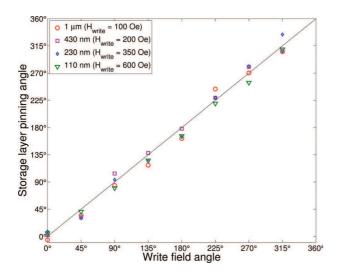

The pinning angles of the storage layer magnetization inferred from the phase of the resistance responses are plotted in Figure 3 as a function of the write field

FIG. 3. Measured pinning angle of the storage layer as a function of the write field angle, for 8 writing directions and various MTJ diameters. The continuous line denotes the result expected from the macrospin simulation.

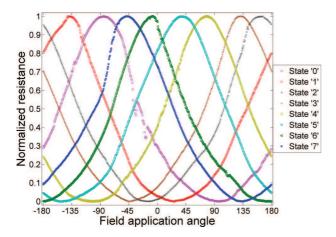

FIG. 4. Normalized resistance as a function of the field angle (applied field  $= 600\,\mathrm{Oe}$ ) measured on a 110 nm wide self-referenced MRAM cell written in 8 directions, demonstrating a 3 bits per cell device feasibility.

application angle. Within the range of write field investigated ( $H_{\text{write}} > H_{1 \to 2} + H_{2 \to 1} + H_K$ ), the storage layer magnetization is asymptotically aligned to the applied write field direction within 5°. Lower values of write field would result in the storage layer magnetization being aligned inbetween its intrinsic anisotropy axis and the write field angle, leading thus to a write error (not shown).

The normalized responses during the read operation for the 110 nm MTJ are plotted in Figure 4 and confirm the feasibility of 3 bits functionality at that dimensions. Some deviation from the model and noise can be observed on the experimental data (Figures 2 and 4), which are ascribed to micromagnetic distorsions at the edge of the pillars likely associated with imperfections in the pillar shapes arising from the etching process.

In order to further reduce the reading and writing consumption of the device, both the read and write field requirements need to be reduced. To do that, the magnetostatic interaction  $(H_{1\rightarrow 2}+H_{2\rightarrow 1})$  between both layers has to be minimized. This can be achieved by either using low magnetization materials or synthetic antiferromagnet bilayers that reduce magnetostatic interactions thanks to magnetic flux closure within each bilayers.

In summary, a functional 3 bits self-referenced MRAM has been successfully demonstrated both by simulation using a Stoner-Wohlfarth model and experimentally on MTJ of various dimensions down to 110 nm. Further studies should be conducted in order to enhance the scalability of read and write fields and reduce power consumption. For that purpose, either synthetic antiferromagnet structures or low-magnetization-ferromagnets could be employed for a significant reduction of magnetostatic interactions between the storage and the sense layers.

This work was supported by iARPA (N66001-13-C-2003).

<sup>&</sup>lt;sup>1</sup>C. Y. You and H. Kim, J. Magn. **18**(4), 380–385 (2013).

<sup>&</sup>lt;sup>2</sup>R. Patel, E. Ipek, and E. G. Friedman, Microelectron. J. **45**(2), 133–143 (2014).

<sup>&</sup>lt;sup>3</sup>J. Åkerman, Science **308**, 508–510 (2005).

<sup>&</sup>lt;sup>4</sup>International Technology Roadmap for Semiconductors, (2009).

<sup>&</sup>lt;sup>5</sup>International Technology Roadmap for Semiconductors (2005).

<sup>&</sup>lt;sup>6</sup>L. Savtchenko, A. Korkin, B. N. Engel, N. D. Rizzo, and J. A. Janesky, U.S. patent 6,545,906 B1 (2013).

<sup>7</sup>I. L. Prejbeanu, M. Kerekes, R. C. Sousa, H. Sibuet, O. Redon, B. Dieny, and J. P. Nozières, J. Phys.: Condens. Matter 19, 165218 (2007).

<sup>&</sup>lt;sup>8</sup>I. L. Prejbeanu, S. Bandiera, J. Alvarez-Hérault, R. C. Sousa, B. Dieny, and J. P. Nozières, J. Phys. D: Appl. Phys. 46, 074002 (2013).

<sup>&</sup>lt;sup>9</sup>N. Berger and J. P. Nozières, U.S. patent 20110007561 (2011).

<sup>&</sup>lt;sup>10</sup>Q. Stainer, L. Lombard, K. Mackay, R. C. Sousa, I. L. Prejbeanu, and B. Dieny, 5th IEEE International Memory Workshop (2013).

<sup>&</sup>lt;sup>11</sup>N. Berger and M. El Baraji, U.S. patent 8,467,234 B2 (2013).

<sup>&</sup>lt;sup>12</sup>R. Leuschner, U. Klostermann, H. Park, F. Dahmani, R. Dittrich, C. Grigis, K. Hernan, S. Mege, C. Park, M. C. Clech, G. Y. Lee, S. Bournat, L. Altimime, and G. Mueller, International Electron Devices Meeting (2006).

<sup>&</sup>lt;sup>13</sup>E. C. Stoner and E. P. Wohlfarth, Philos. Trans. R. Soc., Ser. A 240, 599–642 (1948).

<sup>&</sup>lt;sup>14</sup>H. Jaffrès, D. Lacour, F. Nguyen Van Dau, J. Briatico, F. Petroff, and A. Vaurès, Phys. Rev. B 64, 064427 (2001).

<sup>&</sup>lt;sup>15</sup>N. S. Safron, B. D. Schrag, X. Liu, W. Shen, D. Mazumdar, M. J. Carter, and G. Xiao, J. Appl. Phys. **103**(3), 033507 (2008).

<sup>&</sup>lt;sup>16</sup>W. N. Dong and A. L. Schlack, AIAA J. **12**, 1737–1739 (1974).