## A Novel Passive Cost-Effective Technique to Improve Radiated Immunity on PCBs

Mohsen Koohestani, Richard Perdriau, Jean-Luc Levant, Mohamed Ramdani

### ► To cite this version:

Mohsen Koohestani, Richard Perdriau, Jean-Luc Levant, Mohamed Ramdani. A Novel Passive Cost-Effective Technique to Improve Radiated Immunity on PCBs. IEEE Transactions on Electromagnetic Compatibility, 2019, 61 (6), pp.1733-1739. 10.1109/TEMC.2018.2882732 . hal-01996029

## HAL Id: hal-01996029 https://hal.science/hal-01996029

Submitted on 12 Apr 2019

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# A Novel Passive Cost-Effective Technique to Improve Radiated Immunity on PCBs

Mohsen Koohestani<sup>(D)</sup>, *Member, IEEE*, Richard Perdriau<sup>(D)</sup>, *Senior Member, IEEE*, Jean-Luc Levant, and Mohamed Ramdani<sup>(D)</sup>, *Senior Member, IEEE*

Abstract—This paper proposes a novel simple cost-effective technique to improve the potential immunity of integrated circuits (ICs) to radiated electromagnetic (EM) disturbances. It is based on dielectric loading which lessens the susceptibility of ICs independently of frequency by confining the reactive fields inside the dielectric load. This has no side effects on the IC performance. To highlight the importance of the proposed technique, immunity testing was performed numerically both in near and far fields. A loaded IC (a microcontroller) was compared to an unloaded one through far-field measurements inside a transverse EM cell to indirectly assess the suitability of the proposed approach. Results show that loading the IC with non-ferromagnetic dielectric material not only effectively decreases its susceptibility to electric field, but also to magnetic field. Moreover, a significant difference of  $\sim 48\%$  less failure rate was achieved for the loaded compared to the unloaded IC demonstrating the usefulness of this technique as a potential solution for radiated immunity improvement.

*Index Terms*—Dielectric loading, far field, integrated circuits (ICs), near field, radiated immunity, transverse electromagnetic (TEM) cell.

#### I. INTRODUCTION

**E** LECTROMAGNETIC (EM) immunity (EMI) and EM compatibility (EMC) testing are of great importance with the fast increasing functionality and complexity of integrated circuits (ICs) [1]–[3]. A higher clock frequency or any electrical transition with sharp edges (e.g., addressing or controlling data) gives rise to EMI issues [4].

In an embedded system, a microcontroller ( $\mu$ C) plays a major role in governing specific operations.  $\mu$ Cs are subjected to a partial or a complete malfunction in presence of an EM disturbance [5]. Moreover, printed circuit boards (PCBs) having relatively long tracks connected to IC pins suffer more in terms of radiation, as they act as antennas driven by IC activity. These have led the EMC/EMI regulatory commissions (e.g., international electrotechnical commission IEC [6]) to define limits on EM radiation produced by ICs. Besides, the industrial trends in the EMC of  $\mu$ Cs show an increasing demand for IC miniaturization technology, which leads to speed up their functionality at the cost of a higher power consumption and stronger switching currents [7]. To counteract the latter effect, voltage supply is reduced, which in return lowers the noise margin of digital circuitry and consequently IC immunity [8]. This fact fostered some interest in the wireless communications community for ways to improve immunity of ICs to radiated disturbances.

A most commonly used approach to improve the EMI field generated by today's high-speed ICs is shielding [9]. Another prevalent solution is to take benefit from flexible polymer absorbers [10], [11]. They are made of either soft metal flakes filler in polymer resin or high permeability magnetic flake particles. The latter is usually preferred as it is non-conductive and can be directly applied to circuit tracks.

Here, we propose a new simple passive approach to improve the radiated immunity on PCBs using dielectric loading. It is worth mentioning that dielectric loading has been mainly employed by antenna engineers as an effective technique to reduce antenna dimensions [12], to introduce notch frequency bands [13], and, in general, to improve antenna behavior with no side effects [14]. It has also been used to reduce interactions between antenna and human body by making the antenna less sensitive to human body proximity effects [15]. It consists in gluing small pieces of demetalized commercially available substrate with a proper permittivity around/over the IC. Simulations and measurements were conducted to confirm the adequacy of the proposed technique.

There exist several near and far field measurements techniques to evaluate the radiated EM immunity of ICs. The most commonly used near-field technique is the IEC 62132-9 scan method [16], which is a reciprocal use of IEC 61967-3 employed for immunity testing. A transverse EM (TEM) cell, which approximates a uniform and linearly polarized plane wave, is widely used for far-field EMI/EMC tests of radio frequency (RF) devices [17]. In general, measurements in far field indicate the PCB radiation with respect to its orientation and to frequency. However, they cannot determine the internal sources of emissions. Conversely, near-field techniques overcome this limitation providing a precise location of radiation sources. Here, for the sake of completeness, the suitability of the proposed approach was investigated both in near and far field zones.

The paper is organized as follows. Section II describes the materials used, the methodology employed, and the simulation

Manuscript received September 19, 2018; revised October 29, 2018; accepted November 16, 2018. (Corresponding author: Mohsen Koohestani.)

M. Koohestani, R. Perdriau, and M. Ramdani are with the ESEO-TECH, RF-EMC Research Group, Angers 49107, France, and also with the Institute of Electronics and Telecommunications of Rennes (IETR), Rennes 35042, France (e-mail: mohsen.koohestani@eseo.fr; richard.perdriau@eseo.fr; mohamed. ramdani@eseo.fr).

J.-L. Levant is with the Microchip (previously ATMEL) Nantes, Nantes 44300, France (e-mail: jeanluc.levant@microchip.com).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TEMC.2018.2882732

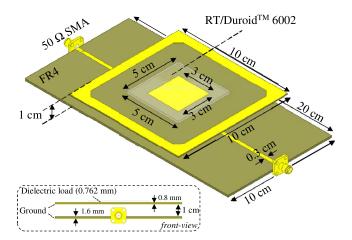

Fig. 1. Schematic geometry used in simulation.

and experimental setup configurations. Section III details the analysis of the numerical results, while Section IV addresses the experimental results of the proposed technique. Concluding contributions of this study are provided in Section V.

#### II. MATERIALS AND METHODS

This section deals with the research material and methodology to study the influence of dielectric loading on the radiated immunity on PCBs.

#### A. Simulation Setup and Method

As described in IEC 62132 [6], a simple 10 cm  $\times$  10 cm square PCB was considered with a 3 cm  $\times$  3 cm square metal patch in its center representing a rough approximation of an IC (see Fig. 1). The patch is printed on a low-cost FR4 epoxy substrate ( $\epsilon_r = 4.4$ , thickness = 0.8 mm, and tan  $\delta = 0.02$ ). The other side of the PCB is coated with metal serving as ground plane. The PCB is mounted 1 cm above a 50  $\Omega$  transmission line (TL) of 0.37 cm width to be in near-field conditions (see Fig. 1). The other side of the TL substrate (FR4, thickness = 1.6 mm) is a metallic ground plane. All the metallic parts in the numerical model are considered to be copper.

A 5 cm × 5 cm solid piece of demetalized low-loss commercial substrate (RT/Duroid 6002) with a permittivity of  $\varepsilon_r$  = 2.94, thickness of 0.762 mm, and tan  $\delta$  = 0.001 was used as the dielectric load to fully cover the square patch. This small low-loss load confines the reactive (non-radiating) fields, which would result in lower electric field intensity while maintaining magnetic field, with no EM power dissipation. To evaluate the importance of the proposed dielectric loading technique, simulations were performed using Ansys HFSS full-wave solver both in near and far EM field zones. In EMC, the limits for near and far field zones are usually fixed at  $\frac{\lambda}{2\pi}$  and  $\frac{2D^2}{\lambda}$  from the source, respectively, where  $\lambda$  and D are the wavelength and the largest radiator dimension, respectively.

#### B. Measurement Setup and Method

In order to perform experiments, an indirect measurement was considered due to the impossibility of measuring the EM fields directly at the PCB level under the dielectric pad. As modern  $\mu$ Cs are generally equipped with embedded phase lock loops (PLLs) to accurately protect the system clock from jitter and instabilities, they are very sensitive to EM disturbances [5], [19], [20]; in [5] and [20], the  $\mu$ C malfunction due to injecting magnetic field on PLL power supply pins has been reported. Here, a 32-bit  $\mu$ C (ATMEL SAM3S4B) [21] initially designed for a previous research project was used. It was loaded by a piece of dielectric to check whether it improves the immunity of the  $\mu$ C's clock PLL to the EM interferences. A TEM cell as the far-field free space condition emulator was also employed for radiated immunity testing. We used a standard TEM cell (Model: FCC-TEM-JM2, dc up to 1.6 GHz) for the purpose of this study [22].

The thermal conductivity of RT/Duroid 6002 is  $0.6 \frac{W}{m.K}$  [18]. For the considered load dimension of 50 mm × 50 mm × 0.762 mm layer, the thermal resistance is  $0.5 \frac{K}{W}$ , which would lead to a low temperature difference between both sides of the load even for large size ICs (e.g., dissipating about 15 W, such as Intel Core<sup>TM</sup> i3-7020U laptop processors). In case of small ICs, such as SAM3S4B, with 10 mm × 10 mm package, the thermal resistance would be  $12.5 \frac{K}{W}$  ( $25 \times 0.5 \frac{K}{W}$ ), considering the worst case scenario where no heat would be dissipated in the horizontal plane. With the SAM3S4B dissipating about 132 mW (40 mA × 3.3 V), the difference between the upper and lower sides remains very low ( $0.132 \times 12.5 = 1.65 \degree$  C).

#### **III. NUMERICAL RESULTS AND DISCUSSION**

This section presents the impact of dielectric loading on the PCB behavior in near and far field scenarios. A comparison is made between the loaded and unloaded ICs (an equivalent patch) considering the distribution of wave impedance, i.e., the ratio of the norms electric to magnetic field (||E||/||H||), as the criterion to provide an index of the relative strength between the electric and magnetic fields. The magnitude of the electric field decreases under the load due to the dielectric properties of the material. As far as the magnetic field is concerned, coupling with the pins of an IC depends on the orientation of the tangential component: The more parallel to the pins, the lesser coupling and consequently lower is the disturbance injected into low-impedance pins (such as power supply pins).

In a TEM cell, magnetic field lines are supposed to be all in the same direction. In the case presented in the paper, it must be noted that the purpose of loading is not to ensure the most homogeneous magnetic field below the load surface, but to decrease the IC susceptibility. Therefore, when the IC is replaced by an equivalent patch, it is necessary to check out the following, when the patch is loaded:

If the direction of the tangential magnetic field around the patch at a given frequency remains unchanged, the magnitude of that field decreases (or, at least, does not increase).

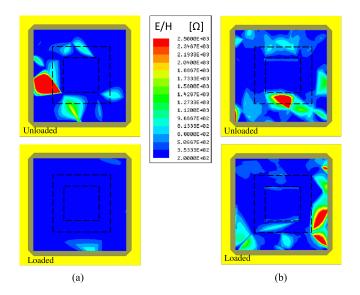

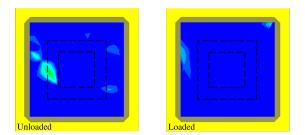

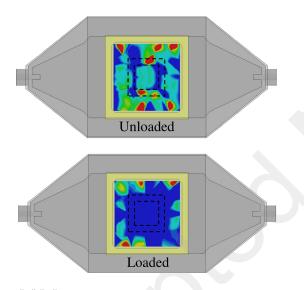

Fig. 2.  $||\mathbf{E}||/||\mathbf{H}||$  ratio for unloaded and loaded ( $\varepsilon_r = 2.94$ ) PCBs for 1-W input power at (a) 1 GHz and (b) 1.85 GHz.

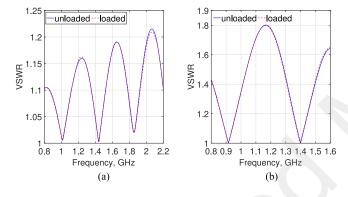

Fig. 3. Influence of dielectric loading on VSWR. (a) TL. (b) TEM cell.

If the direction of that magnetic field changes, the latter becomes more perpendicular to the patch sides (i.e., parallel to IC pins).

If those conditions are met, it is possible to claim that the immunity of the IC to magnetic field would either decrease or remain unchanged with the dielectric load.

#### A. Near Field

Fig. 1 shows the simulation setup; one port is excited, while the other one is terminated with a 50  $\Omega$  load. The IEC standard for the voltage standing wave ratio (VSWR) with 50  $\Omega$  termination has to be lower than 1.25, which is the case here over a wide range of frequencies [see Fig. 3(a)]. To evaluate the importance of the dielectric loading, a comparison was made with the unloaded PCB.

Fig. 2 shows the wave impedance distribution on the PCB surface with and without the dielectric loads at two gigahertzrange resonance frequencies, i.e., 1 and 1.85 GHz [see Fig. 3(a)]. Note that loading neither detunes the frequency nor changes the level and, therefore, the variation in impedance distribution is not a result of a frequency change due to the load. In Fig. 2, the colors representing the  $||\mathbf{E}||/||\mathbf{H}||$  ratio distribution in linear

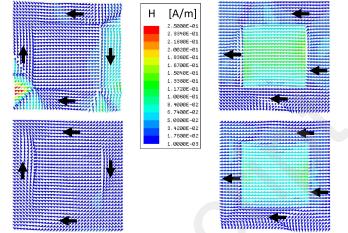

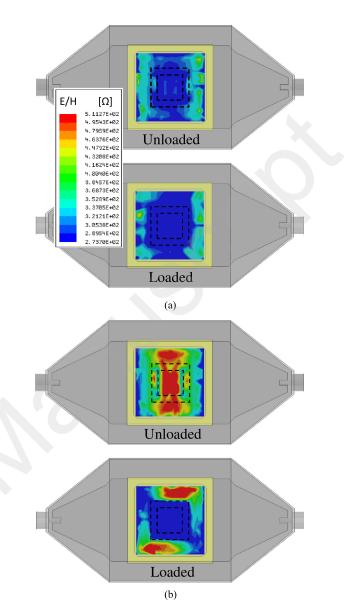

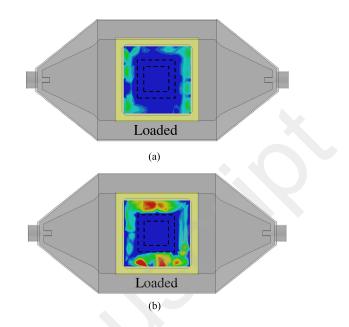

Fig. 4. Simulated vector magnetic field distribution around the unloaded (top) and loaded (bottom) patch under the load at (a) 1 GHz and (b) 1.85 GHz. Black arrows indicate the privileged orientation.

scale go from dark blue (low impedance) to green, yellow, and red (high impedance). As observed in Fig. 2(b), we can clearly see that the highest impedance at the bottom side of the IC is ~800  $\Omega$  for the loaded case, whereas for the unloaded one, it ranges over relatively higher values from 1500 to 2500  $\Omega$ . This is a result of reactive field confinement in the dielectric loads. The effectiveness of the loading technique was checked through simulations and found to remain unchanged for a similar scenario, but with the PCB flipped down to have the patch facing the TL.

Fig. 4 plots the simulated distribution of the vector magnetic field around the patch for both frequencies, with and without the load. At 1 GHz, the orientation is almost the same in both cases, with a worst-case coupling (the field is often parallel to a side and, consequently, perpendicular to IC package pins) over a very significant part of the patch perimeter, while the magnitude decreases and becomes much more uniform in presence of the load. At 1.85 GHz, the orientation does not change with the load either (but is the same on the four sides of the patch), while the magnitude distribution exhibits low-color spots at different locations; however, that fact can be neglected, as field lines are perpendicular to the patch left and right sides where magnitude increases (hence, negligible coupling to IC pins); conversely, where field lines are parallel to the top and bottom sides, magnitude is reduced.

In both cases, it can thus be considered that the susceptibility of an IC to magnetic field would decrease (most of the time) or remain unchanged depending on the frequency and the location of the sensitive pins. Meanwhile, it should be remembered that, in all cases, the susceptibility to electric field would decrease.

On the one hand, as most of the  $\mu$ Cs tend to have an emission spectrum and a susceptibility frequency bandwidth over the 10–100 MHz frequency range, a study was conducted at 60 MHz to check the suitability of the proposed technique at lower frequencies (see Fig. 5). Following the previous reasoning, improvements in immunity as a result of lower EM fields due to loading are evident; the  $||\mathbf{E}||/||\mathbf{H}||$  ratio at 60 MHz reduces from

Fig. 5.  $||\mathbf{E}||/||\mathbf{H}||$  ratio for unloaded and loaded ( $\varepsilon_r = 2.94$ ) PCBs for an input power of 1 W at 60 MHz. The scale is the same as in Fig. 2.

Fig. 6.  $||\mathbf{E}||/||\mathbf{H}||$  ratio for a loaded PCB with  $\varepsilon_r = 10.2$  PCB for 1-W input power at (a) 1 GHz and (b) 1.85 GHz. The scale is the same as in Fig. 2.

1400 to 200  $\Omega$  (by 85%) for a loaded compared to an unloaded PCB.

On the other hand, since the amount of stored energy in a dielectric is directly proportional to its permittivity, it is expected to have even higher immunity in a loaded IC with higher  $\varepsilon_r$  values. Fig. 6 shows results for a case study with RT/Duroid 6010 loads ( $\varepsilon_r = 10.2$ ) demonstrating a significant improvement in wave impedance around the IC where the load is located; it reduces from 800 to 200  $\Omega$  (by 75%) for a dielectric load with a higher  $\varepsilon_r$  of 10.2 compared to 2.94.

#### B. Far Field

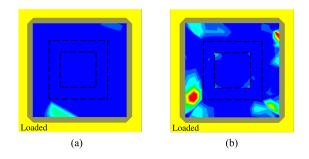

A standard TEM cell as the far-field free space condition emulation was used for far-field testing of radiated immunity [22]. Loaded and unloaded versions of the 10 cm × 10 cm PCB, shown in Fig. 1, were placed on the TEM cell aperture. The IEC standard for VSWR lower than 1.25 was fully met at the TEM cell resonant frequencies. Fig. 7 shows the  $||\mathbf{E}||/||\mathbf{H}||$  ratio distribution over the PCB at the first two resonance frequencies, i.e., 0.9 and 1.4 GHz [see Fig. 3(b)]. Note that, unlike the septum used in simulation, the one of the real TEM cell is asymmetric, which allows much lower VSWR. As observed, loading neither detunes the frequency nor changes the VSWR level and, hence, the variation in impedance distribution is independent of the load impact on the resonant frequency change.

Following the above-mentioned reasoning at the beginning of the current Section, a first glance at the results in Fig. 7 clearly shows the effectiveness of the proposed dielectric loading technique to improve IC radiated immunity independently of frequency. At both considered frequencies, much lower impedance was observed in the loaded compared to the unloaded PCB around the IC where the dielectric loads are attached; the wave

Fig. 7.  $||\mathbf{E}||/||\mathbf{H}||$  ratio for unloaded and loaded ( $\varepsilon_r = 2.94$ ) PCBs inside a standard TEM cell for an input power of 1 W at (a) 0.9 GHz and (b) 1.4 GHz.

impedance at higher frequency is reduced by 46.5% (from 511 to 273  $\Omega$ ).

A plot similar to Fig. 4 for near field is provided in Fig. 8 for far field. As observed, at both frequencies, the magnetic field on left and right sides of the patch has the same magnitude and orientation with or without any load. On top and bottom sides, higher magnitudes can be observed with the load, but can be neglected due to the magnetic field lines being perpendicular to the patch sides. Note that those simulations were performed at the resonant frequencies of the TEM cell, which is indeed the worst case in terms of field homogeneity. Consequently, the same conclusions can be drawn in a TEM cell: Loading would decrease the susceptibility of an IC both to electric and magnetic fields (or, in the worst case, leave the latter unchanged).

At 60 MHz, thanks to dielectric loading, a similar behavior of the  $||\mathbf{E}||/||\mathbf{H}||$  ratio to that of higher frequencies (around 1 GHz)

Simulated vector magnetic field distribution inside the TEM cell Fig. 8. around the unloaded (top) and loaded (bottom) patch under the load at (a) 0.9 GHz and (b) 1.4 GHz. Black arrows indicate the privileged orientation.

$||\mathbf{E}||/||\mathbf{H}||$  ratio for unloaded and loaded ( $\varepsilon_r = 2.94$ ) PCBs for an input Fig. 9. power of 1 W at 60 MHz. The scale is the same as in Fig. 7.

was achieved observing lower impedance and consequently less field strength around the IC (see Fig. 9). Therefore, the dielectric loading technique is also effective at lower MHz frequencies where most  $\mu C$  tend to radiate.

A plot similar to Fig. 6 for near field is provided in Fig. 10 for far field in a TEM cell. It can be seen that the higher permittivity ( $\varepsilon_r = 10.2$ ) does not provide any  $||\mathbf{E}||/||\mathbf{H}||$  improvement compared to the lower value ( $\varepsilon_r = 2.94$ ).

#### IV. EXPERIMENTAL RESULTS AND DISCUSSION

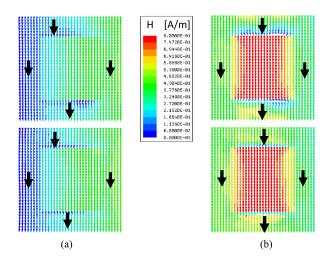

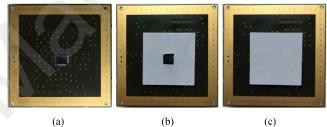

Due to the impossibility to measure the EM field directly under the dielectric layer, an indirect measurement technique was set up. It consisted in using an IC (a  $\mu$ C) with an observable criterion for radiated immunity. A loaded IC was compared to an unloaded one through measurements using a standard TEM cell (see Fig. 11).

Fig. 10.  $||\mathbf{E}||/||\mathbf{H}||$  ratio for a loaded PCB with  $\varepsilon_r = 10.2$  for an input power of 1 W at (a) 0.9 GHz and (b) 1.4 GHz. The scale is the same as in Fig. 7.

(c)

Fig. 11. Measurement setup with a loaded and unloaded 32-bit  $\mu$ C. (a) Unloaded. (b) Partially loaded. (c) Fully loaded. (d) TEM cell used for the purpose of this study [22].

A 10 cm  $\times$  10 cm PCB with a 32-bit  $\mu$ C (ATMEL SAM3S4B) [21] was employed for the experiments (see Fig. 11). The  $\mu$ C was configured to generate a 48-MHz core clock from its internal PLL referenced by an external 18.432 MHz crystal. It was then programmed with simple software toggling one output pin at a fixed frequency (about 1.5 kHz).

A previous measurement campaign highlighted that the clock generation circuitry of that  $\mu C$  was sensitive to continuous-wave

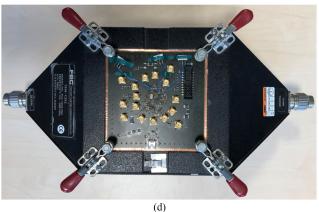

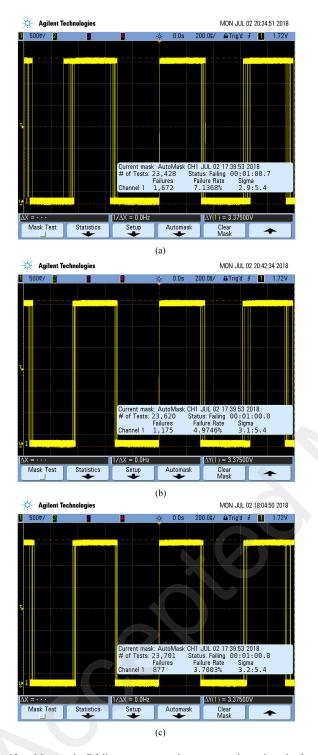

Fig. 12. Measured  $\mu$ C failure rate averaged over a one-minute time slot for an input power of 20 W at 223 MHz. (a) Unloaded. (b) Partially loaded. (c) Fully loaded.

interference at 223 MHz. Therefore, immunity could be assessed by measuring the jitter of the output signal through automatic mask testing, thanks to a Keysight DSO6014L oscilloscope fitted with the appropriate option. The time-domain limit of the mask was fixed at a 5% deviation in signal period in both directions (lower and higher). The immunity criterion was the statistical failure rate (i.e., the output signal leaving the area of the oscilloscope mask) averaged over a one-minute time slot. The PCB was secured on the aperture of the TEM cell and exposed to radiated interference through continuous-wave power injection into the septum [see Fig. 11(d)], thanks to a Keysight N5183A generator feeding a Prâna AP32DT120 20 W power amplifier. The other port of the TEM cell was terminated with a 50- $\Omega$  load. Incident and reflected powers were monitored with a Keysight E4419B dual-channel power meter through the built-in directional coupler of the amplifier. As mentioned in Section II, the PLL of a  $\mu$ C is highly sensitive to a tangential magnetic field coupled to its power supply pins (namely V<sub>DDPLL</sub>), provided that the field component is in the same direction as the loops formed by the pins on the PCB: The PLL is perturbed when the interference is propagated into its power supply rail.

The incident power was measured at 43 dBm (20 W upper limit of the amplifier) while the reflected power was monitored at 15 dBm (31 mW). Of course, the injection frequency was chosen at 223 MHz, in order to make use of the weakness in immunity mentioned previously.

Three different injections were considered: (1) without any dielectric loading [see Fig. 11(a)]; (2) with dielectric loading covering only the PCB traces and  $\mu C$  pins [see Fig. 11(b)]; and (3) with dielectric loading over the whole  $\mu C$  (package and pins) and the PCB traces [see Fig. 11(c)]. They were carried out exactly in the same conditions (same RF power, same PCB location, and orientation). The orientation of the PCB was chosen to maximize magnetic field coupling to the power supply pins. That was demonstrated by the fact that no errors could be observed by rotating the PCB by 90°. Results are shown in Fig. 12 observing a 7.14% failure rate in case (1) [see Fig. 12(a)], 4.97% in case (2) [see Fig. 12(b)], and 3.70% in case (3) [see Fig. 12(c)]. These results clearly demonstrate the improvements in radiated immunity due to dielectric loading in a significant manner. The results also show that dielectric loading not only makes the IC and PCB immune to the electric field, but also decreases the susceptibility of the  $\mu$ C to external magnetic field. From an economic point of view, a dielectric or a non-ferromagnetic material would be a better option compared to a ferrite-based material.

#### V. CONCLUSION

A dielectric loading technique was proposed to improve the radiated immunity of ICs, which has no side effects on their performances. The behavior of an electronic circuit with a loaded IC was compared to an unloaded one both in near and far fields. It was found that, independently of frequency, a loaded circuit is less susceptible compared to an unloaded one due to the reactive field confinement in the dielectric load without inducing side effects on its performance. Moreover, loading an IC with non-ferromagnetic dielectric material proved to be effective to enhance its susceptibility to both magnetic and electric field, which makes it possible to reduce the cost of the technique compared to the ubiquitous use of ferrites. An experimental show case study using a TEM cell proved a  $\sim 48\%$  less failure rate for a loaded  $\mu$ C (ATMEL SAM3S4B) compared to the unloaded IC. The obtained results demonstrate the suitability of the proposed technique as a potential candidate to improve the radiated immunity of electronic devices.

#### ACKNOWLEDGMENT

The authors would like to cordially thank V. Arboux for his assistance with prototype construction.

#### REFERENCES

- [1] S. Ben Dhia, M. Ramdani, and E. Sicard, Electromagnetic Compatibility of Integrated Circuits: Techniques for Low Emission and Susceptibility. Berlin, Germany: Springer, 2006.

- [2] F. Pythoud, "Proficiency testing in EMC radiated immunity," IEEE Trans. *Electromagn. Compat.*, vol. 60, no. 5, pp. 1249–1253, Oct. 2018. [3] V. S. Reddy, P. Kralicek, and J. Hansen, "A novel segmentation approach

- for modeling of radiated emission and immunity test setups," IEEE Trans. Electromagn. Compat., vol. 59, no. 6, pp. 1781-1790, Dec. 2017.

- [4] J. Kim, D. G. Kam, P. J. Jun, and J. Kim, "Spread spectrum clock generator with delay cell array to reduce electromagnetic interference," IEEE Trans. Electromagn. Compat., vol. 47, no. 4, pp. 908-920, Nov. 2005

- [5] S.-Y. Yuan, Y.-L. Wu, R. Perdriau, and S.-S. Liao, "Detection of electromagnetic interference in microcontrollers using the instability of an embedded phase-lock loop," IEEE Trans. Electromagn. Compat., vol. 55, no. 2, pp. 299-306, Apr. 2013.

- [6] Integrated Circuits, Measurement of Electromagnetic Immunity, 150 kHz to 1 GHz: General Conditions and Definitions, Second Edition, IEC 62132-1, 2015.

- [7] S. Op't Land, "Integrated circuit immunity modeling beyond 1 GHz," Ph.D. dissertation, INSA-Rennes, Rennes, France, 2014.

- [8] M. Ramdani et al., "The electromagnetic compatibility of integrated circuits-past, present, and future," IEEE Trans. Electromagn. Compat., vol. 51, no. 1, pp. 78-100, Feb. 2009.

- W. H. Parker, "Electromagnetic interference: A tutorial," in Proc. IEEE [9] Aerosp. Appl. Conf., vol. 3. Aspen, CO, USA, 1996, pp. 177-186.

- [10] R. Valente, C. De Ruijter, D. Vlasveld, S. Van Der Zwaag, and P. Groen, "Setup for EMI shielding effectiveness tests of electrically conductive polymer composites at frequencies up to 3.0 GHz," IEEE Access, vol. 5, pp. 16665–16675, 2017.

- [11] 3M EMI/RFI Absorbers. [Online]. Available: https://www.digikey.com/ en/product-highlight/3/3m/emirfi-absorbers

- [12] A. A. Moreira, N. Pires, N. Serro, and R. Santos, "Ultra wideband dielectric sandwich loaded antennas," in Proc. 3rd Eur. Conf. Antennas Propag., Berlin, Germany, 2009, pp. 3535-3538.

- [13] M. Koohestani, N. Pires, A. K. Skrivervik, and A. A. Moreira, "Bandreject ultra-wideband monopole antenna using patch loading," Electron. Lett., vol. 48, no. 16, pp. 974–975, 2012.

- [14] M. Koohestani, N. Pires, A. K. Skrivervik, and A. A. Moreira, "Influence of dielectric loading on the fidelity factor of an ultra wideband monopole antenna," in Proc. Loughborough Antennas Propag. Conf., U.K., 2012, pp. 1–3.

- [15] M. Koohestani, N. Pires, A. K. Skrivervik, and A. A. Moreira, "Bandwidth enhancement of a wearable UWB antenna near a human arm," Microw. Opt. Technol. Lett., vol. 55, no. 12, pp. 2965-2967, 2012.

- [16] N. Lacrampe, S. Serpaud, A. Boyer, and S. Tran, "Radiated suceptibility investigation of electronic board from near field scan method," in Proc. 11th Int. Workshop Electromagn. Compat. Integr. Circuits, Saint-Petersburg, Russia, 2017, pp. 125-130.

- [17] M. Stojanovic, F. Lafon, S. Op't Land, R. Perdriau, and M. Ramdani, "Determination of equivalent coupling surface of passive components using the TEM Cell," IEEE Trans. Electromagn. Compat., vol. 60, no. 2, pp. 298-309, 2018.

- [18] Rogers corporation, RT/Duroid 6002 low-loss high frequency laminates. [Online]. Available: http://www.rogerscorp.com/documents/609/ acm/RT-duroid-6002-laminate-data-sheet

- [19] E. Orietti, S. Saggini, P. Mattavelli, and G. Spiazzi, "Electromagnetic susceptibility analysis on a digital pulse width modulator for SMPSs," IEEE Trans. Electromagn. Compat., vol. 51, no. 4, pp. 1034–1043, Nov. 2009.

- [20] Y. J. Lee et al., "Analysis and measurement of timing jitter induced by radiated EMI noise in automatic test equipment," IEEE Trans. Electromagn. Compat., vol. 52, no. 6, pp. 1749-1755, Dec. 2003.

- [21] ATEMEL SAM3S ARM-based Flash MCU series microcontrollers. [Online]. Available: https://www.microchip.com/wwwproducts/en/ ATsam3s4b

- [22] FCC-TEM-JM2 TEM cell, Fischer Custom Communications Inc. [Online]. Available: https://www.fischercc.com/products/fcc-tem-jm2

Mohsen Koohestani (S'13-M'15) received the Ph.D. degree (with honor) in electromagnetics from the École polytechnique fédérale de Lausanne (EPFL), Lausanne, Switzerland, and the Universidade de Lisboa (ULISBOA), Lisbon, Portugal, in 2014.

From 2014 to 2018, he was a Postdoctoral Fellow with the Institut d'Electronique et de Télécommunications de Rennes (IETR), Université de Rennes 1, France, working mainly on biomedical applications of wireless power transfer systems

(WPTs). He is currently an Associate Professor with ESEO, Angers, France, in the field of RF/microwave wireless systems. He is also an Associate Researcher with IETR. He has authored over 40 peer-reviewed scientific journal papers. His research interests include novel design and analysis of antennas and microwave components, design and characterization of human body models, dosimetry and exposure assessment, and WPT and energy harvesting.

Richard Perdriau (M'01-SM'07) was born in Angers, France, in 1971. He received the engineering degree in electronics and computer science from ESEO, Angers, France, in 1992, the Ph.D. degree in applied sciences from Université Catholique de Louvain, Louvain-la-Neuve, Belgium, in 2004, and the "Habilitation Diriger des Recherches" (Accreditation Degree) from Université de Rennes 1, France, in 2012.

From 1992 to 2012, he was an Associate Profes-

sor with ESEO in the fields of microelectronics and

embedded systems. In 2013, he was promoted to Full Professor. His research interests include EMC of integrated circuits, mixed-signal hardware description languages, and integrated circuit design.

Dr. Pedriau served as the Vice-Chair and Technical Program Co-Chair of EMC Europe 2017.

Jean-Luc Levant received the Ph.D. degree from the Institut National des Sciences Appliquées (INSA), Rennes, France, in 2007.

He is currently working with Microchip as a Senior EMC Expert. His research interests include ICs modeling, power and signal integrity, and electrical fast transient analyses.

Dr. Levant is a member of the IEC Standardization Working Group in the SC47A Subcommittee on the EMC for Integrated Circuits.

Mohamed Ramdani (M'01-SM'07) was born in

Oujda, Morocco. He received the Ph.D. degree

in microelectronics from Université Paul Sabatier,

Toulouse, France, in 1989, and the "Habilitation Diriger des Recherches" (Accreditation Degree) from

From 1991 to 2008, he was an Associate Professor

with ESEO, Angers, France, in the fields of micro-

electronics and microwave electronics. In 2008, he

was promoted to Full Professor. His research inter-

Université de Rennes 1, France, in 2004.

ests include EMC of integrated circuits and integrated circuit design. Dr. Ramdani is a member of Union Technique de l'Electricité et de la communication (UTE - French section of the IEC). He served as General Chair of EMC Europe 2017, which was held in Angers, France. He was elected as the Vice-Chair of the IEEE France Section in 2016.