## A Predictive Hybrid Pulse-Width-Modulation Technique for Active-Front-End Rectifiers

Martin Gendrin, Jean-Yves Gauthier, Xuefang Lin-Shi

### ▶ To cite this version:

Martin Gendrin, Jean-Yves Gauthier, Xuefang Lin-Shi. A Predictive Hybrid Pulse-Width-Modulation Technique for Active-Front-End Rectifiers. IEEE Transactions on Power Electronics, 2017, 32 (7), pp.5487-5496. 10.1109/TPEL.2016.2612832 . hal-01983352

### HAL Id: hal-01983352 https://hal.science/hal-01983352v1

Submitted on 13 May 2022

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# A Predictive Hybrid Pulse-Width-Modulation Technique for Active Front-End Rectifiers

Martin Gendrin, Jean-Yves Gauthier, Xuefang Lin-Shi, Member, IEEE

Laboratoire Ampère, Université de Lyon, Institut National des Sciences Appliquées

21 avenue Jean-Capelle, 69621 Villeurbanne, France

Email: martin.gendrin@insa-lyon.fr, jean-yves.gauthier@insa-lyon.fr, xuefang.shi@insa-lyon.fr

Abstract-Nowadays Active-Front-End (AFE) rectifiers are increasingly used as grid connected devices. Their efficiency and performances have become relevant for reducing the overall grid losses. This paper thus introduces a Predictive Hybrid Pulse-Width-Modulation (PH-PWM) technique, adaptable to any Space Vector PWM (SVPWM) controller. As opposed to hybrid PWM techniques based on sector partitioning, the PH-PWM technique selects the appropriate PWM sequence on-line with the help of a predictive algorithm. This selection is based on a cost-function where users can define a trade-off between various criteria, such as the reduction of current distortion and of switching losses, as presented in this paper. The use of the PH-PWM technique increases performances in comparison with the conventional PWM techniques. The simulation and experimental results are presented to confirm the effectiveness of the proposed PH-PWM technique. Aside from the trade-off capacity of the proposed PH-PWM technique, the simulation results validate a reduction of the switching losses for the converter up to 23% as compared with the conventional SVPWM technique.

*Index Terms*—Bus-clamping PWM, Space Vector PWM, hybrid PWM techniques, Model Predictive Control, Active-Front-End rectifier

#### I. INTRODUCTION

CTIVE front-end (AFE) rectifiers are more and more being considered for use as grid-connected devices. When compared to the diode rectifiers, they enable a bi-directional power flow. They also offer a naturally low current distortion and cancel the requirement for heavy inductive filters between the grid and the rectifiers. Therefore, these topologies are increasingly used as active filters, to correct the power factor of loads or to compensate the lack of reactive power in the source grid. Due to good features, AFE rectifiers are the focus of many scientific papers. They aim to produce fast and reliable grid controllers that keep the current distortion low without increasing the size of inductive filters, which at the same time improves the efficiency of the rectifiers.

One possible control structure of an AFE rectifier is the direct controller. At each sample time, it enables the selection of the switching configuration to be applied on the converter. The Direct Power Control (DPC) [1] and the Finite Control Set Predictive-DPC (FCS P-DPC) [2][3][4][5] are both based on this working principle. More recently, a Modified Model Predictive Control (MMPC) was proposed in [6]. However despite its good dynamic performances, the direct controller approach

suffers from a variable frequency spectrum and requires a high sampling frequency. Therefore in this study, a controller with a space vector Pulse Width Modulation (SVPWM) generator has been preferred, such as the Voltage-Oriented Control (VOC) [7] or the Predictive - DPC (P-DPC) [8][9]. Those controllers deliver the required dwell-times of the switching configurations to be used and the corresponding sector to the SVPWM generator that produces the switching sequence. For all controllers with a SVPWM generator, the switching frequency is fixed, and the constraint on the sampling time is reduced.

1

The modulation schemes have in the recent years become the center of a growing number of studies, due to their key role in the development of modern power electronics [10]. In particular, the SVPWM generator enables a precise application of the voltage reference to the AC-side of the converter. Furthermore, in SVPWM, a given voltage reference can be applied by different PWM sequences that lead to the same voltage in an average perspective over the PWM period, but have a specific current distortion and specific switching losses. Therefore, several Hybrid PWM techniques have been detailed in the literature as well as coupled PWM sequences. The by far most popular PWM technique is the conventional spacevector PWM (CSVPWM) because it implies a high line-side voltage and a low current distortion over a large range of modulation indexes [11]. However at high modulation indexes, the bus-clamping PWM (BCPWM) techniques represent good candidates [11] [9]. In one study [12], a hybrid PWM technique using a CSVPWM sequence and BCPWM sequences was developed to reduce the torque ripple linked to the q-axis current component in a permanent magnet synchronous motor. Novel specific BCPWM-type sequences were introduced in [13] and [14], enabling the production of new hybrid PWM techniques. In other investigations [14] [11], the aforementioned sequences were used in hybrid PWM techniques so as to reduce the resultant current distortion. Such hybrid PWM techniques were also used to reduce both current distortion and switching losses in [15], to diminish the acoustic noise of an induction motor in [16] or to lower the torque ripple of an induction motor in [17][18]. Recently [19] [20], new sequences were drawn for three-level converters and novel hybrid PWM techniques were introduced.

Although the aforementioned Hybrid PWM techniques achieve an improvement in comparison with CSVPWM, they are all based on a sector partitioning to select the appropriate sequence and are therefore fixed designs. For this reason, the latter hybrid PWM techniques cannot be optimized for all the existing operating conditions. The contribution of this paper is to propose a Predictive Hybrid PWM (PH-PWM) technique for an AFE rectifier, that can be coupled to any kind of SVPWM controller. The originality is that the PWM sequences are selected on-line by a predictive algorithm. The choice of the PWM sequence is based on a user-defined tradeoff between various criteria, such as the current distortion and the switching losses. The trade-off can be adjusted on-line, which offers more flexibility than the existing hybrid PWM techniques and enables a better fitting to the working point under consideration. Independent of the used SVPWM-based controller, the proposed PH-PWM technique achieves both a better current Total Harmonic Distortion (THD) and lower switching losses through modulation without change of the AFE converter. Here, a conventional VOC is used since it is more reputed and since the contribution of this paper focuses on the modulation level.

The rest of the paper is organized as follows. Section II describes the AFE rectifier and its control scheme to indicate where the proposed PH-PWM is located. Section III introduces the principle of the PH-PWM technique, including the specification of the considered PWM sequences, the current distortion and switching loss predictions mandatory for the cost function calculation, and the predictive algorithm. Section IV analyzes the simulation results and Section V presents the experimental results and shows the effectiveness of the proposed solution.

#### II. THE AFE RECTIFIER AND ITS CONTROL SCHEME

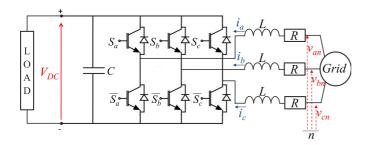

The considered AFE rectifier is composed of a basic three-leg two-level converter, a set of three inductances on the AC side and a storage capacitor connected in parallel to the load on the DC side, as depicted in Fig. 1. In order to control this structure, one can use a VOC controller, which is a vector control based on a rotating dq reference frame with the *d*-axis aligned with the grid-voltage. In this frame, the current behavior is described by the following model:

$$V_d = -R \cdot i_d - L \cdot i_d + L \cdot \omega \cdot i_q + V_{gridd}$$

$$V_q = -R \cdot i_q - L \cdot i_q - L \cdot \omega \cdot i_d + V_{gridq}$$

(1)

where  $V_d$  and  $V_q$  are the *d*- and *q*- axis voltages on the rectifier side,  $i_d$  and  $i_q$  are the *d*- and *q*-axis currents, *L* and *R* are

Fig. 1. Functional scheme of an AFE based on a three-leg two-level converter.

0885-8993 (c) 2016 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

2

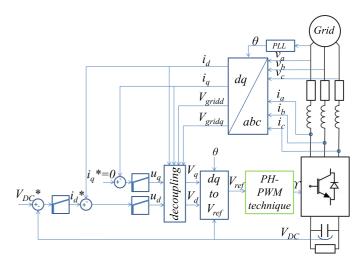

Fig. 2. Functional scheme of the complete VOC of the AFE rectifier with the proposed Predictive Hybrid PWM technique.

the line inductance and resistance,  $\omega$  is the grid pulsation, and  $V_{gridd}$  and  $V_{gridq}$  are the projection of the grid voltage on the d- and q-axis, respectively. The functional scheme of the AFE controller is given in Fig. 2. To separately control the dand q-axis currents, the decoupling terms  $e_d = L\omega i_q + V_{qridd}$ and  $e_q = -L\omega i_d + V_{gridq}$  are added to the outputs,  $u_d$  and  $u_q$ , of the current regulators, thus enabling the control of  $i_d$ and  $i_q$  by conventional proportional-integral (PI) controllers. To simultaneously achieve the control of the DC bus voltage and a unity power factor, a voltage PI controller delivers a current reference to the d-axis current controller. The q-axis current reference is set to 0. The resultant control voltages,  $V_d$  and  $V_q$ , are then translated into a voltage reference  $V_{ref}$  delivered to the proposed PH-PWM technique which is the focus of this paper and which is developed in the next section. The PH-PWM technique applies this voltage reference to the AC side of the converter taking into account its discrete characteristics. The resulting PWM sequence can be implemented with a deadtime compensation method as in [21].

# III. THE PRINCIPLE OF THE PREDICTIVE HYBRID PWM TECHNIQUE

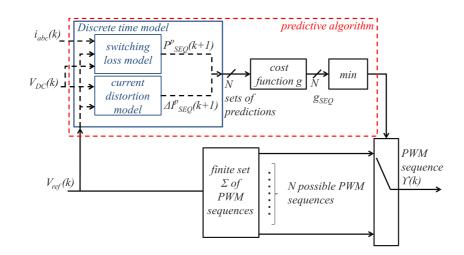

The principle of the PH-PWM technique is drawn as a functional scheme in Fig.3. At each sample time  $k.T_s$ , where  $T_s$  is the sampling period of the VOC controller, it will select the appropriate PWM sequence, among a finite set  $\Sigma$  of N PWM sequences, and use it to apply  $V_{ref}(k)$ . This selection is based on a predictive algorithm, whose principle can be summarized in the following steps:

- At each sample time, k, the voltage reference,  $V_{ref}(k)$ , the three-phase currents,  $i_{abc}(k)$ , and the DC bus voltage,  $V_{DC}(k)$ , are acquired;

- For each considered PWM sequences, the prediction of the current distortion and the switching losses for the next sampling period, noted respectively  $\Delta I_{SEQ}^{p}(k+1)$  and  $P_{SEQ}^{p}(k+1)$ , will be evaluated;

This article has been accepted for publication in a future issue of this journal, but has not been fully edited. Content may change prior to final publication. Citation information: DOI 10.1109/TPEL.2016.2612832, IEEE Transactions on Power Electronics

Fig. 3. Functional scheme of the proposed Predictive-PWM Technique.

• These predictions are integrated in a cost function, given in (2), expressing the trade-off between the reduction of the current distortion and the lowering of the switching losses. In (2),  $\beta$  is a weighting factor enabling the user to adapt the cost function to its specifications;

$$g = \Delta I_{SEQ}^p(k+1) + \beta \cdot P_{SEQ}^p(k+1)$$

(2)

The PWM sequence, Υ(k), whose predictions minimize the cost function, is selected, and applied to the drivers of the converter during the next sampling period.

As such, the predictive algorithm has some similarities to the FCS-MPC which has been extensively covered in the literature [22]. However, contrary to the FCS-MPC which acts on the current or power level, the predictive algorithm is used in a PWM generator. Thus, it has no impact on either the closed loop dynamic, or the system stability.

According to the aforementioned structure of the PH-PWM, we require definitions of the considered PWM sequences  $\Sigma$  and of the discrete-time model enabling the current distortion and the switching loss predictions. They will thus be the focus of the three following subsections.

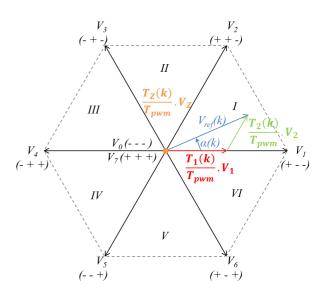

### A. The considered PWM sequences

As a conventional SVPWM generator, the PH-PWM tends, at each sample time, to apply the voltage reference delivered by the controller,  $V_{ref}(k)$ , in an average approach over a PWM period. It therefore considers this reference as a vector of a magnitude,  $v_{ref}(k)$ , and a phase lag,  $\alpha(k)$ , in the stationary reference frame (Fig. 4). It then applies the two nearest among the six existing active configurations for specific dwell times. The zero vector is set for the rest of the PWM period,  $T_{pwm}$ . The magnitude of vectors representing the active configurations in the stationary reference frame and  $v_{ref}(k)$  are normalized with respect to  $\frac{2}{3}$  of the measured  $V_{DC}(k)$ , and  $v_{ref}(k)$  can then be defined as the modulation index. The sum of the resultant vectors equals  $V_{ref}(k)$  in an average approach over

the PWM period, as can be seen for sector I in Fig. 4. For this sector, between the active vectors 1 and 2, the dwell times  $T_1(k)$  and  $T_2(k)$  are calculated as in (3). The zero voltage vector will be applied during  $T_z(k)$ .

$$T_{1}(k) = v_{ref}(k) \cdot \frac{\sin\left(\frac{\pi}{3} - \alpha(k)\right)}{\sin\left(\frac{\pi}{3}\right)} \cdot T_{pwm}$$

$$T_{2}(k) = v_{ref}(k) \cdot \frac{\sin\left(\alpha(k)\right)}{\sin\left(\frac{\pi}{3}\right)} \cdot T_{pwm}$$

$$T_{z}(k) = T_{pwm} - T_{1}(k) - T_{2}(k)$$

(3)

The zero voltage vector can be applied by the two switching configurations 0 and 7, leading to the connection of the three phases of the load either on the negative or on the positive DC bus potential. Moreover, the active configurations can be

Fig. 4. Example of the application of a voltage reference on the load in the normalized stationary reference frame.

applied more than once in the PWM period as long as the total application time equals the corresponding dwell time. A multiplicity of sequences leading to the application of the same value of  $V_{ref}(k)$  arises from these facts. According to the criterium given in [14] and considering a maximum of three switchings per half PWM period, seven sequences emerge:

- the CSVPWM sequence (0127;7210), denoted 0127. In the example of Fig. 4, this corresponds to the application of vectors  $V_0$ ,  $V_1, V_2, V_7$  in the half PWM period. In the other half PWM period, a symmetrical sequence is applied as  $V_7$ ,  $V_2, V_1, V_0$ . This leads to an equal partitioning of the zero vector between 0 and 7;

- the BCPWM sequences (012;210) and (721;127), denoted 012 and 721 respectively, that use either 0 or 7;

- the special BCPWM sequences (0121;1210), (1012;2101), (2721;1272) and (7212;2127), denoted respectively 0121, 1012, 2721 and 7212, which are derived from the BCPWM sequences by applying one of the active configurations twice.

In order to keep the switching frequency over the fundamental independent of the sequences, the PWM period of the BCPWM sequences is set to  $\frac{2}{3}$  of the PWM period of the CSVPWM sequence [14]. The special BCPWM sequences possess the same PWM period as the CSVPWM sequence. These seven sequences form the finite set  $\Sigma$  of PWM sequences of the PH-PWM technique for the rest of the paper, even if more PWM sequences exist and improve other characteristics such as the common mode voltage. It has to be noted that the more PWM sequences that are included in  $\Sigma$ , the more the computational load increases. Therefore, in order to limit it, it is interesting to adapt the composition of  $\Sigma$  according to the user specifications.

Aside from the finite set of PWM sequences, the discretetime model used in the predictive algorithm to predict the behavior of the converter and load association over the next sample time has to be developed.

#### B. The current distortion factor

The factor  $\Delta I_{SEQ}^p(k+1)$ , quantifying the current distortion over the next sample time for every PWM sequences, has to be defined.

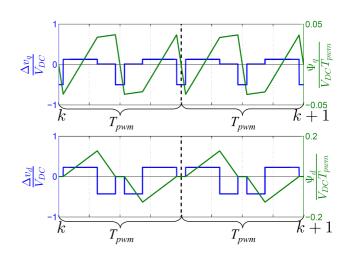

Two approaches make it possible to define the current distortion due to the PWM sequences. This can be studied directly in the stationary reference frame and the phase currents kept as a three-phase system [23][24]. Another approach cancels the influence of the current fundamental on the current distortions [13][14][15][11][17]. It is based on a dq-frame that rotates synchronously with the voltage reference vector,  $V_{ref}$ , and whose q-axis is aligned with  $V_{ref}$ . As has been underlined earlier, the instantaneous three-phase voltages resulting from each PWM sequence achieve the value of  $V_{ref}(k)$  in a average approach between the sample time k and the next sample time k+1. However each sequence leads to a specific instantaneous voltage error  $\Delta v$  over the PWM period, expressed in the dqframe. The time integral of this voltage error is termed the stator flux ripple [15] and is denoted  $\Psi$ . When the phaseresistance of the load can be neglected, which is most often the case for the AFE rectifier, this stator flux ripple is directly proportional to the current ripple. Fig.5 gives as an example the evolution of  $\Delta v$  and  $\Psi$  in the dq-frame between the sample time k and the future sample time k+1 for a specific working point  $(v_{ref}(k) = 0.75 \text{ and } \alpha(k) = 20^{\circ})$  and for the sequence 0127, with two PWM periods per sampling cycle. The shapes of these curves depend on the actual working point, i.e.,  $v_{ref}(k)$ and  $\alpha(k)$ . As the PWM sequences differ in the succession of configurations they induce, the evolution of  $\Delta v$  over the PWM period, and thus of  $\Psi$ , is also specific to the used PWM sequence. In Fig.5, the use of a PWM sequence other than 0127 for this working point results in different values of  $\Delta v$  and  $\Psi$ . The RMS value of the current distortion over the PWM period between the sample time k and the next sample time k + 1enables a comparison of the current distortion induced by each PWM sequence, for the actual working point. It is derived from the RMS value of the stator flux ripple, developed for each sequence in [15], and leads to:

4

$$\Delta I_{SEQ}^{p}(k+1) = \frac{V_{DC}(k) \cdot T_{pwm}}{3 \cdot L} \cdot \left[ C_{0(SEQ,\alpha(k))} \cdot v_{ref}^{2}(k) + C_{1(SEQ,\alpha(k))} \cdot v_{ref}^{3}(k) + C_{2(SEQ,\alpha(k))} \cdot v_{ref}^{4}(k) \right]^{1/2}$$

(4)

Here,  $v_{ref}(k)$  is the modulation index,  $V_{DC}(k)$  the measured DC bus voltage, and the coefficients  $C_0$ ,  $C_1$  and  $C_2$  depend on the chosen PWM sequence and on the phase lag  $\alpha(k)$ . They are taken from [15].

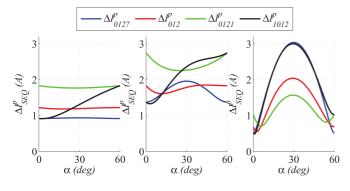

For the studied AFE rectifier with a phase inductance of 2.3mH and a DC bus voltage of 670V, Fig. 6 shows the evolution of the predicted value  $\Delta I_{SEQ}^p(k+1)$  for an  $\alpha(k)$  varying on the first sector for different PWM sequences with three different values of  $v_{ref}(k)$ . Due to the axis symmetry between the sectors, a study on the first sector is sufficient to determine the behavior over the entire stationary reference

Fig. 5. Evolution of  $\Delta v$  and  $\Psi$  between k and k + 1 for the PWM sequence 0127.

0885-8993 (c) 2016 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information

5

Fig. 6. RMS values of the current distortion for different PWM sequences with on the left side  $v_{ref}$ =0.2, on the middle  $v_{ref}$ =0.6 and on the right side  $v_{ref}$ =0.9.

frame.  $\Delta I_{SEQ}^p(k+1)$  induced by the BCPWM sequences using the 0-configuration and the one using the 7-configuration are symmetric around the center of each sector [14]. Only the values of the sequences using the 0-configuration are shown in Fig. 6 for the BCPWM and special BCPWM sequences.

### C. The switching loss factor

The second part of the discrete-time model included in the predictive algorithm of the PH-PWM is the factor  $P_{SEQ}^{p}(k+1)$ , which predicts the switching losses of the converter and load association between the sample time k and the following one, k+1, for each sequences.

If the PWM sequence implies a change of state in one inverter leg, then the energy lost in the switching process during the PWM period,  $T_{pwm}$ , is the sum of the turn-on and turnoff switching losses,  $E_{on}$  and  $E_{off}$ , of each IGBT and of the turn-off switching losses,  $E_{offD}$ , of each diode. These values are normally given in the datasheets of the IGBT/diode module for specific test conditions,  $V_{test}$  and  $I_{test}$ . By assuming that  $E_{on}$ ,  $E_{off}$  and  $E_{offD}$  of one module are proportional to the DC bus voltage,  $V_{DC}$ , and to the phase current, *i*, their values are ruled by (5) [25].

$$E_{off} = \frac{1}{2} \cdot \frac{2 \cdot E_{off \ test}}{V_{test} \cdot I_{test}} \cdot i \cdot V_{DC} = \frac{t_{off}}{2} \cdot i \cdot V_{DC}$$

$$E_{on} = \frac{1}{2} \cdot \frac{2 \cdot E_{on \ test}}{V_{test} \cdot I_{test}} \cdot i \cdot V_{DC} = \frac{t_{on}}{2} \cdot i \cdot V_{DC} \quad (5)$$

$$1 \quad 2 \cdot E_{offD \ test} \quad t_{offD}$$

$$E_{offD} = \frac{1}{2} \cdot \frac{2 \cdot E_{offD \ test}}{V_{test} \cdot I_{test}} \cdot i \cdot V_{DC} = \frac{t_{offD}}{2} \cdot i \cdot V_{DC}$$

where  $t_{on}$ ,  $t_{off}$  and  $t_{offD}$  are the resultant equivalent turnon and turn-off times respectively, and  $E_{on \ test}$ ,  $E_{off \ test}$  and  $E_{offD \ test}$  the energy losses in the test conditions.

A second-order behavioral model between the switching losses and the phase current is actually more accurate [25][26], but as  $P_{SEQ}^p(k+1)$  has to be kept simple, the linear model is going to be considered. According to (5), this factor can be evaluated for the different PWM sequences as the sum of the energies lost in each leg in the switching process over a PWM period. It results in (6) for the sequence 0127:

$$P_{0127}^{p}(k+1) = \frac{1}{T_{pwm}} \cdot V_{DC}(k) \cdot (t_{on} + t_{off} + t_{offD}) \\ \cdot (|i_{a}(k)| + |i_{b}(k)| + |i_{c}(k)|)$$

(6)

For the BCPWM sequences, it results in (7):

$$P_{SEQ}^{p}(k) = \frac{3}{2T_{pwm}} \cdot V_{DC}(k) \cdot (t_{on} + t_{off} + t_{offD}) \\ \cdot (|i_{i}(k)| + |i_{j}(k)|)$$

(7)

where SEQ denotes 012 or 721, i and j denote the two nonclamped phases a, b, or c on the PWM period.

For the special BCPWM sequences, (8) is obtained:

$$P_{SEQ}^{p}(k) = \frac{1}{T_{pwm}} \cdot V_{DC}(k) \cdot (t_{on} + t_{off} + t_{offD}) \\ \cdot (2 \cdot |i_i(k)| + |i_j(k)|)$$

(8)

where SEQ denotes 0121, 7212, 1012 or 2721, i denotes the double-switching phase a, b, or c and j denotes the single-switching phase a, b, or c on the PWM period.

In short, with the acquired three-phase currents  $i_{abc}(k)$ , voltage reference  $V_{ref}(k)$  and DC bus voltage  $V_{DC}(k)$  at the current sample time, the predictions of the current distortion and the switching losses caused be each PWM sequence between k and k + 1 will be quantified by using (4)-(8).

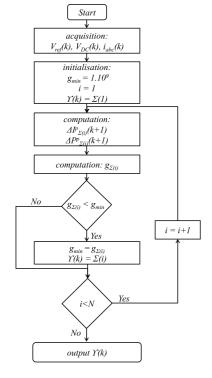

#### D. The predictive algorithm

According to the descriptions above, the predictive algorithm included in the proposed PH-PWM technique to select the appropriate PWM sequence can be formulated as an algorithm of Fig. 7.

According to the developed discrete time model, the results obtained with the PH-PWM technique are relatively independent of a variation of inductance of the input filter as long as this value is the same for the three lines. Indeed, since the current distortion model is based on the stator flux ripple for the different PWM sequences, the inductance value does not impact their order. The switching loss model will not depend on the input filter parameters. Thus the only effect of the variation of the inductance value is the same as a modification of the weighting factor  $\beta$  of (2), so it leads to a slightly different trade-off as opposed to the one that the user has defined.

#### **IV. SIMULATION RESULTS**

In order to show the effectiveness of the proposed PH-PWM technique, the system which corresponds to the VOC controlled AFE-rectifier, presented in Fig. 2, will be simulated. The resulting electrical signals will be compared to the ones issued from the same VOC controlled AFE-rectifier using two other PWM techniques: the CSVPWM technique and the BCPWM technique. This simulation study will be performed for three different cases, corresponding to three user specifications. In the first considered specification, the user just wants to reduce

6

Fig. 7. Algorithm of the predictive algorithm that defines the PWM sequence to be used in the PH-PWM technique, with  $\Sigma=\{0127,012,721,0121,7212,1012,2721\}.$

the current distortion. In the second specification, the user prioritizes the switching losses. In the last specification, the user wants to achieve a trade-off between the current distortion and the switching losses.

The complete system shown in Fig. 2 is modeled in Matlab/Simulink using the SimPowerSystem toolbox for the electrical elements. The grid is modeled as ideal three-phase voltages, whose values are set to represent the European grid. The line inductances are modeled with their parasitic resistances. The parameters are given in Table I. The resistive load is set to consume a nominal power of 4kW at a nominal DC bus voltage of 670V. All the physical parts are modeled with an ode23tb variable step-solver.

From a control point of view, the control loops of the VOC and the predictive algorithm of the PH-PWM technique are implemented with a sampling frequency,  $F_s$ , fixed at 3kHz. The PWM sequences are created with a frequency of 2.25MHz, offering a decimation of 250 points per PWM period for the BCPWM sequences.

TABLE I PARAMETERS USED FOR THE SIMULATION

| Grid frequency $\omega$ (Hz) | 50  | Grid peak voltage $V_{peak}$ (V)    | 325,27 |

|------------------------------|-----|-------------------------------------|--------|

| Line inductance $L(mH)$      | 2.3 | Line parasitic resistor $R(\Omega)$ | 0.6586 |

| Storage Capacitor $C$ $(mF)$ | 9.4 | Sampling frequency $F_s$ (kHz)      | 3      |

| PWM frequency CSVPWM         | 6   | PWM frequency BCPWM                 | 9      |

| and special type BCPWM       |     | $F_{pwm2} (kHz)$                    |        |

| $F_{pwm1} (kHz)$             |     | -                                   |        |

### A. Specification 1: reduction of the current distortion

In order to fulfill this specification, the cost function defined in (2) is modified as (9):

$$g = \Delta I_{SEQ}^p(k+1) \tag{9}$$

As the input voltage is set to the fixed grid voltage value given in Table I, the impact of the DC bus voltage level and the modulation indexes is analyzed. The reference of  $V_{DC}$  is set to different values from 600V to 1000V. In this case, the resistive load is adapted according to the operating conditions in order to consume the nominal power.

For each considered operating point, VOC is simulated using the PH-PWM technique, the CSVPWM technique and the  $30^{\circ}$ clamp, which is the BCPWM technique offering the lowest current distortion. In this last technique, the change of zero configurations used is made at the middle of every sector, so that each phase is clamped in the middle  $30^{\circ}$  duration in every quarter cycle of the fundamental [13]. To quantify the results, the RMS value of the current distortion over several periods of the fundamental is calculated according to (10):

$$\Delta I_{RMS} = \sqrt{\frac{1}{N_s} \sum_{i=1}^{N_s} (di_a)^2}$$

(10)

Here  $N_s$  is the number of samples (1.10<sup>6</sup> samples),  $di_a$  is the instantaneous current distortion of the first line current  $i_a$ , and is defined as the difference between the instantaneous current  $i_a$  and its fundamental.

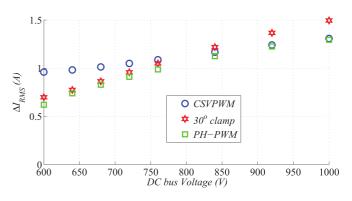

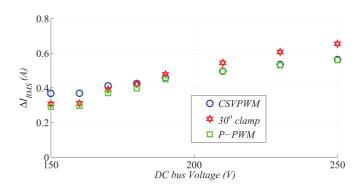

The simulated results are given in Fig. 8 according to the voltage reference. For a low DC bus voltage, the modulation index is high, and the  $30^{\circ}$  clamp therefore gives less current distortion. As the DC bus voltage increases, the modulation index drops, and the CSVPWM technique becomes more interesting with regard to the current distortion. For all the conditions, the PH-PWM technique demonstrates the lowest current distortion.

Fig. 8. Simulated RMS values of the current distortion for the three considered PWM techniques.

7

#### B. Specification 2: the reduction of the switching losses

In this specification, the user focuses on the switching losses of the converter. This means that the cost function described in (2) becomes:

$$g = P^p_{SEO}(k+1) \tag{11}$$

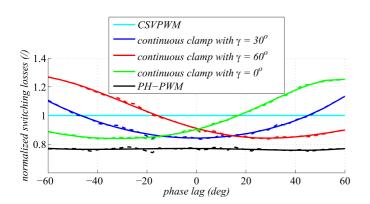

The performances of the hybrid PWM techniques developed in literature regarding the switching losses are highly dependent on the phase lag between the three-phase currents and the three-phase voltages. Therefore, in order to quantify the performances of the PH-PWM technique compared with the other PWM methods, the DC bus voltage is set to its nominal value 670V. The *q*-axis current reference, and thereby the reactive power, varies in order to change the phase lag between the three-phase voltages and the resultant three-phase currents.

The simulation results obtained with the PH-PWM technique are compared with respectively the ones with the CSVPWM technique and with those of the continual BCPWM techniques. The continual BCPWM techniques lead to the clamping of every phase continually for a  $60^{\circ}$  duration in every half cycle of the fundamental. The angle at which the change between the two zero configurations is made in the sectors, noted  $\gamma$ , can vary from  $0^{\circ}$  and  $60^{\circ}$ , and it shifts the clamping duration on the half cycle of the fundamental, resulting in different continual BCPWM techniques. These achieve the lowest switching losses among the BCPWM techniques [13]. The common  $60^{\circ}$  clamp, for example, has a  $\gamma$  of  $30^{\circ}$ , leading to a clamping of each phase in the middle of every half cycle of the fundamental, and thus to the lowest switching losses at unity power factor. Fig. 9 presents the simulated switching losses normalized by the switching losses obtained with the CSVPWM technique. In this plot, the dotted lines represent the raw simulation data and the solid lines correspond to the resulting polynomial curve fitting. As can be seen, the switching losses with the continual BCPWM techniques have a local minimum at a phase lag of  $-30^{\circ}$ ,  $0^{\circ}$  or  $30^{\circ}$  depending of the value of  $\gamma$ . The proposed PH-PWM technique demonstrates a better reduction of the switching losses independently of the phase lag. It leads to

Fig. 9. Normalized switching losses obtained in simulation for the considered PWM techniques vs the phase lag between the current and the voltage systems.

a constant reduction of the switching losses close to 23% in comparison to the CSVPWM technique, whereas the  $60^{\circ}$  clamps only enable a reduction of at most 16% in comparison with the CSVPWM.

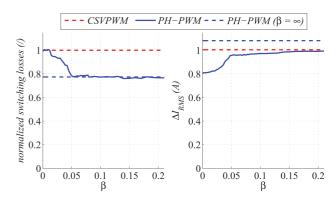

# C. Specification 3: the trade-off between the current distortion and the switching losses

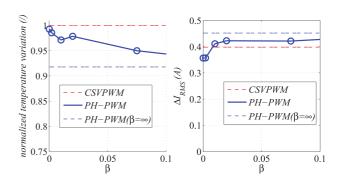

When the user wants to make a trade-off between the current distortion and the switching losses, (2) has to be implemented as the cost function, and the user has to choose the weighting factor  $\beta$ . To show the influence of  $\beta$ , the simulated normalized switching losses and the simulated normalized current distortion obtained with the PH-PWM technique on the nominal operating point are given in Fig. 10. Here,  $\beta$  is varied from 0 to 0.21, and the CSVPWM technique serves as a reference. As can be seen, an increase in  $\beta$  leads to a decrease of the switching losses and an increase of the current distortion. The resultant values of the switching losses and current distortion stabilize for higher values of  $\beta$  and converge in a slower manner to the values obtained for  $\beta = \infty$ . The distortions on the switching losses presented in Fig. 10 are due to the fact that the switching between two PWM sequences is not taken into account, leading to a difference between the estimated switching losses and their real counterparts.

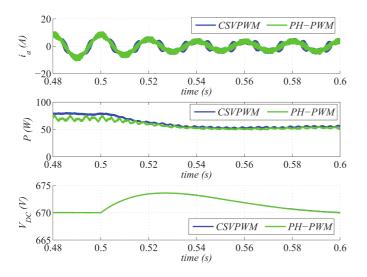

According to the latter curves and for the nominal operating point, an appropriate trade-off can be obtained by fixing the weighting factor  $\beta$  to 0.039. This enables a 12.7% reduction of the switching losses, and still 10% less current distortion than the CSVPWM technique. Once the value of  $\beta$  is set, the AFE-rectifier controlled by VOC using the resulting PH-PWM technique is simulated for a change in the load from its nominal value to half of its nominal value. The simulated  $i_a$ , the simulated switching losses and the simulated  $V_{DC}$  are given in Fig. 11 and are compared to the ones obtained with the CSVPWM technique. As can be clearly seen in Fig. 11, the PH-PWM technique enables a reduction of both the current distortion and the switching losses in comparison with the CSVPWM technique without impacting the DC bus voltage. Both PWM techniques lead to the same DC bus voltage (Fig. 11).

Fig. 10. Normalized switching losses and normalized current distortion for the PH-PWM technique for different values of  $\beta$ .

Fig. 11. Simulated waveforms of line current,  $i_a$ , switching losses, P, and DC bus voltage,  $V_{DC}$ , for a  $\beta = 0.039$ .

It has to be noted that the shape of the curves presented in Fig.10 depends slightly on the working point, leading to a variation of the gains obtained with PH-PWM. However, this effect can be countered by an on-line variation of the weighting factor  $\beta$ .

According to Figs. 8-11, the simulation results presented in this section make it clear that the use of the PH-PWM technique enables an increase in performances of the controlled AFE rectifier. It shows the ability of the proposed PH-PWM technique to reduce both the current distortion and the switching losses in this grid connected device. It also demonstrates the adaptability of the proposed design.

### V. EXPERIMENTAL RESULTS

A set of experiments has been realized on a laboratory test bench. It is supplied by the grid through an autotransformer with a fixed reduction ratio of 1/4 for safety reasons. As both the current distortion and the switching losses are proportional to the DC bus voltage, it is assumed that if the experimental results validate the simulation results, an increase in the DC bus voltage can only benefit the proposed design. The output of the autotransformer is linked to a set of three inductances connected to the AC side of an Arcel 17kW three-phase twolevels converter. Its parameters are given in Table I.

From an implementation point of view, the VOC and the predictive algorithm of the PH-PWM technique are implemented on a dSPACE DS1006 with a sampling frequency  $F_s$  of 3kHz. The creation of the PWM sequence, the addition of the deadtime (3 $\mu s$ ) and the PWM sequence selector are implemented on a dSPACE DS5203 FPGA board. The choice of the PWM sequence is communicated at each  $T_s$  at the same time as  $V_{ref}(k)$  between the two boards. To ensure the acquisition of the many electrical signals at a proper time independently of the used PWM sequence, the PWM period,  $T_{pwm}$ , is set to  $2.T_s$ , leading to a PWM frequency of 6kHz for the CSVPWM sequence and for the special BCPWM sequences, and of 9kHz for the BCPWM sequences. The clock frequency of the FPGA is fixed on the DS5203 at 10MHz, enabling over a thousand points per PWM period and thus a high resolution.

8

The tests on a VOC-controlled AFE with the PH-PWM technique are performed for specification 1 and specification 3. The studied working points are adapted in order to keep the same modulation indexes as in the simulation section.

#### A. Specification 1: the reduction of the current distortion

Fig. 12 presents the experimental RMS values of the current distortion calculated with (10) when (9) is used as a cost function for the PH-PWM technique. The DC bus voltage is set between 150V to 250V, and the resistive load consumes 1kW. Due to the low DC-bus voltage values, the current distortions as well as the resulting gains obtained with the proposed PH-PWM technique in comparison to the two other PWM techniques presented in Fig. 12 are lower than the ones obtained in simulation. However, if the DC bus voltages are normalized with respectively 1000V for the simulation and 250V for the experimentation, the normalized ranges where the CSVPWM technique and the 30° clamp demonstrate better results are mostly respected when compared with the simulation results. Furthermore, when the gains obtained with the proposed PH-PWM technique are expressed in percent of the RMS values of the current distortion of the other techniques, comparable values in simulation and in experimentation are achieved. Nevertheless, the obtained experimental results prove that the proposed PH-PWM technique is able to reduce the current distortion when (9) is used as the cost function.

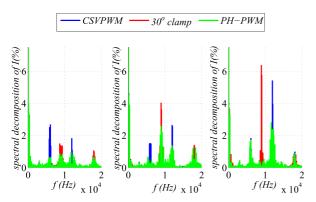

The spectral decomposition of the current distortion obtained in experimentation for a DC bus voltage of 150V, 190V and 250V is given in Fig. 13. It can be seen that in the higher frequency range, the PH-PWM technique presents lower harmonic peaks than the two other techniques regardless of the studied operating point. These peaks are spread over the two PWM frequencies,  $F_{pwm1}$  and  $F_{pwm2}$ , defined in Table I, since all the possible PWM sequences are used. In the lower frequency range, the spectral decompositions of the line current present significant harmonic peaks for all the PWM

Fig. 12. Experimental RMS values of the current distortion for the three considered PWM techniques.

0885-8993 (c) 2016 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

This article has been accepted for publication in a future issue of this journal, but has not been fully edited. Content may change prior to final publication. Citation information: DOI 10.1109/TPEL.2016.2612832, IEEE Transactions on Power Electronics

Fig. 13. Experimental spectral decomposition of the line current for the three PWM techniques for a DC bus voltage of 150V, 190V and 250V, respectively.

techniques and all the DC bus voltages. They are mostly due to the harmonic distortions of the voltage grid that are not completely canceled by the decoupling in VOC. These current harmonics result in a THD value calculated for the first 30 harmonics, varying between 4.7% and 6.7%. Throughout, there is no correlation between the use of a specific PWM technique and the minimization of the THD for the first 30 harmonics. Thus, the proposed PH-PWM technique enables a reduction of the current distortion in the higher frequency range without significantly impacting the lower frequency range.

# *B.* Specification 3: the trade-off between the reduction of the current distortion and the switching losses

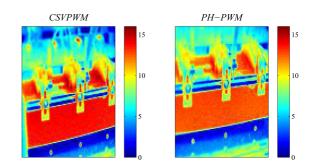

To validate the trade-off ability of the PH-PWM technique as well as its capacity to reduce the switching losses, the DC bus voltage is set to 160V and the resistive load is adapted in order to consume 1kW. Here, (2) is used as the cost function. To quantify the resulting reductions of switching losses, the temperature variation on the converter using the PH-PWM technique is measured with a FLUKE TI9 thermal camera and normalized with the one obtained with the CSVPWM. The use of a thermal camera makes it possible to avoid the installation of a temperature sensor directly on the converter used in the laboratory, and still offers the required precision. Furthermore, it delivers a global overview of the temperature of the converter. Fig. 14 presents the normalized temperature variation and the current distortion versus the weighting factor  $\beta$ . The results obtained with the CSVPWM technique are given as a reference. The figure proves the predicted behavior: an increase in  $\beta$  induces a decrease of the temperature variation for the converter and an increase of the current distortion. The maximal gain obtained with regard to the temperature variation is about 8.21% and involves both the conduction and the switching losses for the converter. Fig. 15 shows the temperature increase measured for a test of two hours for the PH-PWM technique when  $\beta$  is very large and for the CSVPWM technique. The figure displays a reduced overall temperature increase for the PH-PWM technique in comparison with its CSVPWM counterpart.

Fig. 14. Evolution of the temperature variation on the converter and of the current distortion vs  $\beta$  for the PH-PWM technique (experimental results).

Fig. 15. Temperature increase in degrees Celsius measured for the converter for the CSVPWM technique and for the PH-PWM technique.

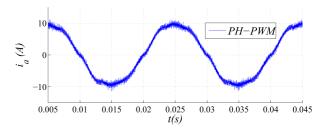

According to Fig. 14 and to the operating point, fixing  $\beta$  in the cost function (2) at 0.075 enables a reduction of 5% of the temperature variation for the converter for a small increase of the current distortion of 0.02A in comparison with CSVPWM. The measured  $i_a$  resulting from this operating point is given in Fig. 16 for a  $\beta$  of 0.075, and shows the closed-loop behavior of the complete VOC controlled AFE rectifier. One can also decide to keep the same current distortion as with the CSVPWM by setting  $\beta$  at 0.0083, leading to a temperature increase that is reduced by 2.55%.

Therefore, both the reductions with regard to the current distortion and the switching losses as well as the trade-off ability of the PH-PWM technique are validated by experimental results. Furthermore, in the proposed technique, the weighting factor  $\beta$  can be tuned on-line by a supervisor, in order to more accurately fit the working conditions.

Fig. 16. Measured  $i_a$  for the considered working point and for the PH-PWM technique with  $\beta=0.075.$

#### VI. CONCLUSION

This paper describes the integration of a PH-PWM technique in a VOC to control an AFE-rectifier. The method selects the appropriate PWM sequence on-line according to the operating point with the help of a predictive algorithm applied at the level of PWM generation. The effectiveness of the proposed PH-PWM technique has been validated both in simulation and in experimentation, and was found to enable larger reductions of both the switching losses and the current distortions in comparison with the conventional PWM techniques. Furthermore, the trade-off between the current distortion and the switching losses can be adapted by fixing a weighting factor. This weighting factor can also be varied on-line, enabling us to increase the range of performance improvements that are attainable with the proposed PH-PWM. Consequently the resulting PH-PWM technique offers increased performances in comparison with existing PWM generators. The proposed PH-PWM technique can be associated with other PWM based controllers, such as a Predictive Direct Power Controller, to improve the performance of an AFE rectifier both with regard to power control and modulation. This association enables a fixed switching frequency as well as a lower computational load in comparison with the direct control methods. The PH-PWM technique can be extended to enable a reduction of other parasitic phenomena, such as the common-mode-voltage, by taking into account their models in the cost function.

#### ACKNOWLEDGMENT

As a part of the ELEXC FUI project, the authors have to be thankful for the financial support of the French government. The authors also would like to thank the industrial partners as Volvo CE and Bonfiglioli for the sharing of knowledge and data.

#### REFERENCES

- Y. Zhang, Z. Li, Y. Zhang, W. Xie, Z. Piao, and C. Hu, "Performance improvement of direct power control of pwm rectifier with simple calculation," *Power Electronics, IEEE Transactions on*, vol. 28, no. 7, pp. 3428–3437, July 2013.

- [2] D. Quevedo, R. Aguilera, M. Perez, and P. Cortes, "Finite control set mpc of an afe rectifier with dynamic references," in *Industrial Technology* (*ICIT*), 2010 IEEE International Conference on, March 2010, pp. 1265– 1270.

- [3] D. Quevedo, R. Aguilera, M. Perez, P. Cortes, and R. Lizana, "Model predictive control of an afe rectifier with dynamic references," *Power Electronics, IEEE Transactions on*, vol. 27, no. 7, pp. 3128–3136, July 2013.

- [4] M. Perez, R. Fuentes, and J. Rodriguez, "Predictive control of dc-link voltage in an active-front-end rectifier," in *Industrial Electronics (ISIE)*, 2011 IEEE International Symposium on, June 2011, pp. 1811–1816.

- [5] S. Kwak, U.-C. Moon, and J.-C. Park, "Predictive-control-based direct power control with an adaptive parameter identification technique for improved afe performance," *Power Electronics, IEEE Transactions on*, vol. 29, no. 11, pp. 6178–6187, Nov 2014.

- [6] M. P. Akter, S. Mekhilef, N. M. L. Tan, and H. Akagi, "Modified model predictive control of a bidirectional ac-dc converter based on lyapunov function for energy storage systems," *IEEE Transactions on Industrial Electronics*, vol. 63, no. 2, pp. 704–715, Feb 2016.

- [7] Y. Zhang, Q. Zhang, Z. Li, and Y. Zhang, "Comparative study of model predictive current control and voltage oriented control for pwm rectifiers," in *Electrical Machines and Systems (ICEMS)*, 2013 International Conference on, Oct 2013, pp. 2207–2212.

- [8] R. Aguilera, D. Quevedo, S. Vazquez, and L. Franquelo, "Generalized predictive direct power control for ac/dc converters," in *ECCE Asia Downunder (ECCE Asia)*, 2013 IEEE, June 2013, pp. 1215–1220.

- [9] S. Vazquez, A. Marquez, R. Aguilera, D. Quevedo, J. Leon, and L. Franquelo, "Predictive optimal switching sequence direct power control for grid-connected power converters," *Industrial Electronics, IEEE Transactions on*, vol. 62, no. 4, pp. 2010–2020, April 2015.

- [10] J. I. Leon, S. Kouro, L. G. Franquelo, J. Rodriguez, and B. Wu, "The essential role and the continuous evolution of modulation techniques for voltage-source inverters in the past, present, and future power electronics," *IEEE Transactions on Industrial Electronics*, vol. 63, no. 5, pp. 2688– 2701, May 2016.

- [11] V. Hari and G. Narayanan, "Space-vector-based hybrid pulse width modulation technique to reduce line current distortion in induction motor drives," vol. 5, pp. 1463–1471(8), 2012. [Online]. Available: http://digital-library.theiet.org/content/journals/10.1049/iet-pel.2012.0078

- [12] K. Basu, J. Prasad, and G. Narayanan, "Minimization of torque ripple in pwm ac drives," *Industrial Electronics, IEEE Transactions on*, vol. 56, no. 2, pp. 553–558, 2009.

- [13] G. Narayanan, H. Krishnamurthy, D. Zhao, and R. Ayyanar, "Advanced bus-clamping pwm techniquesbased on space vector approach," *Power Electronics, IEEE Transactions on*, vol. 21, no. 4, pp. 974–984, 2006.

- [14] G. Narayanan, V. T. Ranganathan, D. Zhao, H. Krishnamurthy, and R. Ayyanar, "Space vector based hybrid pwm techniques for reduced current ripple," *Industrial Electronics, IEEE Transactions on*, vol. 55, no. 4, pp. 1614–1627, 2008.

- [15] D. Zhao, V. Hari, G. Narayanan, and R. Ayyanar, "Space-vector-based hybrid pulsewidth modulation techniques for reduced harmonic distortion and switching loss," *Power Electronics, IEEE Transactions on*, vol. 25, no. 3, pp. 760–774, 2010.

- [16] A. C. Binojkumar, J. Prasad, and G. Narayanan, "Experimental investigation on the effect of advanced bus-clamping pulsewidth modulation on motor acoustic noise," *Industrial Electronics, IEEE Transactions on*, vol. 60, no. 2, pp. 433–439, 2013.

- [17] V. Hari and G. Narayanan, "Space-vector-based hybrid pwm technique to reduce peak-to-peak torque ripple in induction motor drives," in *Applied Power Electronics Conference and Exposition (APEC), 2014 Twenty-Ninth Annual IEEE*, March 2014, pp. 812–817.

- [18] V. S. S. P. K. Hari and G. Narayanan, "Space-vector-based hybrid pwm technique to reduce peak-to-peak torque ripple in induction motor drives," *IEEE Transactions on Industry Applications*, vol. 52, no. 2, pp. 1489– 1499, March 2016.

- [19] S. Das and G. Narayanan, "Novel switching sequences for a space-vectormodulated three-level inverter," *Industrial Electronics, IEEE Transactions* on, vol. 59, no. 3, pp. 1477–1487, March 2012.

- [20] S. Das, G. Narayanan, and M. Pandey, "Space-vector-based hybrid pulsewidth modulation techniques for a three-level inverter," *Power Electronics, IEEE Transactions on*, vol. PP, no. 99, pp. 1–1, 2014.

- [21] D.-H. Lee and J.-W. Ahn, "A simple and direct dead-time effect compensation scheme in pwm-vsi," *Industry Applications, IEEE Transactions* on, vol. 50, no. 5, pp. 3017–3025, Sept 2014.

- [22] J. Rodriguez, M. Kazmierkowski, J. Espinoza, P. Zanchetta, H. Abu-Rub, H. Young, and C. Rojas, "State of the art of finite control set model predictive control in power electronics," *Industrial Informatics, IEEE Transactions on*, vol. 9, no. 2, pp. 1003–1016, May 2013.

- [23] G. Grandi and J. Loncarski, "Evaluation of current ripple amplitude in three-phase pwm voltage source inverters," in *Compatibility and Power Electronics (CPE), 2013 8th International Conference on*, June 2013, pp. 156–161.

- [24] G. Grandi, J. Loncarski, and O. Dordevic, "Analysis and comparison of peak-to-peak current ripple in two-level and multilevel pwm inverters," *Industrial Electronics, IEEE Transactions on*, vol. 62, no. 5, pp. 2721– 2730, May 2015.

- [25] S. Das, G. Narayanan, and A. Tiwari, "Variation of igbt switching energy loss with device current: An experimental investigation," in *Power Electronics (IICPE), 2014 IEEE 6th India International Conference on*, Dec 2014, pp. 1–5.

- [26] A. Bazzi, P. Krein, J. Kimball, and K. Kepley, "Igbt and diode loss estimation under hysteresis switching," *Power Electronics, IEEE Transactions* on, vol. 27, no. 3, pp. 1044–1048, March 2012.