# Deterministic Concurrency: A Clock-Synchronised Shared Memory Approach

Joaquín Aguado, Michael Mendler, Marc Pouzet, Partha Roop, Reinhard von

Hanxleden

# ▶ To cite this version:

Joaquín Aguado, Michael Mendler, Marc Pouzet, Partha Roop, Reinhard von Hanxleden. Deterministic Concurrency: A Clock-Synchronised Shared Memory Approach. ESOP 2018 - European Symposium on Programming, Apr 2018, Thessaloniki, Greece. hal-01960404

# HAL Id: hal-01960404 https://hal.science/hal-01960404

Submitted on 19 Dec 2018

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Deterministic Concurrency: A Clock-Synchronised Shared Memory Approach

Joaquín Aguado<sup>1</sup>, Michael Mendler<sup>1</sup>, Marc Pouzet<sup>2</sup>, Partha Roop<sup>3</sup>, and Reinhard von Hanxleden<sup>4</sup>

Otto-Friedrich-Universität Bamberg, Germany

<sup>2</sup> École Normale Supérieure Paris, France

<sup>3</sup> University of Auckland, New Zealand

<sup>4</sup> Christian-Albrechts-Universität zu Kiel, Germany

**Abstract.** Synchronous Programming (SP) is a universal computational principle that provides deterministic concurrency. The same input sequence with the same timing always results in the same externally observable output sequence, even if the internal behaviour generates uncertainty in the scheduling of concurrent memory accesses. Consequently, SP languages have always been strongly founded on mathematical semantics that support formal program analysis. So far, however, communication has been constrained to a set of primitive clock-synchronised shared memory (CSM) data types, such as data-flow registers, streams and signals with restricted read and write accesses that limit modularity and behavioural abstractions.

This paper proposes an extension to the SP theory which retains the advantages of deterministic concurrency, but allows communication to occur at higher levels of abstraction than currently supported by SP data types. Our approach is as follows. To avoid data races, each CSM type publishes a *policy interface* for specifying the admissibility and precedence of its access methods. Each instance of the CSM type has to be policy-coherent, meaning it must behave deterministically under its own policy—a natural requirement if the goal is to build deterministic systems that use these types. In a policy-constructive system, all access methods can be scheduled in a policy-conformant way for all the types without deadlocking. In this paper, we show that a policy-constructive program exhibits deterministic concurrency in the sense that all policyconformant interleavings produce the same input-output behaviour. Policies are conservative and support the CSM types existing in current SP languages. Technically, we introduce a kernel SP language that uses arbitrary policy-driven CSM types. A big-step fixed-point semantics for this language is developed for which we prove determinism and termination of constructive programs.

**Keywords:** synchronous programming, data abstraction, clock-synchronised shared memory, determinacy, concurrency, constructive semantics.

# 1 Introduction

Concurrent programming is challenging. Arbitrary interleavings of concurrent threads lead to non-determinism with data races imposing significant integrity and consistency issues [1]. Moreover, in many application domains such as safety-critical systems, *determinism* is indeed a matter of life and death. In a medical-device software, for instance, the same input sequence from the sensors (with the same timing) must always result in the same output sequence for the actuators, even if the run-time software architecture regime is unpredictable.

Synchronous programming (SP) delivers deterministic concurrency out of the box<sup>1</sup> which explains its success in the design, implementation and validation of embedded, reactive and safety-critical systems for avionics, automotive, energy and nuclear industries. Right now SP-generated code is flying on the Airbus 380 in systems like flight control, cockpit display, flight warning, and anti-icing just to mention a few. The SP mathematical theory has been fundamental for implementing correct-by-construction program-derivation algorithms and establishing formal analysis, verification and testing techniques [2]. For SCADE<sup>2</sup>, the SP industrial modelling language and software development toolkit, the formal SP background has been a key aspect for its certification at the highest level A of the aerospace standard DO-178B/C. This SP rigour has also been important for obtaining certifications in railway and transportation (EN 50128), industry and energy (IEC 61508), automotive (TÜV and ISO 26262) as well as for ensuring full compliance with the safety standards of nuclear instrumentation and control (IEC 60880) and medical systems (IEC 62304) [3].

Synchronous Programming in a Nutshell. At the top level, we can imagine an SP system as a black-box with inputs and outputs for interacting with its environment. There is a special input, called the *clock*, that determines when the communication between system and environment can occur. The clock gets an input stimulus from the environment at discrete times. At those moments we say that the clock *ticks*. When there is no tick, there is no possible communication, as if system and environment were disconnected. At every tick, the system *reacts* by reading the current inputs and executing a *step function* that delivers outputs and changes the internal memory. For its part, the environment must synchronise with this reaction and do not go ahead with more ticks. Thus, in SP, we assume (*Synchrony Hypothesis*) that the time interval of a system reaction, also called *macro-step* or (*synchronous*) *instant*, appears instantaneous (has zero-delay) to the environment. Since each system reaction takes exactly one clock tick, we describe the evolution of the system-environment interaction as a synchronous (lock-step) sequence of macro-steps. The SP theory guarantees

<sup>&</sup>lt;sup>1</sup> Milner's distinction between *determinacy* and *determinism* is that a computation is *determinate* if the same input sequence produces the same output sequence, as opposed to *deterministic* computations which in addition have identical internal behaviour/scheduling. In this paper we use both terms synonymously to mean determinacy in Milner's sense, i. e., observable determinism.

<sup>&</sup>lt;sup>2</sup> SCADE is a product of ANSYS Inc. (http://www.esterel-technologies.com/)

that all externally observable interaction sequences derived from the macro-step reactions define a functional input-output relation.

The fact that the sequences of macro-steps take place in time and space (memory) has motivated two orthogonal developments of SP. The *data-flow* view regards input-output sequences as synchronous streams of data changing over time and studies the functional relationships between streams. Dually, the *control-flow* approach projects the information of the input-output sequences at each point in time and studies the changes of this global state as time progresses, i.e., from one tick to the next. The SP paradigm includes languages such as Esterel [4], Quartz [5] and SC [6] in the imperative control-flow style and languages like Signal [7], Lustre [8] and Lucid Synchrone [9] that support the declarative data-flow view. There are even mixed control-data flow language such as Esterel V7 [10] or SCADE [3]. Independently of the execution model, the common strength to all of these SP languages is a precise formal semantics—an indispensable feature when dealing with the complexities of concurrency.

At a more concrete level, we can visualise an SP system as a white-box where inside we find (graphical or textual) code. In the SP domain, the program must be divided into fragments corresponding to the macro-step reactions that will be executed instantaneously at each tick. Declarative languages usually organise these macro-steps by means of (internally generated) activation clocks that prescribe the blocks (nodes) that are performed at each tick. Instead, imperative textual languages provide a **pause** statement for explicitly delimiting code execution within a synchronous instant. In either case, the Synchrony Hypothesis conveniently abstracts away all the, typically concurrent, low-level *micro-steps* needed to produce a system reaction. The SP theory explains how the micro-step accesses to shared memory must be controlled so as to ensure that all internal (white-box) behaviour eventually stabilises, completing a deterministic macrostep (black-box) response. For more details on SP, the reader is referred to [2].

State of the Art. Traditional imperative SP languages provide constructs to model control-dominated systems. Typically, these include a concurrent composition of threads (sequential processes) that guarantees determinism and offers signals as the main means for data communication between threads. Signals behave like shared variables for which the concurrent accesses occurring within a macro-step are scheduled according to the following principles: A pure signal has a status that can be present (1) or absent (0). At the beginning of each macrostep, pure signals have status 0 by default. In any instant, a signal  $\mathbf{s}$  can be explicitly *emitted* with the statement **s**.**emit**() which atomically sets its status to 1. We can read the status of **s** with the statement **s**.**pres**(), so the control-flow can branch depending on run-time signal statuses. Specifically, inside programs, if-then-else constructions await for the appropriate combination of present and absent signal statuses to emit (or not) more signals. The main issue is to avoid inconsistencies due to circular causality resulting from decisions based on absent statuses. Thus, the order in which the access methods emit, pres are scheduled matters for the final result. The usual SP rule for ensuring determinism is that the **pres** test must wait until the final signal status is decided. If all signal accesses can be scheduled in this *decide-then-read* way then the program is *constructive*. All schedules that keep the decide-then-read order will produce the same input-output result. This is how SP reconciles concurrency and observable determinism and generates much of its algebraic appeal. Constructiveness of programs is what static techniques like the *must-can* analysis [4,11,12,13] verify although in a more abstract manner. Pure signals are a simple form of *clock-synchronised shared memory* (CSM) data types with access methods (operations) specific to this CSM type. Existing SP control-flow languages also support other restricted CSM types such valued signals and arrays [10] or sequentially constructive variables [6].

Contribution. This paper proposes an extension to the SP model which retains the advantages of deterministic concurrency while widening the notion of constructiveness to cover more general CSM types. This allows shared-memory communication to occur at higher levels of abstraction than currently supported. In particular, our approach subsumes both the notions of *Berry-constructiveness* [4] for Esterel and *sequential constructiveness* for SCL [14]. This is the first time that these SP communication principles are combined side-by-side in a single language. Moreover, our theory permits other predefined communication structures to coexist safely under the same uniform framework, such as data-flow variables [8], registers [15], Kahn channels [16], priority queues, arrays as well as other CSM types currently unsupported in SP.

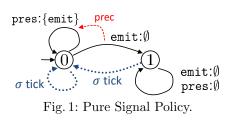

Synopsis and Overview. The core of our approach is presented in Sec. 2 where policies are introduced as a (constructive) synchronisation mechanism for arbitrary abstract data types (ADT). For instance, the policy of a pure signal is depicted in Fig. 1. It has two control states 0 and 1 corresponding to the two possible signal statuses. Transitions are decorated with method names **pres**, **emit** or with  $\sigma$  to indicate a clock tick.

The policy tells us whether a given method or tick is *admissible*, i. e., if it can be scheduled from a particular state<sup>3</sup>. In addition, transitions include a *blocking* set of method names as part of their *action* labels. This set determines

a precedence between methods from a given state. A label m : L specifies that all methods in L take precedence over m. An empty blocking set  $\emptyset$  indicates no precedences. To improve visualisation, we highlight precedences by dotted (red) arrows tagged prec<sup>4</sup>. The policy interface in Fig. 1 specifies the decide-thenread protocol of pure signals as follows. At any instant, if the signal status is 0

<sup>&</sup>lt;sup>3</sup> The signal policy in Fig. 1 does not impose any admissibility restriction since methods **pres** and **emit** can be scheduled from every policy state.

<sup>&</sup>lt;sup>4</sup> We tacitly assume that the tick transitions  $\sigma$  have the lowest *priority* since only when the reaction is over, the clock may tick. We could be more explicit and write  $\sigma$ : {pres.emit} as action labels for these transitions.

then the **pres** test can only be scheduled if there are no more potential **emit** statements that can still update the status to 1. This explains the precedence of the **emit** transition over the self loop with action label **pres** : {**emit**} from state 0. Conversely, transitions **pres** and **emit** from state 1 have no precedences, meaning that the **pres** and **emit** methods are *confluent* so they can be freely scheduled (interleaved). The reason is that a signal status 1 is already decided and can no longer be changed by either method in the same instant. In general, any two admissible methods that do not block each other must be confluent in the sense that the same policy state is reached independently of their order of execution. Note that all the  $\sigma$  transition go to the *initial* state 0 since at each tick the SP system enters a new macro-step where all pure signals get initialised to the 0 status.

Sec. 2 describes in detail the idea of a scheduling policy on general CSM types. This leads to a type-level *coherence* property, which is a local form of determinism. Specifically, a CSM type is *policy-coherent* if it satisfies the (policy) specification of admissibility and precedence of its access methods. The point is that a policy-coherent CSM type per se behaves deterministically under its own policy—a very natural requirement if the goal is to build deterministic systems that use this type. For instance, the fact that Esterel signals are deterministic (policy-coherent) in the first place permits techniques such as the must-can analysis to get constructive information about deterministic programs. We show how policy-coherence implies a global determinacy property called *commutation*. Now, in a *policy-constructive* program all access methods can be scheduled in a *policy-conforming* way for all the CSM types without deadlocking. We also show that, for policy-coherent types, a policy-constructive program exhibits deterministic concurrency in the sense that all policy-conforming interleavings produce the same input-output behaviour.

To implement a constructive scheduling mechanism parameterised in arbitrary CSM type policies, we present the synchronous kernel language, called *Deterministic Concurrent Language* (DCoL), in Sec. 2.1. DCoL is both a minimal language to study the new mathematical concepts but can also act as an intermediate language for compiling existing SP Sec. 3 presents its policy-driven operational semantics for which determinacy and termination is proven. Sec. 3 also explains how this model generalises existing notions of constructiveness. We discuss related work in Sec. 4 and present our conclusions in Sec. 5.

A companion of this paper is the research report [17] which contains detailed proofs and additional examples of CSM types.

# 2 Synchronous Policies

This section introduces a kernel synchronous *Deterministic Concurrent Lan*guage (DCoL) for policy-conformant constructive scheduling which integrates policy-controlled CSM types within a simple syntax. DCoL is used to discuss the behavioural (clock) abstraction limitations of current SP. Then policies are introduced as a mechanism for specifying the scheduling discipline for CSM types which, in this form, can encapsulate arbitrary ADTs.

### 2.1 Syntax

The syntax of DCoL is given by the following operators:

| P ::= skip                | instantaneous termination                   |

|---------------------------|---------------------------------------------|

| pause                     | wait for next instant (clock tick)          |

| $  P \parallel P$         | parallel composition                        |

| P;P                       | sequential composition                      |

| let $x = c.m(e)$ in $P$   | access method call, $x$ value variable      |

| if $e$ then $P$ else $P$  | conditional branching, $e$ value expression |

| $\operatorname{rec} p. P$ | recursive closure                           |

| p                         | process variable                            |

The first two statements correspond to the two forms of immediate *comple*tion: skip terminates instantaneously and pause waits for the logical clock to terminate. The operators  $P \parallel Q$  and P; Q are parallel interleaving and imperative sequential composition of threads with the standard operational interpretation. Reading and destructive updating is performed through the execution of method calls c.m(e) on a CSM variable  $c \in O$  with a method  $m \in M_c$ . The sets O and  $M_c$  define the granularity of the available memory accesses. The construct let x = c.m(e) in P calls m on c with an input parameter determined by value expression e. It binds the return value to variable x and then executes program P, which may depend on x, sequentially afterwards. The execution of c.m(e) in general has the side-effect of changing the internal memory of c. In contrast, the evaluation of expression e is side-effect free. For convenience we write x = c.m(e); P for let x = c.m(e) in P. When P does not depend on x then we write c.m(e); P and c.m(e); for c.m(e); skip. The exact syntax of value expressions e is irrelevant for this work and left open. It could be as simple as permitting only constant value literals or a full-fledged functional language. The conditional if e then P else P has the usual interpretation. For simplicity, we may write if c.m(e) then P else Q to mean x = c.m(e); if x then P else Q. The recursive closure  $\operatorname{rec} p. P$  binds the behaviour P to the program label p so it can be called from within P. Using this construct we can build iterative behaviours. For instance,  $loop P end =_{df} rec p. P$ ; pause ; p indefinitely repeats P in each tick. We assume that in a closure rec p. P the label p is (i) clock quarded, i.e., it occurs in the scope of at least one **pause** (meaning no instantaneous loops) and (ii) all occurrences of p are in the same thread. Thus, rec p. p is illegal because of (i) and rec p. (pause; p || pause; p) is not permitted because of (ii).

This syntax seems minimalistic compared to existing SP languages. For instance, it does not provide primitives for pre-emption, suspension or traps as in Quartz or Esterel. Recent work [18] has shown how these control primitives can be translated into the constructs of the SCL language, exploiting destructive update of sequentially constructive (SC) variables. Since SC variables are a special case of policy-controlled CSM variables, DCoL is at least as expressive as SCL.

## 2.2 Limited Abstraction in SP

The pertinent feature of standard SP languages is that they do not permit the programmer to express sequential execution order inside a tick, for destructive updates of signals. All such updates are considered concurrent and thus must either be combined or concern distinct signals. For instance, in languages such as Esterel V7 or Quartz, a parallel composition

$$(v = xs.read(); ys.emit(v+1)) \parallel (xs.emit(1); xs.emit(5))$$

(1)

of signal emissions is only constructive if a commutative and associative function is defined on the shared signal xs to combine the values assigned to it. But then, by the properties of this *combination function*, we get the same behaviour if we swap the assignments of values 1 and 5, or execute all in parallel as in

```

v = xs.read() \parallel ys.emit(v+1) \parallel xs.emit(1) \parallel xs.emit(5).

```

If what we intended with the second emission xs.emit(5) in (1) was to override the first xs.emit(1) like in normal imperative programming so that the concurrent thread v = xs.read(); ys.emit(v + 1) will read the updated value as v = 5? Then we need to introduce a **pause** statement to separate the emissions by a clock tick and delay the assignment to ys as in

$(pause; v = xs.read(); ys.emit(v+1)) \parallel (xs.emit(1); pause; xs.emit(5)).$

This makes behavioural abstraction difficult. For instance, suppose **nats** is a synchronous reaction module, possibly composite and with its own internal clocking, which returns the stream of natural numbers. Every time its step function **nats.step**() is called it returns the next number and increments its internal state. If we want to pair up two successive numbers within one tick of an outer clock and emit them in a single signal ys we would write something like  $x_1 = \texttt{nats.step}()$ ;  $x_2 = \texttt{nats.step}()$ ;  $y.\texttt{emit}(x_1, x_2)$  where  $x_1, x_2$  are thread-local value variables. This over-clocking is impossible in traditional SP because there is no imperative sequential composition by virtue of which we can call the step function of the same module instance twice within a tick. Instead, the two calls nats.step() are considered concurrent and thus create non-determinacy in the value of y.<sup>5</sup> To avoid a compiler error we must separate the calls by a clock as in  $x_1 = \texttt{nats.step}()$ ; pause;  $x_2 = \texttt{nats.step}()$ ;  $y.\texttt{emit}(x_1, x_2)$  which breaks the intended clock abstraction.

The data abstraction limitation of traditional SP is that it is not directly possible to encapsulate a composite behaviour on synchronised signals as a shared synchronised object. For this, the simple decide-then-read signal protocol must be generalised, in particular, to distinguish between concurrent and sequential accesses to the shared data structure. A concurrent access  $x_1 = nats.step() \parallel$

<sup>&</sup>lt;sup>5</sup> In Esterel V7 it is possible to use a module twice in a "sequential" composition  $x_1 =$ **nats.step**();  $x_2 =$ **nats.step**(). However, the two occurrences of **nats** are distinct instances with their own internal state. Both calls will thus return the same value.

$x_2 = \texttt{nats.step}()$  must give the same value for  $x_1$  and  $x_2$ , while a sequential access  $x_1 = \texttt{nats.step}()$ ;  $x_2 = \texttt{nats.step}()$  must yield successive values of the stream. In a sequence x = xs.read(); xs.emit(v) the x does not see the value v but in a parallel  $x = \texttt{xs.read}() \parallel \texttt{xs.emit}(v)$  we may want the read to wait for the emission. The rest of this section covers our theory on policies in which this is possible. The modularity issue is reconsidered in Sec. 2.6.

#### 2.3 Concurrent Access Policies

In the white-box view of SP, an imperative program consists of a set of threads (sequential processes) and some CSM variables for communication. Due to concurrency, a given thread under control (TUC) has the chance to access the shared variables only from time to time. For a given CSM variable, a concurrent access policy (CAP) is the locking mechanism used to control the accesses of the current TUC and its environment. The locking is to ensure that determinacy of the CSM type is not broken by the concurrent accesses. A CAP is like a policy which has extra transitions to model potential environment accesses outside the TUC. Concretely, a CAP is given by a state machine where each transition label a: L codifies an *action* a taking place on the shared variable with *blocking set* L, where L is a set of methods that take precedence over a. The action is either a method m: L, a silent action  $\tau: L$  or a clock tick  $\sigma: L$ . A transition m: Lexpresses that in the current CAP control state, the method m can be called by the TUC, provided that no method in L is called concurrently. There is a *Deter*minacy Requirement that guarantees that each method call by the TUC has a blocking set and successor state. Additionally, the execution of methods by the CAP must be *confluent* in the sense that if two methods are admissible and do not block each other, then the CAP reaches the same policy state no matter the order in which they are executed. This is to preserve determinism for concurrent variable accesses. A transition  $\tau : L$  internalises method calls by the TUC's concurrent environment which are uncontrollable for the TUC. In the sequel, the actions in  $M_{c} \cup \{\sigma\}$  will be called *observable*. A transition  $\sigma : L$  models a clock synchronisation step of the TUC. Like method calls, such clock ticks must be determinate as stated by the Determinacy Requirement. Additionally, the clock must always wait for any predicted concurrent  $\tau$ -activity to complete. This is the Maximal Progress Requirement. Note that we do not need confluence for clock transitions since they are not concurrent.

**Definition 1.** A concurrent access policy  $(CAP) \Vdash_c of a CSM$  variable c with (access) methods  $M_c$  is a state machine consisting of a set of control states  $\mathbb{P}_c$ , an initial state  $\varepsilon \in \mathbb{P}_c$  and a labelled transition relation  $\to \subseteq \mathbb{P}_c \times A_c \times \mathbb{P}_c$  with action labels  $A_c = (M_c \cup \{\tau, \sigma\}) \times 2^{M_c}$ . Instead of  $(\mu_1, (a, L), \mu_2) \in \to$  we write  $\mu_1 - a: L \to \mu_2$ . We then say action a is admissible in state  $\mu_1$  and blocked by all methods  $m \in L \subseteq M_c$ . When the blocking set L is irrelevant we drop it and write  $\mu_1 - a \to \mu_2$ . A CAP must satisfy the following conditions:

- Determinacy. If  $\mu - a: L_1 \rightarrow \mu_1$  and  $\mu - a: L_2 \rightarrow \mu_2$  then  $L_1 = L_2$  and  $\mu_1 = \mu_2$ provided a is observable, i. e.,  $a \neq \tau$ .

- Confluence. If  $\mu m_1: L_1 \to \mu_1$  and  $\mu m_2: L_2 \to \mu_2$  do not block each other, i. e.,  $m_1 \in M_c \setminus L_2$  and  $m_2 \in M_c \setminus L_1$ , then for some  $\mu'$  both  $\mu_1 - m_2 \to \mu'$ and  $\mu_2 - m_1 \to \mu'$ .

- Maximal Progress.  $\mu a: L_1 \to \mu_1$  and  $\mu \sigma: L_2 \to \mu_2$  imply a is observable and  $a \in L_2 \cup \{\sigma\}$ .

A policy is a CAP without any (concurrent)  $\tau$  activity, i. e., every  $\mu - a \rightarrow \mu'$  implies that a is observable.

The use of a CAP as a concurrent policy arises from the notion of enabling. Informally, an observable action  $a \in M_c \cup \{\sigma\}$  is enabled in a state  $\mu$  of a CAP if it is admissible in  $\mu$  and in all subsequent states reachable under arbitrary silent steps not blocked by a. To formalise this we define weak transitions  $\mu_1 = L \Rightarrow \mu_2$ inductively to express that either  $\mu_1 = \mu_2$  and  $L = \emptyset$  or  $\mu_1 = L_1 \Rightarrow \mu'$  and  $\mu' - \tau: L_2 \rightarrow \mu_2$  and  $L = L_1 \cup L_2$ . We exploit the determinacy for observable actions  $a \in M_c \cup \{\sigma\}$  and write  $\mu \odot a$  for the unique  $\mu'$  such that  $\mu - a \rightarrow \mu'$ , if it exists.

**Definition 2.** Given a CAP  $\Vdash_c = (\mathbb{P}_c, \varepsilon, \longrightarrow)$ , an observable action  $a \in M_c \cup \{\sigma\}$ is enabled in state  $\mu \in \mathbb{P}_c$ , written  $\mu \Vdash_c \downarrow a$ , if  $\mu' \odot a$  exists for all  $\mu'$  such that  $\mu = L \Rightarrow \mu'$  and  $a \notin L$ . A sequence  $\mathbf{a} \in (M_c \cup \{\sigma\})^*$  of observable actions is enabled in  $\mu \in \mathbb{P}_c$ , written  $\mu \Vdash_c \downarrow \mathbf{a}$ , if (i)  $\mathbf{a} = \varepsilon$  or (ii)  $\mathbf{a} = a\mathbf{b}$ ,  $\mu \Vdash_c \downarrow a$  and  $\mu \odot a \Vdash_c \downarrow \mathbf{b}$ .

Example 1. Consider the policy  $\Vdash_{\mathbf{s}}$  in Fig. 1 of an Esterel pure signal  $\mathbf{s}$ . An edge labelled a:L from state  $\mu_1$  to  $\mu_2$  corresponds to a transition  $\mu_1 - a:L \rightarrow \mu_2$  in  $\Vdash_{\mathbf{s}}$ . The start state is  $\varepsilon = 0$  and the methods  $\mathsf{M}_{\mathbf{s}} = \{\mathsf{pres}, \mathsf{emit}\}$  are always admissible, i.e.,  $\mu \odot m$  is de-

Fig. 2: Synchronous IVar.

fined in each state  $\mu$  for all methods m. The presence test does not change the state and any emission sets it to 1, i.e.,  $\mu \odot \operatorname{pres} = \mu$  and  $\mu \odot \operatorname{emit} = 1$  for all  $\mu \in \mathbb{P}_s$ . Each signal status is reset to 0 with the clock tick, i.e.,  $\mu \odot \sigma = 0$ . Clearly,  $\Vdash_s$  satisfies Determinacy. A presence test on a signal that is not emitted yet has to wait for all pending concurrent emissions, that is emit blocks pres in state 0, i.e.,  $0 - \operatorname{pres} : \{\operatorname{emit}\} \to 0$ . Otherwise, no transition is blocked. Also, all competing transitions  $\mu - m_1: L_1 \to \mu_1$  and  $\mu - m_2: L_2 \to \mu_2$  that do not block each other, are of the form  $\mu_1 = \mu_2$ , from which Confluence follows. As the clock transitions  $\sigma$  are implicitly blocked by all methods and since there are no silent transitions, Maximal Progress is always fulfilled too. Moreover, an action sequence is enabled in a state  $\mu$  (Def. 2) iff it corresponds to a path in the automaton starting from  $\mu$ . Hence, for  $m \in M_s^*$  we have  $0 \Vdash_s \downarrow m$  iff m is in the regular language<sup>6</sup> pres<sup>\*</sup> + pres<sup>\*</sup> emit(pres + emit)<sup>\*</sup> and  $1 \Vdash_s \downarrow m$  for all  $m \in M_s^*$ .

$<sup>^{6}</sup>$  We are more liberal than Esterel where emit cannot be called sequentially after pres.

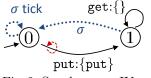

Contrast  $\Vdash_s$  with the policy  $\Vdash_c$  of a synchronous *immutable variable* (IVar) c shown in Fig. 2 with methods  $M_c = \{get, put\}$ . During each instant an IVar can be written (put) at most once and cannot be read (get) until it has been written. No value is stored between ticks, which means the memory is only temporary and can be reused, e.g., IVars can be implemented by wires. Formally,  $\mu \Vdash_c \downarrow put$  iff  $\mu = 0$ , where 0 is the initial empty state and  $\mu \Vdash_c \downarrow get$  iff  $\mu = 1$ , where 1 is the filled state. The transition  $0 - put: \{put\} \rightarrow 1$  switches to filled state where get is admissible but put is not, anymore. The blocking  $\{put\}$  means there cannot be other concurrent threads writing c at the same time.

#### 2.4 Enabling and Policy Conformance

A policy describes what a single thread can do to a CSM variable c when it operates alone. In a CAP all potential activities of the environment are added as  $\tau$ -transitions to block the TUC's accesses. To implement this  $\tau$ -locking we define an operation that generates a CAP  $[\mu, \gamma]$  out of a policy. In this construction,  $\mu \in \mathbb{P}_{c}$  is a policy state recording the history of methods that have been performed on c so far (*must* information). The second component  $\gamma \subseteq M_{c}^{*}$  is a prediction for the sequences of methods that can still potentially be executed by the concurrent environment (*can* information).

**Definition 3.** Let  $(\mathbb{P}_c, \varepsilon, \rightarrow)$  be a policy. We define a CAP  $\Vdash_c$  where states are pairs  $[\mu, \gamma]$  such that  $\mu \in \mathbb{P}_c$  is a policy state and  $\gamma \subseteq M_c^*$  is a prediction. The initial state is  $[\varepsilon, M_c^*]$  and the transitions are as follows:

- 1. The observable transitions  $[\mu_1, \gamma_1] m: L \rightarrow [\mu_2, \gamma_2]$  are such that  $\gamma_1 = \gamma_2$ and  $\mu_1 - m: L \rightarrow \mu_2$  provided that for all sequences  $n \mathbf{n} \in \gamma_1$  with  $\mu_1 - n \rightarrow \mu'$ we have  $n \notin L$ .

- 2. The silent transitions are  $[\mu_1, \gamma_1] \tau: L \rightarrow [\mu_2, \gamma_2]$  such that  $\emptyset \neq m \gamma_2 \subseteq \gamma_1$ and  $\mu_1 - m: L \rightarrow \mu_2$ .

- 3. The clock transitions are  $[\mu_1, \gamma_1] \sigma: L \rightarrow [\mu_2, \gamma_2]$  such that  $\gamma_1 = \emptyset$  and  $\mu_1 \sigma: L \rightarrow \mu_2$ .

Silent steps arise from the concurrent environment: A step  $[\mu_1, \gamma_1] - \tau: L \rightarrow [\mu_2, \gamma_2]$  removes some prefix method m from the environment prediction  $\gamma_1$ , which contracts to an updated suffix prediction  $\gamma_2$  with  $m \gamma_2 \subseteq \gamma_1$ . This method m is executed on the CSM variable, changing the policy state to  $\mu_2 = \mu_1 \odot m$ . A method m is enabled,  $[\mu, \gamma] \Vdash_{\mathsf{c}} \downarrow m$ , if for all  $[\mu_1, \gamma_1]$  which are  $\tau$ -reachable from  $[\mu, \gamma]$  and not blocked by a, method m is admissible, i. e.,  $[\mu_1, \gamma_1] - m \rightarrow [\mu_2, \gamma_1]$  for some  $\mu_2$ .

Example 2. Consider concurrent threads  $P_1 \parallel P_2$ , where  $P_2 = \texttt{zs.put}(5)$ ; u = ys.get() and  $P_1 = v = \texttt{zs.get}()$ ; ys.put(v+1) with IVars zs, ys according to Ex. 1. Under the IVar policy the execution is deterministic, so that first  $P_2$  writes on zs, then  $P_1$  reads from zs and writes to ys, whereupon finally  $P_1$  reads ys. Suppose the variables have reached policy states  $\mu_{\texttt{zs}}$  and  $\mu_{\texttt{ys}}$  and the

threads are ready to execute the residual programs  $P'_i$  waiting at some method call  $c_i.m_i(v_i)$ , respectively. Since thread  $P'_i$  is concurrent with the other  $P'_{3-i}$ , it can only proceed if  $m_i$  is not blocked by  $P'_{3-i}$ , i.e., if  $[\mu_{c_i}, can_{c_i}(P'_{3-i})] \Vdash_{c_i} \downarrow m_i$ , where  $can_c(P) \subseteq \mathsf{M}^*_{\mathsf{c}}$  is the set of method sequences predicted for P on  $\mathsf{c}$ .

Initially we have  $\mu_{zs} = 0 = \mu_{ys}$ . Since method get is not admissible in state 0, we get  $[0, can_{zs}(P_2)] \nvDash_{zs} \downarrow$  get by Def. 3 and Def. 2. So,  $P_1$  is blocked. The zs.put of  $P_2$ , however, can proceed. First, since no predicted method sequence  $can_{zs}(P_1) = \{\text{get}\}$  of  $P_1$  starts with put, the transition  $0 -\text{put:}\{\text{put}\} \rightarrow 1$  implies that  $[0, can_{zs}(P_1)] -\text{put:}\{\text{put}\} \rightarrow [1, can_{zs}(P_1)]$  by Def. 3(1). Moreover, since get of  $P_1$  is not admissible in 0, there are no silent transitions out of  $[0, can_{zs}(P_1)]$  according to Def. 3(2). Thus,  $[0, can_{zs}(P_1)] \Vdash_{zs} \downarrow$  put, as claimed.

When the zs.put is executed by  $P_2$  it turns into  $P'_2 = u = ys.get()$  and the policy state for zs advances to  $\mu'_{zs} = 1$ , while ys is still at  $\mu_{ys} = 0$ . Now ys.get of  $P'_2$  blocks for the same reason as zs was blocked in  $P_1$  before. But since  $P_2$  has advanced, its prediction on zs reduces to  $can_{zs}(P'_2) = \emptyset$ . Therefore, the transition  $1 - get: \emptyset \to 1$  implies  $[1, can_{zs}(P'_2)] - get: \emptyset \to [1, can_{zs}(P'_2)]$  by Def. 3(1). Also, there are no silent transitions out of  $[1, can_{zs}(P'_2)]$  by Def. 3(2) and so  $[\mu'_{zs}, can_{zs}(P'_2)] \Vdash_{zs} \downarrow get$  by Def. 2. This permits  $P_1$  to execute zs.get() and proceed to  $P'_1 = ys.put(5+1)$ . The policy state of zs is not changed by this, neither is the state of ys, whence  $P'_2$  is still blocked. Yet, we have  $[\mu_{ys}, can_{zs}(P'_2)] \Vdash_{ys} \downarrow put$  which lets  $P'_1$  complete ys.put. It reaches  $P''_1$  with  $can_{ys}(P''_1) = \emptyset$  and changes the policy state of ys to  $\mu'_{ys} = 1$ . At this point,  $[\mu'_{ys}, can_{zs}(P''_1)] \Vdash_{ys} \downarrow get$  which means  $P'_2$  unblocks to execute ys.get.

**Definition 4.** Let  $\Vdash_c$  be a policy for c. A method sequence  $\mathbf{m}_1$  blocks another  $\mathbf{m}_2$  in state  $\mu$ , written  $\mu \Vdash_c \mathbf{m}_1 \to \mathbf{m}_2$ , if  $\mu \Vdash_c \downarrow \mathbf{m}_2$  but  $[\mu, \{\mathbf{m}_1\}] \nvDash_c \downarrow \mathbf{m}_2$ . Two method sequences  $\mathbf{m}_1$  and  $\mathbf{m}_2$  are concurrently enabled, denoted  $\mu \Vdash_c \mathbf{m}_1 \diamond \mathbf{m}_2$  if  $\mu \Vdash_c \downarrow \mathbf{m}_1$ ,  $\mu \Vdash_c \downarrow \mathbf{m}_2$  and both  $\mu \nvDash_c \mathbf{m}_1 \to \mathbf{m}_2$  and  $\mu \nvDash_c \mathbf{m}_2 \to \mathbf{m}_1$ .

Our operational semantics will only let a TUC execute a sequence  $\boldsymbol{m}$  provided  $[\mu, \gamma] \Vdash_{c} \downarrow \boldsymbol{m}$ , where  $\mu$  is the current policy state of c and  $\gamma$  the predicted activity in the TUC's concurrent environment. Symmetrically, the environment will execute any  $\boldsymbol{n} \in \gamma$  only if it is enabled with respect to  $\boldsymbol{m}$ , i. e., if  $[\mu, \{\boldsymbol{m}\}] \Vdash \downarrow \boldsymbol{n}$ . This means  $\mu \Vdash_{c} \boldsymbol{m} \diamond \boldsymbol{n}$ . Policy coherence (Def. 5 below) then implies that every interleaving of the sequences  $\boldsymbol{m}$  and any  $\boldsymbol{n} \in \gamma$  leads to the same return values and final variable state (Prop. 1).

#### 2.5 Coherence and Determinacy

A method call m(v) combines a method  $m \in M_c$  with a method parameter<sup>7</sup>  $v \in \mathbb{D}$ , where  $\mathbb{D}$  is a universal domain for method arguments and return values, including the special don't care value  $_{-} \in \mathbb{D}$ . We denote by  $A_c = \{m(v) \mid m \in M_c, v \in \mathbb{D}\}$  the set of all method calls on object **c**. Sequences of method calls  $\alpha \in A_c^*$  can be abstracted back into sequences of methods  $\alpha^{\#} \in M_c^*$  by dropping the method parameters:  $\varepsilon^{\#} = \varepsilon$  and  $(m(v) \alpha)^{\#} = m \alpha^{\#}$ .

$<sup>^7</sup>$  This is without loss of generality since  $\mathbb D$  may contain value tuples.

Coherence concerns the semantics of method calls as state transformations. Let  $\mathbb{S}_{c}$  be the domain of memory states of the object c with initial state  $init_{c} \in \mathbb{S}_{c}$ . Each method call  $m(v) \in \mathsf{A}_{c}$  corresponds to a semantical action  $[\![m(v)]\!]_{c} \in \mathbb{S}_{c} \to (\mathbb{D} \times \mathbb{S}_{c})$ . If  $s \in \mathbb{S}_{c}$  is the current state of the object then executing a call m(v) on c returns a pair  $(u, s') = [\![m(v)]\!]_{c}(s)$  where the first projection  $u \in \mathbb{D}$  is the return value from the call and the second projection  $s' \in \mathbb{S}_{c}$  is the new updated state of the variable. For convenience, we will denote  $u = \pi_{1}[\![m(v)]\!]_{c}(s)$  by u = s.m(v) and  $s' = \pi_{2}[\![m(v)]\!]_{c}(s)$  by  $s' = s \odot m(v)$ . The action notation is extended to sequences of calls  $\alpha \in \mathsf{A}^{*}_{c}$  in the natural way:  $s \odot \varepsilon = s$  and  $s \odot (m(v) \alpha) = (s \odot m(v)) \odot \alpha$ .

For policy-based scheduling we assume an abstraction function mapping a memory state  $s \in \mathbb{S}_{c}$  into a policy state  $s^{\#} \in \mathbb{P}_{c}$ . Specifically,  $init_{c}^{\#} = \varepsilon$ . Further, we assume the abstraction commutes with method execution in the sense that if we execute a sequence of calls and then abstract the final state, we get the same as if we executed the policy automaton on the abstracted state in the first place. Formally,  $(s \odot \alpha)^{\#} = s^{\#} \odot \alpha^{\#}$  for all  $s \in \mathbb{S}_{c}$  and  $\alpha \in A_{c}^{*}$ .

**Definition 5 (Coherence).** A CSM variable *c* is policy-coherent if for all method calls  $a, b \in A_c$  whenever  $s^{\#} \Vdash_c a^{\#} \diamond b^{\#}$  for a state  $s \in S_c$ , then *a* and *b* are confluent in the sense that  $s.a = (s \odot b).a$ ,  $s.b = (s \odot a).b$  and  $s \odot a \odot b = s \odot b \odot a$ .

*Example 3.* Esterel pure signals do not carry any data value, so their memory state coincides with the policy state,  $\mathbb{S}_s = \mathbb{P}_s = \{0, 1\}$  and  $s^{\#} = s$ . An emission emit does not return any value but sets the state of s to 1, i. e., s. emit(\_) = \_\_  $\in \mathbb{D}$  and  $s \odot \text{emit}(\_) = 1 \in \mathbb{S}_s$ . A present test returns the state, s. pres(\_) = s, but does not modify it,  $s \odot \text{pres}(\_) = s$ . From the policy Fig. 1 we find that the concurrent enablings  $s^{\#} \Vdash_s a^{\#} \diamond b^{\#}$  according to Def. 4 are (i)  $a = b \in \{\text{pres}(\_), \text{emit}(\_)\}$  for arbitrary s, or (ii) s = 1,  $a = \text{emit}(\_)$  and  $s \odot a \odot b = s \odot b \odot a$  without difficulty. Note that  $1 \Vdash_s \text{emit} \diamond \text{pres}$  since the order of execution is irrelevant if s = 1. On the other hand,  $0 \nvDash_s \text{emit} \diamond \text{pres}$  because in state 0 both methods are not confluent. Specifically, 0. pres(\_) = 0 \neq 1 = (0 \odot \text{emit}(\\_)). pres(\_).

A special case are *linear precedence policies* where  $\mu \Vdash_{c} \downarrow m$  for all  $m \in M_{c}$ and  $\mu \Vdash_{c} m \to n$  is a linear ordering on  $M_{c}$ , for all policy states  $\mu$ . Then, for no state we have  $\mu \Vdash_{c} m_{1} \diamond m_{2}$ , so there is no concurrency and thus no confluence requirement to satisfy at all. Coherence of c is trivially satisfied whatever the semantics of method calls. For any two admissible methods one takes precedence over the other and thus the enabling relation becomes deterministic. There is however a risk of deadlock which can be excluded if we assume that threads always call methods in order of decreasing precedence.

The other extreme case is where the policy makes all methods concurrently enabled, i. e.,  $\mu \Vdash_{c} m_{1} \diamond m_{2}$  for all policy states  $\mu$  and methods  $m_{1}$ ,  $m_{2}$ . This avoids deadlock completely and gives maximal concurrency but imposes the strongest confluence condition, viz. independently of the scheduling order of any two methods, the resulting variable state must be the same. This requires complete isolation of the effects of any two methods. Such an extreme is used, e. g., in the CR library [19]. The typical CSM variable, however, will strike a tradeoff between these two extremes. It will impose a sensible set of precedences that are strong enough to ensure coherent implementations and thus determinacy for policy-conformant scheduling, while at the same time being sufficiently relaxed to permit concurrent implementations and avoiding unnecessary deadlocks risking that programs are rejected by the compiler as un-scheduleable.

Whatever the policies, if the variables are coherent, then all policy-conformant interleavings are indistinguishable for each CSM variable. To state schedule invariance in its general form we lift method actions and independence to multivariable sequences of methods calls  $A = \{c.m(v) \mid c \in O, m(v) \in A_c\}$ . For a given sequence  $\alpha \in A^*$  let  $\pi_c(\alpha) \in A_c^*$  be the projection of  $\alpha$  on c, formally  $\pi_c(\varepsilon) = \varepsilon$ ,  $\pi_c(c.m(v)\alpha) = m(v)\pi_c(\alpha)$  and  $\pi_c(c'.m(v)\alpha) = \pi_c(\alpha)$  for  $c' \neq c$ . A global memory  $\Sigma \in \mathbb{S} = \prod_{c \in O} \mathbb{S}_c$  assigns a local memory  $\Sigma.c \in \mathbb{S}_c$  to each variable c. We write *init* for the initial memory that has *init.c* = *init*<sub>c</sub> and  $(init.c)^{\#} = \varepsilon \in \mathbb{P}_c$ .

Given a global memory  $\Sigma \in \mathbb{S}$  and sequences  $\alpha, \beta \in \mathsf{A}^*$  of method calls, we extend the independence relation of Def. 4 variable-wise, defining  $\Sigma \Vdash \alpha \diamond \beta$  iff  $(\Sigma.\mathsf{c})^{\#} \Vdash_{\mathsf{c}} (\pi_{\mathsf{c}}(\alpha))^{\#} \diamond (\pi_{\mathsf{c}}(\beta))^{\#}$ . The application of a method call  $a \in \mathsf{A}$  to a memory  $\Sigma \in \mathbb{S}$  is written  $\Sigma.a \in \mathbb{S}$  and defined  $(\Sigma.(\mathsf{c}.m(v))).\mathsf{c} = (\Sigma.\mathsf{c}).m(v)$  and  $(\Sigma.(\mathsf{c}.m(v))).\mathsf{c}' = \Sigma.\mathsf{c}'$  for  $\mathsf{c}' \neq \mathsf{c}$ . Analogously, method actions are lifted to global memories, i. e.,  $(\Sigma \odot \mathsf{c}.m(v)).\mathsf{c}' = \Sigma.\mathsf{c}'$  if  $\mathsf{c}' \neq \mathsf{c}$  and  $(\Sigma \odot \mathsf{c}.m(v)).\mathsf{c} = \Sigma.\mathsf{c} \odot m(v)$ .

**Proposition 1 (Commutation).** Let all CSM variables be policy-coherent and  $\Sigma \Vdash a \diamond \alpha$  for a memory  $\Sigma \in \mathbb{S}$ , method call  $a \in V$  and sequences of method calls  $\alpha \in V^*$ . Then,  $\Sigma \odot a \odot \alpha = \Sigma \odot \alpha \odot a$  and  $\Sigma . a = (\Sigma \odot \alpha). a$ .

#### 2.6 Policies and Modularity

Consider the synchronous data-flow network cnt in Fig. 3b with three process nodes, a multiplexer mux, a register reg and an incrementor inc. Their DCoL code is given in Fig. 3a. The network implements a settable counter, which produces at its output ys a stream of consecutive integers, incremented with each clock tick. The wires ys, zs and ws are IVars (see Ex. 2) carrying a single integer value per tick. The input xs is a pure Esterel signal (see Ex. 1). The counter state is stored by reg in a local variable xv with read and write methods that can be called by a single thread only. The register is initialised to value 0 and in each subsequent tick the value at ys is stored. The inc takes the value at zs and increments it. When the signal xs is absent, mux passes the incremented value on ws to ys for the next tick. Otherwise, if xs is present then mux resets ys.

The evaluation order is implemented by the policies of the IVars ys, zs and ws. In each case the put method takes precedence over get which makes sure that the latter is blocked until the former has been executed. The causality cycle of the feedback loop is broken by the fact that the reg node first sends the current

```

cnt

module cnt

[ % mux node

inc

reg

WS

zs

loop

v = xs.pres();

(b) Block diagram of the feedback network.

if v then ys.put(0);

module cnt-cmp

else u = ws.get();

reg.init(0);

ys.put(u);

[ % mux-cmp node

end

loop

] []

v = xs.pres();

[ % reg node

if v then reg.set(0);

xv.write(0);

else u = ws.get();

loop

reg.set(u);

v = xv.read(); zs.send(v);

end

u = ys.get(); xv.write(u);

] ||

end

[ % inc-cmp node

] []

loop

[ % inc node

v = reg.get(); ws.put(v+1);

loop

end

v = zs.get(); ws.put(v+1);

]

end

]

```

XS

(a) Network with mux, reg, inc threads.

(c) Network with **reg** as a precompiled DCoL object.

ys

mux

Fig. 3: Synchronous data-flow network cnt built from control-flow processes.

counter value to **zs** before it waits for the new value at **ys**. The other nodes **mux** and **inc**, in contrast, first read their inputs and then send to their output.

Now suppose, for modularity, the **reg** node is pre-compiled into a synchronous IO automaton to be used by mux and inc as a black box component. Then, reg must be split into three modes [20] reg.init, reg.get and reg.set that can be called independently in each instant. The init mode initialises the register memory with 0. The get mode extracts the buffered value and set stores a new value into the register. Since there may be data races if get and set are called concurrently on reg, a policy must be imposed. In the scheduling of Fig. 3b, first reg.get is executed to place the output on zs. Then, reg waits for mux to produce the next value of ys from xs or ws. Finally, reg.set is executed to store the current value of ys for the next tick. Thus, the natural policy for the register is to require that in each tick set is called by at most one thread and if so no concurrent call to get by another thread happens afterwards. In addition, the policy requires init to take place at least once before any set or get. Hence, the policy has two states  $\mathbb{P}_{reg} = \{0, 1\}$  with initial  $\varepsilon = 0$  and admissibility such that  $0 \Vdash_{reg} \downarrow m$  iff m = init and  $1 \Vdash_{reg} \downarrow m$  for all m. The transitions are  $0 \odot \texttt{init} = 1$  and  $1 \odot m = 1$  for all  $m \in \mathsf{M}_{reg}$ . Further, for coherence, in state 1

no set may be concurrent and every get must take place before any concurrent set. This means, we have  $1 \Vdash_{reg} m \to set$  for all  $m \in \{get, set\}$ . Fig. 3c shows the partially compiled code in which reg is treated as a compiled object. The policy on reg makes sure the accesses by mux and inc are scheduled in the right way (see Ex. 4). Note that reg is not an IVar because it has memory.

The cnt example exhibits a general pattern found in the modular compilation of SP: Modules (here reg) may be exercised *several times* in a synchronous tick through *modes* which are executed in a specific *prescribed order*. Mode calls (here reg.set, reg.get) in the same module are coupled via common *shared memory* (here the local variable xs) while mode calls in distinct modules are isolated from each other [15,20].

### 3 Constructive Semantics of DCoL

To formalise our semantics it is technically expedient to keep track of the *completion status* of each active thread inside the program expression. This results in a syntax for *processes* distinguished from programs in that each parallel composition  $P_{1 \ k_1} \parallel_{k_2} P_2$  is labelled by *completion codes*  $k_i \in \{\perp, 0, 1\}$  which indicate whether each thread is *waiting*  $k_i = \perp$ , *terminated* 0 or *pausing*  $k_i = 1$ . Since we remove a process from the parallel as soon as it terminates then the code  $k_i = 0$  cannot occur. An expression  $P_1 \parallel P_2$  is considered a special case of a process with  $k_i = \perp$ . The formal semantics is given by a reduction relation on processes

$$\Sigma; \Pi \vdash P \stackrel{\mathbf{m}}{\Longrightarrow} \Sigma' \vdash_{k'} P' \tag{2}$$

specified by the inductive rules in Fig. 4 and Fig. 5. The relation (2) determines an instantaneous sequential reduction step of process P, called an sstep, that follows a sequence of enabled method calls  $m \in M^*$  in sequential program order in P. This does not include any context switches between concurrent threads inside P. For thread communication, several ssteps must be chained up, as described later. The sstep (2) results in an updated memory  $\Sigma'$  and residual process P'. The subscript k' is a completion code, described below. The reduction (2) is performed in a context consisting of a global memory  $\Sigma \in S$  (must context) containing the current state of all CSM variables and an environment prediction  $\Pi \subseteq M^*$  (can context). The prediction records all potentially outstanding methods sequences from threads running concurrently with P.

We write  $\pi_{c}(\boldsymbol{m}) \in \mathsf{M}^{*}_{c}$  for the projection of a method sequence  $\boldsymbol{m} \in \mathsf{M}^{*}$  to variable c and write  $\pi_{c}(\Pi)$  for its lifting to sets of sequences. Prefixing is lifted, too, i. e.,  $c.m \odot \Pi = \{c.m \, \boldsymbol{m} \mid \boldsymbol{m} \in \Pi\}$  for any  $c.m \in \mathsf{M}$ .

Performing a method call  $\mathbf{c}.m(v)$  in  $\Sigma; \Pi$  advances the *must* context to  $\Sigma \odot \mathbf{c}.m(v)$  but leaves  $\Pi$  unchanged. The sequence of methods  $\mathbf{m} \in \mathsf{M}^*$  in (2) is enabled in  $\Sigma; \Pi$ , written  $[\Sigma, \Pi] \Vdash \downarrow \mathbf{m}$  meaning that  $[(\Sigma, \mathbf{c})^{\#}, \pi_{\mathbf{c}}(\Pi)] \Vdash_{\mathbf{c}} \downarrow \pi_{\mathbf{c}}(\mathbf{m})$  for all  $\mathbf{c} \in \mathsf{O}$ . In this way, the context  $[\Sigma, \Pi]$  forms a joint policy state for all variables for the TUC P, in the sense of Sec. 2 (Def. 3).

Most of the rules in Figs. 4 and 5 should be straightforward for the reader familiar with structural operational semantics. Seq<sub>1</sub> is the case of a sequential P; Q Sequence

$$\frac{\Sigma; \Pi \vdash P \stackrel{\text{m}}{\longrightarrow} \Sigma' \vdash_{k'} P' \quad k' \neq 0}{\Sigma; \Pi \vdash P ; Q \stackrel{\text{m}}{\Rightarrow} \Sigma' \vdash_{k'} P' ; Q} \operatorname{Seq}_{1}$$

$$\frac{\Sigma; \Pi \vdash P \stackrel{\text{m}}{\Longrightarrow} \Sigma' \vdash_{0} P' \quad \Sigma'; \Pi \vdash Q \stackrel{\text{m}}{\Longrightarrow} \Sigma'' \vdash_{k'} Q'}{\Sigma; \Pi \vdash P ; Q \stackrel{\text{m}_{1}m_{2}}{\Longrightarrow} \Sigma'' \vdash_{k'} Q'} \operatorname{Seq}_{2}$$

m

Completion

$$\frac{}{\Sigma; \Pi \vdash \mathsf{skip} \stackrel{\varepsilon}{\Rightarrow} \Sigma \vdash_0 \mathsf{skip}} \mathsf{Cmp}_1 \qquad \frac{}{\Sigma; \Pi \vdash \mathsf{pause} \stackrel{\varepsilon}{\Rightarrow} \Sigma \vdash_1 \mathsf{pause}} \mathsf{Cmp}_2$$

Recursion

$$\frac{\Sigma; \Pi \vdash P\{\operatorname{\mathsf{rec}} p. P/p\} \stackrel{\text{def}}{\longrightarrow} \Sigma' \vdash_{k'} P'}{\Sigma; \Pi \vdash \operatorname{\mathsf{rec}} p. P \stackrel{\text{def}}{\longrightarrow} \Sigma' \vdash_{k'} P'} \operatorname{\mathsf{Rec}}$$

Fig. 4: SStep Reductions for Sequence, Completion and Recursion.

where P pauses or waits  $(k' \neq 0)$  and Seq<sub>2</sub> is where P terminates and control passes into Q. The statements skip and pause are handled by rules Cmp<sub>1</sub> and Cmp<sub>2</sub>. The rule Rec explains recursion rec p.P by syntactic unfolding of the recursion body P. All interaction with the memory takes place in the method calls let x = c.m(e) in P. Rule Let<sub>1</sub> is applicable when the method call is enabled, i. e.,  $[\Sigma, \Pi] \Vdash \downarrow c.m$ . Since processes are closed, the argument expression e must evaluate, eval(e) = v, and we obtain the new memory  $\Sigma \odot c.m(v)$  and return value  $\Sigma.c.m(v)$ . The return value is substituted for the local (stack allocated) identifier x, giving the continuation process  $P\{\Sigma.c.m(v)/x\}$  which is run in the updated context  $\Sigma \odot c.m(v)$ ;  $\Pi$ . The prediction  $\Pi$  remains the same. The second rule Let<sub>2</sub> is used when the method call is blocked or the thread wants to wait and yield to the scheduler. The rules for conditionals Cnd<sub>1</sub>, Cnd<sub>2</sub> are canonical. More interesting are the rules Par<sub>1</sub>-Par<sub>4</sub> for parallel composition, which implement non-deterministic thread switching. It is here where we need to generate predictions and pass them between the threads to exercise the policy control.

The key operation is the computation of the *can*-prediction of a process P to obtain an over-approximation of the set of possible method sequences potentially executed by P. For compositionality we work with sequences  $can^s(P) \subseteq \mathsf{M}^* \times \{0,1\}$  stoppered with a completion code 0 if the sequence ends in termination or 1 if it ends in pausing. The symbols  $\bot_0$ ,  $\bot_1$  and  $\top$  are the *terminated*, paused and fully unconstrained can contexts, respectively, with  $\bot_0 = \{(\varepsilon, 0)\}, \bot_1 = \{(\varepsilon, 1)\}$  and  $\top = \mathsf{M}^* \times \{0, 1\}$ . The set  $can^s(P)$ , defined in Fig 6, is extracted from the structure of P using prefixing  $c.m \odot \Pi'$ , choice  $\Pi'_1 \oplus \Pi'_2 = \Pi'_1 \cup \Pi'_2$ , parallel  $\Pi'_1 \otimes \Pi'_2$  and sequential composition  $\Pi'_1 \cdot \Pi'_2$ . Sequential composition is obtained pairwise on stoppered sequences such that  $(m, 0) \cdot (n, c) = (m, n, c)$  and  $(m, 1) \cdot (n, c) = (m, 1)$ . As a consequence,  $\bot_0 \cdot \Pi' = \Pi'$  and  $\bot_1 \cdot \Pi' = \bot_1$ . Parallel composition is pairwise free interleaving with synchronisation on completion codes. Specifically, a product  $(m, c) \otimes (n, d)$  generates all interleavings of m

#### Method Call

| $\underline{[\varSigma,\Pi] \Vdash \downarrow c.m  eval(e) = v \qquad \varSigma \odot c.m(v); \Pi \vdash P\{\varSigma.c.m(v)/x\} \xrightarrow{\mathbf{m}} \varSigma' \vdash_{k'} P'  Let_1$                                                                                        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\Sigma; \Pi \vdash \texttt{let}  x = \texttt{c}.m(e) \text{ in } P \xrightarrow{\texttt{c.m.m.}} \Sigma' \vdash_{k'} P'$                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                    |

| Let <sub>2</sub>                                                                                                                                                                                                                                                                   |

| $\varSigma;\Pi\vdash {\tt let} x={\tt c}.m(e){\tt in}P\stackrel{\varepsilon}{\Rightarrow}\varSigma\vdash_{\bot}{\tt let} x={\tt c}.m(e){\tt in}P$                                                                                                                                  |

| Conditional                                                                                                                                                                                                                                                                        |

| $\frac{eval(e) = true}{\Sigma; \Pi \vdash P \stackrel{m}{\Longrightarrow} \Sigma' \vdash_{k'} P'} \operatorname{Cnd}_{1}$ $\frac{F}{\Sigma; \Pi \vdash if \ e \ then \ P \ else \ Q \stackrel{m}{\Longrightarrow} \Sigma' \vdash_{k'} P'} \sum_{k' \in k'} \operatorname{Cnd}_{1}$ |

| $\Sigma; \Pi \vdash \texttt{if} \ e \ \texttt{then} \ P \ \texttt{else} \ Q \stackrel{\textbf{m}}{\Rightarrow} \Sigma' \vdash_{k'} P'$                                                                                                                                             |

| $eval(e) = false$ $\Sigma; \Pi \vdash Q \stackrel{m}{=} \Sigma' \vdash_{k'} Q'$ $Cnd_2$                                                                                                                                                                                            |

| $\Sigma; \Pi \vdash \texttt{if} \ e \ \texttt{then} \ P \ \texttt{else} \ Q \stackrel{\textbf{m}}{\Rightarrow} \Sigma' \vdash_{k'} Q'$                                                                                                                                             |

| Parallel                                                                                                                                                                                                                                                                           |

| $\underline{\Sigma; \Pi \otimes can(Q) \vdash P \stackrel{m}{\Longrightarrow} \Sigma' \vdash_{k'} P' \qquad k' \neq 0}_{Par_1} Par_1$                                                                                                                                              |

| $\Sigma; \Pi \vdash P_k \ _{k_Q} Q \stackrel{m}{\Longrightarrow} \Sigma' \vdash_{k' \sqcap k_Q} P'_{k'} \ _{k_Q} Q \stackrel{T}{\longrightarrow} Q$                                                                                                                                |

| $\underline{\Sigma;\Pi\otimes can(Q)\vdash P\stackrel{\mathbf{m}}{\Longrightarrow}\Sigma'\vdash_0P'}_{Par_2}Par_2$                                                                                                                                                                 |

| $\Sigma; \Pi \vdash P_k \parallel_{k_Q} Q \stackrel{\mathbf{m}}{\Longrightarrow} \varSigma' \vdash_{k_Q} Q$                                                                                                                                                                        |

| $\underline{\Sigma; \Pi \otimes can(P) \vdash Q \stackrel{\mathbf{m}}{\Longrightarrow} \Sigma' \vdash_{k'} Q' \qquad k' \neq 0}_{Par_3}$                                                                                                                                           |

| $\Sigma; \Pi \vdash P_{k_P} \parallel_k Q \xrightarrow{\mathbf{m}} \Sigma' \vdash_{k_P \sqcap k'} P_{k_P} \parallel_{k'} Q'$                                                                                                                                                       |

| $\underline{\Sigma; \Pi \otimes can(P) \vdash Q \stackrel{\mathbf{m}}{\Longrightarrow} \varSigma' \vdash_0 Q'}_{Par_4} Par_4$                                                                                                                                                      |

| $\Sigma; \Pi \vdash P_{k_P} \parallel_k Q \stackrel{m}{\Longrightarrow} \Sigma' \vdash_{k_P} P$                                                                                                                                                                                    |

#### Fig. 5: SStep Reductions for Method Calls, Conditional and Parallel.

and  $\boldsymbol{n}$  with a completion that models a parallel composition that terminates iff both threads terminate and pauses if one pauses. Formally,  $(\boldsymbol{m}, c) \otimes (\boldsymbol{n}, d) =$  $\{(\boldsymbol{c}, max(c, d)) \mid \boldsymbol{c} \in \boldsymbol{m} \otimes \boldsymbol{n}\}$ . Thus,  $\Pi'_P \otimes \Pi'_Q = \bot_0$  iff  $\Pi'_P = \bot_0 = \Pi'_Q$  and  $\Pi'_P \otimes \Pi'_Q = \bot_1$  if  $\Pi'_P = \bot_1 = \Pi'_Q$ , or  $\Pi'_P = \bot_0$  and  $\Pi'_Q = \bot_1$ , or  $\Pi'_P = \bot_1$ and  $\Pi'_Q = \bot_0$ . From  $can^s(P)$  we obtain  $can(P) \subseteq M^*$  by dropping all stopper codes, i.e.,  $can(P) = \{\boldsymbol{m} \mid \exists d. (\boldsymbol{m}, d) \in can^s(P)\}$ .

The rule  $\operatorname{Par}_1$  exercises a parallel  $P_k \|_{k_Q} Q$  by performing an sstep in P. This sstep is taken in the extended context  $\Sigma$ ;  $\Pi \otimes can(Q)$  in which the prediction of the sibling Q is added to the method prediction  $\Pi$  for the outer environment in which the parent  $P \| Q$  is running. In this way, Q can block method calls of P. When P finally yields as P' with a non-terminating completion code,  $0 \neq k' \in \{\bot, 1\}$ , the parallel completes as  $P'_{k'} \|_{k_Q} Q$  with code  $k' \sqcap k_Q$ . This operation is defined  $k_1 \sqcap k_2 = 1$  if  $k_1 = 1 = k_2$  and  $k_1 \sqcap k_2 = \bot$ , otherwise. When P terminates its sstep with code k' = 0 then we need rule  $\operatorname{Par}_2$  which removes child P' from the parallel composition. The rules  $\operatorname{Par}_3$ ,  $\operatorname{Par}_4$  are symmetrical to  $\operatorname{Par}_1$ ,  $\operatorname{Par}_2$ . They run the right child Q of a parallel  $P_{k_P} \|_k Q$ .

Completion and Stability. A process P' is 0-stable if P' = skip and 1-stable if P' = pause or  $P' = P'_1$ ;  $P'_2$  and  $P'_1$  is 1-stable, or  $P' = P'_1 \parallel_1 P'_2$ , and  $P'_i$  are 1-

$\begin{aligned} & \operatorname{can}^{s}(\operatorname{skip}) = \operatorname{can}^{s}(p) = \bot_{0} & \operatorname{can}^{s}(\operatorname{pause}) = \bot_{1} \\ & \operatorname{can}^{s}(\operatorname{rec} p. P) = \operatorname{can}^{s}(P) & \operatorname{can}^{s}(P \parallel Q) = \operatorname{can}^{s}(P) \otimes \operatorname{can}^{s}(Q) \\ & \operatorname{can}^{s}(P \text{ ; } Q) = \begin{cases} \operatorname{can}^{s}(P) & \operatorname{if} \operatorname{can}^{s}(P) \subseteq \mathsf{M}^{*} \times \{1\} \\ \operatorname{can}^{s}(P) \cdot \operatorname{can}^{s}(Q) & \operatorname{otherwise} \end{cases} \\ & \operatorname{can}^{s}(\operatorname{let} x = \operatorname{c.m}(e) \operatorname{in} P) = \operatorname{c.m} \odot \operatorname{can}^{s}(P) \\ & \operatorname{can}^{s}(\operatorname{rec} p) = \operatorname{can}^{s}(P) & \operatorname{if} \operatorname{eval}(e) = \operatorname{true} \\ & \operatorname{can}^{s}(Q) & \operatorname{if} \operatorname{eval}(e) = \operatorname{false} \\ & \operatorname{can}^{s}(P) \oplus \operatorname{can}^{s}(Q) & \operatorname{otherwise.} \end{cases} \end{aligned}$

Fig. 6: Computing the *can* Prediction.

stable. A process is *stable* if it is 0-stable or 1-stable. A process expression is *well-formed* if in each sub-expression  $P_{1 \ k_1} \parallel_{k_2} P_2$  of P the completion annotations are matching with the processes, i. e., if  $k_i \neq \bot$  then  $P_i$  is  $k_i$ -stable. Stable processes are well-formed by definition. For stable processes we define a *(syntactic) tick function* which steps a stable process to the next tick. It is defined such that  $\sigma(\texttt{skip}) = \texttt{skip}, \sigma(\texttt{pause}) = \texttt{skip}, \sigma(P'_1; P'_2) = \sigma(P'_1); P'_2 \text{ and } \sigma(P'_1 \ k_1 \parallel_{k_2} P'_2) = \sigma(P'_1) \parallel \sigma(P'_2).$

*Example 4.* The data-flow cnt-cmp from Fig. 3c can be represented as a DCoL process in the form  $C = \text{reg.init}(0); (M_{\perp} \parallel_{\perp} I)$  with

$$\begin{split} M &=_{df} \operatorname{rec} p. \, \mathtt{v} = \mathtt{xs. pres}(); P(v); \mathtt{pause}; p \\ P(v) &=_{df} \mathtt{if} v \mathtt{then reg.set}(0); \mathtt{else} Q \\ Q &=_{df} u = \mathtt{ws.get}(); \mathtt{reg.set}(u); \\ I &=_{df} \mathtt{rec} q. \, \mathtt{v} = \mathtt{reg.get}(); \mathtt{ws.put}(v+1); \mathtt{pause}; q \end{split}$$

Let us evaluate process C from an initialised memory  $\Sigma_0$  such that  $\Sigma_0.\mathbf{xs} = 0 = \Sigma_0.\mathbf{ws}$ , and empty environment prediction  $\{\epsilon\}$ .

The first sstep is executed from the context  $\Sigma_0$ ;  $\{\epsilon\}$  with empty can prediction. Note that reg.init(0);  $(M_{\perp} \parallel \perp I)$  abbreviates let \_ = reg.init(0) in  $(M_{\perp} \parallel \perp I)$ . In context  $\Sigma_0$ ;  $\{\epsilon\}$  the method call reg.init(0) is enabled, i.e.,  $[\Sigma_0, \{\epsilon\}] \Vdash \downarrow$  reg.init. Since eval(0) = 0, we can execute the first method call of C using rule Let<sub>1</sub>. This advances the memory to  $\Sigma_1 = \Sigma_0 \odot$  reg.init(0). The continuation process  $M_{\perp} \parallel \perp I$  is now executed in context  $\Sigma_1; \perp_0$ . The left child M starts with method call xs.pres() and the right child I with reg.get(). The latter is admissible, since  $(\Sigma_1.reg)^{\#} = 1$ . Moreover, get does not need to honour any precedences, whence it is enabled,  $[\Sigma_1, \Pi] \Vdash \downarrow$  reg.get for any  $\Pi$ . On the other hand, xs.pres in M is enabled only if  $(\Sigma_1.xs)^{\#} = 1$  or if there is no concurrent emit predicted for xs. Indeed, this is the case: The concurrent context of M is  $\Pi_I = \{\epsilon\} \otimes can(I) = can(I) = \{\text{reg.get} \cdot \text{ws.put}\}$ . We project  $\pi_{xs}(\Pi_I) = \{\epsilon\}$  and find  $[\Sigma_1, \Pi_I] \Vdash \downarrow xs.pres$ . Hence, we have a nondeterministic choice to take an sstep in M or in I. Let us use rule  $Par_1/Par_2$  to run M in context  $\Sigma; \Pi_I$ . By loop unfolding Rec and rule Let<sub>1</sub> we execute the present test of M which returns the value  $\Sigma_1.\mathbf{xs.pres}() = \mathbf{false}$ . This leads to an updated memory  $\Sigma_2 = \Sigma_1 \odot \mathbf{xs.pres}() = \Sigma_1$  and continuation process  $P(\mathbf{false})$ ;  $\mathbf{pause}; M$ . In this (right associated) sequential composition we first execute  $P(\mathbf{false})$  where the conditional rule  $Cnd_2$  switches to the  $\mathbf{else}$  branch Q which is  $u = \mathbf{ws.get}()$ ;  $\mathbf{reg.set}(u)$ ;, still in the context  $\Sigma_2, \Pi_I$ . The reading of the data-flow variable  $\mathbf{ws}$ , however, is not enabled,  $[\Sigma_2, \Pi_I] \nvDash \downarrow \mathbf{ws.get}$ , because  $(\Sigma_2.\mathbf{ws})^{\#} = 0$  and thus get not admissible. The sstep blocks with rule Let<sub>2</sub>:

$$\begin{array}{c} \overbrace{\Sigma_{2}; \Pi_{I} \vdash Q \stackrel{\epsilon}{\Rightarrow} \Sigma_{2} \vdash_{\perp} Q}^{\text{Let}_{2}} \operatorname{Cnd}_{2} \\ \xrightarrow{\Sigma_{2}; \Pi_{I} \vdash P(\texttt{false}) \stackrel{\epsilon}{\Rightarrow} \Sigma_{2} \vdash_{\perp} Q}^{\text{Let}_{2}} \operatorname{Cnd}_{2} \\ \xrightarrow{\Sigma_{2}; \Pi_{I} \vdash P(\texttt{false}); \texttt{pause}; M \stackrel{\epsilon}{\Rightarrow} \Sigma_{2} \vdash_{\perp} Q; \texttt{pause}; M}_{\text{Seq}_{1}} \operatorname{Let}_{1}(\Sigma_{1}; \Pi_{I} \vdash \downarrow \texttt{xs. pres})} \\ \xrightarrow{\Sigma_{1}; \Pi_{I} \vdash \texttt{v} = \texttt{xs. pres}(); P(v); \texttt{pause}; M \stackrel{\epsilon}{\Rightarrow} \Sigma_{2} \vdash_{\perp} Q; \texttt{pause}; M}_{\text{Rec}} \operatorname{Let}_{1}(\Sigma_{1}; \Pi_{I} \vdash \downarrow \texttt{xs. pres})}_{\text{Rec}} \\ \xrightarrow{\Sigma_{1}; \{\epsilon\} \vdash M \perp \parallel_{\perp} I \stackrel{m_{2}}{\Longrightarrow} \Sigma_{2} \vdash_{\perp} Q; \texttt{pause}; M) \perp \parallel_{\perp} I}_{\Sigma; \{\epsilon\} \vdash C \stackrel{m_{1}m_{2}}{\longrightarrow} \Sigma_{2} \vdash_{\perp} (Q; \texttt{pause}; M) \perp \parallel_{\perp} I}} \operatorname{Par}_{1} \\ \xrightarrow{\Sigma; \{\epsilon\} \vdash C \stackrel{m_{1}m_{2}}{\longrightarrow} \Sigma_{2} \vdash_{\perp} (Q; \texttt{pause}; M) \perp \parallel_{\perp} I}}_{\text{Let}_{1}(\Sigma; \perp_{0} \Vdash \downarrow \texttt{reg.init})} \end{array}$$

where  $m_1 = \operatorname{reg.init}$  and  $m_2 = \operatorname{xs.pres}$ . In the next sstep, from  $\Sigma_2$ ;  $\Pi_Q$  with  $\Pi_Q = \{\epsilon\} \otimes can(Q; \operatorname{pause}; M) = can(Q; \operatorname{pause}; M) = \{\operatorname{ws.get} \cdot \operatorname{reg.set}\}$  we let the process I execute its  $\operatorname{reg.get}()$  with rules Rec and  $\operatorname{Let}_1$ . The return value is  $v = \Sigma_2 \cdot \operatorname{reg.get}() = 0$ . Then, from the updated memory  $\Sigma_3 = \Sigma_2 \odot \operatorname{reg.get}()$  we run the continuation process  $\operatorname{ws.put}(0+1)$ ;  $\operatorname{pause}; I$ . The ws.put is enabled if the IVar is empty and there is no concurrent put on ws predicted from M. Both conditions hold since  $(\Sigma_3.\operatorname{ws})^{\#} = (\Sigma.\operatorname{ws})^{\#} = 0$  and  $\pi_{\operatorname{ws}}(\Pi_Q) = \{\operatorname{get}\}$ . Therefore,  $[\Sigma_3, \Pi_Q] \Vdash \downarrow \operatorname{ws.put}$ . With the evaluation eval(0+1) = 1 the rule  $\operatorname{Let}_1$  permits us to update the memory as  $\Sigma_4 = \Sigma_3 \odot \operatorname{ws.put}(1)$  and continue with process  $\operatorname{pause}; I$  which completes by pausing. Formally, this sstep is:

| $ \begin{array}{c} \hline & \Sigma_4; \Pi_Q \vdash \texttt{pause} \xrightarrow{\epsilon} \Sigma_4 \vdash_1 \texttt{pause} \\ \hline & \Sigma_4; \Pi_Q \vdash \texttt{pause}; I \xrightarrow{\epsilon} \Sigma_4 \vdash_1 \texttt{pause}; I \end{array} \\ \begin{array}{c} Seq_1 \\ Seq_1 \\ state \end{array} $ |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $ \underbrace{ \Sigma_4; \Pi_Q \vdash \texttt{pause}; I \stackrel{\epsilon}{\Rightarrow} \Sigma_4 \vdash_1 \texttt{pause}; I }_{\text{Transform}} Let_2 $                                                                                                                                                       |

| $\Sigma_3: \Pi_O \vdash \texttt{ws.put}(0+1): \texttt{pause}: I \stackrel{m_4}{\Longrightarrow} \Sigma_4 \vdash_1 \texttt{pause}: I$                                                                                                                                                                            |

| $ \underbrace{\Sigma_2; \Pi_Q \vdash v = \operatorname{reg.get}(); \operatorname{ws.put}(v+1); \operatorname{pause}; I \xrightarrow{m_3 m_4} \Sigma_4 \vdash_1 \operatorname{pause}; I}_{m_2 m_4} \operatorname{Let}_1 }_{\text{Rec}} $                                                                         |

| $ \underbrace{\Sigma_2; \Pi_Q \vdash I \xrightarrow{m_3m_4} \Sigma_4 \vdash_1 \text{ pause}; I }_{Para} Para $                                                                                                                                                                                                  |

| $\Sigma_2; \{\epsilon\} \vdash (Q; \mathtt{pause}; M) \perp \parallel \perp I \xrightarrow{\mathfrak{m}_3\mathfrak{m}_4} \Sigma_4 \vdash_{\perp} (Q; \mathtt{pause}; M) \perp \parallel_1 (\mathtt{pause}; I)$                                                                                                  |

where  $m_3 = \operatorname{reg.get}$  and  $m_4 = \operatorname{ws.put}$ . In the next systep the waiting method  $u = \operatorname{ws.get}$  in Q is now admissible and can proceed,  $(\Sigma_4.\operatorname{ws})^{\#} = ((\Sigma_3 \odot \operatorname{ws.put}(1)).\operatorname{ws})^{\#} = 1$  and thus  $[\Sigma_4, \Pi] \Vdash \downarrow \operatorname{ws.get}$  for all  $\Pi$ . The return value is  $u = \Sigma_4.\operatorname{ws.get}() = 1$ , the updated memory  $\Sigma_5 = \Sigma_4 \odot \operatorname{ws.put}(1)$  and the continuation process  $\operatorname{reg.set}(1)$ ; pause; M. The register set method is admissible since  $(\Sigma_4.\operatorname{reg})^{\#} = 1$  and also enabled because there is no get predicted in the concurrent environment  $\bot_0$ . Thus,  $[\Sigma_5, \bot_0] \Vdash \downarrow \operatorname{reg.set}$ . The execution of the method yields the memory  $\Sigma_6 = \Sigma_5 \odot \operatorname{reg.set}(1)$  with continuation process

pause; M which completes by pausing. This yields the derivation tree:

| - Cmp <sub>2</sub>                                                                                                                                                                       |                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| $\Sigma_6$ : $\{\epsilon\} \vdash $ pause: $M \Rightarrow \Sigma_6 \vdash_1$ pause: $M \stackrel{12}{\rightarrow} \dots$                                                                 |                  |

| $\frac{\Sigma_5; \{\epsilon\} \vdash \text{reg.set}(1); \text{pause}; M \stackrel{m_6}{\Longrightarrow} \Sigma_6 \vdash_1 \text{pause}; M}{\text{Let}_1}$                                |                  |

| $ \underbrace{\Sigma_4; \{\epsilon\} \vdash Q; \mathtt{pause}; M \xrightarrow{\mathfrak{m}_5\mathfrak{m}_6} \Sigma_6 \vdash_1 \mathtt{pause}; M } $                                      | Par <sub>2</sub> |

| $\overline{\Sigma_4; \{\epsilon\} \vdash (Q; \mathtt{pause}; M) \perp \ _1 \text{ (pause}; I)} \xrightarrow{m_5 m_6} \Sigma_6 \vdash_1 (\mathtt{pause}; M) \ _1 \ _1 \text{ (pause}; I)$ | 1 d12            |

#### 3.1 Determinacy, Termination and Constructiveness

Determinacy of DCoL is a result of two components, monotonicity of policyconformant scheduling and CSM coherence. Monotonicity ensures that whenever a method is executable and policy-enabled, then it remains policy-enabled under arbitrary ssteps of the environment. Symmetrically, the environment cannot be blocked by a thread taking policy-enabled computation steps.

The second building block for determinacy is CSM variable coherence. Consider a context  $\Sigma; \Pi_Q$  in which we run an sstep of P with prediction  $\Pi_Q$  for concurrent process Q, resulting in a final memory  $\Sigma'_P$  arising from executing a sequence  $\mathbf{m}_P$  of method calls from P. Because of the policy constraint, the sequence  $\mathbf{m}_P$  must be enabled under all predictions  $\mathbf{n} \in \Pi_Q$ , i. e.,  $[\Sigma, \mathbf{n}] \Vdash \downarrow \mathbf{m}_P$ . Suppose, on the other side, we sstep the process Q in the same memory  $\Sigma$  with prediction  $\Pi_P$  for P, resulting in an action sequence  $\mathbf{m}_Q$  and final memory  $\Sigma'_Q$ . Then, by the same reasoning,  $[\Sigma, \mathbf{n}] \Vdash \downarrow \mathbf{m}_Q$  for all  $\mathbf{n} \in \Pi_P$ . But since  $\mathbf{m}_P$  is an actual execution of P it must be in the prediction for P, i. e.,  $\mathbf{m}_P \in \Pi_P$  and symmetrically,  $\mathbf{m}_Q \in \Pi_Q$ . But then we have  $[\Sigma, \mathbf{m}_Q] \Vdash \downarrow \mathbf{m}_P$  and  $[\Sigma, \mathbf{m}_P] \Vdash \downarrow \mathbf{m}_P$  which means  $\Sigma \Vdash \mathbf{m}_P \diamond \mathbf{m}_Q$ . Now if the semantics of method calls is policy-coherent then the Monotonicity can be exploited to derive a confluence property for processes which guarantees that  $\mathbf{m}_P$  can still be executed by P in state  $\Sigma'_Q$  and  $\mathbf{m}_Q$  by Q in state  $\Sigma'_P$ , and both lead to the same final memory.