## SEFI Modeling in Readout Integrated Circuit induced by Heavy Ions at Cryogenic Temperatures

Laurent Artola, S. Ducret, F. Advent, Guillaume Hubert, Julien Mekki

## ▶ To cite this version:

Laurent Artola, S. Ducret, F. Advent, Guillaume Hubert, Julien Mekki. SEFI Modeling in Readout Integrated Circuit induced by Heavy Ions at Cryogenic Temperatures. IEEE Nuclear & Space Radiation Effects Conference (NSREC 2018), Jul 2018, Waikoloa, HI, United States. hal-01957110

HAL Id: hal-01957110

https://hal.science/hal-01957110

Submitted on 17 Dec 2018

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## SEFI Modeling in Readout Integrated Circuit induced by Heavy Ions at Cryogenic Temperatures

L. Artola, S. Ducret, F. Advent, G. Hubert, J. Mekki

This paper presents for the first time a modeling approach of SEFI which takes into account all the physical and electrical processes from the radiation particle down to the event at the system level. This work was focused on the evaluation of SEFI sensitivity by experimental and simulation analyses of a ROIC designed by Sofradir for their IR image sensors. Relevant correlations between simulation and experimental results of SEFI cross sections for heavy ions were presented and discussed. The simulation results confirmed the strong SEFI robustness of the ROIC at 57 K.

Index Terms - Single Event Functional Interrupt, modeling, heavy ions, readout integrated circuit, infrared detectors, low temperatures

#### I. INTRODUCTION

Space environment is known to be an harsh environment in terms of temperature, vibration, or radiations for embedded devices and circuits. Soft error (SE) can be induced in electronics systems by radiation particles [1][1], such as cosmic rays, protons, even electrons (more recently) [3].

Complementary Metal Oxide Semiconductor (CMOS) technology is the main technology used in on-board systems, especially in digital circuits such as readout integrated circuit (ROIC) of CMOS image sensors (CIS) or infrared (IR) image sensors. The pixel array is controlled by the readout circuit of the image sensor. A readout circuit is composed by raw and column decoders, multiplexers, memories and various logics and sequential cells. CIS of Infrared image sensors are keys device in spacecraft for applications, like Earth or space observation, the guidance system in a spacecraft (launcher or satellite). For these reasons, it is necessary to assure the reliability of such systems during the space mission.

Due to the harsh space environment, ROICs are known to be sensitive to single event effects (SEE), such as single event transient (SET), single event upset (SEU) [4]. One of the main critical failure in space environment of digital device is the lost of functionality of the device, also called Single Event Functional Failure (SEFI) [14]. For space industry it is

necessary to evaluate this risk. Radiation tests with heavy ion or proton beams are used to quantify of the SEFI risk on embedded devices or circuits such as ROICs. However, the SEE radiation tests are performed twice: at the beginning of the device/circuit development, and at the end. If the results of radiation tests are not acceptable, at this time, it could be critical (technically and financially) to re-develop additional SEFI countermeasures in order to fit with project requirements.

So, the SEFI modeling in ROICs could be very useful in order to anticipate the risk due to space radiations. Simulation-based fault injection frameworks allow early evaluation of the system reliability when only the system description and the associate models are available [5]-[10]. Some soft error modeling approaches have been developed by the mean of fault injection at RTL (Register Transfer Level) using different code such as VHDL (Very High Description Language). However, none of these approaches allow linking the injected faults in the studied circuit with the radiation constraint.

The goal of this paper is to present a new SEFI modeling approach which considers the radiation particle down to the occurrence of a functional interruption of one of ROICs designed by Sofradir for their IR image sensor. The SEFI modeling was based on the use of the Monte Radiation tool, MUSCA SEP3 tool [11][12] coupled with an new injection platform dedicated to simulate fault injections at multiple system levels: transistor, and gate: TERRIFIC (Transient ERRor Injection Framework for Integrated CMOS).

First, the ROIC device will be presented. Second, the experimental results (SEE cross sections) obtained during heavy ion test will be presented. Third, the approach dedicated to the modeling of SEE and especially SEFI will be detailed. Finally, the SEFI estimations will be compared with experimental data and discussed.

# II. READOUT INTEGRATED CIRCUIT DEDICATED TO INFRARED IMAGE SENSOR

The readout circuits developed and studied in this work has been developed by Sofradir in a 0.25  $\mu m$  Bulk technology, with shallow trench isolation (STI) [13]. This technology is a mixed technology allowing high voltages on analog parts. This technology allows working at cryogenic temperature: 57 K for this circuit. Infrared image sensors are cooled down at

L. Artola and G. Hubert are with ONERA / DPHY, Université de Toulouse, F-31055 Toulouse, France (email: <a href="mailto:laurent.artola@onera.fr">laurent.artola@onera.fr</a>)

S. Ducret, F. Advent are with Sofradir, 38113, Veurey-Voroize, France.

J. Mekki, is with CNES, The French Space Agency 31401, Toulouse, France

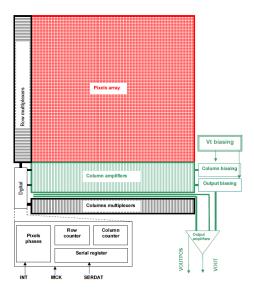

Fig. 1 Overview of the investigated Readout integrated circuit developed by Sofradir.

cryogenic temperature with the aim to reduce the leakage current, or also known as the dark current and to increase its performances

Fig. 1 presents a global description of the ROIC. The current-voltage conversion was realized by the integration of the input charges on the integrated capacitance. The charges transferred from integration to readout capacitances were then transferred to the amplifiers located into the columns and at the output of the ROIC. The circuit was composed by row and columns multiplexers in order to address the pixels arrays.

However, a test transistor was implemented into the direct injection stage to allow the ROIC tests before the hybridization of the detectors. This approach was used for the SEE radiation tests. The ROIC proposes three modes: NORMAL mode, IMAGER mode, and MEMORY mode. The master clock frequency is set at 4 MHz. For confidential reasons, only a brief description of the three modes is presented below:

- NORMAL mode: during this mode the macro-pixels are read. The pixel array size is 160 × 160. One frame is required to output the whole array.

- IMAGER mode: The aim of this mode is either to perform images with all the sub-pixels, or to detect permanent changes in the sub-pixel array. This mode will be used to determine the initial sub-pixel mapping or a new mapping linked to the evolution of the detector during its operational life.

- MEMORY mode: The aim of this mode is to detect state changes in the sub-pixels memories. These changes are mainly

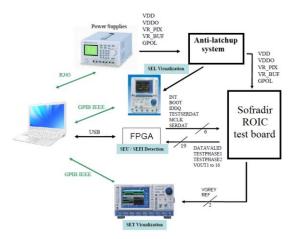

Fig. 2 Experimental setup of SEE detection in ROIC from Sofradir during heavy ion tests.

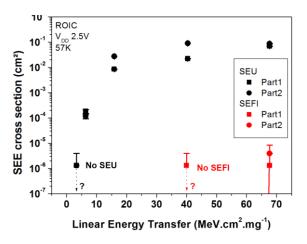

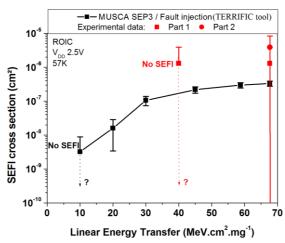

Fig. 3 Experimental SEE cross sections, for SEU (in black), for SEFI (in red) of the two samples of ROIC under heavy ions beam at 57 K

linked to mapping or irradiations issues. The system should store the sub-pixel mapping to be able to detect the states changes after a MEMORY mode sequence.

In this work, the modeling of SEFI events was done in IMAGER mode. Note that in this work, only the CMOS digital parts of the ROIC were modeled and analyzed.

### III. SEFI SENSITIVITY OF SOFRADIR ROIC

#### A. SEE irradiation tests under heavy ions

SEE tests were performed at UCL (Université Catholique de Louvain, Belgium) by the mean of the heavy ions facility. The principle of the temperature control system used during the heavy ion tests is based on a cooling machine with a cooled finger. The ASIC device is fixed on the top of the cooled finger and directly connected to the vacuum chamber. The complete description of the heavy ions test setup and

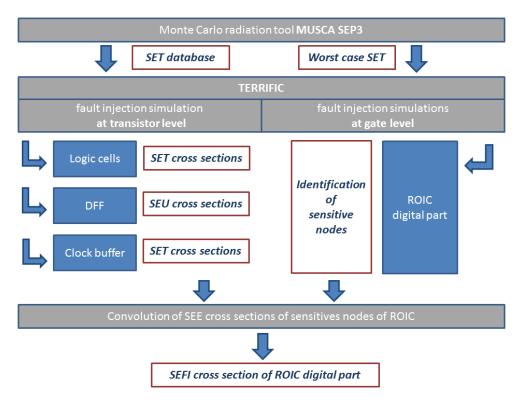

Fig. 4 General framework of SEFI modeling in the digital part of the ROIC based on MUSCA SEP3 and TERRIFIC (Transient ERRor Injection Framework for Integrated CMOS: (a) Simulations and calculation steps are in grey, (b) simulation targets (gate and device) are in blue, inputs/outputs of simulations and calculations are in red rectangles.

the temperature control system (at 57 K) were presented in previous works [4] [14]. However, the specific detection of SEFI signatures on the ROIC is illustrated in Fig. 2.

Fig. 3 presents the experimental SEE cross sections, for SEU (in black), for SEFI (in red) of the two ROIC samples tested in IMAGER mode under heavy ions. A strong difference in cross sections is observed for the SEU and the SEFI. The error signature of the observed SEFI corresponds to a change in the used mode of the ROIC. This change required an on/off cycle to recover the correct ROIC. Because of project behavior of the requirements for the SEE qualification of the ROIC, the fluence of each run is about 7.7x10<sup>5</sup> cm<sup>-2</sup>, as mandatory by the European Space Components Coordination (ESCC) basic specification No 25100 [15]. Two samples of ROIC were tested. The SEFI sensitivity of the ROIC is very low; Even if the SEU sensitivity is very well characterized (with very low statistic error bar), it appears that data of SEFI measurements could be completed by simulations.

One of the interests of the modeling of SEFI presented in next section will be to provide more data and discussed the reasons of such SEFI robustness. A potential new test plan for future radiation campaign will be also discussed.

### B. Description of the SEFI modeling approach

The main principle of this modeling approach is based on the two steps of simulations. Fig. 4 presents the global framework of the SEFI modeling approach.

The Monte Carlo (MC) radiation tool, MUSCA SEP3 was used [11][12][13]. This tool is developed at ONERA since 2008. As mentioned, the tool uses a MC approach coupled in a sequential modeling of all the physical and electrical processes. The following steps are considered: (a) the modeling of the radiation constraint, (b) the transport mechanisms of radiation particles (in this work heavy ions) through the layer stack (BEOL), (c) the generation of electron-hole pairs in the silicon, (d) the mechanisms of charges transport and collection, (e) the circuit feedback.

The modeling of the radiation environment is based on several inputs data (from engineer models, physical models), regarding the accessible data. These models are provided by ONERA's internal research group which is considered as a one of worldwide references [16].

The modeling of transport mechanisms of radiation particles through the over layers is based on databases from GEANT4 (for nuclear reactions) and SRIM (for ionization mechanism). The interest of using database is the time consuming gain in comparison to full direct simulations.

The modeling transport and collection of free carriers in the silicon is performed by the mean of 3D analytical models in order to take into account the

following mechanisms: ambipolar diffusion, dynamic collection, multi-collection bipolar amplification, recombination, bias dependence, temperature dependence. It is important to highlight that all the physical and electrical models used for the transport and collection of charges in the semi-conductor take into account the impact of the temperature, down to 50K.

The modeling of the Front-End Of Line (FEOL) is issued from the description (dimensions and locations) of drain and source implants of each n-MOS and p-MOS transistor. This information was extracted by a GDS extractor from the design file provided by Sofradir.

This simulation framework allows for obtaining SET database. The communication link between MUSCA SEP3 and Spectre simulator was done by the mean of a new simulation framework called TERRIFIC (Transient ERRor Injection Framework for Integrated CMOS). This injection tool allows for performing electrical SET injections at various levels: (a) transistor level, (b) at gate level.

At transistor level, the injections are performed using the SET databased generated by MUSCA SEP3 as done in several previous works [12][13]. These simulations allowed estimating the SET and SEU cross sections of a set of basic digital cell used in the ROIC. After an analysis of the layout of the ROIC, three main families of standard cells were selected: logic cells, D-Flip-Flops (DFF), and clock buffers. This selection is based on a preliminary fault injection simulation at gate level of the ROIC. These cell families correspond to the majority area of the digital part of the ROIC. It was revealed that the standard cells of the PDK (Process Design Kit) used by Sofradir for their ROIC have a very similar SET/SEU cross sections for various design in each digital function, especially at cryogenic temperatures (57 K) [4][17]. According to these works, a hypothesis of a variation of +/- 25% of SET/SEU cross section would be considered for each main family of standard cells. The MUSCA SEP3 simulations were performed for one reference of each selected main families. The respective SEE cross sections will be presented and discussed in the next section.

At gate level, TERRIFIC performs fault injection simulations based on SEE evaluation of SET injections (issued from MUSCA SEP3). The characteristics of these SETs correspond to the worst cases in terms of amplitude and duration.

In the same time, automatized fault injection simulations were performed on the digital modules of the ROIC using the TERRIFIC tool developed in SKILL [18]. The fault injection was done at gate level on each floating node of the circuitry using Spectre simulator. Injections of current pulses were simulated on clocked signals, while injections of voltage pulsed were simulated on the other floating nodes. This

(c)

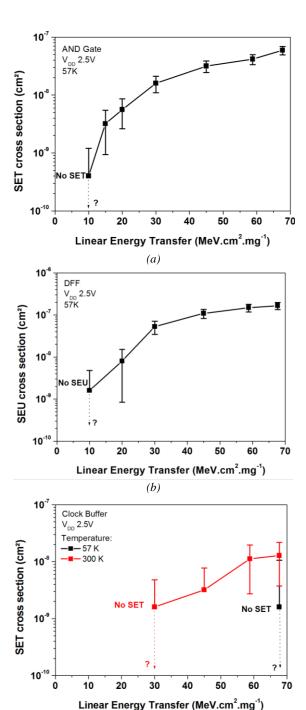

Fig. 5 Simulations of SEU and SET cross sections of: (a)

AND gate, (b), DFF, (c) clock buffer

allowed for not disturbing the nominal bias of the ROIC before the fault injection. The simulations allowed identifying the sensitive nodes and the associated standard cells which could induce a SEFI in the digital part of the ROIC.

The identification of sensitive nodes and the SEE cross section of logic cells, DFF, and clock buffers were used to calculate the SEFI cross section of the ROIC.

Fig. 6 Comparison of experimental (red symbols) and simulation (black symbols) of the SEFI cross section of ROIC as a function of LET of heavy ions at 57K.

#### IV. DISCUSSION

Fig. 5 shows the simulations of SEE (SET and SEU) cross sections of the selected reference for each cell family: logics, DFF, and clock buffers. The results MUSCA SEP3 simulations coupled TERRIFIC runs were obtained for a simulated fluence of  $1x10^8$  cm<sup>-2</sup> up to  $1x10^9$  cm<sup>-2</sup> regarding the investigated cell. The error bars correspond two times of the standard deviation (97% of confidence). Fig. 5 (a) presents the SET cross section of a reference of AND gates as a function of LET of heavy ions simulated at 57 K. As expected for the SET, the saturation of the cross section is not well observed. The phenomenon is due to the low drive current for this design of the AND gate [17]. Fig. 5 (b) presents the SEU cross section of a reference of DFF as a function of heavy ion LETs simulated at 57 K. The LET threshold is the same as the AND gate (i.e., 10 MeV.cm<sup>2</sup>.mg<sup>-1</sup>) illustrated in the figures by a dashed arrow and a question mark. Fig. 5 (c) presents the SET cross section of a reference of clock buffer as a function of heavy ion LETs. No event was observed during the simulations at 57 K (in black). In order to evaluate if the cell is totally immune to SET, an increase in the temperature was simulated. An increase in temperature is known to lead to an increase in the SET duration [19]. This point is in good correlation with previous works which highlighted that if a cryogenic temperature dependence of SEE occurrence is observed, the worst case must be at room temperature [13][14]. The simulations highlight the potential SET sensitivity of the clock buffer at 300 K (in red). However, for the ROIC point of view, the contribution of clock buffer to the SEFI occurrence is very limited (~ 10%).

As mentioned in the previous section, these SEE cross sections were convoluted with the identified sensitive nodes of the ROIC (thank to the fault

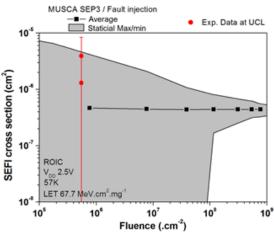

Fig. 7 Comparison of experimental data (in red) and Monte Carlo simulation of the SEFI cross section as a deposited fluence of 67.6 MeV.cm<sup>2</sup>.mg<sup>-1</sup> heavy ions

injection simulation). This final step allowed calculating the SEFI sensitivity of the ROIC. Fig. 6 presents the comparison of experimental (red symbols) and simulation (black symbols) data of the SEFI cross section of the ROIC as a function of LET of heavy ions at 57 K. The error bars correspond to two times of the standard deviation (97% of confidence). The simulations are in good correlation with the experimental data and confirm the strong robustness of the ROIC against SEFI.

Fig. 7 presents the calculated SEFI cross section by MC simulation as a function of fluence. It integrates the evolution of the statistical errors. The simulation results show a similar SEFI sensitivity (i.e. between  $1\times10^{-6}$  and  $4\times10^{-6}$  cm<sup>2</sup>) obtained for the same fluence used during experimental tests  $(7.7\times10^5 \, \text{cm}^{-2})$ . The simulation results confirmed the weak deposited fluence during experimental data for a relevant quantitative evaluation of the SEFI sensitivity of the ROIC. Considering the simulation results a relevant fluence would be around  $1\times10^8 \, \text{cm}^{-2}$  and  $5\times10^9 \, \text{cm}^{-2}$ .

In the future projects, the radiation test plan of ROICs developed by Sofradir will be updated. In addition to the standard specification from ESCC (for SEU tests), a dedicated run for SEFI measurement could be performed with high fluence levels. This specific SEFI test plan will be developed regarding preliminary simulations of this new SEFI modeling approach. Even if such increase in fluence is not representative of a given space mission for Earth orbits, it would improve the understanding of SEFI in complete digital systems under a radiation constraint.

#### V. CONCLUSION

This paper presented for the first time a modeling approach of SEFI which takes into account all the physical and electrical processes from the radiation particle down to the event at the system level. This

work was focused on the evaluation of SEFI sensitivity by experimental and simulation analyses of a ROIC designed by Sofradir for their IR image sensors. Relevant correlations between simulation and experimental results of SEFI cross sections for heavy ions were presented and discussed. The simulation results confirmed the strong SEFI robustness of the ROIC at 57 K.

The SEFI modeling approach has presented promising applications for radiation hardness assurance and will be a strong input for the preparation of future radiation tests. For rare events such SEFI, it allows obtaining a first sensitive level of the device before radiation tests and defining potentially higher fluence than the regular radiation standards with the aim to reduce error bars if needed. Even if such increase in fluence during radiation test is not representative of a given space mission for Earth orbits, it would improvement the understanding of SEFI mechanisms in complete digital systems under a radiation constraint.

By definition the SEFI evaluation defines the operability rate of a given system. An other promising perspective of such SEFI modeling approach will be the operational evaluation of an embedded system used in a given space integration platform for various orbits.

#### V. REFERENCES

- [1] G. R. Hopkinson, "Radiation effects in CMOS active pixel sensor," IEEE Trans. Nucl. Sci., vol. 47, no, 6, pp. 2480-2484, Dec. 2000.

- [2] D. Falguere, D. Boscher, T. Nuns, S. Duzellier, S. Bourdarie, R. Ecoffet, S. Barde, J. Cueto, C. Alonzo, C. Hoffman," In-flight observations of the radiation environment and its effects on devices in the SAC-C polar orbit" IEEE Trans. Nucl. Sci., vol. 49, no. 6, pp.2782 -2887, Dec. 2002.

- [3] P. Caron, C. Inguimbert, L. Artola, N. Chatry, N. Sukhaseum, R. Ecoffet, F. Bezerra, "Physical mechanisms inducing electron Single Event Upset," IEEE Trans. Nucl. Sci., early access 2018.

- [4] A. Al Youssef, L. Artola, S. Ducret, G. Hubert, R. Buiron, C. Poivey, F. Perrier, S. Parola, "Single-Event Transients in Readout Circuitries at Low Temperature Down to 50 K" et al, IEEE Trans. Nucl. Sci., vol. 65, no. 1, pp. 119-125, Jan. 2018.

- [5] R. Leveugle, "Fault injection in VHDL descriptions and emulation", The IEEE International Symposium on Defect and Fault Tolerance in VLSI Systems, Yamanashi, Japan, October 25-27, 2000", IEEE Computer Society Press, Los Alamitos, California, 2000, pp. 414-419 S. K. S. Hari, et al, ASPLOS Proceedings, pp. 123–134, 2012.

- [6] P. S. Magnusson, M. Christensson, J. Eskilson, D. Forsgren, G. Hallberg, J. Hogberg, F. Larsson, A. Moestedt, B. Werner," Simics: A full system simulation platform", Computer, vol. 35, no. 2, pp. 50–58, Feb. 2002.

- [7] G. C Cardarilli, F. Kaddour, A. Leandri, M. Ottavi, S. Pontarelli and R. Velazco, "Bit flip injection in processor-based architectures: A case study,"

- Proceedings of the Eighth IEEE International On-Line Testing Workshop (IOLTW'02), 2002.

- [8] N. Binkert, B. Beckmann, G. Black, S. K Reinhardt, A. Saidi, A. Basu, J. Hestness, D. R Hower, T. Krishna, S. Sardashti, R. Sen, K. Sewell, M. Shoaib, N. Vaish, M. D Hill, D. A Wood, "The gem5 simulator" SIGARCH Comput. Archit. News, vol. 39, no. 2, pp. 1–7, Aug. 2011.

- [9] Jun Xu, Ping Xu, "The Research Of Memory Fault Simulation And Fault Injection Method For BIT Software Test", Second International Conference on Instrumentation & Measurement, Computer, Communication and Control, 2012.

- [10] F. de Aguiar Geissler, F. Lima Kastensmidt, J. Eduardo Pereira Souza, "Soft error injection methodology based on QEMU software platform" IEEE Latin American Test Workshop - LATW, pp. 1–5, Mar. 2014.

- [11] G. Hubert, S. Duzellier, C. Inguimbert, C. Boatella-Polo, F. Bezerra, R. Ecoffet, "Operational SER Calculations on the SAC-C Orbit Using the Multi-Scales Single Event Phenomena Predictive Platform (MUSCA SEP3)" IEEE Trans. Nucl. Sci., vol. 56, no. 6, pp. 3032-3042, Dec. 2009.

- [12] G. Hubert, L. Artola, "Single-Event Transient Modeling in a 65-nm Bulk CMOS Technology Based on Multi-Physical Approach and Electrical Simulations", IEEE Trans. Nucl. Sci., vol. 60, no. 6, pp. 4421-4429, Dec. 2013.

- [13] L. Artola, G. Hubert, O. Gilard, S. Ducret, F. Perrier, M. Boutillier, P. Garcia, G. Vignon, B. Baradat, N. Ricard, "Single Event Upset Sensitivity of D-Flip Flop of Infrared Image Sensors for Low Temperature Applications Down to 77 K," IEEE Trans. Nucl. Sci., vol. 64, no. 6, pp. 2979-2987, Dec. 2015.

- [14] L. Artola, A. Al Youssef, S. Ducret, R. Buiron, S. Parola, G. Hubert, C. Poivey, Single Event Transient and Functional Interrupt in Readout Integrated Circuit of Infrared Image Sensors at Low Temperatures' IEEE Radiation Effects Data Workshop, pp. 315-319, 2017.

- [15] ESA radiation standards and guidelines https://escies.org/

- [16] S. Bourdarie, M. Xapsos, "The near-earth space radiation environment" IEEE TNS, vol. 54, pp. 1810-1832, 2008.

- [17] L. Artola, G. Hubert, S. Ducret, J. Mekki, Ahmad Al Youssef, N. Ricard, "Impact of D-Flip-Flop Architectures and Designs on Single Event Upset Induced by Heavy Ions", IEEE Trans. Nucl. Sci., early access 2018.

- [18] T. J. Barnes, "SKILL: a CAD system extension language" IEEE 27th ACM/IEEE Design Automation Conference Proceeding, pp. 266-271, 1990.

- [19] L. Artola, G. Hubert "Modeling of Elevated Temperatures Impact on Single Event Transient in Advanced CMOS Logics Beyond the 65-nm Technological Node", IEEE Trans. Nucl. Sci., vol. 61, no. 4, pp. 1610-1617, Aug. 2014.

- [20] OMERE software. ver. 4.0, 2014 [Online]. Available: http://www.trad.fr/OMERE-14.html