## Normally-off AlGaN/GaN MOS-HEMT using ultra-thin Al0.45 Ga0.55N barrier layer

Ahmed Chakroun, Abdelatif Jaouad, Meriem Bouchilaoun, Osvaldo Arenas,

Ali Soltani, Hassan Maher

### ▶ To cite this version:

Ahmed Chakroun, Abdelatif Jaouad, Meriem Bouchilaoun, Osvaldo Arenas, Ali Soltani, et al.. Normally-off AlGaN/GaN MOS-HEMT using ultra-thin Al0.45 Ga0.55N barrier layer. Physica Status Solidi A (applications and materials science), 2017, 214 (8), 10.1002/pssa.201600836. hal-01914374

### HAL Id: hal-01914374 https://hal.science/hal-01914374v1

Submitted on 16 Nov 2018

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Normally-off AlGaN/GaN MOS-HEMT using ultra-thin Al<sub>0.45</sub>Ga<sub>0.55</sub>N barrier layer

#### Ahmed Chakroun, Abdelatif Jaouad, Meriem Bouchilaoun, Osvaldo Arenas, Ali Soltani, and Hassan Maher

Laboratoire Nanotechnologies Nanosystèmes (LN2) – CNRS UMI-3463 – Institut Interdisciplinaire d'Innovation Technologique (3IT), Université de Sherbrooke, 3000 Boulevard de l'université, Sherbrooke, QC J1 K OA5, Canada

In this work, we report on the fabrication of a normally-off AlGaN/GaN Metal–Oxide–Semiconductor High Electron Mobility Transistor (MOS-HEMT) using an ultra-thin  $Al_{0.45}Ga_{0.55}N$  barrier layer. The AlGaN barrier was thinned down to 1 nm using a digital etching process (Oxidation/ Etching) and was followed by a PECVD deposition technique of a 7 nm thick SiO<sub>x</sub> layer used as gate insulator. Thanks to the thin AlGaN barrier layer (4 nm), only a few digital etching

cycles are required to shift the threshold voltage toward positive values. The fabricated normally-off device exhibits a pinch-off voltage of +1.1 V, a maximum  $I_{\rm DS}$  current of 460 mA mm<sup>-1</sup> at  $V_{\rm GS} = +5$  V, an On-state resistance ( $R_{\rm ON}$ ) of 7.8  $\Omega$  · mm and an  $I_{\rm ON}/I_{\rm OFF}$  ratio higher than 10<sup>9</sup>. Moreover, the pulsed  $I_{\rm DS}-V_{\rm DS}$  and capacitance–voltage (C-V) curves versus frequency confirm that there is no damage induced by the digital etching process.

Keywords AlGaN, digital etching, GaN, high electron mobility transistors, metal-oxide-semiconductor structures, passivation

**1 Introduction** Thanks to its superior fundamental properties, Gallium Nitride (GaN) has received extensive attention for high power and high frequency applications. AlGaN/GaN High Electron Mobility Transistors (HEMTs) have demonstrated tremendous potential due to their high sheet carrier density and 2DEG electron mobility. Standard AlGaN/GaN HEMT structures have a negative threshold voltage ( $V_{TH}$ ), giving a "normally-on" operation mode. One of the major challenges for GaN-HEMTs power devices is the achievement of an enhancement-mode device "normally-off," required for a simpler drive circuitry and safer operation [1].

Several techniques have been reported in order to shift the threshold voltage toward positive values. The most cited ones are: fluorine ( $F^-$ ) ion implantation [1–4], AlGaN barrier recess [5–8], and p-GaN (or p-AlGaN) gated structure [9–10]. The gate recess approach by dry etching has been largely used but it suffers from a non-uniformity recess depth and a high plasma induced damage, which considerably deteriorates the electron mobility in the channel and the device reliability [11]. To avoid the plasma induced damage, some works reported

on the use of digital etching process to etch the AlGaN barrier layer. This consists of barrier oxidation using a soft oxygenbased plasma followed by a wet-chemistry removal of the formed oxide layer [12]. The major drawback of this technique is the extremely low etching rate (~5 Å/cycle). Sixty-three Oxidation/Etching cycles have been used to etch a 24 nm thick AlGaN barrier [12]. In addition, the reported MOSHEMT device exhibits a large hysteresis (~0.7 V), suggesting a deficient Al<sub>2</sub>O<sub>3</sub>/GaN interface with an estimated interface traps density ( $D_{it}$ ) of 2.6 × 10<sup>12</sup> eV<sup>-1</sup>.cm<sup>-2</sup> [12].

In this work, we report on the achievement of a normally-off AlGaN/GaN MOS-HEMT by using an ultrathin Al<sub>0.45</sub>Ga<sub>0.55</sub>N barrier and a digital etching process followed by an optimized PECVD-SiO<sub>x</sub> passivation procedure. Thanks to the initially thin Al<sub>0.45</sub>Ga<sub>0.55</sub>N barrier (4 nm), only six Oxidation/Etching cycles are needed to shift the threshold voltage toward positive values. The fabricated device exhibits stable characteristics, with a positive pinch-off voltage of +1.1 V, an  $I_{DS}$  current of 460 mA mm<sup>-1</sup> at  $V_{GS} = +5$  V and a gate leakage current below 1 nA mm<sup>-1</sup>. Based on the hysteresis measurements, the extracted  $D_{it}$  was estimated to be as low as  $1.49 \times 10^{11} \text{ cm}^{-2} \text{ eV}^{-1}$ . This showcases the low damage induced by the digital etching technique and the efficiency of the proposed passivation process.

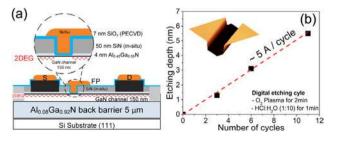

2 Experimental The AlGaN/GaN MOS-HEMTs were fabricated on commercial HEMT wafers (supplied by EpiGaN) grown by Metal-Organic Chemical Vapor Deposition (MOCVD) on a Si substrate. The epitaxial structure consists of an Al<sub>0.08</sub>Ga<sub>0.92</sub>N back barrier layer, a 150 nm undoped GaN channel layer and a thin 4 nm Al<sub>0.45</sub>Ga<sub>0.55</sub>N barrier layer. The epitaxial structure was finally capped with a 50 nm in situ SiN layer. The fabrication process begins by dry-etching the in situ SiN layer before the e-beam evaporation of the ohmic contact metal stack (Ti/Al/Ni/Au). Rapid thermal annealing was then performed at 875 °C for 30 sec in N2 ambient. Device isolation was achieved by nitrogen ion implantation. For the gate electrode, the 50 nm SiN cap layer was first etched using very low power (5W) SF<sub>6</sub>-based ICP plasma. The revealed AlGaN layer, in the gate area, was then oxidized using an  $O_2$ plasma asher for 2 min. The sample was then dipped in an HCl: H<sub>2</sub>O (1:10) solution for 1 min to remove the formed oxide layer. After six digital etching cycles, the AlGaN barrier was thinned down to near 1 nm, as confirmed by Atomic Force Microscopy (AFM) shown in Fig. 1(b). A control sample, without digital recess, was also fabricated as a reference. Both samples were then cleaned and annealed at  $420 \degree C$  for 20 min under a N<sub>2</sub> ambient to desorb the F<sup>-</sup> ions from the AlGaN surface [13]. Prior to the gate dielectric layer deposition, the samples were pretreated using a KOH solution, followed by an immersion in HCl for 2 min. A 7 nm thick PECVD-SiO<sub>x</sub> layer was then deposited as a gate insulator using the passivation process previously reported in [14]. Finally, a Ni/Au (40/600 nm) gate metal stack was deposited by e-beam evaporation. Fig. 1(a) illustrates a schematic of the fabricated MOS-HEMT device using digital etching process. The etching rate, extracted from the Atomic Force Microscopy (AFM) analyses, is about 5 A/cycle, as can be seen in Fig. 1(b). Electrical characterizations were performed using a Keithley 4200SCS analyzer.

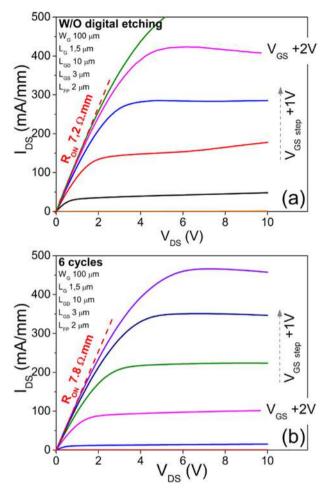

**3 Results and discussion** Figure 2 shows the DC output characteristics for the fabricated AlGaN/GaN

**Figure 1** (a) Schematics of the fabricated MOS-HEMT and (b) digital etching depth versus digital etching cycles.

**Figure 2**  $I_{DS}-V_{DS}$  characteristic measured on fabricated MOS-HEMTs (a) W/O digital etching (reference) and (b) with six cycles.

MOS-HEMTs with a 1.5 µm gate length, a 10 µm gateto-drain distance, a 3 µm gate-to-source distance, and a 2 µm field plate length. The MOS-HEMT device, fabricated on a reference sample, without digital etching (Fig. 2(a)), demonstrates a normally-on operation with a pich-off voltage of -1.2 V and an On-state resistance ( $R_{ON}$ ) of  $7.2 \Omega \cdot \text{mm}$ . The MOS-HEMT with six cycles of digital etching shows a normally-off operation with a drain current density of 460 mA mm<sup>-1</sup> at  $V_{GS} = +5$  V (Fig. 2(b)). The extracted  $R_{ON}$  is slightly higher, about  $7.8 \Omega \cdot \text{mm}$ , showing that no significant surface degradation was induced by digital etching on the device  $R_{ON}$ .

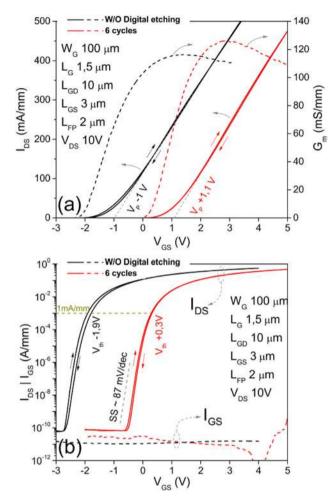

Figure 3 shows the device hysteresis transfer characteristics  $(I_{DS}-V_{GS})$  at  $V_{DS} = 10$  V. The pinch-off voltage  $(V_p)$ was shifted from -1.2 to +1.1 V after six cycles of digital etching. The maximum  $G_m$  peaks, measured on both devices, were about 130 mS mm<sup>-1</sup> as can be seen in Fig. 3 (a). The threshold voltage  $(V_{TH})$  measured at  $I_{DS} = 1$  mA mm<sup>-1</sup> was shifted from -1.9 to +0.3 V after AlGaN barrier thinning as can be seen in Fig. 3(b). A low hysteresis was observed in both samples on (a) linear and (b)

**Figure 3** (a) Linear and (b) semi-logarithmic transfer characteristics  $I_{DS}-V_{GS}$  of the fabricated MOS-HEMTs device.

semi-logarithmic scale  $I_{\rm DS}-V_{\rm GS}$  curves. This demonstrates the efficiency of the gate recess and the passivation processes. Moreover, thanks to the high quality of the 7 nm PECVD-SiO<sub>x</sub> gate insulator, the device exhibits a low gate leakage current. For the whole measurement range, the maximum gate leakage current ( $I_{\rm GS}$ ) is below 1 nA mm<sup>-1</sup>. Furthermore, the off-state drain leakage current is also below 1 nA mm<sup>-1</sup>, giving an  $I_{\rm ON}/I_{\rm OFF}$  ratio higher than 10<sup>9</sup>. The sub-threshold slope (SS) extracted from the transfer characteristic is about 87 mV dec<sup>-1</sup> for both devices, as can be seen in Fig. 3(b).

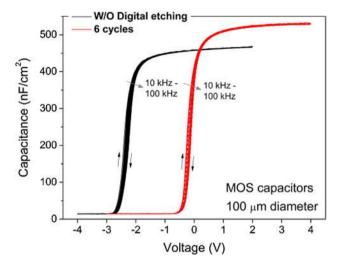

Circular MOS capacitors, with a 100  $\mu$ m diameter, were also fabricated on both samples. Figure 4 shows the hysteresis capacitance–voltage ( $C_{GS}-V_{GS}$ ) measurements performed at frequency ranged from 10 to 100 kHz. Both devices show good surface potential modulation with very low hysteresis. MOS capacitor fabricated on the control sample, without digital etching, shows a maximum accumulation capacitance of 460 nF.cm<sup>-2</sup>. By thinning down the AlGaN barrier to near 1 nm using six oxidation/ etching cycles, the threshold voltage is positively shifted and the maximum accumulation capacitance value increases

**Figure 4** Capacitance–Voltage ( $C_{GS}-V_{GS}$ ) hysteresis measurements performed on MOS capacitors at frequencies ranging from 10 to 100 kHz with a 10 kHz step.

to 530 nF.cm<sup>-2</sup>. Using the equation:  $D_{it} = C_{MOS} \cdot \Delta V_{TH}/q$  [2, 6], the extracted traps density ( $D_{it}$ ) for the reference sample without digital etching is estimated to be  $3.71 \times 10^{11}$  cm<sup>-2</sup> eV<sup>-1</sup>. For the gate recessed sample, using six cycles of digital etching, the estimated  $D_{it}$  was as low as  $1.49 \times 10^{11}$  cm<sup>-2</sup> eV<sup>-1</sup>. This indicates that there is no major damage induced by the digital etching process. Due to the low thickness of the SiO<sub>x</sub>-PECVD dielectric layer used in this study (7 nm), the *C*-*V* two-step behavior, as previously reported by Yatabe et al. [15], is not observed in our reference sample, even at higher voltage (up to +6 V). Moreover, a catastrophic dielectric breakdown was observed at a voltage around +6.5 V. This dielectric breakdown was also confirmed by the large increase in the dielectric leakage current after the dielectric breakdown.

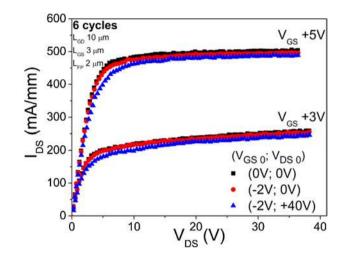

Pulsed  $I_{\rm DS}-V_{\rm DS}$  characteristics were performed on the normally-off MOSHEMT device, achieved using AlGaN barrier digital etching. The measurement pulse width was 500 ns and the period was fixed to 10 ms. The results, as shown in Fig. 5, demonstrate a negligible gate lag and a low drain lag, below 8%, for a drain voltage of up to +40 V. These results strongly support the high SiO<sub>x</sub>/AlGaN interface quality and that no damage was induced by the proposed digital etching process.

**4 Conclusions** In summary, a normally-off MOS-HEMT device with extremely low hysteresis was demonstrated by using an ultra-thin  $Al_{0.45}Ga_{0.55}N$  barrier layer. The electrical characterizations show a pinch-off voltage ( $V_p$ ) of +1.1 V, a threshold voltage of +0.3 V at  $I_{\rm DS} = 1 \text{ mA mm}^{-1}$ , a maximum drain current of 460 mA mm<sup>-1</sup>, and a low gate and drain leakage current. The device also shows an  $I_{\rm ON}/I_{\rm OFF}$  ratio higher than 10<sup>9</sup> and a Subthreshold slope of 87 mV dec<sup>-1</sup>. From *C*-*V* and  $I_{\rm DS}-V_{\rm GS}$ hysteresis measurements, a  $D_{\rm it}$  value as low as  $1.49 \times 10^{11} \text{ cm}^{-2} \text{ eV}^{-1}$  has been extracted for the sample

**Figure 5** Pulsed  $I_{DS}-V_{DS}$  curves measured on MOSHEMT device with six cycles of digital etching. Pulse width = 500 ns, period = 10 ms.

with the gate digital etching recess. All these results confirm the low damage induced by the digital etching recess at the  $SiO_x/AlGaN$  interface. The usage of initial thin  $Al_{0.45}Ga_{0.55}N$  barrier reduces the recess time by digital etching required for this critical step. This approach could be used for the monolithically integration of enhancement and depletion (E/D) mode GaN devices on the same wafer, which will simplify drastically circuit design.

Acknowledgements Authors would like to acknowledge Caroline Roy, Adrien Cutivet and all LNN staff for their contributions in microfabrication process, pulsed characterizations and for fruitful discussions. LN2 is a joint International Research Laboratory (Unité Mixte Internationale UMI 3463) funded and cooperated by CNRS (France) and Université de Sherbrooke (Canada) as well as INSA Lyon, ECL, CPE, Université Grenoble Alpes (UGA), as well as the French national nanofabrication network RENATECH.

#### References

- Z. Tang, Q. Jiang, Y. Lu, S. Huang, S. Yang, X. Tang, and K. J. Chen, 600-V normally off SiN<sub>x</sub>/AlGaN/GaN MIS-HEMT with large gate swing and low current collapse, IEEE Electron. Device Lett. **34**(11), 1373–1375 (2013).

- [2] Y. Wang, M. Wang, B. Xie, C. P. Wen, J. Wang, Y. Hao, W. Wu, K. J. Chen, and Bo Shen, High-performance normally-off Al<sub>2</sub>O<sub>3</sub>/GaN MOSFET using a wet etching-based gate recess technique, IEEE Electron Device Lett. **34**(11), 1370–1372 (2013).

- [3] Z. Xu, J. Wang, Y. Cai, J. Liu, Z. Yang, X. Li, M. Wang, Z. Yang, Bin Xie, M. Yu, W. Wu, X. Ma, J. Zhang, and Y. Hao, 300 °C operation of normally-off AlGaN/GaN MOSFET with low leakage current and high on/off current ratio, Electron. Lett. 50(4), 315–316 (2014).

- [4] T. Oka and T. Nozawa, AlGaN/GaN recessed MIS-Gate HFET with high-threshold-voltage normally-off operation for power electronics applications, IEEE Electron Device Lett. 29(7), 668–670 (2008).

- [5] S. Huang, S. Yang, J. Roberts and K. J. Chen, Threshold voltage instability in Al<sub>2</sub>O<sub>3</sub>/GaN/AlGaN/GaN metal-insulator-semiconductor high-electron mobility transistors, Jpn. J. Appl. Phys. 50, 110202 (2011).

- [6] Z. Xu, J. Wang, J. Liu, C. Jin, Y. Cai, Z. Yang, M. Wang, M. Yu, B. Xie, W. Wu, X. Ma, J. Zhang, and Y. Hao, Demonstration of normally-off recess-gated AlGaN/GaN MOSFET using GaN cap layer as recess mask, IEEE Electron Device Lett. **35**(12), 1197–1199 (2014).

- [7] S. Liu, S. Yang, Z. Tang, Q. Jiang, C. Liu, M. Wang, and K. J. Chen, Al<sub>2</sub>O<sub>3</sub>/AlN/GaN MOS-channel-HEMTs with an AlN interfacial layer, IEEE Electron Device Lett. **35**(7), 723–725 (2014).

- [8] T. E. Hsieh, E. Y. Chang, Y. Z. Song, Y. C. Lin, H. C. Wang, S. C. Liu, S. Salahuddin, and C. C. Hu, Gate recessed quasinormally OFF Al<sub>2</sub>O<sub>3</sub>/AlGaN/GaN MIS-HEMT with low threshold voltage hysteresis using PEALD AlN interfacial passivation layer, IEEE Electron Device Lett. **35**(7), 732–734 (2014).

- [9] Y. Uemoto, M. Hikita, H. Ueno, H. Matsuo, H. Ishida, M. Yanagihara, T. Ueda, T. Tanaka, and D. Ueda, Gate Injection Transistor (GIT) A Normally-Off AlGaN/GaN Power Transistor Using Conductivity Modulation, IEEE Trans. Electron Devices 54(12), 3393–3399, (2007).

- [10] O. Hilt, A. Knauer, F. Brunner, E. Bahat-Treidel, and J. Würfl, Normally-off AlGaN/GaN HFET with p-type Ga gate and AlGaN buffer, 22nd International Symposium on Power Semiconductor Devices & IC's (ISPSD), Hiroshima, pp. 347–350 (2010)

- [11] H. Hahn, G. Lukens, N. Ketteniss, H. Kalisch, and A. Vescan, Recessed-gate enhancement-mode AlGaN/GaN heterostructure field-effect transistors on Si with record DC performance, Appl. Phys. Express 4, 114102 (2011).

- [12] Y. Wang, M. Wang, B. Xie, C. P. Wen, J. Wang, Y. Hao, W. Wu, K. J. Chen, and B. Shen, High-performance normally-off Al<sub>2</sub>O<sub>3</sub>/GaN MOSFET using a wet etching-based gate recess technique, IEEE Electron Device Lett. **34**(11), 1370–1372 (2013).

- [13] A. Lorenz, J. Derluyn, J. Das, K. Cheng, S. Degroote, F. Medjdoub, M. Germain, and G. Borghs, Influence of thermal anneal steps on the current collapse of fluorine treated enhancement mode SiN/AlGaN/GaN HEMTs, Phys. Status Solidi C 6(S29), S996–S998 (2009).

- [14] A. Chakroun, H. Maher, E. Al Alam, A. Souifi, V. Aimez, R. Ares, and A. Jaouad, Optimized pre-treatment process for MOS-GaN devices passivation, IEEE Electron Device Lett. 35(3), 318–320 (2014).

- [15] Z. Yatabe, Y. Hori, W.-C. Ma, J. T. Asubar, M. Akazawa, T. Sato, and T. Hashizume, Characterization of electronic states at insulator/(Al)GaN interfaces for improved insulated gate and surface passivation structures of GaN-based transistors, Jpn. J. Appl. Phys. 53, 100213 (2014).