# High-quality Ge/Si virtual substrates fabricated by a low cost and scalable process

Youcef A. Bioud<sup>1</sup>, Abderraouf Boucherif<sup>1</sup>, Maksym Myronov<sup>2</sup>, Ali Soltani<sup>1</sup>, Gilles Patriarche<sup>3</sup>, Nadi Braidy<sup>1</sup>, Dominique Drouin<sup>1</sup> and Richard Arès<sup>1</sup>

<sup>2</sup> Department of Physics, University of Warwick, Coventry, CV4 7AL, United Kingdom.

## 1. Summary

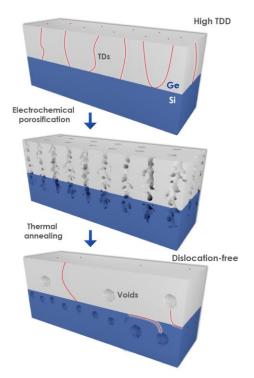

In this presentation, we propose a new defect engineering strategy in highly mismatched heteroepitaxy to simultaneously achieve low dislocation density and epi-ready Ge/Si virtual substrate using a scalable process. By self-assembling nanovoids around the Ge/Si interface from both sides through dislocation-selective electrochemical deep etching and thermal annealing, a continuous Ge layer is obtained, in which, a large portion of the original threading dislocations are pinned and annihilated close to a free surface (see Fig. 1), giving a new configuration so-called "Nanovoids-based Ge/Si Virtual Substrate (NVS)".

### 2. Introduction

Developing inexpensive, high-performance epitaxial devices with the hope of achieving widespread market adoption, depends critically on production costs and ultimate material quality. Any process that meets these challenges successfully provides solutions for a wide range of leading-edge applications. Due to the large difference in the lattice constant between the epitaxial materials and heterosubstrates, strain is introduced in epitaxial layer, which leads to the generation of a high density of misfit dislocations. Dislocations act as recombination centers for carriers and have a detrimental effect on device performance. Devices like photodetectors, multi-junction solar cells, transistors, modulators, based on Ge-on-Si (001) technology are facing these issues. To this end, several approaches have been proposed for reducing the TD density. However, many of these techniques are limited to small-scale processes and require the use of expensive and complex processing technologies. In addition, the TD density remains high for many device applications [1].

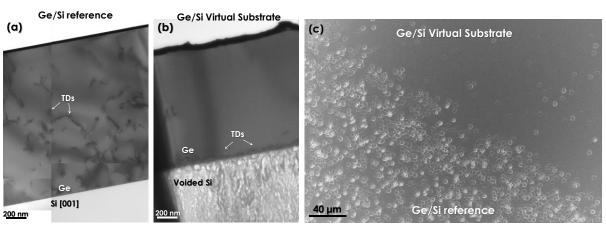

Ge/Si (001) samples with high TDD are anodically porosified by the bipolar electrochemical etching technique [2]–[4]. The layer structure shows selectively distributed mesopores obtained by selective dislocations deep etching. The porosification front reaches the Ge/Si heterointerface, forming a porous layer in the Si substrate, as shown in Fig. 2. The resulting mesoporous Ge/Si structure is transformed into quasi-monocrystalline voided Ge on voided Si during thermal annealing [5]–[7].

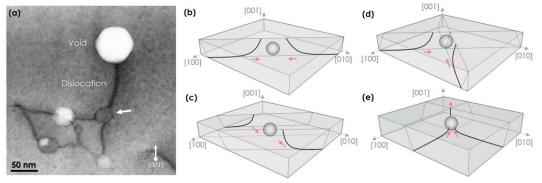

Fig. 3a. indicates the location where a dislocation segment ends at the nanovoid with no propagation beyond. A reasonable explanation for the TD reduction is that two dislocations with opposite Burgers vectors having the same magnitude have reached the void, according to fusions, complete and half annihilation reactions (See Fig. 3b-d). In such structure, the TDs have an interaction radius higher than the interaction radius in the conventional structure without voids, which in turn increases their recombination probability.

Fig. 4 ab. shows TEM micrographs from the Ge/Si reference and the NVS, respectively. A high defect density region, extending from the heterointerface towards the surface may be observed for the Ge/Si reference. A dense dislocation network confined in a region of 50 nm close to the Ge/Si interface of the NVS, and almost nonexistent defects within the Ge layer. In the NVS configuration, TDs bend towards the voids in Si onto the glide plane in order to minimize their length, causing their elimination at the nearest free surface. The averaged TDD is reduced significantly from  $\sim 10^7$  cm<sup>-2</sup> to  $\sim 10^4$  cm<sup>-2</sup> for 1.5  $\mu$ m thick Ge layers, which is considered low for such a thin epitaxial layer (see Fig. 4a).

### 4. Conclusion

Ultra-low TDD in mismatched Ge on Si films is produced by a simple and inexpensive process, which consists on tuning the dislocation motion by selfassembling nanovoids close to the Ge/Si interface. It that introducing nanovoids recombination of dislocations by increasing their interaction radius. The voids located at the Si substrate act as a free surface for inhibiting threading dislocation propagation towards the active layer of the device, leading to the creation of an almost defect free Ge layer on Si.

## References

- KETEPERICES

[1] H. Ye and J. Yu, "Germanium epitaxy on silicon," Sci. Technol. Adv. Mater., vol. 15, p. 24601, 2014.

[2] Y. A. Bioud et al., "Fast growth synthesis of mesoporous germanium films by high frequency bipolar electrochemical etching," Electrochim. Acta, vol. 232, pp. 422–430, 2017.

[3] M. N. Beattie et al., "Tunable conductivity in mesoporous germanium," Nanotechnology, pp. 0–23, 2018.

[4] Y. A. Bioud, A. Boucherif, A. Belarouci, E. Paradis, D. Drouin, R. Ares, "Chemical composition of anodically formed p-type porus GaAs in HF based electrolyte," in Conference: Porous Semiconductors Semiconductors Semiconductors Semiconductors Semiconductors Semiconductors Semiconductors Semiconductors and Technology (PSST), 2016.

[5] Y. A. Bioud, A. Boucherif, E. Paradis, A. Soltani, D. Drouin, and R. Arès, "Low cost Ge/Si virtual substrate through dislocation trapping by nanovoids," Inter. Conf. Si Epi. Heterostruct. proceeding, vol. 2, 2017.

- 2017.

[6] M. N. Beattie et al., "Quasi-monocystalline Ge as an interface layer for multi-junction solar cells on Si substrates: Electrical resistivity and device modelling," in 2017 Photonics North (PN), 2017, p. 1.

[7] Y. Bioud, A. Boucherif, A. Belarouci, E. Paradis, D. Drouin, and R. Arès, "MESOPOROUS GERMANIUM BY HIGH FREQUENCY BIPOLAR ELECTROCHEMICAL ETCHING FOR OPTICAL Conference, 2016.

<sup>&</sup>lt;sup>1</sup> Laboratoire Nanotechnologies Nanosystèmes (LN2) - CNRS UMI-3463, Institut Interdisciplinaire d'Innovation Technologique (3IT), Université de Sherbrooke, 3000 Boulevard Université, Sherbrooke, J1K OA5, Québec, Canada.

<sup>&</sup>lt;sup>3</sup> Centre for Nanoscience and Nanotechnology, CNRS, Université Paris-Sud, Université Paris-Saclay, Route de Nozay, 91460 Marcoussis, France. Email: Y.Bioud@usherbrooke.ca, A.Boucherif@USherbrooke.ca

Fig. 1. Schematic illustration of the nanovoid based Ge/Si virtual substrate architecture.

Fig. 2. TEM image of porous Ge/Si formed using a current density of 4 mA/cm² during 30 min shows a thick porous Ge layer with weakly branched pores crossing threading dislocation cores up to full uprooting of misfit dislocations.

Fig. 3. BF-STEM image shows gliding dislocations in the Ge layer join the void area until its complete annihilation (a). Possible processes for annihilation of TDs at the void surface by interaction of several threading segments from: the same slip system (b), the parallel slip system (c), by a combination of glide and slip motion (d) and by fusion (e).

Fig. 4. TEM images of the Ge/Si reference substrate (a) and the nanovoid based Ge/Si virtual substrate (b) show the annihilation of dislocation segments coming from the Ge/Si interface at the void located in the Si substrate. (c) Etch-pit density taken from the edge of the NVS shows the TDD reducing from  $\sim 10^7$  cm<sup>-2</sup> to  $\sim 10^4$  cm<sup>-2</sup> for 1.5  $\mu$ m thick Ge layer.