# Current mode read-out circuit for infrared photodiode applications in 0.35 $\mu m$ CMOS

Pietro Maris Ferreira, José Gabriel R.C. Gomes, Antonio Petraglia

## ▶ To cite this version:

Pietro Maris Ferreira, José Gabriel R.C. Gomes, Antonio Petraglia. Current mode read-out circuit for infrared photodiode applications in 0.35  $\mu m$  CMOS. Proc ACM IEEE Symp. Integr. Circuits Syst. Design, Aug 2008, Gramado, Brazil. 10.1145/1404371.1404405 . hal-01898807

HAL Id: hal-01898807

https://hal.science/hal-01898807

Submitted on 5 Oct 2022

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Current Mode Read-out Circuit for Infrared Photodiode Applications in 0.35 $\mu$ m CMOS

Pietro M. Ferreira, José Gabriel R. C. Gomes and Antonio Petraglia

Federal University of Rio de Janeiro

Program of Electrical Engineering - EPOLI,COPPE-UFRJ

CP 68504 - 21941-972 Rio de Janeiro, RJ - Brazil

maris@ieee.org,{gabriel,antonio}@pads.ufrj.br

### **ABSTRACT**

Infrared focal plane arrays have a wide range of military, medical, industrial and scientific applications, where high resolution and high performance read-out integrated electronics are required. This work advances a regulated cascode current mirror (RCCM) amplifier in  $0.35\,\mu{\rm m}$  CMOS technology for application in hybrid CMOS-InGaAs implementations. With an output impedance of  $236~{\rm k}\Omega$ , the RCCM produces and output noise power of  $8.06~{\rm nA}$  (RMS), to achieve a SNR of 77 dB and a dynamic range of 60 dB at  $-40~{\rm dB}$  THD. Comparisons with alternative approaches considering key performance parameters are presented.

## **Categories and Subject Descriptors**

B.7.2 [Integrated Circuits]: Design Aids—Layout; Simulation

## **General Terms**

Design

## **Keywords**

current-mode,infra-red, read-out, image sensor

### 1. INTRODUCTION

Read-out integrated circuits (ROICs) for image sensors are designed for visual wavelength detection purposes, such as the ones in [1]-[7], and have been proposed for infrared wavelength [8]-[13]. However, infrared focal plane arrays have a wide range of military, medical, industrial, and scientific applications, where high resolution and high performance read-out electronics are required. The resolution can be increased by increasing the number of pixels, but then, the pixel size needs to be reduced to decrease not only the overall chip area and therefore its cost, but also the cost of optics. However, the small pixel size limits the complexity, and hence the performance of the read-out circuit.

A high performance circuit should provide a controlled detector bias to reduce the dark current and detector noise. It should have low input impedance to obtain high injection efficiency (i.e.,

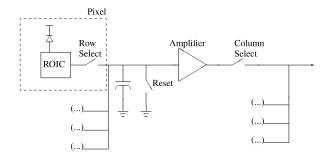

$R_D/R_{IN}+R_j$ ), for integrating maximum amount of current generated by the detector on the integration capacitance and for increasing its bandwidth and decreasing its input referred noise. Also, it should have a large dynamic range to increase the maximum charge storage capacity, which requires large integration capacitance and high voltage swing [12]. The integration capacitor is preferable placed outside the pixel, as shown in Fig. 1, so the capacitance can be increased without increasing the pixel size.

Figure 1: Architecture for current mode read-out circuits.

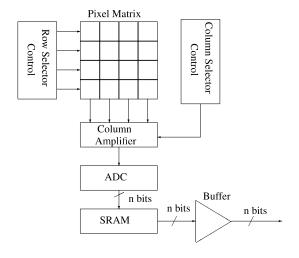

The majority of the reported read-out circuits are implemented in voltage-mode. They are based on the framework illustrated in Fig. 2, and digitize the integrated current at the column amplifiers. However, as technology scales down, the voltage supply is reduced, affecting the column amplifier operation. The most significant resulting effect is a lower signal swing.

Figure 2: Architecture for voltage mode read-out circuits.

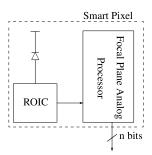

By contrast, in current-mode signal processing, the signal swing is not affected by such trends. Also, current-mode circuits demand less silicon area, have higher operation speed and use simpler building blocks to process the image signal. Moreover, a current-mode read-out approaches, as depicted in Fig. 3, is easily integrated with mixed-signal smart pixels for image processing in analog domain before digitization [14]-[18]. However, the read-out circuit must have high output impedance, aiming at an ideal current controlled source output.

Figure 3: Smart pixel architecture for current mode read-out circuits analog image processing.

The InP-InGaAs infrared sensors have been considered to be potential alternatives to low band gap semiconductor infrared photodetectors such as HgCdTe, which suffers from nonuniformity problems in the long-wavelength infrared band. The InP-InGaAs technology offers long-wavelength infrared arrays at significantly lower cost. A disadvantage of InP-InGaAs for infrared applications is the lack of flexibility in adjusting the peak detection wavelength by changing the barrier/well material composition limiting the peak responsitivity wavelength to a narrow range around 8  $\mu$ m [19]. On the other hand, an InGaAs photodiode can be easily modeled as a Si photodiode, and the read-out circuits implemented in CMOS technology can be redesigned in a hybrid CMOS-InGaAs implementation [20], where the photodiodes are integrated in InGaAs technology and the read-out CMOS circuits are flip-chip Indium bond connected to the sensors.

This work proposes a new design approach for current amplifier implementation for read-out circuit purposes. The target application is in hybrid CMOS-InGaAs implementations, using a  $0.35~\mu m$  CMOS technology. The proposed circuit is compared to other competing realizations, considering key performance parameters. Section 2 provides a short review on reported read-out circuits. The proposed current amplifier scheme is presented in Section 3. Results, obtained through theoretical derivation, of noise distortion produced by the proposed circuit are shown in Section 4. Post-layout Spice simulations using BSIM3V3 device model are presented in Section 5, where comparisons are made with alternative realizations. Concluding remarks are made in Section 6.

# 2. REVIEW ON PREVIOUS READ-OUT CIR-CUITS

The majority of the reported read-out circuits are implemented with the three transistors active pixel sensor (APS) topology. They are based on an amplifier scheme (transconductance amplifier for current mode applications), having one switch to reset the pixel light information and another one to select line read-out mode. These topologies, including self-integration, source-follower-per-detector, and direct-injection, are simple and occupy small area, but they are unable to satisfy most of the usual performance requirements [1], [12].

More recently proposed amplifier structures, such as buffereddirect-injection and capacitive feedback transimpedance amplifiers, provide a better performance in terms of injection efficiency and detector bias stability with the help of an in-pixel operational amplifier [12], but their performances are limited by the quality of the operational amplifier that should be implemented in a small pixel area. The buffered gate modulation input approach [11] provides in-pixel detector current amplification and background flux suppression with the integration capacitance placed outside the pixel, but it also requires and operational amplifier for detector bias stabilization purposes. As a result, its performance depends on area and operational amplifier performance. Another interesting approach, called switched current integration [13], provides large charge storage capacity with the use of an off-pixel integration capacitor. However, it requires an in-pixel amplifier that limits its detector bias and injection efficiency performance and affects the pixel area.

The current mirroring direct injection technique [10], satisfies the high injection efficiency and controlled detector bias requirements. But it also requires the integration capacitor to be in the pixel, and therefore has large pixel area, low dynamic range, and low charge storage capacity. A high performance read-out structure called current mirroring integration (CMI) was presented in [9]. The circuit provides high performance without needing an inpixel operational amplifier or integration capacitor, and can be implemented in a small pixel area.

In summary, previous solutions present either low performance with simple structures, or achieve high performance at the cost of large pixel area. Best trade-offs combining high performance with small area was achieved by the CMI structure with a cascode output. However, such circuits do not have large enough output impedance for applications in smart pixel image signal processing (see Figure 3).

#### 3. THE RCCM AMPLIFIER

The InGaAs sensor electric model is a non-ideal current source, whose current is a function of the energy of the incident photon. This function is determined by the photodiode responsitivity. The current amplifier reads the instantaneous light information directly in continuous time.

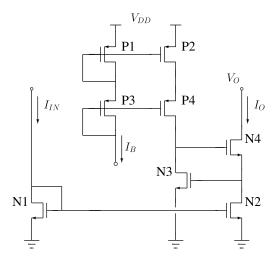

A current mirror can be regarded as a current amplifier, whose gain is controlled by the transistor dimensions. Since these are produced simultaneously during the fabrication process, the gain can be precisely implemented, except for channel-length modulation effects, which are the dominant cause of non-linear distortions in the circuit. the RCCM amplifier's gain, shown in Fig. 4, is given by the equation

$$\frac{I_O}{I_{IN}} = \frac{W_2/L_2}{W_1/L_1} \frac{1 + \lambda V_{DS2}}{1 + \lambda V_{DS1}}.$$

(1)

where  $I_{IN}$  is anode current produced by the photodiode, and  $\lambda$  is termed the channel-length modulation parameter. This equation indicates that channel-length modulation occurs if  $V_{DS1} \neq V_{DS2}$  [21]. By choosing the bias current  $I_B$  as a fraction of  $I_{IN}$ , equal to the scale factor relating the aspect ratios of N1 and N3, then channel-length modulation effects can be considerably reduced, regardless of the load driven by the RCCM.

The circuit was designed to provide a gain  $I_O/I_{IN}=10$ , with  $I_B=0.5~\mu\mathrm{A}$  from DC up to a cutoff frequency of 2 MHz, taking into account the output capacitance of the input current source, that is, the junction capacitance of the photodiode. The design focused on maximum dynamic range (maximum output current swing) with lower area cost, and it achieved the transistors dimensions shown in Table 1.

Figure 4: Schematic diagram of the RCCM amplifier.

Designing N1 and N2 in the saturation region, it should be observed dynamic range trades with harmonic distortion, since  $V_{DS1}$  deviates from  $V_{DS2}$  in large dynamic range applications. Note that  $V_{DS2}$  is fixed at

$$V_{DS2} = \sqrt{\frac{2I_B}{K'_n} \frac{L_3}{W_3}} + V_{Tn}$$

= 0.55 V (2)

whereas

$$V_{DS1} = \sqrt{\frac{2I_{IN}}{K_n'} \frac{L_1}{W_1}} + V_{Tn} \tag{3}$$

varies in the range

$$0.51 \,\mathrm{V} < V_{DS1} < 0.58 \,\mathrm{V}$$

(4)

because the input current  $I_{IN}$  changes with illumination conditions. As a consequence, a current deviation gain of about 2% is produced by Eq. 1. Another constraint in current gain can be observed by

$$V_O \ge \sqrt{\frac{2I_B}{K'_n} \frac{L_3}{W_3}} + \sqrt{\frac{2I_o}{K'_n} \frac{L_4}{W_4}} - V_{Tn},$$

(5)

where lower output signal removes the transistor N4 from the saturation region. The transistor N3 will be always saturated by the bias circuit ( $I_B$ ).

Table 1: Transistor dimensions.

| Tuble 1: 11 unbibtor unitensions. |                |             |  |  |  |

|-----------------------------------|----------------|-------------|--|--|--|

| Transistor                        | $W$ ( $\mu$ m) | $L (\mu m)$ |  |  |  |

| $N_1, N_3$                        | 1.4            | 0.7         |  |  |  |

| $N_2, N_4$                        | 14             | 0.7         |  |  |  |

| $P_1 - P_4$                       | 1.4            | 0.7         |  |  |  |

Other current amplifier schemes, such as the ones shown in [4] and [5], also employ a fixed voltage to bias the transistor that provides  $I_B$ . In theses case, the difference between  $V_{DS1}$  and  $V_{DS2}$  leads to more significant channel-length modulation effects.

## 4. NOISE ANALYSIS

In this section a theoretical noise analysis is developed for the RCCM circuit. To this end each transistor of Fig. 4 is replaced with a noiseless transistor having a current source connected between the drain and the source terminals with noise power  $I_{Ni}^2$  or  $I_{Pi}^2$ , depending on the transistor type.

The analysis gives the total output current noise power

$$I_{n,O}^2 = I_{n,N}^2 + I_{n,P}^2, (6)$$

where

$$I_{n,N}^2 = I_{N2}^2 + I_{N4}^2 + \frac{gm_{N2}^2}{gm_{N1}^2} I_{N1}^2 + \frac{gm_{N4}^2 r_{o3}^2 I_{N3}^2}{r_{o2} (gm_{N4} + 1/r_{o4}) + 1}$$

(7)

is the noise power produced by the transistors N1-N4, and

$$I_{n,P}^{2} = \frac{gm_{N4}^{2} r_{o3}^{2}}{r_{o2} (gm_{N4} + 1/r_{o4}) + 1} \left( I_{P2}^{2} + I_{P4}^{2} + \frac{gm_{P2}^{2}}{gm_{P1}^{2}} I_{P1}^{2} + \frac{gm_{P3}^{2}}{gm_{P3}^{2}} I_{P3}^{2} \right)$$

$$(8)$$

is the noise produced by the transistors P1-P4, of the bias circuit.

Since the RCCM gain has a dominant pole at 2 MHz, its noise frequency band is  $\pi$  MHz [22]. The theoretical analysis gives  $I_{n,N}=4.27$  nA RMS,  $I_{n,P}=0.69$  nA RMS, and hence the output noise is  $I_{n,O}=4.33$  nA RMS, integrated in the noise frequency band.

#### 5. POST-LAYOUT SIMULATION RESULTS

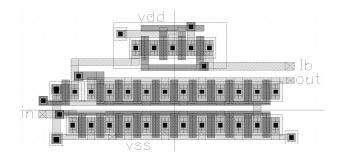

With an area of  $273 \mu m^2$ , the layout of the RCCM circuit is displayed in Fig. 5. Post-layout simulations have been carried out for the proposed RCCM circuit. Some key results are compared with those reported by other approaches, namely, the CMI in [9] and the 3T current mode APS in [1].

Figure 5: Layout of the RCCM circuit.

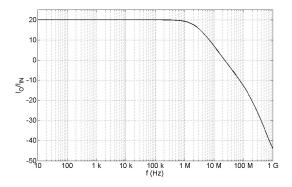

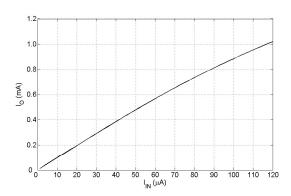

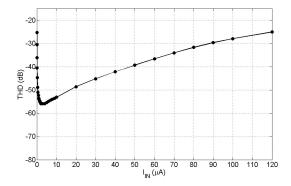

As presented in Fig. 6, the frequency response shows a cut-off frequency of 2.3 MHz with a current gain  $I_O/I_{IN}=20$  dB. These results agree closely with the theory. Another important parameter is depicted in Fig. 7, in which the RCCM input is a DC current that is swept from 8 nA up to  $120~\mu$ A. As can be observed, the output practically deviates from the linear relationship as the current increases beyond about  $50~\mu$ A. As predicted in Section 3, the increasing non-linearity is mainly caused by channel-length modulation. The total harmonic distortion (THD), as a function of the input current, is plotted in Fig. 8. The THD is smaller than -40~dB THD for input currents in the range from 50~nA up to  $50~\mu$ A.

The output noise was computed and integrated in the passband, yielding 4.86 nA RMS, which is close to the theoretical estimate, if one recalls that the simulated frequency band is about 15% larger than the theoretical one. Since the maximum input current is  $50\,\mu\text{A}$  for a THD of -40 dB, the signal-to-noise ratio is 77.2 dB. The

Figure 6: Frequency response.

Figure 7: DC signal range.

dynamic range, defined as the ratio of the maximum and minimum inputs such that the THD is smaller than -40 dB, is 60 dB. The measured output impedance is  $236 \ k\Omega$ , and the input impedance is evaluated as  $25 \ k\Omega$  for the maximum signal swing. The injection efficiency calculated with this input impedance is 73%.

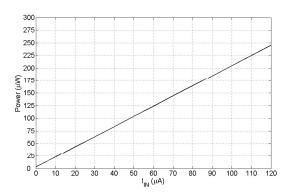

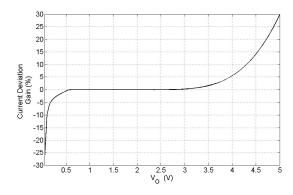

The power consumption was evaluated against the DC signal range, and is shown in Fig. 9. Variations in the output voltage produce gain deviations if the bounds defined by Eq. 5 are not satisfied. Such deviations, as a function of the output voltage, are shown in Fig. 10. It has been observed that for output voltages in the range from  $0.45~\mathrm{V}$  up to  $3.35~\mathrm{V}$ , the current gain error is smaller than 1%.

Table 2 summarizes and compares the performance of the RCCM circuit with the CMI presented in [9] and the two 3T current mode APS approaches reported in [1]. It can be seen that the RCCM outperforms the other approaches in most of the parameters. In addition, the RCCM amplifier presented larger signal-to-noise ratio and dynamic range, with lower area than that of the CMI circuit. The 3T current mode APS circuits [1] have smaller area, but their small output impedance, owing to the single output transistor, make them inviable for smart pixel processing application, such as shown in see Fig. 3.

### 6. CONCLUSIONS

This paper proposed the implementation of a current amplifier for photodiode read-out. The circuit was designed in a  $0.35\,\mu\mathrm{m}$  CMOS, for application in hybrid CMOS-InGaAs technologies. Notwithstanding, the regulated cascode current mirror can be designed in

Figure 8: Harmonic distortion analysis.

Figure 9: Power consumption.

moderate or weak inversion. This design allows a trade-off between high output impedance and high output range; this trade-off can be used to choose current-mode amplifiers for specific low-voltage applications.

The regulated cascode current mirror, developed in this work, achieved a better balance between high performance requirements, low area cost, high signal-to-noise ratio, and high dynamic range. Post-layout simulation results agreed with the theoretical predictions. Comparisons were made with other approaches. The proposed circuit seems to be a good choice for mixed-signal smart pixels for image processing in analog domain applications.

#### 7. REFERENCES

- [1] R. M. Phillipp et al., "Linear current-mode active pixel sensor," *IEEE J. Solid-State Circuits*, vol. 42, no. 11, pp. 2482–2491, November 2007.

- [2] D. Stoppa et al., "A 120-dB dynamic range CMOS image sensor with programmable power responsivity," *IEEE J. Solid-State Circuits*, vol. 42, no. 7, pp. 1555–1563, July 2007.

- [3] X. Wang, W. Wong, and R. Hornsey, "A high dynamic range CMOS image sensor with inpixel light-to-frequency conversion," *IEEE Trans. Electron Devices*, vol. 53, no. 12, pp. 2988–2992, December 2006.

- [4] M. Tänzer, A. Graupner, and R. Schüffny, "Design and evaluation of currente-mode image sensor in CMOS-technology," *IEEE Trans. Circuits Syst. II*, vol. 51, no. 10, pp. 566–570, October 2004.

- [5] Y. Huang and R. I. Hornsey, "Current-mode CMOS image sensor using lateral bipolar phototransistors," *IEEE Trans.*

Table 2: Performance summary of the RCCM approach and comparisons with other approaches.

|                         | [9]                     | [1]                           | [1]                           | This Work                |

|-------------------------|-------------------------|-------------------------------|-------------------------------|--------------------------|

| Technology              | $0.8\mu\mathrm{m}$ CMOS | $0.35\mu\mathrm{m}$ CMOS      | $0.18\mu\mathrm{m}$ CMOS      | $0.35 \mu \text{m CMOS}$ |

| Area $(\mu \text{m}^2)$ | 500                     | 100                           | 100                           | 273                      |

| $R_O$                   | $gmr_{ds}^2$            | $\frac{r_{ds}}{(1+gmr_{ds})}$ | $\frac{r_{ds}}{(1+gmr_{ds})}$ | $gm^2r_{ds}^3$           |

| SNR (dB)                | N/A                     | 42                            | 39                            | 77                       |

| DR (dB)                 | 20                      | 64                            | 53                            | 60                       |

Figure 10: Simulated output voltage according the gain error.

- *Electron Devices*, vol. 50, no. 12, pp. 2570–2573, December 2003.

- [6] D. Y. H. Cheung, "CMOS active pixel sensor designs for fault tolerance and background illumination subtraction," Master's thesis, B.A.Sc. Simon Fraser University, 2002.

- [7] H. Tian, B. Fowler, and A. E. Gamal, "Analysis of temporal noise in CMOS photodiode active pixel sensor," *IEEE J. Solid-State Circuits*, vol. 36, no. 1, pp. 92–101, January 2001.

- [8] K. Guo and et al, "1d InGaAs lock-in FPA," in *Infrared Technology and Applications XXX. Edited by Andresen, Bjorn F., and Fulop, Gabor F. Proceedings of the SPIE*, ser. Presented at the Society of Photo-Optical Instrumentation Engineers (SPIE) Conference, vol. 5406, pp. 64–72, August 2004.

- [9] H. Kulah and T. Akin, "A current mirroring integration based readout circuit for high performance infrared FPA applications," *IEEE Trans. Circuits Syst. II*, vol. 50, no. 4, April 2003.

- [10] H. C. L. Nanyoung Yoon, Byunghyuk Kim and C.-K. Kim, "High injection efficiency readout circuit for low resistance infra-red detector," *IEEE Eletron. Lett.*, vol. 35, no. 8, pp. 1188–1198, September 1999.

- [11] C.-C. Hsieh et al, "High-performance CMOS buffered gate

- modulation input (BGMI) readout circuits for IR FPA," *IEEE J. Solid-State Circuits*, vol. 33, no. 8, pp. 1188–1198, August 1998.

- [12] C.-C. Hsieh et al., "Focal-plane-arrays and CMOS readout techniques of infrared imaging systems," *IEEE Trans. Circuits Syst. Video Technol*, vol. 7, no. 4, pp. 594–605, August 1997.

- [13] C.-C. Hsieh et al., "A new cryogenic cmos readout structure for infrared focal plane array," *IEEE J. Solid-State Circuits*, vol. 32, no. 8, pp. 1192–1199, August 1997.

- [14] W. D. León-Salas et al., "CMOS imager with focal plane compression using predictive coding," *IEEE J. Solid-State Circuits*, vol. 42, no. 11, pp. 2555–2572, November 2007.

- [15] M. J. C. de Mello, "Sensibilidade de produtos internos à fabricação em circuitos CMOS para quantização vetorial em sistemas de compressão de imagens no plano focal," Master's thesis, Universidade Federal do Rio de Janeiro, 2007.

- [16] N. Massari and M. Gottardi, "A 100 dB dynamic-range CMOS vision sensor with programmable image processing and global feature extraction," *IEEE J. Solid-State Circuits*, vol. 42, no. 3, pp. 647–657, March 2007.

- [17] H. L. Hass et al, "New error sensitivity model for the analog hardware implementation of inner products," in *Proc. IEEE International Conference on Image Processing*, pp. 3333–3336, October 2006.

- [18] J. L. Huertas et al, "Smart-pixel cellular neural networks in analog current-mode CMOS technology," *IEEE J. Solid-State Circuits*, vol. 29, no. 8, p. 895Ű-905, August 1994.

- [19] S. Ozer et al, "Demonstration and performance assessment of large format InP-InGaAsP quantum-well infrared photodetector focal plane array," *IEEE J. Quantum Electron.*, vol. 43, no. 8, pp. 709–713, August 2007.

- [20] M. Sun and Y. Lu, "Nonlinearity in ESD robust InGaAs P-I-N photodiode," *IEEE Trans. Electron Devices*, vol. 52, no. 7, pp. 1508–1513, July 2005.

- [21] D. Jonhs and K. Martin, *Analog integrated circuit design*. John Wiley & Sons, 1997.

- [22] B. Razavi, *Design of analog CMOS integrated circuits*. McGraw-Hill, 2001.