## Electromechanical Adiabatic Computing: Towards Attojoule Operation

Yann Perrin, Ayrat Galisultanov, Hervé Fanet, Gaël Pillonnet

#### ▶ To cite this version:

Yann Perrin, Ayrat Galisultanov, Hervé Fanet, Gaël Pillonnet. Electromechanical Adiabatic Computing: Towards Attojoule Operation. 2017 IEEE International Conference on Rebooting Computing (ICRC), Nov 2017, Washington, United States. 10.1109/ICRC.2017.8123660. hal-01887177

HAL Id: hal-01887177

https://hal.science/hal-01887177

Submitted on 3 Oct 2018

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Electromechanical adiabatic computing: towards attojoule operation

Yann Perrin, Ayrat Galisultanov, Hervé Fanet, Gaël Pillonnet Univ. Grenoble Alpes, CEA LETI, F-38000 Grenoble

Abstract-Considerable efforts have been devoted to the design of low-power digital electronics. However, after decades of improvements and maturation, CMOS technology could face an efficiency ceiling. This is due to the trade-off between leakage and conduction losses inherent to transistors. Consequently, the lowest dissipation per operation remains nowadays few decades higher than the theoretical Landauer's limit (3 zJ at 300 K). Adiabatic CMOS architectures are good candidates for reducing the dynamic losses. But adiabatic operation reduces operating frequency, thus exacerbating the leakage loss. Consequently, transistors could not be the appropriate support for adiabatic logic. In this paper, we bring in a new paradigm for computation. The elementary device which replaces transistor is based on coupled moving masses suspended by springs. Such objects can be fabricated with MEMS in order to provide a relatively high computing speed (in the order of 1 MHz for a micrometerscaled device). In this paradigm, the logic states are encoded mechanically instead of electrically. The computation is performed by means of electrostatic interactions between the moving elements. We show how they can be arranged in order to create combinational logic gates that can be cascaded. Information is injected and extracted electrically, thus allowing compatibility with conventional circuits. We estimate resistive and damping dissipation of the system via electromechanical simulations, for the case of an AND gate. When the gate is driven adiabatically. the energy per operation drops in the range of the attojoule, even with a micrometer-scaled elementary device. This dissipation almost vanishes for lower frequencies of operation. This suggests that electromechanical adiabatic computing (EMAC) could be able to approach Landauer's limit. EMAC could be valuable for devices operating under high energy constrains with low computing power requirements, such as future massively spread environmental sensors.

#### I. INTRODUCTION

Over the last decades, considerable efforts have been devoted to the design of low power electronics. The power consumption of conventional CMOS devices arises from three main contributions [1]: switching dissipation, direct-path short-circuit current (dynamic) and leakage current (static). Switching dissipation occurs at each transition between logic states, as it involves to charge or discharge abruptly a capacitance  $C_L$  from 0 to the supply voltage  $V_{dd}$  (or vice versa). This process leads to an unavoidable energy dissipation about  $\frac{1}{2}C_LV_{dd}^2$  [2]. Most of the load capacitance results from transistors gates and interconnecting wires. Direct-path short-circuit current happens when PMOS and NMOS are simultaneously "on" during a transition. And nowadays, leakage current arises essentially from sub-threshold conduction and tunnelling through the gate dielectric.

Numerous approaches seeking for more energy-efficient MOSFET transistors are explored, such as multigate transistors [3] or FDSOI technology [4], amongst others. On the other hand, the energy efficiency of a circuit can be optimised by using appropriate architectures and power management solutions, e.g. sub-threshold circuits [5], asynchronous logic [6] or adiabatic logic [7]–[9]. Despite this, the minimal dissipated energy per operation (in the order of  $10^4\ k_BT$  [10]) remains far beyond the theoretical limit  $k_BT \ln 2$  introduced by Landauer [11].

In adiabatic logic, dynamic dissipation is reduced by avoiding abrupt charging of  $C_L$ , i.e. by using smooth transition between logic states. Furthermore, the energy contained in the circuit must be recycled at each cycle. This can be achieved by using a clock signal (which is also the power supply) provided by a capacitive or inductive generator [12], [13]. When operated adiabatically, the dissipation of the circuit must be proportional to its operating frequency. Therefore, the energy per operation might be lowered at will, but at the expense of the speed of computation. However, when implemented with MOSFET transistors, adiabatic operation exacerbates the leakage dissipation. In addition, the non linearity inherent to transistors prevents the system to evolve strictly adiabatically [8]. Therefore, the transistor is probably not the best candidate for building an adiabatic circuit.

A more recent approach consists in replacing transistors by MEMS relays, since they does not suffer from current leakage [14], [15]. However, they show an high contact resistance and reliability issues [16]. This suggests that, although the use of MEMS devices might be a promising approach, mechanical and electrical contact must be avoided. To this purpose, we recently demonstrate the possibility to implement an adiabatic logic circuit with comb-drive actuators [17], [18]. Indeed, comb-drive behaves as a voltage-controlled capacitance, which could realise combinational functions. The main drawback of this Capacitive-based Adiabatic Logic (CAL) is that the computing capacitances have to be greater than the parasitic capacitances of the wires. This leads to large devices, in the millimeter scale. In addition, the moving comb must be divided in two insulated parts.

In this paper, we propose a different approach which overcomes these difficulties. As in CAL, the computation is performed via comb-drive actuators. But information is encoded and transmitted from gate to gate by means of a mechanical displacement, instead of voltages levels. We also show how the information of electrical inputs can be processed mechanically

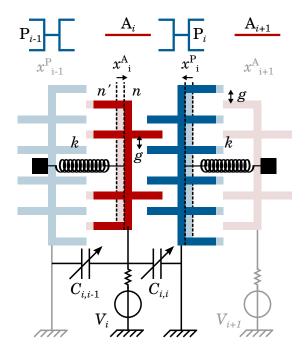

Fig. 1. Schematics of the electromechanical system considered here. It shows two combs in electrostatic influence. As they are free to move along  $\boldsymbol{x}$  (horizontal) direction, they form a variable capacitor. Combs in light colours (on both sides) will be considered further. The top symbols are the simplified diagram of this system, which will be used in the next section.

with comb-drives, and that the output can be converted into an electrical signal. This ensure a full compatibility of EMAC with other logic families.

### II. PRINCIPLE OF ELECTROMECHANICAL ADIABATIC COMPUTING

#### A. Elementary device

We consider the elementary device depicted in Figure 1. It contains two moving parts  $A_i$  and  $P_i$ , each carrying a mass m, and suspended by springs with a total stiffness k. We assume that they move only along the horizontal axis. These two parts are shaped like combs and are coupled through n interdigitated fingers. The right comb  $P_i$  (in blue) is grounded and is reffered to as "passive" comb. The left comb  $A_i$  (in red) is connected to a voltage source with an electric potential  $V_i$ , and is reffered to as "active" comb.  $V_i(t)$  ranges from 0 to the supply voltage of the circuit  $V_{dd}$ .

The comb structure ensures a strong electrostatic coupling. For this reason, it is wildly used for MEMS devices; this is called "comb-drive actuator" [19]. Comb-drive actuators have a mobile and an anchored comb. However, in our case both combs are free to move when a voltage  $V_i$  is applied. Their relative positions are labelled as  $\tilde{x}_i^A$  and  $\tilde{x}_i^P$ . We now need to express the electrostatic force acting on the combs. In this paper, we consider a comb-drive model based on the approximation of infinite plane capacitor. Although it neglects the fringing electric field, this approximation is commonly used in the literature. More accurate approximations, including fringing field effects, have also been investigated [20]–[22].

We consider that the capacitance  $\tilde{C}_{i,i}$  between  $A_i$  and  $P_i$  is given by:

$$\tilde{C}_{i,i} = \frac{2nt\epsilon_0(\tilde{x}_i^A - \tilde{x}_i^P)}{q} H(\tilde{x}_i^A - \tilde{x}_i^P) \tag{1}$$

where g, n, t and  $\epsilon_0$  correspond to the gap between the fingers of opposite combs (cf. Fig. 1), the number of fingers, their thickness and the vacuum permittivity. H(x) refers to the Heaviside step function, which equals 0 if x < 0 or 1 if  $x \ge 0$ .

Applying a voltage  $V_{Ci}$  between  $A_i$  and  $P_i$  creates an attractive electrostatic force  $\tilde{F}_{i,i}$ . This force can be calculated by differentiating the electrostatic energy  $E_{i,i}$  with respect to the overlap between the combs:

$$\tilde{F}_{i,i} = \frac{\partial E_{i,i}}{\partial x} = \frac{nt\epsilon_0}{g} \tilde{V}_{Ci}^2 H(\tilde{x}_i^A - \tilde{x}_i^P)$$

(2)

By design, there is no overlap between the combs in the state  $\tilde{x}_i^A = \tilde{x}_i^P = 0$ . As a consequence of (1) and (2), the capacitance vanishes but an electrostatic force arises when a voltage is applied. This force causes the displacement of the combs. As it is always attractive,  $A_i$  moves to the right  $(\tilde{x}_i^A > 0)$  and  $P_i$  to the left  $(\tilde{x}_i^P < 0)$ . The springs then lead to restoring forces which tends to bring the combs back to their initial positions  $\tilde{x}_i^A = \tilde{x}_i^P = 0$ . At the equilibrium position, electrostatic and spring forces compensate. The equilibrium positions write:

$$\tilde{x}_i^{Aeq} = -\tilde{x}_i^{Peq} = \frac{\tilde{F}_{i,i}}{k} \tag{3}$$

#### B. Reduced units

In order to clarify the expressions and to reduce the number of free parameters, we choose a specific set of units from now on. The lengths are expressed with respect to the space between the combs g. Capacitances are normalised by the capacitance unit  $C_0$  below:

$$C_0 = nt\epsilon_0$$

Similarly, forces, voltages and time are normalised respectively by:

$$F_0 = kg$$

$$V_0 = \sqrt{\frac{kg^2}{nt\epsilon_0}}$$

$$T_0 = \sqrt{\frac{m}{k}}$$

In order to distinguish the normalised quantities from those in SI units, the normalised quantities are written without the wavy line. In our set of units, equations (1), (2) and (3) become dimensionless:

$$C_{i,i} = 2(x_i^A - x_i^P)H(x_i^A - x_i^P)$$

(4)

$$F_{i,i} = V_{Ci}^2 H(x_i^A - x_i^P)$$

(5)

$$x_i^{Aeq} = -x_i^{Peq} = V_i^2 \tag{6}$$

In the following, we show how comb-drive actuators can be assembled in order to create structures that are able to transfer and process information.

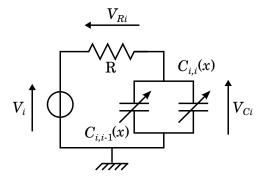

Fig. 2. Electric diagram associated to a pair of combs. The resistor R represents the resistance of the wire connecting the voltage source with the comb A:

#### C. Synchronous pipeline

$A_i$  and  $P_i$  are now part of a larger system composed of N pairs of combs in interaction. Their first neighbours are depicted in light colours in Figure 1. The 2N combs are arranged along a chain in such a way that each pair i is coupled with pairs i-1 and i+1 (except for the edges i=0 and i=N). Figure 2 depicts the equivalent electric diagram of  $A_i$ . The voltage source  $V_i$  is connected to two capacitances:

- $C_{i,i}$  is the capacitance between  $A_i$  and  $P_i$

- $C_{i,i-1}$  is the capacitance between  $A_i$  and  $P_{i-1}$

Consequently, two opposite forces act on  $A_i$ . Therefore,  $A_i$  cannot move if the combs are symmetrical. For this reason, an asymmetry is designed to make the coupling between  $A_i$  and  $P_i$  weaker than between  $A_i$  and  $P_{i-1}$ . This can be achieved by adjusting the numbers of fingers n and n' depicted in Fig. 1 (in this Figure, n=2 and n'=4 so n'>n).

In this section, we assume that the system is driven by the voltage sources with a timescale infinitely greater than the mechanical relaxation time. This assumption allows to ignore the dynamic mechanical effects, in a first step. It also allows to neglect the electrical currents and to consider that the voltages across the capacitances are equal to the voltages applied by the voltage sources, i.e.  $V_{Ci} = V_i$ .

Under these assumptions, we calculate the electrostatic forces within the chain of comb-drives. Previous expressions of equilibrium positions (6) were derived for an isolated pair of combs. But the first neighbours couplings now must be considered. To do so, we express the total electrostatic forces  $F_i^A$  and  $F_i^P$  that acts on  $A_i$  and  $P_i$  using eq. (5).

$$F_i^A = -F_{i-1,i} + F_{i,i}$$

$$F_i^P = -F_{i,i} + F_{i,i+1}$$

(7)

After replacing the forces by their expressions,  $F_i^P$  and  $F_i^A$  become:

$$F_i^A = -\alpha V_i^2 H(x_{i-1}^P - x_i^A) + V_i^2 H(x_i^A - x_i^P)$$

$$F_i^P = -V_i^2 H(x_i^A - x_i^P) + \alpha V_{i+1}^2 H(x_i^P - x_{i+1}^A)$$

(8)

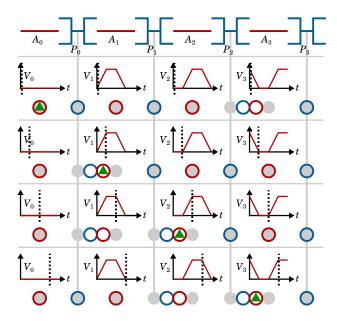

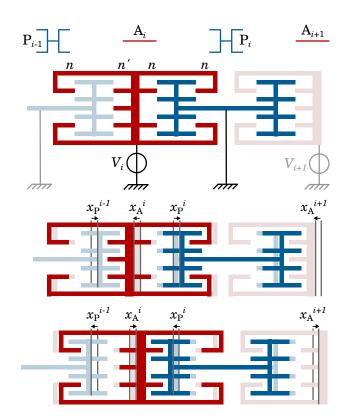

Fig. 3. Sketch of four cascaded buffer gates (top) and their states at specific times, from top to down: t=0,  $t=0.25\ T$ ,  $t=0.5\ T$  and  $t=0.75\ T$ . The four power supplies are driven according to eq. (10). The grey rounds indicate the positions  $x_i^A=x_i^P=0$ . Blue and red circles depict the positions of active and passive combs at the time t. The green rectangle indicates the position of the information sent at time t=0, which corresponds to a logic state "1".

where  $\alpha = \frac{n'}{n}$  refers to the ratio between the numbers of fingers n' and n ( $\alpha > 1$ ). The equilibrium positions can be deduced from these forces:

$$x_i^{Aeq} = V_i^2 \left[ H(x_i^A - x_i^P) - \alpha H(x_{i-1}^P - x_i^A) \right]$$

$$x_i^{Peq} = -V_i^2 H(x_i^A - x_i^P) + \alpha V_{i+1}^2 H(x_i^P - x_{i+1}^A)$$

(9)

If all the power supplies  $V_i$  are set to an high state, e.g.  $V_i = V_{dd} \ \forall i \in [0;N]$ , all the active combs move towards the left  $(x_i^A < 0)$ . Obviously, passive combs move towards the right  $(x_i^P > 0)$ . A last but not least ingredient must be added here, in order to induce an oriented propagation. The power supplies must be driven sequentially by a four phases power clock, with a period of time T. These trapezoidal shaped signals are depicted in Figure 8. Applied voltages must satisfy the following relation:

$$V_{i}(t) = V_{i-1}(t - \frac{T}{4})$$

(10)

Therefore, the mechanical propagation is oriented by introducing a phase shift about  $\frac{\pi}{2}$  between adjacent voltage sources. The input electric signal is sent in the first comb-drive  $A_0$ , and is denoted as  $V_0$ . For transmitting a logic state "1", this voltage must satisfy eq. (10), meaning that it is synchronised with the power clocks. For transmitting a logic state "0",  $V_0$  must be grounded. In the following, we describe the sequential behaviour of the system for both logic states.

Fig. 4. Sketch of the system depicted in Figure 3 when the input voltage  $V_0$  is grounded. The chain show the opposite behaviour, with active and passive comb moving towards the left and the right, respectively. This case corresponds to the transmission of a logic state "0".

1) State "1": Figure 4 depicts the propagation of a state "1" through the chain, at different times:

- At time t=0 (first row), we assume an initial state where  $V_0$  is in an high level state and  $V_1=0$ . Therefore,  $F_0^P<0$  and  $P_0$  moves towards  $A_0$ . We point out that at t=0,  $V_3$  is also in an high state. Consequently,  $P_2$  and  $A_3$  collapse. This event is not an issue since the information (located in  $A_0$ ) had not yet had sufficient time to travel through the chain.

- At time  $t=\frac{1}{4}T$  (second row),  $V_0$  and  $V_1$  are in an high state. As  $P_0$  is shifted on the left  $(x_0^P=-V_0^2)$ , no electrostatic force arise between  $P_0$  and  $A_1$ . Consequently,  $A_1$  is only attracted by  $P_1$  and moves towards the right. Therefore,  $x_1^A=V_1^2$  and  $x_1^P=-V_1^2$ . Information is now located in  $A_1$ .

- The same process occurs at time  $t = \frac{1}{2}T$  and  $\frac{3}{4}T$ , leading to the propagation of the information through the chain.

- 2) State "0": We now consider the opposite case where the first voltage source is inhibited, i.e.  $V_0=0 \ \forall t\geq 0$ . Figure 4 shows how information propagates through the system. As  $V_0=0$ , the force between  $A_0$  and  $P_0$  vanishes so that  $P_0$  is only attracted by  $A_1$ . When  $V_1$  reaches the high state at  $t=\frac{1}{4}T$ , two opposite forces act on  $A_1$ . As  $\alpha>1$ ,  $A_1$  moves preferably towards the left. This motion inhibits the force between  $A_1$  and  $P_1$ . Consequently,  $x_0^P=\alpha V_1^2$  and  $x_1^A=-\alpha V_1^2$ . On the other hand,  $P_1$  remains in the position  $x_1^P=0$ . During the following steps, the same process occurs until the information reaches the last element.

The two cases depicted above (cf. Fig. 3 and 4) can be regarded as an example of transmission of two distinct logic states. The state "1" is associated to a displacement of active combs toward the right, and passive combs toward the left.

The state "0" implies the opposite behaviour. Because the logic state is maintained during its propagation, the chain can be regarded as a cascade of four buffer gates forming a synchronous pipeline.

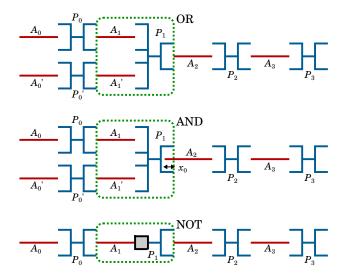

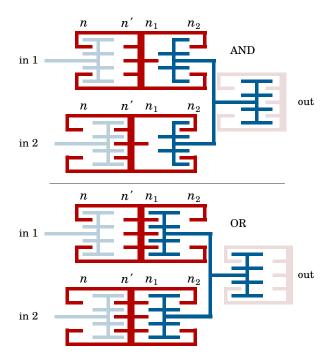

#### D. Examples of OR, AND and NOT gates

An OR gate with two inputs can easily be deduced from the previous design. To do so, one can design a comb coupled with two neighbours on the left, and one on the right. Figure 5 depicts an implementation of such OR gate, were the logic function is performed by  $P_1$ . In this circuit,  $P_1$  can be attracted and brought in a "1" state by  $A_1$  or  $A_1'$ . But if both inputs are in a "0" state,  $P_2$  is only attracted by  $A_2$  and a "0" state is transmitted.

Only few geometrical changes are required in order to create an AND gate from the OR gate. This can be achieved by introducing an initial overlap between  $P_1$  and  $A_2$ , denoted  $x_0$  (cf. Fig. 5). With this design, when  $x_1^P = x_2^A = 0$ , the overlap between  $P_1$  and  $A_2$  equals  $x_0$ . Let us now determine the values of  $x_0$  which lead to an AND gate. At time t = 0.5T,  $V_1 = V_{dd}$  and  $V_2 = 0$ . The total electrostatic force applied on  $P_1$  then writes:

$$F_1^P(t=0.5T) = -V_{dd}^2 \left( H(x_1^A - x_1^P) + H(x_1^{A'} - x_1^P) \right)$$

Depending on the inputs,  $P_1$  can access to three positions: 0 (case of "00" inputs),  $-V_{dd}^2$  (case of "01" or "10" inputs) or  $-2V_{dd}^2$  (case of "11" inputs). Afterwards,  $V_4$  starts to rise (t>0.5T) and three cases must be considered:

- $0 \le x_0 < V_{dd}$ : Only one input  $(A_1 \text{ or } A_1')$  is required to disengage  $P_1$  from  $A_2$ , which then collapses with  $P_2$ . This corresponds to a "1" logic state, so the gate is an OR gate.

- $V_{dd} < x_0 < 2V_{dd}$ : As both input  $(A_1 \text{ and } A_1')$  are required to disengage  $P_1$  from  $A_2$ , the gate behaves as an AND gate.

- $x_0 > 2V_{dd}$ : No matter the states of  $A_1$  and  $A'_1$  are, there is always an overlap between  $P_1$  and  $A_2$ . The gate always pass a "0" state, regardless of the inputs.

Hence, two different logic gates can be achieved only by adjusting  $x_0$ .

To illustrate the versatility of EMAC, we now examine the case of an inverter (NOT) gate. An inverter can be obtained by the addition of a mechanical link between two adjacent P and A combs ( $A_1$  and  $P_1$  in Fig. 5). The link holds the condition  $x_1^A = x_1^P$ . As it must not create an electric contact between the combs, the link must be insulating. Such particular MEMS devices have been discussed in earlier works on capacitive adiabatic logic [17], [18]. In addition, the possibility of creating a insulating mechanical link on a comb-drive device has been demonstrated [23]. The drawback of this approach comes from the complexity of the fabrication process to create this insulating link. To overcome this issue, an electrostatic link could be achieved using a specific type of comb-drive actuators; this will be the subject of a separate study.

Fig. 5. Schematics depicting a possible layout for an electromechanical OR (top), AND (middle) or NOT gates (bottom). These functions are achieved by the pair of combs surrounded in dashed green. Gates are surrounded by buffers in order to show how to connect them. The grey square in the NOT gate stands for a insulating mechanical link between  $A_1$  and  $P_1$ .

#### III. DYNAMICAL SIMULATIONS

In this section, the dynamical features of the system (e.g. inertia, damping, currents) are no longer neglected. Using the reduced set of units presented above, the differential equation describing the mechanical motion of a comb i writes:

$$\frac{\partial^2}{\partial t^2} x_i + \frac{1}{Q} \frac{\partial}{\partial t} x_i + x_i + F_i(t) = 0 \tag{11}$$

where  $F_i$  refers to the total electrostatic force, and Q to the mechanical quality factor. Electrical features must also be considered. The current  $i_i$  provided by the voltage source  $V_i$  is given by:

$$i_i = \frac{1}{R} \left[ \frac{q_i(t)}{C_i(t)} - V_i(t) \right]$$

(12)

where  $C_i$  is the equivalent capacitance of the comb-drive  $A_i$  (cf. Fig. 2).

$$C_i = C_{i,i} + C_{i,i+1}$$

The quantity  $q_i$  refers to the amount of electric charges stored in the equivalent capacitor  $C_i$ . Assuming that all the capacitors are discharged at time t=0,  $q_i$  can be calculated by integrating the current over the time:

$$q_i(t) = \int_0^t i_i \mathrm{d}t$$

Note that the differential equation of the RC circuit in Figure 2 cannot be established, since  $C_i$  varies over the time.

Equations (11) and (12) need to be solved for each pair of combs in order to describe the dynamic of the system. In the following, we do so numerically for the circuit with an AND gate pictured in Figure 5.

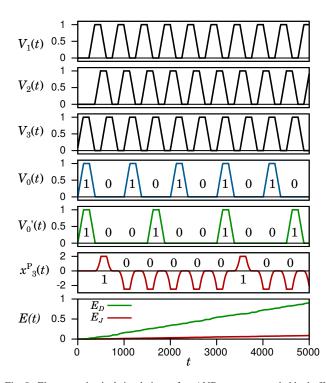

Fig. 6. Top: Representation of the complementary comb-drives employed for the simulations below. Middle: configuration corresponding to a "0" logic state, where  $A_i$  shifts on the left and  $P_i$  on the right. Down: configuration corresponding to a "1" logic state, where  $A_i$  shifts on the right and  $P_i$  on the left.

#### A. Complementary comb-drives

In dynamical simulations, the simple comb-drive model considered above (cf. eq. (1) and (2)) cannot provide a stable behaviour. The main issue arises from the fact that each active comb tends to attract the two neighbouring passive combs simultaneously, instead of only one of them. Consequently, logic states "1" are switched in states "0" by mistake. Furthermore, an electrostatic force also exists when there is no overlap between the combs, due to the stray electric field. This parasitic force affects the proper functioning of the system. To overcome this limitation, we use more complex comb-drives with the geometry depicted in Figure 6. For a pair of combs i, capacitance and electrostatic force become:

$$C_{i,i} = 2(x_i^A - x_i^P) \left(\alpha - (\alpha + 1)H(x_i^P - x_i^A)\right)$$

(13)

$$F_{i,i} = \left(\alpha - (\alpha + 1)H(x_i^P - x_i^A)\right)V_i^2 \tag{14}$$

In this complementary geometry, repulsive  $(F_{i,i} < 0)$  or attractive  $(F_{i,i} > 0)$  forces can exist depending on the positions  $x_i^A$  and  $x_i^P$ . This is rather different than the case of the simple combs in Figure 1, where only attractive or zero force exists. The benefit of this structure comes from the fact that  $A_i$  is able to hold both  $P_{i-1}$  and  $P_i$  during all the power clock pulse  $V_i$ . This is verified for both logic states "0" and "1" (cf. Fig. 6). This is in strong contrast with the initial case,

Fig. 7. Representation of an AND gate (top) and an OR gate (bottom), for inputs in a configuration "1-0". The AND gate shows an output "0" whereas the OR gate shows an output "1". These gates differ simply by the ratio of fingers  $n_1$  and  $n_2$  ( $\frac{n_1}{n2} < 1$  for the AND gate,  $\frac{n_1}{n2} > 1$  for the OR gate).

where  $A_i$  can only hold  $P_{i-1}$  for a "0" state, or  $P_i$  for a "1" state.

#### B. AND gate

In order to create an AND gate, two active combs (corresponding to the inputs) must be placed in the vicinity of a passive comb, as depicted in Figure 5. The input signals correspond to voltages  $V_0$  and  $V'_0$  applied to  $A_0$  and  $A'_0$ . We remind that they need to be synchronised with the power clocks signals. Figure 8 presents the results of dynamical simulations performed on the circuit with the AND gate in Fig. 5, using complementary comb-drives. The output signal is recovered in the position of the last comb-drive  $x_3^P$ . Note that the output signal could also be recovered in  $A_2$ ,  $P_2$  or  $A_3$ . We emphasise that this signal is not affected by the number of buffers gates positioned after and before the gate. However, each gate introduces a delay about  $\frac{1}{4}T$ , where T is the driving period of time. Consequently, in this circuit the output is delayed by  $\frac{3}{4}T$  with respect to the inputs signal. The graphs in Figure 8 show that the output signal  $x_3^A$  is positive when both inputs  $V_0(t)$  and  $V_1(t)$  are simultaneously high, and negative otherwise. Therefore, this circuits behaves as an AND gate.

We now discuss the values of the free parameters used for this simulation:

•  $\alpha$ : In order to have a motion for inputs in "0" state, an asymmetry is required. Thus, we chose  $\alpha = \frac{n'}{n} = 1.2$ , but this parameter is not critical. In order to transmit a "0" state, we only need to have  $\alpha > 1$ . If fringing field effects are neglected, there is no upper limit on  $\alpha$ , as

Fig. 8. Electromechanical simulations of an AND gate, surrounded by buffers. The physical quantities are dimensionless, since a reduced set of units has been employed.

- the force vanishes for negative combs overlaps. However, considering the fringing fields leads to an upper limit on  $\alpha$ , over which "1" state are converted in "0" states.

- R: This resistor is depicted in Figure 2 and models the interconnections between the power clocks and the electromechanical device. Its value only affects the energy dissipation of the system, which will be discussed in the next paragraph. For these simulations, R was set to 10<sup>-4</sup>, corresponding to few megaohms in SI units (see §III-D).

- T: The time period of the signals is critical. It T is too small, the mechanical system cannot respond to the electrical excitation. Consequently, only a weak motion occurs. In our case, the system works properly from  $T \geq 400$ . The graph in Figure 8 was obtained for T = 500.

- Q: The quality factor of comb-drive actuators ranges from 3 to 200 depending on many factors (design, material, pressure, frequency...) [23], [24]. Here, Q was set to 10, although the circuit works for Q ranging from 0.3 to 20. Higher Q requires greater T in order for the circuit to work properly.

The energetic aspects of the problem are discussed below.

#### C. Power dissipation

Earlier works suggests that logical operations could be performed on a micro-electromechanical cantilever with an amount of energy in the same order than the Landauer limit [25]. This question is addressed here in the case of EMAC. With the model presented above, the power provided by the

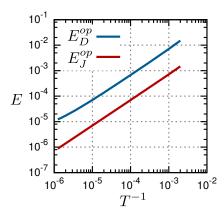

Fig. 9. Dissipation per operation caused by mechanical damping and Joule effect, with respect to the operating frequency, for the circuit with the AND gate.

voltages sources  $V_i$  (inputs and power clocks) is dissipated only by mechanical damping and Joule effect. Damping within the springs is then neglected. The instantaneous dissipated energies  $E_D(t)$  and  $E_I(t)$  write:

$$E_D(t) = \sum_{i=0}^{N} \int_0^t \frac{1}{Q} \frac{\partial x_i}{\partial t} dt$$

$$E_J(t) = \sum_{i=0}^{M} \int_0^t Ri_i^2 dt$$

(15)

where N refers to the total number of combs, and M to the number of active combs only. Figure 8 depicts the evolution of losses during the operation of the AND gate, for a time period about T=500. With the parameters chosen here (Q=10,  $R=10^{-4}$ ), the damping loss is ten times higher than the resistive loss. However, this ratio is not intrinsic to EMAC, but rather fixed by the values chosen for Q and R. Experimentally, these parameters will be determined by the technology used for building the logic gates.

In order for EMAC to be suitable for adiabatic operation, the power consumption of the circuit must decrease proportionally to the operating frequency. This question is addressed here in the case of the AND gate presented above. We look over the average Joule and damping losses of one active comb-drive after one clock cycle, for different time periods T. In order to estimate these energies, we divide the losses encountered during all the simulation by the number of cycles (ten here) and by the number of active comb-drives (here six). For the simulation in Figure 8, this leads to:

$$E_D^{op} = \frac{1}{6 \times 10} E_D(10T)$$

and  $E_J^{op} = \frac{1}{6 \times 10} E_J(10T)$

Figure 9 depicts the dissipation per operation  $E_D^{op}$  and  $E_J^{op}$  with respect to  $\frac{1}{T}$ , for T ranging over four decades. There is no point above  $\frac{1}{T}=2.5.10^{-3}$  because the system requires a time period greater than 400 in order to work properly; under this value, the electrical time period becomes too close to the mechanical relaxation time. However, the driving time period has no upper limit. Figure 9 reveals that both dissipation

decrease when the system is driven slower, following a  $\frac{1}{T}$  law. Therefore, one could conclude that the dissipation per operation vanishes for infinitely slow frequencies, as expected for an adiabatic system.

#### D. Numerical application

These results are presented in reduced units in order to generalise them. This paragraph aims to estimate the energy per operation one could expect for a realistic device. The case of the comb-drive actuator presented by Takahashi *et al.* is considered. Using E-beam lithography, the authors made a comb-drive actuator with the following properties [26]:

- Air gap between the fingers: g = 350 nm

- Springs stiffness:  $k = 0.11 \text{ N.m}^{-1}$

- Resonance frequency of the first mechanical mode:  $f_{res} = 132 \text{ kHz}$

- uniform thickness: t = 260 nm

number of fingers: n = 20

These parameters allow to convert our simulations in SI units, using the relations in §II-B. The characteristic time unit is about  $T_0=1.2~\mu s$ . The AND gate presented in this paper works when the power clock period is greater than  $400T_0=50~\mu s$ . This leads to a maximum frequency of operation of 20 kHz. The voltage unit is  $V_0$ =5.5 V, a value compatible with common IC integration technologies. The resistance of  $10^{-4}$  in reduced units correspond to 2.6 M $\Omega$  in this system.

Finally, the relations of §II-B lead to an energy unit  $E_0 = kg^2 = 13$  fJ. From the graph in Figure 9, one can expect from the AND gate an energy per operation about 260 aJ when operated at 20 kHz. According to adiabatic principle, this value can be arbitrary lowered by reducing the operating frequency. As an example, at 1 kHz the energy per operation becomes 13 aJ. This energy can further be reduced by decreasing the size of the system. As the energy scales in  $g^2$ , dividing the gap by ten reduces the energy per operation by a factor of 100.

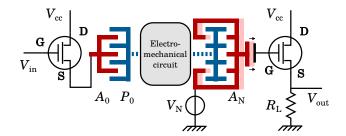

#### IV. CMOS INTERFACING

EMAC must allow integration with conventional CMOS circuits. An example of such integration is pictured in Figure 10. With the actuator of Takahashi *et al.*, the typical capacitance  $C_0$  is extremely weak, in the order of the fF. This is in the same order than the gate capacitance of a typical FET transistor. Consequently, feeding the input active comb-drive  $A_0$  with a FET should not rise any difficulty.

More problematic is the conversion of the mechanical output in electrical signal. To this purpose, a MEMS switch could be used in order to create an electric contact between the last power clock and the gate of an output FET (see Fig. 10). However, this solution causes a non-adiabatic loss inherent to the mechanical contact; but this loss exists only in the output, regardless of the size of the EMAC circuit. The coupling between  $A_N$  and the output FET could also be made by with a supplementary variable comb-drive capacitor.

Fig. 10. Illustration of the interface between a MEMS circuit and a FET. The input comb  $A_0$  is directly connected to the source of the input FET. The output active comb  $A_N$  triggers a nano-relay which connects the last power clock  $V_N$  to the gate of the output FET. The mechanical "1" is then converted to an electrical high state.

#### V. CONCLUSION

In this paper, we introduced a new paradigm for low-energy computation, in which information is encoded mechanically instead of electrically. In this approach, MEMS comb-drive actuators are used for transmitting and processing information. Thanks to their linearity and the absence of leakage currents, comb-drive actuators are compatible with adiabatic operation. We show how these actuators can be arranged and cascaded in order to realise buffer gates, inverters, and the combinational functions AND and OR. Adiabatic operation of a leakage-free circuit leads to a significant reduction of the power dissipated per operation; but this energy saving is obtained at the expense of the speed of the circuit. With a realistic device, one could expect an energy per operation in the order of the attojoule. This is only three orders of magnitude above the Landauer limit for irreversible computation (3 zJ at 300 K). The main dissipation source in EMAC might be the energy loss caused by the mechanical damping.

#### REFERENCES

- A. P. Chandrakasan and R. W. Brodersen, "Minimizing power consumption in digital cmos circuits," *Proceedings of the IEEE*, vol. 83, no. 4, pp. 498–523, Apr 1995.

- [2] S. Paul, A. M. Schlaffer, and J. A. Nossek, "Optimal charging of capacitors," *IEEE Transactions on Circuits and Systems I: Fundamental Theory and Applications*, vol. 47, no. 7, pp. 1009–1016, Jul 2000.

- [3] I. Ferain, C. A. Colinge, and J.-P. Colinge, "Multigate transistors as the future of classical metal-oxide-semiconductor field-effect transistors," *Nature, Volume 479, Issue 7373, pp. 310-316 (2011).*, vol. 479, pp. 310–316, nov 2011.

- [4] S. Vitale, P. Wyatt, N. Checka, J. Kedzierski, and C. Keast, "Fdsoi process technology for subthreshold-operation ultralow-power electronics," *Proceedings of the IEEE*, vol. 98, no. 2, p. 333, 2010.

- [5] H. Soeleman, K. Roy, and B. C. Paul, "Robust subthreshold logic for ultra-low power operation," *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 9, no. 1, pp. 90–99, Feb 2001.

- [6] T. Lin, K.-S. Chong, J. S. Chang, and B.-H. Gwee, "An ultralow power asynchronous-logic in-situ self-adaptive iformula formulatype="inline"¿¡tex notation="tex"¿vddi/tex¿¡/formula¿ system for wireless sensor networks," *IEEE Journal of Solid-State Circuits*, vol. 48, no. 2, p. 573, 2013.

- [7] J. G. Koller and W. C. Athas, "Adiabatic switching, low energy computing, and the physics of storing and erasing information," in Workshop on Physics and Computation, Oct 1992, pp. 267–270.

- [8] W. C. Athas, L. J. Svensson, J. G. Koller, N. Tzartzanis, and E. Y.-C. Chou, "Low-power digital systems based on adiabatic-switching principles," *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 2, no. 4, pp. 398–407, Dec 1994.

- [9] G. L. Snider, E. P. Blair, G. P. Boechler, C. C. Thorpe, N. W. Bosler, M. J. Wohlwend, J. M. Whitney, C. S. Lent, and A. O. Orlov, "Minimum energy for computation, theory vs. experiment," in 2011 11th IEEE International Conference on Nanotechnology, Aug 2011, pp. 478–481.

- [10] J.-S. Wenzler, T. Dunn, T. Toffoli, and P. Mohanty, "A nanomechanical fredkin gate," *Nano Letters*, vol. 14, no. 1, pp. 89–93, 2014. [Online]. Available: http://dx.doi.org/10.1021/nl403268b

- [11] R. Landauer, "Irreversibility and heat generation in the computing process," *IBM J. Res. Dev.*, vol. 5, no. 3, pp. 183–191, jul 1961. [Online]. Available: http://dx.doi.org/10.1147/rd.53.0183

- [12] N. Jeanniot, A. Todri-Sanial, P. Nouet, G. Pillonnet, and H. Fanet, "Investigation of the power-clock network impact on adiabatic logic," in 2016 IEEE 20th Workshop on Signal and Power Integrity (SPI), May 2016, pp. 1–4.

- [13] H. S. Raghav, V. A. Bartlett, and I. Kale, "Investigation of stepwise charging circuits for power-clock generation in adiabatic logic," in 2016 12th Conference on Ph.D. Research in Microelectronics and Electronics (PRIME), June 2016, pp. 1–4.

- [14] S. Houri, A. Valentian, and H. Fanet, Comparing CMOS-Based and NEMS-Based Adiabatic Logic Circuits: 5th International Conference, RC 2013, Victoria, BC, Canada, July 4-5, 2013. Proceedings. Berlin, Heidelberg: Springer Berlin Heidelberg, 2013, pp. 36–45. [Online]. Available: http://dx.doi.org/10.1007/978-3-642-38986-3\_4

- [15] C. L. Ayala, A. Bazigos, D. Grogg, Y. Pu, and C. Hagleitner, "Ultra-low-energy adiabatic dynamic logic circuits using nanoelectromechanical switches," in 2015 IEEE International Symposium on Circuits and Systems (ISCAS), May 2015, pp. 2596–2599.

- [16] C. Pawashe, K. Lin, and K. J. Kuhn, "Scaling limits of electrostatic nanorelays," *IEEE Transactions on Electron Devices*, vol. 60, no. 9, p. 2936, 2013.

- [17] G. Pillonnet, H. Fanet, and S. Houri, "Adiabatic capacitive logic: a paradigm for low-power logic," in 2017 ACM/IEEE 44rd Annual International Symposium on Computer Architecture (ISCA), 2017.

- [18] A. Galisultanov, Y. Perrin, G. Pillonnet, and H. Fanet, Capacitive-based Adiabatic Logic. Springer International Publishing, 2017.

- [19] W. C. Tang, M. G. Lim, and R. T. Howe, "Electrostatically balanced comb drive for controlled levitation," in *IEEE 4th Technical Digest on Solid-State Sensor and Actuator Workshop*, June 1990, pp. 23–27.

- [20] W. A. Johnson and L. K. Warne, "Electrophysics of micromechanical comb actuators," *Journal of Microelectromechanical Systems*, vol. 4, no. 1, pp. 49–59, Mar 1995.

- [21] H. Hammer, "Analytical model for comb-capacitance fringe fields," Journal of Microelectromechanical Systems, vol. 19, no. 1, pp. 175– 182, Feb 2010.

- [22] D. Fang, F. Zheng, B. Chen, Y. Wang, Y. Fang, P. Yang, X. Wen, C. Peng, and S. Xia, "Computation of capacitance and electrostatic forces for the electrostatically driving actuators considering fringe effects," *Microsystem Technologies*, vol. 21, no. 10, pp. 2089–2096, 2015. [Online]. Available: http://dx.doi.org/10.1007/s00542-014-2322-5

- [23] F. Khan, Y. Zhu, J. Lu, J. Pal, and D. V. Dao, "A single-layer micromachined tunable capacitor with an electrically floating plate," *Smart Materials and Structures*, vol. 25, no. 4, p. 045014, 2016. [Online]. Available: http://stacks.iop.org/0964-1726/25/i=4/a=045014

- [24] R. Legtenberg, A. W. Groeneveld, and M. Elwenspoek, "Comb-drive actuators for large displacements," *Journal of Micromechanics and Microengineering*, vol. 6, no. 3, p. 320, 1996. [Online]. Available: http://stacks.iop.org/0960-1317/6/i=3/a=004

- [25] M. López-Suárez, I. Neri, and L. Gammaitoni, "Sub-kbt microelectromechanical irreversible logic gate," *Nature Communications, Volume 7, id. 12068 (2016).*, vol. 7, p. 12068, jun 2016.

- [26] K. Takahashi, E. Bulgan, Y. Kanamori, and K. Hane, "Submicrometer comb-drive actuators fabricated on thin single crystalline silicon layer," *IEEE Transactions on Industrial Electronics*, vol. 56, no. 4, p. 991, 2009.