# Comprehensive Phase-Change Memory Compact Model for Circuit Simulation

Corentin Pigot, Marc Bocquet, Fabien Gilibert, Marina Reyboz, Olga Cueto, V. Della Marca, Paola Zuliani, Jean-Michel Portal

#### ▶ To cite this version:

Corentin Pigot, Marc Bocquet, Fabien Gilibert, Marina Reyboz, Olga Cueto, et al.. Comprehensive Phase-Change Memory Compact Model for Circuit Simulation. IEEE Transactions on Electron Devices, 2018, pp.1 - 8. 10.1109/TED.2018.2862155. hal-01869957

HAL Id: hal-01869957

https://hal.science/hal-01869957

Submitted on 7 Sep 2018

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## Comprehensive Phase-Change Memory Compact Model For Circuit Simulation

Corentin Pigot, Marc Bocquet, Fabien Gilibert, Marina Reyboz, Olga Cueto, Vincenzo Della Marca, Paola Zuliani, and Jean-Michel Portal

Abstract—In this paper, a new continuous multilevel compact model for phase-change memory (PCM) is proposed. It is based on modified rate equations with the introduction of a variable related to GST melting. The model is evaluated using a large set of dynamic measurements and shows a good accuracy with a single model card. All fitting parameters are discussed and their impacts are detailed. Full circuit simulation is performed. Good convergence and fast simulation time suggest that this new compact model can be exploited for PCM circuit design.

Index Terms—Compact modeling; Integrated circuit modeling; Phase-change memory; PCM; PCRAM;

#### I. INTRODUCTION

PHASE-CHANGE memory (PCM) is a non-volatile resistive memory device relying on the phase transition of a small volume in a chalcogenide layer (typically GST). It can be switched from an amorphous high resistive phase to a crystalline low resistive phase by applying a short voltage pulse [1], [2]. This technology is overcoming all of its potential roadblocks and now exhibits rapid switching, extended endurance, high temperature data retention, low power consumption, and good thermal stability under solder reflow conditions [3]–[5].

Device compact models are mandatory to simulate the circuit performance during the back-end design flow step. Consequently, they need to be accurate while ensuring a fast convergence time and a minimal memory usage. Macromodels [6]–[8] and piecewise linear models including a decision module or negative differential resistance [9]-[12] present discontinuities, which are likely to generate convergence issues. Compact models based on rate equations [13]-[17], can be fast and robust. However, despite the enhanced accuracy of some of them, a good correlation with experimental data for any random pulse applied has never been published. Such validations are especially important in a multilevel context, where intermediate resistance level states are exploited. This paper presents a new continuous compact model of phase-change memory, based on comprehensive rate equations. The proposed model is extensively validated by experimental results, in a wide range

of time and temperatures. Using a single model card, the simulation of any random shaped pulse can be achieved, for the very first time. The modeling approach relies on simplified temperature computation, compensated by detailed considerations of the nanophysics inside a PCM cell during programming. The model is efficiently implemented in a Verilog-A code without any decision module to ensure convergence and short simulation time.

Section I describes the model equations and the measurements performed to validate it. Section II presents the correlation between simulations and silicon measurements through a brief extraction flow. Section III is focused on model card parameters with emphasis on their influences and physical meanings. A summary of obtained performances is given in Section IV.

#### II. MODEL PRESENTATION

#### A. Model architecture

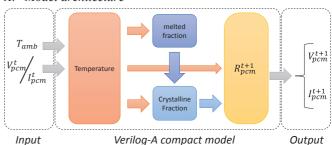

Fig. 1. Modeling flow block diagram

A block diagram of the modeling process is shown in Fig. 1. First, the temperature is computed based on inputs and PCM state from the previous simulation step. The temperature computation module feeds two other related modules: one processing the portion of the active melted volume and the other one determining the crystalline fraction of the remaining nonmelted active part. The crystalline fraction and the temperature are then re-input to the DC module, which computes the cell resistance for the current simulation step.

Manuscript received; revised. The review of this paper was arranged by C. Pigot and F. Gilibert are with STMicroelectronics, 850 rue Jean Monnet, 38926 Crolles, France (e-mail: <a href="mailto:corentin.pigot@st.com">corentin.pigot@st.com</a>; fabien.gilibert@st.com).

P. Zuliani is with STMicroelectronics, Via C. Olivetti 2, 20041 Agrate Brianza, Italy (e-mail: <a href="mailto:paola.zuliani@st.com">paola.zuliani@st.com</a>).

M. Reyboz and O. Cueto are with CEA Leti, Minatec Campus, 38054 Grenoble, France (e-mail: <a href="maina.reyboz@cea.fr">marina.reyboz@cea.fr</a>; <a href="mailto:olga.cueto@cea.fr">olga.cueto@cea.fr</a>).

M. Bocquet, V. Della Marca, and J.M. Portal are with IM2NP, Aix-Marseille Université, 5 rue Enrico Fermi bât Fermi, 13453 Marseille, France (e-mails: marc.bocquet@univ-amu.fr; vincenzo.della-marca@univ-amu.fr; jean-michel.portal@univ-amu.fr).

#### 1) Temperature Module:

Self-heating temperature inside the PCM cell *T<sub>SH</sub>*, follows the first order differential equation (1) [13], [18]:

$$R_{th} * C_{th} \frac{\partial T_{SH}}{\partial t} + T_{SH} = R_{th} * \frac{U^2}{R_{PCM}}$$

(1)

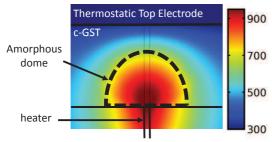

Where U and  $R_{PCM}$  are respectively the voltage across and resistance of the cell,  $R_{th}$  and  $C_{th}$  are effective thermal resistance and capacitance respectively, and t is the time. The ambient temperature  $T_{amb}$  is then added to the self-heating temperature  $T_{SH}$  to obtain the final temperature  $T_{SH}$  used in the next calculations. This temperature has no spatial dimension and we consider that it is calculated on a single point in the system, which is the hottest spot of the device. Thermal calculations performed using Cueto et al.'s electro thermal solver [19] shown in Fig. 2 indicate that this hottest spot inside the PCM layer is located at the interface between the heater and the amorphous dome.

Fig. 2. Finite element simulations of the temperature inside the cell. A temperature gradient is induced between the heater and the top electrode. The simplified temperature calculated in the model refers to the hottest spot.

The effective thermal resistance depends on the phase of the material [15], and has been implemented in the model via the equation (2):

$$R_{th} = R_{thc} \cdot (F_c + F_m) + R_{tha} \cdot F_a \tag{2}$$

$R_{thc}$  is the crystalline thermal resistance and  $R_{tha}$  the amorphous thermal resistance.  $F_c$ ,  $F_m$  and  $F_a$  are respectively the crystalline, melted, and amorphous fraction of the material.

#### 2) Melting Module

Despite its simplified calculation, the temperature is not considered uniform inside the active volume. Hence, some portion of the material can be melted whereas other parts stay solid during a pulse. This partial melting is implemented by the introduction of the state variable  $F_m$ , computed as the solution of the first order differential equation (3):

$$\tau_m \frac{\partial F_m}{\partial t} + F_m = \left[1 + \exp\left(\frac{T_m - T}{\sigma_m}\right)\right]^{-1} \tag{3}$$

Where  $\tau_m$  is the melting time constant,  $T_m$  is the melting temperature of the GST, and  $\sigma_m$  is a parameter reflecting the spatial non-uniformity of the temperature inside the cell. The form of the right hand side of (3) and the fitting parameter  $\sigma_m$  ensure a smooth and continuous transition from solid to melted.

#### 3) Crystalline/Amorphous Module

The crystalline fraction  $F_c$  is calculated by modifying the

right hand side of the classical Johnson-Mehl-Avrami-Kolmogorov (JMAK) equation [20] to take the  $F_m$  variable into account:

$$\tau_c \frac{\partial F_c}{\partial t} + F_c = 1 - F_m \tag{4}$$

Where  $\tau_c$  is the characteristic time of crystallization and "1" stands for the whole active area.

The amorphous fraction is then calculated by:

$$F_a = 1 - F_m - F_c \tag{5}$$

When the time becomes infinite, the variable  $F_c$  tends to the solid fraction, which is 1- $F_m$ , then  $F_a$  tends to 0. Indeed, the amorphous phase is seen as a metastable phase, crystallizing even at room temperature. However, this dynamics do not impact the simulation because the crystallization time is long enough.

#### 4) Resistance Module

The resistance of the whole cell is calculated as a series of resistances for each phase, weighted by using their respective fraction:

$$R_{PCM} = F_c \cdot R_c + F_m \cdot R_c + F_a \cdot R_a + R_{heater} \tag{6}$$

Where  $R_{heater}$  is the resistance of the heater, which is constant for a given technology.  $R_c$  is the resistance of the crystalline phase, and  $R_a$  is the resistance of the amorphous phase. We assume that the resistance of the melted phase is  $R_c$  because in this state, the current is mainly controlled by the resistance of the poly-crystalline GST surrounding the active area.

The current *I<sub>PF</sub>* in the amorphous phase is modeled by Poole-Frenkel conduction [21]–[23] as given by equation (7):

$$I_{PF} = A_{kPF} \cdot F \cdot \exp\left(-\frac{\phi_{PF} - \beta_{PF} \sqrt{F}}{k^T}\right) \tag{7}$$

where  $A_{kPF}$ ,  $\Phi_{PF}$  and  $\beta_{PF}$  are fitting parameters with physical meanings described previously [23], and k is the Boltzmann constant.  $R_a$  is calculated using the Ohm's law, assuming that the voltage drop inside the PCM is mainly located inside the amorphous dome.

The calculation of the field F, as given by equation (8), is impacted by the thickness of the amorphous cap  $u_a$ .  $u_a$  is defined in (8) as a fraction of the maximum size  $u_{a,max}$  of the dome, the latter being treated as a fitting parameter.

$$F = \frac{U}{u_a} \quad \text{with} \quad u_a = F_a u_{a,max} \tag{8}$$

The  $\Phi_{PF}$  parameter of (7) follows Varshni's empirical law [24], [25], such that,

$$\Phi_{PF} = E_{a0} - \frac{a_{va}T^2}{b_{va} + T} \tag{9}$$

Where  $E_{a\theta}$  is the activation energy at 0K, considered as a fitting parameter, and  $a_{va}$  and  $b_{va}$  are thermal parameters, set to the values found in Le Gallo *et al.* [25]:  $a_{va}$ =600 $\mu$ eV.K<sup>-1</sup>,  $b_{va}$ =800K. The temperature dependence of the resistance during the semi-conducting crystalline phase  $R_c$ , follows the expression [26]:

$$R_c = R_{c0} e^{-E_{ac} \left(\frac{1}{kT_{amb}} - \frac{1}{kT}\right)} \tag{10}$$

Where  $E_{ac}$  is an activation energy and  $R_{C_0} = R_{cry}$  when  $T = T_{amb}$ ; both are model card parameters.

#### B. Model innovations

Equation (4) gives the time dependency of  $F_c$ , the parameter  $\tau_c$  contains all other dependencies. In this study, the crystallization speed is considered dependent on the temperature and the amorphous fraction.

Considering (5), the crystallization speed  $\partial F_c/\partial t$  can be extracted from (4) as a function of  $F_a$  and  $\tau_c$ :

$$\frac{\partial F_c}{\partial t} = \frac{F_a}{\tau_c(T, F_a)} \tag{11}$$

To isolate the dependencies, we introduce  $v_g$  as the normalized amorphous-fraction-dependent growth speed and  $\tau_{set}$  the temperature-dependent crystallization time:

$$\tau_c(T, F_a) = \tau_{set}(T) \cdot \frac{F_a}{\nu_g(F_a)} \tag{12}$$

#### 1) Temperature dependent crystallization time

Ciocchini *et al.* [27] show that  $\tau_{set}$  follows a non-Arrhenius behavior, because of an incompatibility of the activation energies between high and low temperatures. This is why in our approach, high- and low-temperature crystallization kinetics are separated, as given in equation (13):

$$\tau_{set} = \tau_{HT} + \tau_{LT} = \left(\tau_{0HT}e^{\frac{E_{AHT}}{kT}} + \tau_{0LT}e^{\frac{E_{ALT}}{kT}}\right)$$

(13)

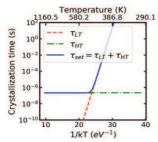

Thereby, equation (13) enables the model to provide a good retention at room temperature and a short crystallization time during high-voltage pulses. Plotted in Fig. 3 is  $\tau_{set}$  as a function of 1/kT, with the temperature scale reported on the upper axis. This plot validates that the crystallization time is short at high temperature, whereas it is many orders of magnitude higher at room temperature.

Fig. 3. Crystallization time as a function of temperature.  $\tau_{set}$  is the sum of  $\tau_{LT}$  and  $\tau_{HT}$ , so that the process is quick at high temperature and slow at low temperature

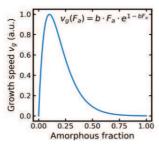

Fig. 4. Growth speed versus the amorphous fraction. This function is implemented to enhance the growth speed for low amorphous fraction.

#### 2) Amorphous-fraction-dependent growth speed

The normalized growth speed  $v_g$  is inserted in the model to reflect the non-uniformity of the crystallization as a function of the size of the amorphous dome. As shown in Fig. 2, the simplified temperature calculated by the model is considered to

be the one at the interface between the heater and the GST. However, the temperature determining the crystallization process, considering re-growth from the surrounding crystalline GST ([19], [28]), is more likely the one at the external interface of the active volume. To take into account this effect while keeping a simple temperature calculation, we chose to let the growth speed vary with the amorphous fraction. Indeed, assuming a constant temperature gradient between the hot spot and the top electrode kept at room temperature, the temperature at the external interface moves with the position of this interface for a given input power. The smaller the amorphous dome, the closer the Amorphous/Crystalline interface is from the heater, and the warmer it is. The normalized growth speed  $v_g$  is defined by the expression shown in (14):

$$v_a(F_a) = b \cdot F_a \cdot e^{1 - bF_a} \tag{14}$$

Where *b* is a fitting parameter. According to this expression,  $v_g$  at a given temperature is higher for low amorphous fractions, as shown in Fig. 4 where  $v_g$  versus  $F_a$  is plotted.

#### C. Electrical characterization method

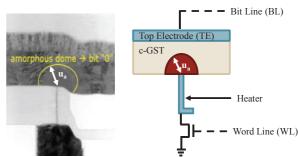

The Transmission Electron Microscopy (TEM) cross-section, along with the equivalent scheme of the test structure is shown in Fig. 5. All characterizations are performed using this test structure. A wall-type PCM structure [29] is connected in series with a MOSFET selector, where the gate is used to limit the current flowing through the cell.  $u_a$  is the radius of the active volume, where phase transitions are located. This material switches from amorphous to crystalline and back to amorphous under the application of pulses. The whole device is integrated in a CMOS technology and the node between the PCM cell and the MOSFET selector is not accessible from outside. Therefore, the following results present the simulation of both devices in series, the MOSFET being previously extracted on a separately.

Fig. 5. TEM cross section of the test structure on the left hand side and equivalent schematics on the right hand side.

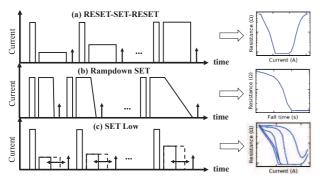

The characterization method aims to test every possible operating condition of the device in order to validate the model extensively. First, the current versus voltage is acquired for several intermediate states by setting the PCM into the desired state and applying a slow ramp voltage on the top electrode [23]. Then, the phase transitions are studied through three different characteristics, shown in Fig. 6; the RESET-SET-RESET is a staircase-up measurement with long squared pulses, the SET Low is a staircase-up with increasing pulse width in

the low current regime and the Rampdown SET is high current pulses with increasing fall times [30], [31].

Fig. 6. Example of typical characteristics of PCM. Each point on the characteristics is composed of a RESET Pulse, a SET pulse and a DC reading: (a) RESET-SET-RESET is long squared pulses with increasing pulse current; (b) Rampdown SET is high current pulses with increasing fall times; (c) Set Low is a staircase-up with increasing pulse width in the low current regime.

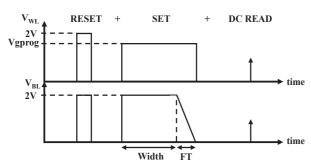

Each measured point reported in these R-time or R-current characteristics is always composed of the same set of pulses, pictured in Fig. 7. First, a RESET operation is performed to fully control the initial state. Then a SET pulse, with a variable width, fall time and current amplitude, is applied to the cell and the programming current is measured. The programming current is averaged in the second half of the pulse width to avoid being disturbed by overshoots, when the current settles. As sketched in Fig. 7, the programming Word Line (WL) voltage is tuned in order to set the current value whereas the Bit Line (BL) voltage controls time width and fall time (FT) parameters. Finally the resistance value of the cell, which is a single point of measurement on the R-time or R-current characteristics, is extracted with 0.1V on the BL and 1.2V on the WL through a DC measurement.

Fig. 7. Detail of the pulse sequence applied to get one measurement. WL programming voltage (Vgprog), pulse width (Width) and fall time (FT) are the programming variables. Reading BL voltage is set at 0.1V. Delays between pulses are fixed to avoid drift effect issue

### TABLE I MEASUREMENT CONDITIONS

| Variable    | RESET-SET-RESET | Rampdown<br>SET | SET Low      |

|-------------|-----------------|-----------------|--------------|

| $V_{ m WL}$ | 0 - 2V          | 2V              | 0 - 1.2V     |

| $ m V_{BL}$ | 2V              | 2V              | 2V           |

| Current     | $0-300\mu A$    | 300μΑ           | $0-200\mu A$ |

| Width       | 10μs            | 10μs            | 200n - 800ns |

| Fall time   | 10ns            | 10n - 600ns     | 10ns         |

| Temperature | 298 - 348K      | 298 - 348K      | 298 - 348K   |

These measurement conditions cover a wide range of the device operating and allow the full extraction of the model card parameters.

The measurement conditions used for each plotted characteristics are summarized in Table I. To get rid of the drift effect [32], the delay between the different pulses is constant. The impact of the ambient temperature is studied and error bars are obtained by repeating three times the exact same set of measurements.

#### III. MODEL VALIDATION THROUGH MODEL CARD EXTRACTION

The entire voltage range measured, including temperature and pulse time dependencies, is fitted using a single model card, which is shown in Table II. Given the simplifications made to ensure the fast convergence of the compact model, the model parameters do not correspond precisely to the physical parameters to which they are related. Yet, all model parameters have been kept to reasonable values during the extraction and they remain coherent with their associated physical parameters. They can be classified into three main categories: the first one is composed of the parameters related to the conductivity of the amorphous and crystalline phases, the second one includes the calculation of the temperature and the melting fraction inside the phase-change area, and the last category refers to time-dependent crystallization.

TABLE II PHYSICAL AND FITTING PARAMETERS

| FHYSICAL AND FILLING PARAMETERS |                                          |                                           |  |

|---------------------------------|------------------------------------------|-------------------------------------------|--|

| Symbol                          | Description                              | Value                                     |  |

| Conduct                         | ion parameters                           |                                           |  |

| $A_{kPF}$                       | Poole-Frenkel conduction prefactor       | $6.5.10^{-12}\Omega^{-1}.m$               |  |

| $\beta_{PF}$                    | Poole-Frenkel constant                   | 14μeV.V <sup>-0.5</sup> .m <sup>0.5</sup> |  |

| $E_{a0}$                        | Poole-Frenkel Activation Energy at 0K    | 0.2eV                                     |  |

| $U_{amax}$                      | Maximum size of the amorphous dome       | 48nm                                      |  |

| $R_{c0}$                        | Crystalline resistance at 0K             | $3k\Omega$                                |  |

| $E_{ac}$                        | Activation energy of the crystalline     | 0.1eV                                     |  |

|                                 | conduction                               |                                           |  |

| $R_{heater}$                    | Resistance of the heater                 | $3.6 \mathrm{k}\Omega$                    |  |

| Thermal parameters              |                                          |                                           |  |

| $C_{th}$                        | Effective thermal capacitance            | $10^{-16}$ J.K <sup>-1</sup>              |  |

| $R_{thc}$                       | Crystalline effective thermal resistance | 2.5K.μW <sup>-1</sup>                     |  |

| $R_{tha}$                       | Amorphous effective thermal resistance   | $7.0K.\mu W^{-1}$                         |  |

| Melting parameters              |                                          |                                           |  |

| $T_m$                           | Melting temperature                      | 960K                                      |  |

| $\sigma_m$                      | Spread of the melting temperature        | 83K                                       |  |

| $\tau_m$                        | Characteristic melting time              | 1ns                                       |  |

| Crystallization parameters      |                                          |                                           |  |

| $\tau_{olt}$                    | Crystallization time prefactor for low   | $2.10^{-39}$ s                            |  |

|                                 | temperature                              |                                           |  |

| $E_{ALT}$                       | Activation energy for low temperature    | 3eV                                       |  |

| $\tau_{oht}$                    | Crystallization time prefactor for high  | 220ns                                     |  |

|                                 | temperature                              |                                           |  |

| $E_{AHT}$                       | Activation energy for high temperature   | 0.0eV                                     |  |

| b                               | Fitting parameter                        | 6                                         |  |

The whole characterizations have been modeled with this only set of parameters.

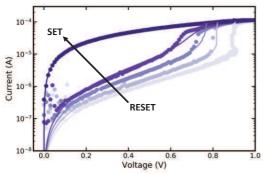

As the resistance is conditional upon the low field conduction, the I-V characteristics must be modeled first. The parameters  $A_{kPF}$ ,  $u_{amax}$  and  $E_{a\theta}$  act respectively on the level, slope and temperature dependence of the amorphous subthreshold conduction. The threshold switching is modeled using a thermal runaway inside a Poole-Frenkel mechanism. Hence, tuning  $R_{tha}$  helps fitting the threshold switching. The SET resistance is modeled using  $R_{c\theta}$  and  $E_{ac}$ . The PCM current versus the Bit Line voltage for several intermediate states is shown in Fig. 8. No snapback is shown because the MOSFET voltage drop is not de-embedded. However, the MOSFET

model has been previously validated on a dedicated test structure, and the snapback capability of the model has already been demonstrated in our previous paper [23]. The model can simulate correctly the subthreshold conduction and the threshold switching for several intermediate states, with only one varying model parameter from one state to another, namely  $u_a$ . It validates the model for multilevel simulations.

Fig. 8. Current of the PCM versus Bit Line voltage for several intermediate states, allowing the extraction of the conduction parameters. Dots are measurements, lines are simulations. The only parameter varying is the amorphous thickness *u<sub>a</sub>*.

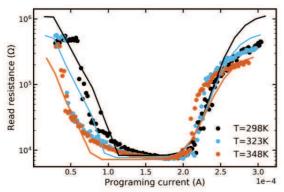

Fig. 9. RESET-SET-RESET characteristics: Staircase-up with long (10μs) pulses and sharp fall time (10ns) under three operating temperatures. Dots are measurements, lines are simulations. Both memory switching are visible on this characteristics and are correctly modeled.

The parameters belonging to the second category act on the RESET-SET-RESET characteristics, presented in Fig. 9. In this figure, the resistance is plotted as a function of the programming current for three different temperatures. The transitions RESET to SET and SET to RESET are well fitted considering the self-heating effect. We demonstrate that our model is able to reproduce the weak impact of external temperature as shown by experimental characterizations. All parameters dealing with both SET and RESET resistances have been previously extracted, using curves shown in Fig. 8. On the SET to RESET transition visible on the right hand side of these curves, the melting parameters  $T_m$  and  $\sigma_m$  are extracted. The time constant  $\tau_m$  has not been measured, because it is shorter than the shortest measured pulse width, i.e. 200ns. It is set to 1ns, as previously described in the literature [25]. The RESET to SET transition is mostly determined by the parameters responsible for the crystallization at low temperature, namely  $\tau_{OLT}$  and  $E_{ALT}$ . The parameter  $R_{thc}$  acts on the whole curve, since it is accountable for the temperature computation.

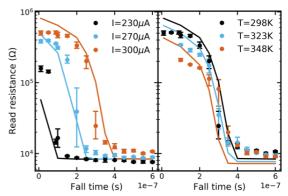

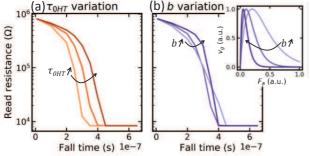

Once all static parameters are extracted, the dynamic behavior of the crystallization is studied on the Rampdown SET plot, presented in Fig. 10. The read resistance as function of the fall time is plotted for different programming currents on the left hand side, and for different temperatures on the right hand side. The transition for several temperatures and current levels is captured by the model using the parameters *b*, *TohT* and *EAHT*.

Fig. 10. Rampdown SET characteristics: Transition from RESET to SET using the fall time increase for three different programming current on the left, under three operating temperatures on the right. Dots are measurements, lines are simulations. Error bars are obtained by repeating three times the exact same set of measurements. The model reacts appropriately for both

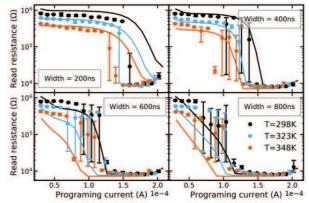

Fig. 11. SET Low characteristics: Transition from RESET to SET using low current density for four pulse widths under three operating temperatures. Dots are measurements, lines are simulations. Error bars are obtained by repeating three times the exact same set of measurements. The dynamics is hard to fit with the same model card as the Rampdown SET, as tradeoff has to be found to fit both characteristics.

The dynamics of the crystallization must also be checked on the SET Low characteristics, where the SET operation is realized at relatively low current but depends on the pulse width. The SET Low results are shown in Fig. 11, exhibiting the phase transition for pulse widths ranging from 200ns to 800ns for three different ambient temperatures. The ambient temperature variation has an important impact on the high resistive conduction, in both the model and the measurements. and it seems that crystallization happens earlier at high ambient temperature in both the measurements and in the model. However, error bars in the transition regime means that the transition happens abruptly and stochastically in the transition regime. The modeling of this transition is smooth, because the model is built on state variables that always vary continuously. This stochasticity, which has been reported by Le Gallo et al. [33], will be integrated in future development using corners.

The modeling of the SET Low characteristics is done using the same crystallization parameters as the Rampdown SET, *i.e b* and  $\tau_{HT}$ . Hence, a tradeoff has to be found between those two fits. The thermal activation  $E_{AHT}$  can be optimized, as well as the ratio  $R_{tha}/R_{thc}$ , so that all features are well fitted.

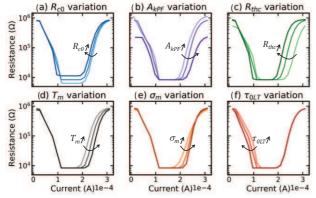

Fig. 12. Impact of the static parameters on the RESET-SET-RESET characteristics. (a)  $R_{c\theta}$  rules the conduction in the SET regime; (b)  $A_{kPF}$  impacts the RESET resistance; (c)  $R_{thc}$  increases the internal temperature, which is mostly seeable in the melting phase; (d) The average melting temperature  $T_m$  impacts the SET to RESET transition current; (e)  $\sigma_m$  changes SET to RESET transition spread; (f)  $\tau_{\theta LT}$  deals with RESET to SET transition.

#### IV. PARAMETER PHYSICAL MEANING

After the model is validated, the variation of the model card parameters is shown in order to illustrate their impact and physical meanings. Let us consider the RESET-SET-RESET characteristics, as pictured in Fig. 12. The level of the crystalline resistance is modified by  $R_{c0}$  and the high resistance level is dependent on  $A_{kPF}$ , the Poole-Frenkel pre-factor.  $R_{thc}$ plays on every aspect of this curve, as it rules the internal temperature. The SET to RESET transition proceeds of the amorphisation of the material, which involves the melting of it first. As the fall time is short in this experiment, the crystal does not have time to grow and the material stays in the disordered phase. The level of resistance achieved only depends on the amount of material that has been melted during the pulse. A change in the melting temperature  $T_m$  shifts the transition whereas a modification of the  $\sigma_m$  parameter modifies the slope of the transition. Finally, the parameter  $\tau_{OLT}$  dominates the RESET-SET transition because the operation happens in the model at a quite low temperature.

Fig. 13. Impact of the variation of the parameters  $\tau_{OHT}$  and b on the growth speed. (a)  $\tau_{OHT}$  acts on the mean crystallization time; (b) b increases the growth speed for low amorphous fraction (inset), so enhances the positive feedback on the Rampdown SET crystallization speed.

Fig. 13 highlights the details of the Rampdown SET operation through the variation of two effective parameters  $\tau_{OHT}$  and b.  $\tau_{OHT}$  impacts the average crystallization time, as illustrated in Fig. 13(a). As displayed in the inset of Fig. 13(b), b accentuates the growth speed for low amorphous fraction, thus accelerates the crystallization process as the crystallization fraction increases. This auto-positive feedback sets the abruptness of the transition that can be seen in Fig. 13(b).

Both Rampdown SET and SET Low operations are modeled by the same mechanism, which is the growth from the surrounding crystalline GST. In order to satisfy both crystallization dynamics with the same set of parameters, two levers are used. First, the temperature activation of the crystallization time can be tuned because both crystallizations do not happen at the same internal temperature. Second, we can use the concurrency between both thermal resistances,  $R_{tha}$  and  $R_{thc}$ . Inspired by finite element simulations done by Cueto et al.[19], the lever consists of enhancing the crystallization speed at low current by artificially increasing the internal temperature immediately after the threshold switching using a strong  $R_{tha}$ . On the contrary, a lower  $R_{thc}$  will slow the crystallization at high current, as the temperature achieved in the cell will be lower.

#### V. PERFORMANCE ASSESSMENT

The performance of the model, measured in simulation time, is now discussed. To check this aspect, addressable matrixes of PCM, including the MOSFET selector, have been simulated using the Mentor Graphics' simulator Eldo on a single 2.60GHz Intel® Xeon® CPU E5-2697 v3. Simulating 10 bits takes half a second and the multiple thread processing of a 10 Kbits matrix on 4 CPU can take just about 12 minutes, for a full RESET/SET/READ sequence. This simple example proves that this model is completely suitable for circuit simulation, because it is accurate and allows fast simulation, even for multiple cells.

#### VI. CONCLUSION

A new comprehensive compact model is proposed. It is compared to extensive measurements covering a wide range of times, currents, and operating temperatures. Our model fits well to all the electrical characterization results using a single model card, including for the first time a compact modeling of two different crystallization dynamics, named Rampdown SET and SET Low. This is possible using several modeling innovations that have never been used before, such as the explicit use of a melting fraction, a non-Arrhenius form of the crystallization time and a growth speed enhanced for low amorphous fractions. The physical effects described in this model help to model the different crystallization dynamics independently on the temperature and programming current variations. A switchless Verilog-A implementation of the physical-based equations ensures the fast convergence of the model, even out of the fitting range. Tests run on multiple addressable matrixes exhibit reasonable simulation times, proving that the model is suitable for circuit simulation, thanks to the efficient implementation which enables short convergence time.

#### VII. REFERENCES

[1] S. R. Ovshinsky and H. Fritzsche, "Amorphous semiconductors for switching, memory, and imaging applications," *IEEE Trans. Electron*

- Devices, vol. 20, no. 2, 1973, DOI: 10.1109/T-ED.1973.17616.

- S. Raoux and M. Wuttig, Phase Change Materials. 2009.

- [2] [3] G. W. Burr, M. J. BrightSky, A. Sebastian, H.-Y. Cheng, J.-Y. Wu, S. Kim, N. E. Sosa, N. Papandreou, H.-L. Lung, H. Pozidis, E. Eleftheriou, and C. H. Lam, "Recent Progress in Phase-Change Memory Technology," IEEE J. Emerging Sel. Top. Circuits Syst., 146-162, no. pp. 10.1109/JETCAS.2016.2547718.

- [4] G. Servalli, "Emerging memory technologies for high density applications," in European Solid-State Device Research Conference, 2017, pp. 156-159, DOI: 10.1109/ESSDERC.2017.8066615.

- F. Xiong, E. Yalon, A. Behnam, C. M. Neumann, K. L. Grosse, S. [5] Deshmukh, and E. Pop, "Towards ultimate scaling limits of phasechange memory," in IEEE International Electron Devices Meeting, 2016, p. 4.1.1-4.1.4, DOI: 10.1109/IEDM.2016.7838342

- P. Junsangsri and F. Lombardi, "A New Comprehensive Model of a [6] Phase Change Memory (PCM) Cell," IEEE Trans. Nanotechnol., vol. 6, 1213-1225, Nov. 13, no. 6, pp. 1213 10.1109/TNANO.2014.2353992

- R. A. Cobley and C. D. Wright, "Parameterized SPICE model for a phase-change RAM device," *IEEE Trans. Electron Devices*, vol. 53, [7] no. 1, pp. 112-117, 2006, DOI: 10.1109/TED.2005.860642.

- N. H. El-Hassan, T. N. Kumar, and H. A. F. Almurib, "Improved [8] SPICE model for Phase Change Memory cell," in International Conference on Intelligent and Advanced Systems, 2014, pp. 1-6, DOI: 10.1109/ICIAS.2014.6869529.

- [9] D.-L. Cai, Z.-T. Song, X. Li, H.-P. Chen, and X.-G. Chen, "A Compact Spice Model with Verilog-A for Phase Change Memory Chin. Phys. Lett., vol. 28, no. 1, p. 018501, Jan. 2011, DOI: 10.1088/0256-307X/28/1/018501.

- [10] D. Ventrice, P. Fantini, A. Redaelli, A. Pirovano, A. Benvenuti, and F. Pellizzer, "A Phase Change Memory Compact Model for Multilevel Applications," *IEEE Electron Device Lett.*, vol. 28, no. 11, pp. 973–975, Nov. 2007, DOI: 10.1109/LED.2007.907288.

- [11] X. Li, Z. Song, D. Cai, X. Chen, and H. Chen, "An SPICE model for phase-change memory simulations," J. Semicond., vol. 32, no. 9, pp. 0-4, 2011, DOI: 10.1088/1674-4926/32/9/094011

- [12] N. Xu, J. Wang, Y. Deng, Y. Lu, B. Fu, W. Choi, U. Monga, J. Jeon, J. Kim, K. Lee, and E. S. Jung, "Multi-domain compact modeling for GeSbTe-based memory and selector devices and simulation for largescale 3-D cross-point memory arrays," in *IEEE International Electron Devices Meeting*, 2016, vol. 1, p. 7.7.1-7.7.4, DOI: 10.1109/IEDM.2016.7838371.

- [13] E. Covi, A. Kiouseloglou, A. Cabrini, and G. Torelli, "Compact model for phase change memory cells," in Conference on Ph.D. Research in Microelectronics and Electronics, 2014, pp. 1-4, DOI: 10.1109/PRIME.2014.6872681.

- K. C. Kwong, J. He, P. K. T. Mok, and M. Chan, "Phase-change [14] memory RESET model based on detailed cell cooling profile," IEEE Trans. Electron Devices, vol. 58, no. 10, pp. 3635–3638, 2011, DOI: 10.1109/TED.2011.2162843.

- K. Sonoda, A. Sakai, M. Moniwa, K. Ishikawa, O. Tsuchiya, and Y. [15] Inoue, "A compact model of phase-change memory based on rate equations of crystallization and amorphization," IEEE Trans. Electron Devices, vol. 55, no. 7, pp. 1672-1681, 2008, DOI: 10.1109/TED.2008.923740.

- A. Pantazi, A. Sebastian, N. Papandreou, M. Breitwisch, C. Lam, H. Pozidis, and E. Eleftheriou, "Multilevel phase change memory [16] modeling and experimental characterization," in European Phase Change and Ovonics Symposium, 2009, pp. 34-41.

- C. M. Jung, E. S. Lee, K. S. Min, and S. M. Kang, "Compact Verilog-[17] A model of phase-change RAM transient behaviors for multi-level applications," Semicond. Sci. Technol., vol. 26, no. 10, p. 105018, 2011, DOI: 10.1088/0268-1242/26/10/105018.

- [18] G. Marcolini, F. Giovanardi, M. Rudan, F. Buscemi, E. Piccinini, R. Brunetti, and A. Cappelli, "Modeling the dynamic self-heating of PCM," in European Solid-State Device Research Conference, 2013, pp. 346-349, DOI: 10.1109/ESSDERC.2013.6818889.

- [19] O. Cueto, V. Sousa, G. Navarro, and S. Blonkowski, "Coupling the Phase-Field Method with an electrothermal solver to simulate phase change mechanisms in PCRAM cells," in International Conference on Simulation of Semiconductor Processes and Devices, 2015, vol. 2015-Octob, 301-304 no. pp 10.1109/SISPAD.2015.7292319.

- [20] M. Avrami, "Granulation, phase change, and microstructure kinetics

- of phase change. III," J. Chem. Phys., vol. 9, no. 2, pp. 177-184, 1941, DOI: 10.1063/1.1750872.

- [21] Y. H. Shih, M. H. Lee, M. Breitwisch, R. Cheek, J.-Y. Wu, B. Rajendran, Y. Zhu, E. K. Lai, C. F. Chen, H.-Y. Cheng, A. Schrott, E. Joseph, R. Dasaka, S. Raoux, H. L. Lung, and C. Lam, "Understanding amorphous states of phase-change memory using frenkel-poole model," in IEEE International Electron Devices Meeting - Technical Digest, 2009, vol. 3, pp. 753-756, DOI: 10.1109/IEDM.2009.5424229.

- R. M. Hill, "Poole-Frenkel conduction in amorphous solids," Philos. [22] vol. 23, no. 181, pp. 59-86, 1971, DOI: 10.1080/14786437108216365.

- [23] C. Pigot, F. Gilibert, M. Reyboz, M. Bocquet, P. Zuliani, and J.-M. Portal, "Phase-change memory: A continuous multilevel compact model of subthreshold conduction and threshold switching," Jpn. J. Appl. Phys., vol. 57, no. 4S, p. 04FE13, Apr. 2018, DOI: 10.7567/JJAP.57.04FE13.

- Y. P. Varshni, "Temperature dependence of the energy gap in semiconductors," *Physica*, vol. 34, no. 1, pp. 149–154, 1967, DOI: [24] 10.1016/0031-8914(67)90062-6.

- M. Le Gallo, A. Athmanathan, D. Krebs, and A. Sebastian, "Evidence [25] for thermally assisted threshold switching behavior in nanoscale phase-change memory cells," J. Appl. Phys., vol. 119, no. 2, p. 025704, 2016, DOI: 10.1063/1.4938532.

- J. A. Becker, C. B. Green, and G. L. Pearson, "Properties and Uses [26] of Thermistors - Thermally Sensitive Resistors," Trans. Am. Inst. Electr. Eng., vol. 65, no. 11, pp. 711-725, 1946, DOI: 10.1109/T-AIEE.1946.5059235.

- N. Ciocchini, M. Cassinerio, D. Fugazza, and D. Ielmini, "Evidence [27] for non-arrhenius kinetics of crystallization in phase change memory devices," IEEE Trans. Electron Devices, vol. 60, no. 11, pp. 3767-3774, 2013, DOI: 10.1109/TED.2013.2282637.

- [28] A. Bastard, J. C. Bastien, B. Hyot, S. Lhostis, F. Mompiou, C. Bonafos, G. Servanton, C. Borowiak, F. Lorut, N. Bicais-Lepinay, A. Toffoli, C. Sandhya, A. Fantini, L. Perniola, E. Gourvest, S. Maitrejean, A. Roule, V. Sousa, D. Bensahel, and B. André. "Crystallization study of 'melt quenched' amorphous GeTe by transmission electron microscopy for phase change memory applications," Appl. Phys. Lett., vol. 99, no. 24, pp. 2009-2012, 2011, DOI: 10.1063/1.3668095.

- R. Annunziata, P. Zuliani, M. Borghi, G. De Sandre, L. Scotti, C. [29] Prelini, M. Tosi, I. Tortorelli, and F. Pellizzer, "Phase Change Memory technology for embedded non volatile memory applications for 90nm and beyond," in IEEE International Electron Devices Meeting, 2009, pp. 1-4, DOI: 10.1109/IEDM.2009.5424413.

- [30] V. Sousa, G. Navarro, N. Castellani, M. Coue, O. Cueto, C. Sabbione, P. Noe, L. Perniola, S. Blonkowski, P. Zuliani, and R. Annunziata, "Operation fundamentals in 12Mb Phase Change Memory based on innovative Ge-rich GST materials featuring high reliability performance," in Symposium on VLSI Technology - Digest of Papers, T98-T99. 2015, Technical pp. 10.1109/VLSIT.2015.7223708.

- G. Puzzilli, F. Irrera, A. Padovani, P. Pavan, L. Larcher, A. Arya, V. [31] Della Marca, and A. Pirovano, "On the RESET-SET transition in phase change memories," in European Solid-State Device Research Conference, 2008, 158-161. 10.1109/ESSDERC.2008.4681723.

- A. Pirovano, A. L. Lacaita, F. Pellizzer, S. A. Kostylev, A. Benvenuti, [32] and R. Bez, "Low-field amorphous state resistance and threshold voltage drift in chalcogenide materials," *IEEE Trans. Electron Devices*, vol. 51, no. 5, pp. 714–719, 2004, DOI: 5, pp. 10.1109/TED.2004.825805.

- [33] M. Le Gallo, T. Tuma, F. Zipoli, A. Sebastian, and E. Eleftheriou, "Inherent stochasticity in phase-change memory devices," in European Solid-State Device Research Conference, 2016, pp. 373-376, DOI: 10.1109/ESSDERC.2016.7599664.

LETI in Grenoble.

Corentin Pigot received the M.S. degree in nanoscience from Grenoble-INP - Phelma, Grenoble, France, in 2015. He is currently pursuing the Ph.D. degree in microelectronics, working on phase-change memory characterization and compact modeling at STMicroelectronics, Crolles with the IM2NP Lab in Marseille and CEA-

Marc Bocquet received the Ph.D. degree in micro and nanoelectronics from University Grenoble, Grenoble, France, in 2009. He became an Associate Professor with the University of Marseille – Polytech'Marseille, in 2010, and he is a member of the Memories Team, IM2NP. His current research interests include electrical characterization and physical/compact

modeling of emerging memory devices.

Fabien Gilibert received the Ph.D. degree in microelectronics from Aix-Marseille University, France, in 2006. He is currently working non-volatile memories compact modeling inside the SPICE team of STMicroelectronics, Crolles.

Marina Reyboz received the Engineering degree from Ecole Supérieure de Physique de Marseille, France, and the D.E.A. degree from Université de Provence, Marseille, both in 2004. From 2004 to 2007, she prepared a Ph.D. thesis with CEALETI, MINATEC and Polytechnic Institute of Grenoble (INPG) on compact modelling of a double gate

MOSFET. Since 2007, she is with CEA-LETI, MINATEC, in the Simulation and Compact Modelling Lab. as a researcher staff member. Her research interests are now focused on compact modelling of non-volatile resistive memories like PCRAM, OxRRAM and CBRAM.

Olga Cueto graduated from "Ecole Nationale des Ponts et Chaussées" in Paris in 1991, with a specialization on Computer Science and Applied Mathematics. In 2001, she joined CEA Grenoble LETI where she has been working in scientific computing applied to several fields: electromagnetism, process simulation and more recently simulation of phase change memories

in collaboration with STMicroelectronics.

Vincenzo Della Marca was born in Modena, Italy, in 1983. He graduated in electrical engineering from the University of Modena and Reggio Emilia, Italy, in 2008 where he has worked on electrical characterization of resistive memories. In 2013 he received his Ph.D. from Aix-Marseille University in collaboration with STMicroelectronics, the IM2NP and CEA-LETI. He is now associate professor

at Aix-Marseille University, department of Microelectronics and Telecommunications. His research activities, at Im2np laboratory, are in the field of embedded non-volatile memories for low power and high reliability applications.

Paola Zuliani received the Laurea degree in Physics from the University of Milan, Italy, in 1993. In 1997 she joined STMicroelectronics. Her activity started on Floating Gate-based NVM, but since 2003 is focused on embedded PCM technology development.

Jean-Michel Portal received the B.S. from University of Strasbourg, France, the M.S. (1996) and the Ph.D. (1999) degree in microelectronics from the University of Montpellier, France. He joined Aix-Marseille University as associate professor in 2000. In 2008, he became Full-Professor and he heads the IM2NP "Memories Team" since

2009. His current research interests include Non-volatile memory modeling, design and test. He is author or co-author of more than 140 articles in International Refereed Journals and Conferences, and is co-inventor of 4 patents. He has supervised 20 Ph.D. students and several Master students.