## Two-stage unbuffered CFOA based non-inverting resistive-feedback amplifier: a study based on the description of the operational transconductance conveyor (OTC)

Herve Barthelemy, Remy Vauche, Valentin Gies, Sylvain Bourdel, Jean

Gaubert

### ▶ To cite this version:

Herve Barthelemy, Remy Vauche, Valentin Gies, Sylvain Bourdel, Jean Gaubert. Two-stage unbuffered CFOA based non-inverting resistive-feedback amplifier: a study based on the description of the operational transconductance conveyor (OTC). Analog Integrated Circuits and Signal Processing, 2018, 97 (2), pp.243-252. 10.1007/s10470-018-1219-0. hal-01856939

## HAL Id: hal-01856939 https://hal.science/hal-01856939

Submitted on 3 Feb 2019

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés. Analog Integrated Circuits and Signal Processing (2018) 97:243–252 https://doi.org/10.1007/s10470-018-1219-0

https://link.springer.com/epdf/10.1007/s10470-018-1219-0?author\_access\_token=kgBJss3Sp0osxUuZUTQL5ve4RwlQNchNByi7wbcMAY4aZEjLid NAjVlNgBarhocx6\_nWJbv3UGAydIAOYvatiWrQbCMn4JxTpJxhj9yfrMOyUSzokRMpKBQ9L2WevC 5VE5LPhp3dW6VUoxGbL45sw%3D%3D

## Two-stage unbuffered CFA based non-inverting resistivefeedback amplifier: a study based on the description of the operational transconductance conveyor (OTC).

H. Barthélemy, R. Vauché, V. Giès, S. Bourdel, J. Gaubert

#### Abstract

A study of the non-inverting amplifier based on a two stages CMOS unbuffered *current-feedback-amplifier* (UCFOA) is proposed in this paper. Using a small-signal equivalent circuit (macro-model) of the non-inverting amplifier, a theoretical explanation of the closed loop gain is given. The opamp phase margin and its bandwidth have been estimated from the quality factor Q of resonance and using a novel description of the UCFOA input stage called *Operational Transconductance Conveyor* (OTC). The OTC description can be viewed as an extension of type II second generation current conveyors. Based on the fundamental parameters of the proposed OTC, a theoretical approach given in this paper explains how to evaluate precisely the value of the UCFOA compensation capacitance. PSPICE was used to simulate both the theoretical macro-model and the CMOS configuration from a 0.35µm typical BSIM3V3 transistor models.

*Index Terms* — opamp, current feedback amplifier, transconductance amplifier, diamond transistor, current conveyor

#### **1. INTRODUCTION**

Since the discovery of the negative feedback amplifier by HS Black [1,2], a few number of feedback amplifier topologies arose from industry. This is due to the fact that these topologies are synthesized from the Voltage Controlled Current Sources (VCCS) which can be electrically simulated, historically by

vacuum tubes and more recently by Bipolar Junction Transistors (BJT) or Metal Oxide Semiconductor (MOS) transistors. Today, two main types of voltage output operational amplifiers are available on the market: *i*) Voltage Feedback Operational Amplifier (VFOA) [3,4] and *ii*) Current Feedback Operational Amplifier (CFOA) [5-8]. The first sold VFOA was the K2-W operational amplifier produced in 1952 [2] and the concept of the current-feedback was introduced around 1942 [9], while the first silicon integrated CFOA topology was probably firstly suggested by D. J. Hamilton in 1964 [10]. The first commercial silicon CFOA called CLC103, was produced by Comlinear corporation in 1982 [11], 20 years after the first commercial silicon VFOA developed by Wildlar and Talbert [4]. The CFOA and the VFOA provide both a voltage type output. However, when their output voltage amplifier (output voltage buffer) is not implemented, they are called unbuffered VFOA (UFVOA) and unbuffered CFOA (UCFOA) and provide both a current type output (*high output impedance*).

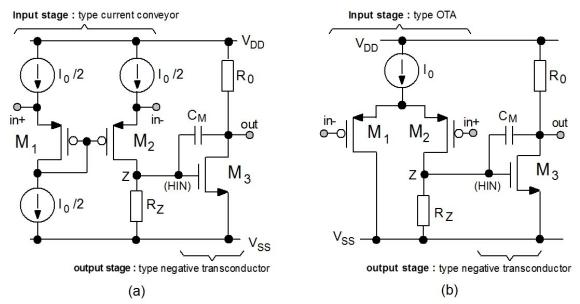

**Fig.1.** Typical two stages UVFOA and UCFOA CMOS topologies: (a) UVFOA : two stage CMOS Miller OTA (ref. [16] with  $C_M=0$ ) (b) UCFOA two stage current mode operational amplifier.

Since the emergence of the CMOS technology, most of loading impedances are capacitive. In this case, the unbuffered operational amplifier could also provide a higher DC open loop gain voltage. For this reason, most analog IC designers use unbuffered feedback operational amplifiers [12] instead of classical output voltage operational amplifiers. The Unbuffered VFOA (UVFOA) can be considered as an Operational Transconductance Amplifier (OTA) since its input impedances are high [13-15]. However, the Unbuffered CFOA (UCFOA) can only be considered as a non-ideal OTA since its negative input node does not provide a high input impedance [6-8]. Thus, use of the OTA acronym for UCFOA can create a misunderstanding. For this reason, the term "Operational Transconductance Conveyor" (OTC) is used in this paper to describe the UCFOA topologies. This proposed Operational

Transconductance Conveyor (OTC) is also an extension of the type II current conveyors and that it will be useful in analog signal processing. Here, using VFOA, CFOA, OTA and OTC acronyms, Table I summarizes the input and output types for the four operational amplifiers previously discussed.

| TABLE I                                  |                                    |        |       |  |

|------------------------------------------|------------------------------------|--------|-------|--|

| Mains opamps topologies                  |                                    |        |       |  |

| (1:0                                     | (I : CURRENT TYPE V: VOLTAGE TYPE) |        |       |  |

|                                          | Inj                                | Inputs |       |  |

| Opamps                                   | (in+)                              | (in-)  | (out) |  |

| Voltage output types                     |                                    |        |       |  |

| VFOA                                     | V                                  | V      | V     |  |

| CFOA                                     | V                                  | Ι      | V     |  |

| Current output types (unbuffered opamps) |                                    |        |       |  |

| OTA                                      | V                                  | V      | Ι     |  |

| OTC                                      | V                                  | Ι      | Ι     |  |

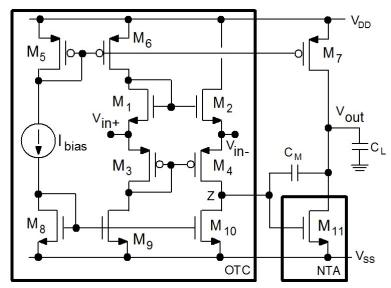

Part (a) of Fig. 1 shows a typical CMOS configuration of a two-stage Miller OTC (two-stage UCFOA) which is used in [16] to implement a high frequency gyrator. This circuit is part of the CFOA family since the node *in-* is not voltage buffered and also, it exists an AC current flowing through the node *in-* and the source of  $M_2$ . Part (b) of Fig. 1 shows the CMOS classical two-stage Miller OTA (two-stage UVFOA) using a traditional pair of two transistors ( $M_1$  and  $M_2$ ). This circuit is part of the VFOA family since the nodes *in+* and *in-* are connected to MOS gates. For both of them, the node Z is a High Impedance Node (HIN) which allows an operational amplifier with high transconductance gain to be achieved thanks to the second stage.

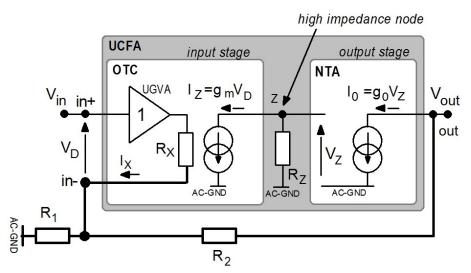

**Fig. 2.** Electrical description of the two stages unbuffered current feedback amplifier (Ideal UCFOA for  $R_x=0$  and  $R_z \rightarrow \infty$ ), the Miller capacitance is not represented.

The purpose of this paper introduces a general approach to study a non-inverting amplifier based on two-stage UCFOA for which the topology is shown in Fig. 2. The study proposed here will differ from traditional ones because the opamp output is not voltage buffered. The circuit is composed of an input

stage (OTC), a high impedance  $R_z$  at node Z (HIN), and a single output voltage controlled current source called here Negative Transconductance Amplifier (NTA). In this representation, the node *in+* of the UCFOA is voltage buffered by a Unit Gain Voltage Amplifier (UGVA). Moreover, the node AC-GND is supplied at the DC common mode-voltage of the operational amplifier. This common mode voltage is generally chosen to obtain the maximum dynamic for output voltage. This leads to set  $V_{AC-GND}$  to  $(V_{DD}+V_{SS})/2$  where  $V_{DD}$  and  $V_{SS}$  are respectively the positive and negative supply voltages of the operational amplifier. Then  $V_{AC-GND}$  is equal to  $V_{DD}/2$  (resp. 0V) when  $V_{SS}$  is set to 0V (resp.  $-V_{DD}$ ). Finally, an ideal UCFOA is obtained when  $R_X$  is null and  $R_Z$  infinite.

In section II, a discussion about the OTC is given. Using as a case study, a two-stage Miller OTC is presented and simulated in section III. In section IV, a theoretical analysis of the non-inverting amplifier is proposed. This analysis and theory are based on the proposed equivalent macro-model of the CMOS configuration using small-signals. Simulation results, discussions, and comparison with theory are given in section V before the conclusion in section VI.

#### 2. OPERATIONAL TRANSCONDUCTANCE CONVEYOR

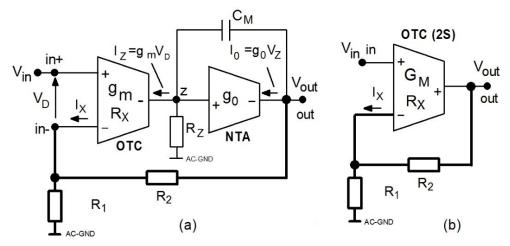

In Fig.2, when the current ration  $|I_Z/I_X|=1$ , the OTC can be designed from different popular active elements like the 2<sup>nd</sup> generation Current Conveyor (CCII) [17], the 2<sup>nd</sup> generation current-controlled current conveyor (CCCII) [18] or the diamond transistor [6,8] for examples. Using the OTC description allows us to consider all possible topologies in terms of current gain ( $I_Z/I_X$ ), i.e. equal or different than 1, in conjunction with different values of the equivalent resistance  $R_X$ . Using a proposed symbol for the OTC (input stage) and the NTA symbol (output stage) as ideal active elements, Fig.3a shows the non-inverting amplifier configuration.

Fig. 3. Two-stage Miller UCFOA based non-inverting amplifier (a) Equivalent circuit using a one-stage OTC as input stage and NTA as output stage (b) equivalent circuit based on a two stages high G<sub>M</sub> OTC (Miller OTC).

Equation (1) shows that the two-stage OTC has the same order of magnitude than a classical two-stage Miller OTA. Its transconductance gain  $G_M$  which is given by:

$$G_M = g_0 \cdot g_m \cdot R_Z \tag{1}$$

has the same order of magnitude than a classical two-stage Miller OTA. From Fig. 2, the following formula of I<sub>x</sub>:

$$I_X = V_D / R_X \tag{2}$$

and Iz:

$$I_Z = g_m V_D \tag{3}$$

can be obtained. By defining a parameter  $\alpha$  equals to the current gain between I<sub>x</sub> and I<sub>z</sub> as follows:

$$\frac{I_z}{I_x} = \alpha \tag{4}$$

the parameter  $\alpha$  can be expressed from (2) and (3) as a function of  $g_m$  and  $R_x$  which gives:

$$\alpha = g_m \cdot R_X \tag{5}$$

Table II gives some examples of correspondences with popular active elements according to  $R_x$  and  $\alpha$ values. As mentioned previously, the OTC also offers the great advantage of taking into account every  $R_x$  and current gain  $\alpha$  compared for example with CCII [6,17,18], or diamond transistor [6]. Thus, in the same way that an OTA is a universal active element which permits to describe the VFOA input stage, an OTC permits to describe all CFOA input stage.

| OTC example of correspondences for $ \alpha =1$ and $ \alpha >1$ |                       |                  |                          |

|------------------------------------------------------------------|-----------------------|------------------|--------------------------|

| α                                                                | <b>R</b> <sub>X</sub> | <b>g</b> _m      |                          |

| -1                                                               | 0                     | 8                | OTC = CCII+ [17]         |

| +1                                                               | 0                     | 8                | OTC = CCII- [17]         |

| -1                                                               | $R_{X} > 0$           | $ \alpha /R_X$   | OTC =CCCII+ [18]         |

|                                                                  |                       |                  | (diamond transistor [8]) |

| +1                                                               | $R_{X} > 0$           | α/R <sub>x</sub> | OTC = CCCII- [18]        |

| <0                                                               | $R_{X} > 0$           | $ \alpha /R_x$   | OTC ( positive output)   |

| >0                                                               | $R_{X} > 0$           | α/R <sub>x</sub> | OTC (negative output)    |

TABLE II

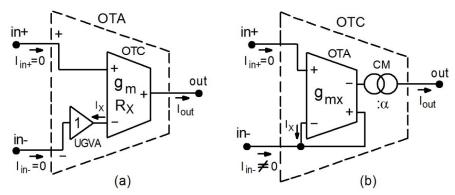

Fig.4. Example of: (a) OTC based OTA and UGVA (b) OTA based OTC and CM (Current Mirror).

To underline the difference between the OTA and the OTC, an OTA configured with an internal OTC, and an OTC configured with an internal OTA are respectively shown in part (a) and (b) of Fig. 4. It is possible to observe that in part (a) of Fig. 4, the OTA transconductance  $g_m$  is the same than the internal OTC, whereas in part (b) of Fig. 4, the OTC transconductance gain  $g_m$  is given by  $g_m = |\alpha| \cdot g_{mx}$  where  $\alpha$  is the gain of the current Mirror (CM) and it is the same coefficient  $\alpha$  used to define the OTC. The commercial CFOA [6-8] exhibit very low  $R_x$  in BJT technologies compared to CMOS technologies operating at low-power. Consequently, the stability condition could differ in CMOS applications since it is not possible to always consider  $R_x$  very low [6-8].

#### 3. STUDY OF A TWO-STAGE CMOS MILLER OTC

To illustrate the configuration shown in Fig.2 (or Fig.3), a CMOS Miller OTC loaded by the  $C_L$  capacitance is shown in Fig.5. Note that a class AB equivalent output could be constructed by designing an additional high impedance node at the drain of  $M_2$  [16]. All simulation was performed for  $V_{DD}$ =- $V_{SS}$ =1.5V.

Fig.5. A CMOS two-stage Miller OTC.

In Fig.5 M<sub>1</sub> to M<sub>10</sub> (except M<sub>7</sub>) simulate the OTC input stage (nodes in+, in- and Z) and M<sub>11</sub> (biased by M<sub>7</sub>) simulates the NTA (node Z and out). By considering M<sub>1</sub> identical to M<sub>2</sub>, M<sub>3</sub> and M<sub>4</sub>, their respective transconductance gain g<sub>m1</sub>, g<sub>m2</sub>, g<sub>m3</sub>, and g<sub>m4</sub> are identical for a given temperature. At a small-signal amplitude and a low frequency of operation, the AC source-drain current of M<sub>4</sub> is half of the AC current I<sub>x</sub> passing through the node *in*- [18]. Consequently, the corresponding value of  $\alpha$  is  $\alpha$ =+0.5 for this topology.

Table III summarizes the MOS transistor size used for all the PSPICE-BSIM simulations of the circuit in Fig.5 [19]. In Table III, an estimation of the drain and source areas (AD, AS) and perimeters (PD,PS) permits to take into account the MOS junction capacitance effects [20]. The transistor sizes proposed here have been fixed to provide similar transconductance and power consumption than the low power CMOS Miller OTA studied in [21].

DI E 111

| TABLE III                                                            |      |      |              |        |

|----------------------------------------------------------------------|------|------|--------------|--------|

| Transistors sizes and equivalent drain and source areas (AD, AS) and |      |      |              |        |

| perimeters (PD, PS) [16].                                            |      |      |              |        |

| Transistors                                                          | W    | L    | $AD=AS(m^2)$ | PD=PS  |

|                                                                      | (µm) | (µm) |              | (m)    |

| $M_{1},M_{2}$                                                        | 108  | 1.5  | 189E-12      | 110E-6 |

| $M_3,M_4$                                                            | 54   | 1.5  | 94E-12       | 56E-6  |

| $M_5, M_6, M_8, M_9, M_{10}$                                         | 15   | 1.5  | 26E6-12      | 17E-6  |

| M <sub>7</sub>                                                       | 237  | 1.5  | 415E-12      | 240E-6 |

| M <sub>11</sub>                                                      | 154  | 1.5  | 270E-12      | 157E-6 |

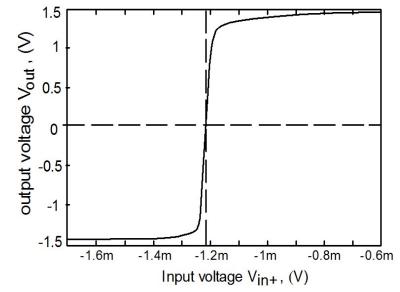

Fig.6. DC characteristics of the two stages Miller OTC in Fig.8,  $V_{in}$ =0V.

| for V <sub>DD</sub> =–V <sub>SS</sub> =1.5V, I <sub>BIAS</sub> =17μA. |                        |                  |  |

|-----------------------------------------------------------------------|------------------------|------------------|--|

| Parameters                                                            | value                  | Units            |  |

| A <sub>OPL</sub>                                                      | 58 000                 | [V/V]            |  |

| THD% (out-                                                            | 6.2                    | %                |  |

| 600mVpp)                                                              |                        |                  |  |

| TRMC (dB)                                                             | 50.3                   | dB               |  |

| G <sub>M</sub>                                                        | 632                    | $[m\Omega^{-1}]$ |  |

| V <sub>OFF</sub> @ in+                                                | -1.2                   | [mV]             |  |

| (Vin-=0)                                                              |                        |                  |  |

| GBW <sup>(1)</sup> (G <sub>0</sub> =1)                                | 94                     | [MHz]            |  |

| (Vout=Vin-)                                                           |                        |                  |  |

| C <sub>M</sub> =50fF                                                  |                        |                  |  |

| Z <sub>IN+</sub>                                                      | 565k Ω //0.7pF         |                  |  |

| Z <sub>IN-</sub>                                                      | R <sub>x</sub> =1829.6 | [Ω]              |  |

| Total power supply                                                    | 988                    | [µW]             |  |

TABLE IV

Main PSPICE simulated characteristics of the Two Stage Miller OTC in Fig.5

for V<sub>DD</sub>=-V<sub>SS</sub>=1.5V. I<sub>BIAS</sub>=17uA.

(1)  $C_M$  is fixed to have no overshoot.

The simulated DC differential characteristic of the operational amplifier is shown in Fig. 6 for  $V_{in}$ =0 and Table IV summarizes the main simulated performances (at this stage  $C_M$  was fixed here from simulation only. The DC input offset of -1.2mV seen in Fig. 6, which is high compared with a classical operational amplifier based on the traditional differential pair of two transistors [14], is mainly due to the diodes made by the transistors  $M_1$  and  $M_3$  since their drain are connected to their gate. In Table IV,  $A_{OPL}$  is the operational amplifier DC open-loop voltage gain and can be written as follows:

$$A_{OPL} = g_0 \cdot g_m \cdot R_Z \cdot R_0 = G_M \cdot R_0 \tag{6}$$

where  $R_0$  is the equivalent output resistance of the operational amplifier, which is approximately equals to the parallel association of drain-source resistors  $R_{DS}$  of  $M_7$  and  $M_{11}$ . AOPL is the open loop voltage gain when not output current occurs, which will not be the case of the unbuffered opamp in Fig.3.

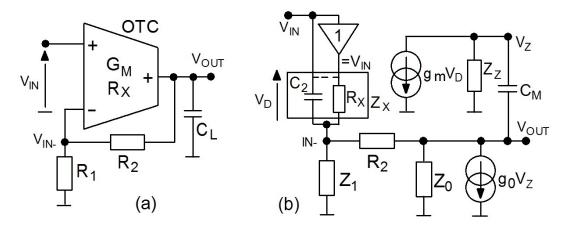

#### 4. THEORETICAL ANALYSIS OF THE NON-INVERTING AMPLIFIER CONFIGURATION

This section presents a theoretical analysis of the non-inverting amplifier using a two-stage Miller OTC (UCFOA). The objective of this section is to present a versatile opamp macro-model and its associated theory. We also aim at being able to estimate the value of the compensation capacitance  $C_M$  for a wanted phase margin and to demonstrate that " $R_x$ " and " $\alpha$ " are the keys design parameters. The non-inverting amplifier configuration is kept in the part (a) of Fig.7 while the part (b) of Fig.7 shows the proposed equivalent macro-model of the non-inverting amplifier. This proposed macro-model takes

into account the main parasitic elements that appear when the OTC presented in the previous section is designed in CMOS technologies.

**Fig.7.** OTC based Non-inverting amplifier **(a)** Circuit **(b)** Proposed equivalent macro-model including the main parasitic elements of the circuits in Fig.8.

The impedances of the OTC macro-model in Fig.7b are defined as follows:

$$Z_X \cong R_X / / C_2 s \tag{7}$$

$$Z_Z = R_Z //C_Z s \tag{8}$$

$$Z_1 = R_1 / / C_1 s (9)$$

$$Z_0 = R_0 / / C_0 s$$

(10)

where  $Z_0$  is the equivalent output impedance of the NTA.

Table V gives the correspondences between the macro-model and the transistors small-signal parameters. Parameters of the macro-model has been extracted from the PSPICE ".AC" simulation of the CMOS configuration around the DC operating point which is fixed in our case by the DC bias current  $I_{\text{bias}}$  and the voltage supplies  $V_{DD}$  and  $V_{SS}$  ( $I_{\text{bias}}=17\mu$ A). Expressions of  $R_Z$  and  $C_Z$  consider that the voltage variations at node *in*- in Fig.5 are very small regarding the voltage variations at node Z (high impedance node). For a transistor  $M_i$ ,  $R_{DSi}$  is the output resistance,  $g_{mi}$  is the gate-source transconductance,  $C_{DBi}$  and  $C_{GSi}$  are respectively the drain-bulk and gate-source equivalent capacitances.

Note that the parasitic resistance in parallel with  $R_1$  has been neglected and we assume that the effect of the time constant ' $R_xC_2$ ' and ' $R_1C_1$ ' are far outside the frequencies of operation. Based on these considerations and after analytical calculation, the voltage transfer function (*closed-loop voltage gain*) is given by:

$$\frac{V_{OUT}}{V_{IN}} = \frac{A_0 \frac{(1 - t_0 s)}{(1 + t_Z s)(1 + t_{02} s)}}{1 + A_0 \frac{(1 - t_0 s)}{(1 + t_Z s)(1 + t_{02} s)} \frac{1}{K_0} (1 + t_X s)}$$

(11)

where:

$$K_0 = 1 + \frac{R_2}{R_1}$$

(12)

$$t_0 = \frac{C_M}{g_0} \tag{13}$$

$$t_{02} = R_{02}(C_M + C_0) \tag{14}$$

$$t_X = \frac{(R_2 + K_0 R_X) \cdot C_M}{\alpha} \tag{15}$$

$$t_Z = R_Z (C_M + C_Z) \tag{16}$$

$$A_0 = \frac{\alpha g_0 R_{02} R_Z}{([R_2 / K_0] + R_X)}$$

(17)

and:

$$R_{02} = (R_0 / / R_2) = \frac{R_0 R_2}{R_0 + R_2}$$

(18)

The analytical calculations given above have been performed considering the following conditions:

- R<sub>x</sub> is non zero

- $R_1/D \ll 1$  and  $[R_1R_X/(DR_2)] \ll 1$  with D=R\_1R\_2+R\_X[R\_1+R\_2]

In (11)  $A_0$  is the DC open loop gain and is different to the DC open-loop gain of the opamp  $A_{OPL}$  given in equation (6) because the resistive feedback consumes a current that could not be neglected. Since the time constant  $t_0=C_M/g_0$  appears at very high frequency, the expression of  $V_{OUT}/V_{IN}$  can be reduced to:

$$\frac{V_{OUT}}{V_{IN}} = \frac{K_{0R}}{1 + \left[\frac{K_0}{A_0}(t_{02} + t_Z) + t_x\right]s + \frac{K_0}{A_0}t_{02}t_Zs^2}$$

(19)

where

$$K_{0R} = A_0 / [1 + \frac{A_0}{K_0}]_{A_0 \to \infty} K_0$$

(20)

Here,  $K_{OR}$  is the effective DC gain of the transfer function and  $K_0=1+(R_2/R_1)$  is the ideal DC gain when  $A_0$  tends to infinity. Equation (19) shows that the non-inverting amplifier operates like a second order low-pass frequency filter for which the Q factor of resonance can be used as follows:

$$\frac{V_{\text{OUT}}}{V_{\text{IN}}} = \frac{K_{\text{OR}}}{1 + \frac{s}{Q\omega_0} + \frac{s^2}{\omega_0^2}} = \frac{K_{\text{OR}}}{1 + \frac{jf}{f_1} - \frac{f^2}{f_0^2}}$$

(21)

with:

$$Q = \frac{f_1}{f_0} = \frac{\sqrt{A_0 K_0 t_{02} t_Z}}{K_0 (t_{02} + t_Z) + A_0 t_X}$$

(22a)

or

$$Q(C_{\rm M}) = \frac{\sqrt{A_0 K_0 R_{02} R_Z (C_{\rm M} + C_0) C_{\rm M}}}{\alpha [K_0 (R_{02} + R_Z) + A_0 (R_2 + K_0 R_{\rm X})] C_{\rm M} + \alpha K_0 (R_{02} C_0 + R_Z C_Z)}$$

(22b)

$$f_{1} \approx \frac{1}{2\pi} \frac{A_{0}}{K_{0}(t_{02} + t_{Z}) + A_{0}t_{x}}$$

(23)

and:

$$\mathbf{f}_0 \approx \frac{1}{2\pi} \sqrt{\frac{\mathbf{A}_0}{\mathbf{K}_0 \mathbf{t}_{02} \mathbf{t}_Z}} \tag{24}$$

The phase margin ( $\Phi_M$ ) of the effective open-loop gain can then be calculated [22], we have:

$$\phi_{\rm M} = \tan^{-1} \left[ \sqrt{\frac{2}{\sqrt{1 + 4Q^2} - 1}} \right]$$

(25)

or

$$\phi_{\rm M} = \tan^{-1} \left[ \sqrt{\frac{2}{\sqrt{1 + \frac{4A_0K_0t_{02}t_Z}{\left[K_0(t_{02} + t_Z) + A_0t_x\right]^2} - 1}}} \right]$$

(26)

Equations (22) and (26) allow to estimate the resonance factor and the phase margin. Note that equation (26) shows that the phase margin ( $\phi_M$ ) is function of  $A_0$  and not of not  $A_{OPL}$

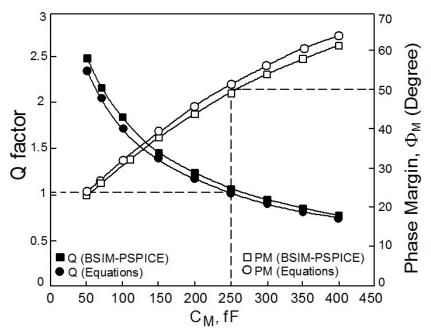

**Fig.8.** Phase margin and Q factor versus  $C_M$  in case of  $G_0$ =6.  $R_2$ =5k $\Omega$ ,  $R_1$ =1k $\Omega$  from BSIM 3V3 simulation and from calculation.

#### **5. SIMULATIONS RESULTS AND DISCUSSIONS**

Most of parameters can be deduced from simulation at the resonance frequency. For this reason, simulations at Q higher than  $1/\sqrt{2}$  help to validate the theoretical approach since the resonance exists and is visible. From PSPICE simulations (macro-model or CMOS-BSIM), the Q factor has been obtained from a coefficient *m* at the frequency of resonance by solving [22]:

$$4mQ^4 - 4Q^2 + 1 = 0 \tag{27}$$

with:

$$m = \left(\frac{K_{OR}}{K_{MAX}}\right)^2$$

(28)

where  $K_{MAX}$  is the maximum voltage gain at the resonance frequency  $f_R$ , and  $K_{OR}$  the simulated DC effective closed loop voltage gain. When Q is higher than  $1/\sqrt{2}$ , the relation between  $f_R$  and  $f_0$  is given by [22]:

$$f_{R} = f_{0} \sqrt{1 - \frac{1}{2Q^{2}}}$$

(29)

and the -3dB bandwidth by:

$$f_{\rm C} = \sqrt{\frac{\left(2Q^2 - 1\right) + \sqrt{8Q^4 - 4Q^2 + 1}}{2Q^2}} f_0$$

(30)

TABLE VEquivalence between the macro-model,  $C_L$  and the transistor small-<br/>signal parameters obtained from PSPICE (Fig.5), $V_{DD}$ =- $V_{SS}$ =1.5V,  $I_{BIAS}$ =17 $\mu$ A.

| $v_{DD} = v_{SS} = 1.5v$ , $I_{BIAS} = 1/\mu A$ . |                                                  |                       |  |

|---------------------------------------------------|--------------------------------------------------|-----------------------|--|

| R <sub>x</sub>                                    | $(g_{m2} + g_{m4})^{-1}$                         | 1829 Ω                |  |

| Rz                                                | $R_{DS4}//R_{DS10}$                              | 1110 k $\Omega$       |  |

| R <sub>0</sub>                                    | R <sub>DS7</sub> //R <sub>DS11</sub>             | 92.6 kΩ               |  |

| <b>g</b> 0                                        | <b>g</b> <sub>m11</sub>                          | 2.65e-3 $\Omega^{-1}$ |  |

| Cz                                                | $C_{\text{DB4}}+C_{\text{DB10}}+C_{\text{GS11}}$ | 1.05 pF               |  |

| C <sub>0</sub>                                    | $C_{DB7}+C_{DB11}+C_{L}$                         | 10.8 pF               |  |

| α                                                 | I <sub>Z</sub> /I <sub>X</sub>                   | 0.39                  |  |

| Gм                                                | $G_{M} \cong g_{0}.g_{m}.R_{Z}$                  | 632 m $\Omega^{-1}$   |  |

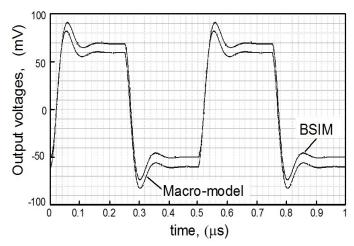

**Fig.9**. Transient output response of the non-inverting OTC with a 2MHz, 20mV peak-to-peak input pulse voltage at node in+,  $G_0=6$ ,  $R_2=5k\Omega$ ,  $R_1=1k\Omega$ ,  $C_M=250$  fF, Q~1.

Fig.8 shows the equivalent Q factor and phase margin versus the capacitor  $C_M$  obtained from the presented theory and from simulation of the CMOS configurations in Fig.5 when  $R_2=5k\Omega$  and  $R_1=1k\Omega$  ( $K_0=6$ ). In Fig. 8, "Equations" label means that Q and  $\phi_M$  have been calculated from equation (26) and by using the parameters of the macro-model given in Table V. Moreover, the Q factor has been computed from the simulated values of the ratio  $m=K_{OR}/K_{MAX}$  and by solving (27) and (28). The values of Q and  $C_M$  extracted from simulation of the macro-model and or computed from equations are very close to the one obtained by simulation of the CMOS configuration using the BSIM models. To underline this accuracy of the proposed macro-model and theory, Fig.9 shows the simulated transient response of the CMOS-BSIM (Fig. 5, Table III) and MACRO-MODEL (part (b) of Fig.7, Table V). Note that the proposed macro-model is valid at AC small signal amplitude only, consequently this simulation of the macro-model shows any DC offset voltage.

Finally Table VI summarizes the main performances of the non-inverting amplifier when the phase margin is around 50° (Q factor around Q=1),  $G_0=6$  with  $R_2=5k\Omega$  and  $R_1=1k\Omega$ . In this case, the

compensation capacitor has been fixed to 250fF (see Fig.8) which corresponds to the one expected in theory. Note that Fig.8 confirms that calculation (theory) and CMOS simulation match very well for different value of  $C_M$  between 50pF and 400pF.

|                                                                                                            |             | I ABLE VI |           |                       |

|------------------------------------------------------------------------------------------------------------|-------------|-----------|-----------|-----------------------|

| Main Performances of the Non-Inverting Amplifier $R_2\!\!=\!\!5\kappa\Omega,R_1\!\!=\!\!1\kappa\Omega$ and |             |           |           |                       |

|                                                                                                            |             | См=250ғF  |           |                       |

|                                                                                                            | Equations   | Macro-    | BSIM      |                       |

|                                                                                                            |             | model     |           |                       |

|                                                                                                            | Theoretical | AC PSPICE | AC PSPICE |                       |

| f <sub>c</sub> (-3dB)                                                                                      | 13.7        | 14        | 14        | [MHz]                 |

| f <sub>R</sub>                                                                                             | 7.69        | 8.11      | 8.11      | [MHz]                 |

| K <sub>MAX</sub>                                                                                           | 7           | 7.18      | 7.18      | [V/V]                 |

| K <sub>OR</sub>                                                                                            | 5.98        | 5.98      | 5.94      | [V/V]                 |

| Q                                                                                                          | 1.02        | 1.06      | 1.07      | -                     |

| Calculation using the theoretical equations                                                                |             |           |           |                       |

| R <sub>02</sub>                                                                                            | 4.74k       |           |           | [V]                   |

| AOPL                                                                                                       | 57.9k       |           |           | [V/V]                 |

| G <sub>M</sub>                                                                                             | 626         |           |           | $[{ m m}\Omega^{-1}]$ |

| A <sub>0</sub>                                                                                             | 2040        |           |           | [V/V]                 |

| $\Phi_{M}$                                                                                                 | 51.5        |           |           | [Deg.]                |

# TABLEVI

#### 6. CONCLUSION

This paper has introduced the operational transconductance conveyor and proposed a study of the non-inverting amplifier based on a CMOS unbuffered current-feedback-amplifier. A precise macromodel has been used and compared with theory and with an equivalent CMOS topology. We have shown that the theoretical approach which consists in the definition of the Q factor allows to set the Miller capacitance with precision, regarding the phase margin. The correlation between the Q factor extracted from simulations and the Q factor computed from theory shows relevance of the proposed approach. We hope that this study and its associated theory using the OTC description will be useful for analog designers, especially for understanding the frequency performances of the operational current feedback amplifiers. Moreover the Operational Transconductance Conveyor (OTC) is an extension of all actual type II current conveyors (CCII, CCCII, diamond transistor).

#### REFERENCES

- [1] Harold S. Black, "Inventing the negative feedback amplifier", IEEE Spectrum, vol. 14, pp. 54-60, Dec. 1977. (50th anniversary of Black's invention of negative feedback amplifier).

- [2] W. Jung: "Amp History", Analog Device, http://www.analog.com/media/en/trainingseminars/design-handbooks/Op-Amp-Applications/SectionH.pdf pp. H1-H70.

- [3] W. G. Jung : "IC Op-Amp Cookbook", by Howard W. Sams & CO., Publisher SAMS 1974.

- [4] J.C Whitaker : "*The Electronics handbook*", second edition, Ed. Taylor & Franci Group, CRC.

- [5] R. Senani, D. Bhaskar, A. K. Singh, V. K. Singh : *"Current Feedback Operational Amplifiers and Their Applications"*, Ed. Springer Science + Business Media New York 2013.

- [6] Texas Instruments: "OPA 860: Wide bandwidth operational transconductance amplifier (OTA) and Buffer", SBOS331C- Revised august 2008, pp.1-27.

- [7] Analog Devices : "AD844", www.analog.com, Rev. F, pp. 1-20.

- [8] Texas Instruments: "OPA 861: Wide bandwidth operational transconductance amplifier (OTA)", SBOS338G - Revised May 2013, pp.1-23.

- [9] Members of the Staff of the Department of Electrical Engineering of the Massachusetts Institute of Technology, Appl. Electron., New York: Wiley, p. 531, 1943.

- [10] J. B. Downey : "Investigation of electronic switches for Analog Computer Applications", M.S. Thesis, University of Arizona, February, 1964.

- [11] David Nelson and Kenneth Saller : "Settling time reduction in wide-band direct-coupled transistor amplifier", US patent n° US4502020, 1985.

- [12] S. Bandyopadhyay1, D. Mukherjee, R. Chatterjee : "Design Of Two Stage CMOS Operational Amplifier in 180nm Technology With Low Power and High CMRR", International Journal of Recent Trends in Engineering & Technology, Vol. 11, June 2014, pp. 239-247.

- [13] J. Silva-Martínez, M. Steyaert, W. Sansen : "High-Performance CMOS Continuous-Time Filters: Design Considerations for OTA-C Integrators and Full CMOS Resistors", Vol. 223, the Springer International Series in Engineering and Computer Science, 1993, pp. 67-119.

- [14] R. M. Thanki, H. R. Sanghani, R. K. Lamba : "Design of Operational Transconductance Amplifier: Analysis of Schematic Circuit and CMOS Layout of OTA", Publisher Lambert Academic Publishing 2011.

- [15] Texas Instruments: "LM13700 Dual operational transconductance amplifier with linearizing diodes and buffers", SNOSBW2F Revised November 2015.

- [16] A. Thanachayanont, S.S. Ngow : *"Class AB VHF CMOS active inductor"*, 2002 45th Midwest Symposium on Circuits and Systems, 2002, MWSCAS-2002, pp. 64-67.

- [17] K.C. Smith, A. Sedra : *"The current conveyor: a new circuit building block"*. Proceeding IEEE CAS, 1968, vol. 56, no. 3, p. 1368-1369.

- [18] A. Fabre, O. Saaid, F. Wiest, F. Boucheron : *"High frequency applications based on a new current-controlled conveyor"*. IEEE Transactions on Circuits and Systems I: Fundamental Theory and Applications, 1996, vol. 43, no. 2, p. 82-91.

- [19] Multi-Project Circuits: "Products: IC Manufacturing : AMS 0.35 C35B4", cmp.imag.fr/product/ic, www.ams.com.

- [20] P. Antognetti, G. Massobrio : "Semiconductor device modeling with spice", Ed. Mc Graw-Hill, New-York 1990.

- [21] F. P. Cortes, E. Fabris, S. Bampi : 'Analysis and design of amplifier and comparators in CMOS 0.35µm technology', Microelectronics Reliability, n°44, ed. Elsevier (2004), pp 657-664

- [22] C. Basso : *"Transient response counts when choosing phase margin"*, Power Electronics Technology, www.powerelectronics.com, November 2008, pp. 18-21.