## Design of pulse synthesizers for the convergence of IR-UWB solutions

R. Vauche, Sylvain Bourdel, E. Muhr, Jean Gaubert, N. Dehaese, F. Hameau, Herve Barthelemy

### ▶ To cite this version:

R. Vauche, Sylvain Bourdel, E. Muhr, Jean Gaubert, N. Dehaese, et al.. Design of pulse synthesizers for the convergence of IR-UWB solutions. 2016 14th IEEE International New Circuits and Systems Conference (NEWCAS), Jun 2016, Vancouver, France. 10.1109/NEWCAS.2016.7604840. hal-01856791

HAL Id: hal-01856791

https://hal.science/hal-01856791

Submitted on 20 Dec 2021

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Design of Pulse Synthesizers for the Convergence of IR-UWB Solutions

R. Vauché\*, S. Bourdel\*\*\*, E. Muhr\*, *Member, IEEE*, J. Gaubert\*, N. Dehaese\*, F. Hameau\*\*, and H. Barthelemy\*, *Member, IEEE*

\* Aix Marseille Université, CNRS, Université de Toulon, IM2NP UMR 7334 Marseille, France \*\*Université Grenoble Alpes, F-38000 Grenoble, France, CEA, LETI, MINATEC Campus, F-38054 Grenoble, France \*\*\*Université Grenoble-Alpes, F-38000 Grenoble, France, IMEP-LAHC, Minatec Campus, 3 Parvis Louis Neel, F-38016

Abstract—This paper presents some techniques to synthesize pulses in the context of IR-UWB. Pulse synthesizers are good candidates when different kinds of pulses are needed to comply with different standards or when the shape of the pulses needs to be modified. Two different approaches are described here. Voltage Controlled Delay Line (VCDL) based pulsers are first described. For this family, two kinds of combiners are presented: differential pairs based and H-bridge based. The second one achieves a larger output dynamic but is limited by the use of the VCDL. A second type of H-bridge based synthesizer using VCO is presented. Using both a VCO and a H-Bridge offers the largest synthesis capabilities. It allows large voltage pulses to be synthesized and the pulse duration is not limited. All proposed architectures has been implemented and their measured performances are given for comparison.

Index Terms— Pulse generation, FCC, Transmitters, Impulse Radio, Ultra-wideband (UWB), Pulse shaping circuit.

#### I. INTRODUCTION

Communication in the UWB band is regulated by the FCC since it has been authorized in 2002 in the 3.1GHz to 10.6GHz frequency band. Several standards have emerged such as the 802.15.4a for PAN applications, the 802.15.4f for asset tracking or the 802.15.6 for WBAN. Dedicated systems have also been developed for localization or biomedical applications but most of these applications needs low power communication systems to operate.

A general trend in communications systems is the convergence of several applications in an unique device. This allows cost reductions and increase the functionality of the devices. To reduce power consumption, functions must be shared by several sub-systems. To do so, these functions must be reconfigurable to meet various requirements. This is especially a bottleneck for RF devices which are often based on passive elements which are not tunable such as inductors. In IR-UWB, reconfigurable front-end means to be able to generate and detect pulses having different shapes, durations and central frequencies. The very wide bandwidth of the systems can be an advantage, especially on the receiver side. Non-coherent receivers are able to detect a large variety of pulses in different frequency bands. By varying the integration

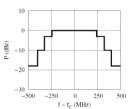

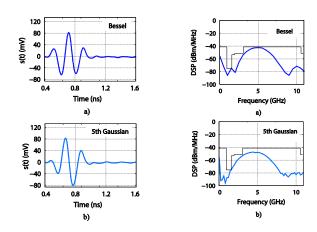

time of the detector; Non-Coherent receivers can detect pulses with different bandwidths and shapes. In coherent receivers, since the correlation is little affected by the pulse shape [1], the most critical point is to control the central frequency and the width of the local pulse used for correlating the received signal. However, this ability is inherent of a correlation receiver and is not a bottleneck. On the transmitter side, the generation of a large variety of pulses is more difficult. The basic parameters to be controlled are the central frequency and the pulse width. To do so, LO switching techniques can be used. It allows the width and the central frequency of the pulse to be controlled. However, adjusting the pulse shape is more difficult whereas it highly affects the spectrum and especially the side lobs which reduces the Adjacent Chanel Power Ratio (ACPR). Several solutions have been proposed to shape the pulse by modulating the pulse magnitude with a shape function [2]. These techniques suffer from a lake of tuning abilities since they are designed to achieve a given pulse shape. Moreover, the performances of the modulator depend on the operating frequency and it is difficult to maintain a constant shape over a very wide frequency band of operation. To overcome this drawback, pulse synthesizing techniques have emerged [3]. By using a pulse synthesizer, it is possible to change the shape of a pulse to comply with different standards which have different requirement regarding the pulse spectrum and the ACPR as shown in Fig. 1.

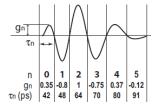

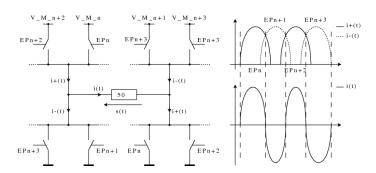

The principle of pulse synthesizing is to control the width  $(\tau_p)$  and the magnitude  $(g_n)$  of each elementary pulse  $(e_n(t))$  that makes the emitted pulse s(t) has given by (1) and represented in Fig. 3.

$$s(t) = \sum_{n=0}^{N-1} g_n . e_n \left( t - \sum_{p=1}^{n-1} \tau_p \right)$$

(1)

In this paper we present several implementations of pulse

Fig. 1. Pulse Shaping for 802.15.4a and 802.15.6

Fig. 3. Principle of pulse synthesizing

synthesizers and we discuss their performances and their limitations. In the first section, synthesizers based on Voltage Controlled Delay Line (VCDL) are presented. In this family of synthesizer, the maximum number (N) of elementary pulses is fixed. This limitation has encouraged the emergence of VCO based pulse synthesizer especially to address lower bandwidths which require a large number of elementary pulses, especially in high frequency bands. These synthesizers will be discussed in section III.

#### II. VCDL BASED PULSE SYNTHESIZER

The first reported work on pulse combining was based on fixed magnitude and width elementary pulse [4]. This preliminary work paves the road to the pulse synthesizing technique.

#### A. Differential pulse combiner based synthesizer

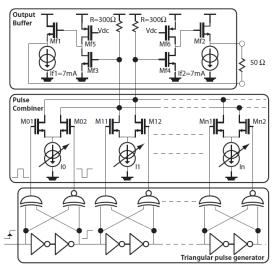

Based on pulse combining techniques, a pulse synthesizer has been proposed [5]. The synthesizer uses a Digital Delay Line (DDL) to propagate a rising edge. The outputs of the delay line are combined to produce delayed complementary square pulses as shown in Fig. 4. The width of the n<sup>th</sup> digital pulse can be modified by changing the propagation delay in the n<sup>th</sup> inverter. The pulses are then combining using current summing in N differential pairs. The outputs of the differential pairs are alternately crossed to achieve positive and negative combination of the elementary pulses. The magnitudes of the elementary pulses are fixed by the DC current in the

Fig. 4. Principle of differential pulse combiner based synthesizer

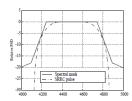

Fig. 2. Synthesized pulse shape with the differential pulse combiner based synthesizer

differential pair. The pulses are then amplified and matched to the antenna with a common source amplifier.

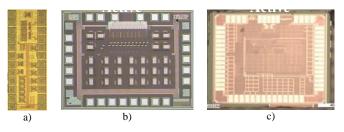

A seven stages synthesizer has been implemented in 130nm CMOS technology. The circuit is represented in Fig. 10.a). The active area is only 0,06mm², it consumes 87.6mW@800MHz and it can achieve several pulse shapes as shown in Fig. 2. This first work demonstrates the possibility of synthesizing different pulse shape but suffer from many drawbacks. The DC power consumption is quite heavy due to the use of differential pair. The performances of the output amplifier highly limit the overall performances. Its limited bandwidth produces distortion and affects the pulse shape. This can be compensated with predistortion methods but the tuning of the synthesizer is not straightforward.

#### B. H-Bridge pulse combiner based synthesizer

To overcome the limitation of the differential pulse combiner, an H-Bridge is proposed to combine the elementary pulses [6]. The principle is presented in Fig. 5. The n<sup>th</sup> elementary pulse (EPn) is used to control the n<sup>th</sup> branch of the bridge. The sign of the current flowing into the charge determines the polarity of the n<sup>th</sup> elementary pulse and the voltage applied to the n<sup>th</sup> branch set the magnitude. The same pulse digital generator is used.

An eight stages synthesizer has been implemented in 130nm CMOS technology. The circuit is represented in Fig. 10.b). The core size is 700um\*400um. Thanks to the H-Bridge

Fig. 5. Principle of H-bridge based synthesizer

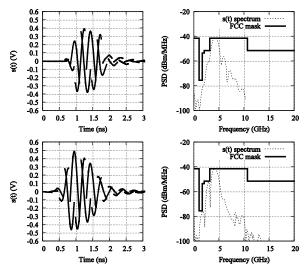

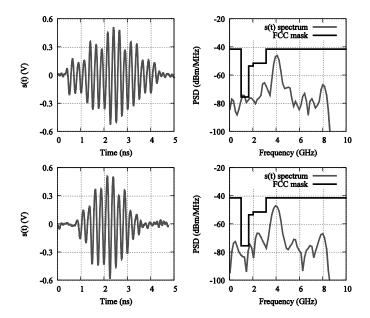

architecture it consumes only 250uW@1MHz and 100uW@0Hz. It can achieves several pulse shapes as shown in Fig. 10 and several frequency bands can be addressed by varying the propagation delay in the VCDL. The maximum output magnitude is 1.8V (resp. 0.9V) when pulses centered on 2.5GHz (resp. 5GHz) are generated.

However this structure is limited by the size of interconnection line required by the H-Bridge output because its length grows with the number of stages which is set by the number of elementary pulses to generate. For the high frequency band, the number of elementary pulses needed to generate a 500MHz pulse can be greater than 60 which makes this architecture unsuitable for the high band of the IEEE 802.15.4a and 802.15.6 standards.

Fig. 6. Synthesized pulse shape with H-Bridge based synthesizer

#### III. VCO BASED PULSE SYNTHESIZER

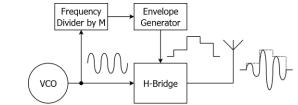

To overcome the limitations of the VCDL based architectures when a high number of elementary pulses is needed, the implementation of a VCO based pulse synthesizers is necessary since it relaxes constraints on the size of the delay line and on the number of the required branches inside the output combining stage. However, this requires at first sight a magnitude control of each elementary pulse. Fortunately, based on an analytical analysis of UWB pulses in time and in frequency domains, it is demonstrated that a discrete symmetrical Gaussian envelope with only 5 samples (N=5) is enough to respect all IEEE frequency masks of 500MHz channels if a margin around 2dB is considered for ACPR [12]. Moreover, as the pulse bandwidth is independent on the central frequency of the targeted channel, it is only necessary to synchronise the sampled envelope generator and the VCO with a programmable frequency divider where the division factor is set according to the targeted channels.

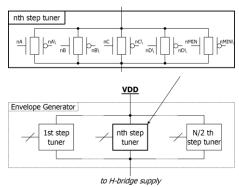

An implementation of this circuit is proposed on Fig. 7. A VCO generates a sinusoidal waveform whose the frequency is equal to the central frequency of the targeted channel. A sampled envelope is synchronously generated according this channel, each sample has also a length multiple of the sinus

half-period. Finally, an H-bridge is used to mix the sinusoidal waveform with the envelope.

To be able to address each channel of IEEE standards, the proposed architecture requires also a VCO which is able to cover all the 3.1GHz-10.6GHz band. Due to the width of the frequency band to address, it is usual to implement two oscillators, one for low band channels and another one for high band channels. However, we demonstrate in [13] that only one VCO designed with a standard 65nm CMOS technology can cover all channels. It is based on a three stages ring oscillator architecture where Current Mode Logic (CML) gates are used instead of usual CMOS gates. The oscillations frequency is also controlled by adjusting the gate source voltages of their active loads and can be started and stopped quasi instantaneously which allow OOK modulation to be obtained. Moreover, it can be put in a low power mode when oscillations are stopped, and is able to directly act as a BPSK modulator.

Fig. 7. Principle of the proposed VCO based pulse synthesizer

Fig. 8. Principle of the discrete envelope generator

To keep simple the control of UWB pulses shape, a sampled envelope generator, which allows each step to be tuned around their nominal values, is proposed here. To set these values, an analytical model of UWB pulses as the Gaussian up-converted pulse introduced in [14] pulse can be used after considering the required bandwidth. However, a degree of freedom on these values must be kept in order to ensure the respect of the targeted frequency masks in case of process, voltage or temperature variations. The proposed implementation is shown in Fig. 8 and used CMOS transmission gates assembled in step tuners to supply a standard H-bridge. As the Gaussian up-converted pulse is symmetrical, only 3 step tuners are required. However, an additional step tuner, which can be turned-off, has been implemented to have a better envelope control abilities. Digital control signals required by these transmission gates are set by a custom serial interface and enable by the frequency

Fig. 9. Synthesized pulse shapes with VCO-based synthesizer

divider. Finally, particular values for step magnitude are fixed by adjusting the size of the transistors of the step tuner.

A prototype of the architecture has been implemented in 65nm CMOS technology from STMicroelectronics. The circuit is represented in Fig. 10.c). Its core area is  $220\mu m$  x  $250\mu m$  and its supply voltage is 1.2V. The VCO based pulse synthesizer has been measured and it shows a peak to peak voltage of 1.1V for low band IEEE channels in the worst case. In this case, its power consumption is between  $600\mu W$  and  $700\mu W@1MHz$ , depending on the configured envelope, when a power gating cycle (turns-on, generates the pulse, and turns-off) of 10ns. Finally, two different pulses for channels 2 and 4 of IEEE 802.15.4 standard are shown in Fig. 9.

#### IV. CONCLUSION

Three pulse synthesizers for IR applications have been presented. The first one uses VCDL and differential pair based combiner. The combiner limits the output dynamic of this structure and the H-Bridge based synthesizer has been proposed. The H-Bridge allows high voltage pulses up to 1,9V to be synthesized but the VCDL avoid the generation of pulses having 500MHz bandwidth. A H-bridge pulse synthesizer using a VCO instead of the VCDL has been proposed to overcome this limitation.

#### REFERENCES

- [1] Wim Vereecken, Michiel S.J. Steyaert, "An I/Q based CMOS Pulsed Ultra Wideband Receiver Front End for the 3.1 to 10.6 GHz Band"; Solid-State Circuits Conference, 2006. ASSCC 2006. IEEE Asian13-15 Nov. 2006 Page(s):75 - 78.

- [2] R. Dokania, X. Wang, S. Tallur, C. Dorta-Quinones, A. Apsel, "An Ultralow-Power Dual-Band UWB Impulse Radio" *IEEE Transactions* on Circuits and Systems II: Express Briefs, Page(s): 541 - 545, vol. 57, no 5, 2010.

- [3] S. Bourdel, Y. Bachelet, J. Gaubert, M. Battista, M. Egels, N. Dehaese, "Low-Cost CMOS Pulse Generator for UWB Systems," Electronic Letters, vol. 43, issue 25, pp. 1425-1427, 6 December 2007.

Fig. 10. Fabricated Pulse Synthesizer: a) differential pair based, b) VCDL and H-bridge Based, c) VCO and H-bridge based.

- [4] H. Kim, D. Park, Y. Joo, "All-digital low-power CMOS pulse generator for UWB system", Electronics LettersI, 25th Nov, Vol. 40, No. 24

- [5] S. Bourdell, R. Vauché2, O. Ramosl, E. Muhrl, J. Gaubertl, N. Dehaesel, H. Barthelemy3, "An Inductorless CMOS UWB Pulse Generator with Active Pulse Shaping Circuit", Ultra Wide Band, IEEE International Conference on, Sept 2013.

- [6] R. Vauche, S. Bourdel, N. Dehaese, O. Fourquin, and J. Gaubert, "Fully tunable UWB pulse generator with zero DC power consumption," IEEE International Conference on Ultra-Wideband, ICUWB, pp. 418–422, 2009

- [7] H. Kim, Y. Joo, "Fifth-derivative Gaussian pulse generator for UWB system," IEEE Radio Frequency Integrated Circuits (RFIC) Symposium 2005, Digest of Papers 2005, pp. 671-674, 12-14 June 2005.

- [8] Yunliang Zhu; Zuegel, J.D.; Marciante, J.R.; Hui Wu; A 0.18 μm CMOS distributed transversal filter for sub-nanosecond pulse synthesis"; Radio and Wireless Symposium, 2006 IEEE; 17-19 Jan. 2006 Page(s):563 566.

- [9] Rui Xu; Jin, Y.; Nguyen, C.; "Power-efficient switching-based CMOS UWB transmitters for UWB communications and Radar systems "Microwave Theory and Techniques, IEEE Transactions on; Volume 54, Issue 8, Aug. 2006 Page(s):3271 - 3277

- [10] Sanghoon Sim; Dong-Wook Kim; Songcheol Hong; A CMOS UWB Pulse Generator for 6–10 GHz Applications Microwave and Wireless Components Letters, IEEE; Volume 19, Issue 2, Feb. 2009 Page(s):83 – 85.

- [11] Phan, A. T.; Lee, J.; Krizhanovskii, V.; Le, Q.; Han, S.-K.; Lee, S.-G.; "Energy-Efficient Low-Complexity CMOS Pulse Generator for Multiband UWB Impulse Radio"; Circuits and Systems I: Regular Papers, IEEE Transactions on; Volume 55, Issue 11, Dec. 2008 Page(s):3552 – 3563.

- [12] E. Muhr, "Design of VCO based CMOS pulse generator for IR-UWB applications", PHD report.

- [13] R. Vauche, E. Muhr, N. Tall, A. Haloua S. Bourdel, J. Gaubert, N. Dehaese, H. Barthelemy, "Ultra-WideBand Voltage Controlled Oscillator with Commutable Phases for BPSK Implementation," IEEE New Circuits and Systems Conference, NEWCAS, pp. 1-4, 2015.

- [14] O. Ramos Sparrow, R. Vauche, N. Dehaese, S. Bourdel, J. Gaubert, I. Ben Amor, E. Muhr, P. Losco and O. Fourquin, "High rate UWB CMOS transceiver chipset for WBAN and biomedical applications," Analog Integrated Circuits and Signal Processing, vol. 81, no. 1, pp. 215-227, July 2014.