Application of the PCB-Embedding Technology in Power Electronics State of the Art and Proposed Development

Cyril BUTTAY<sup>1</sup>, Florent MOREL<sup>1</sup>, Christian MARTIN<sup>1</sup>, Rémy CAILLAUD<sup>2</sup>, Johan LE LESLE<sup>2</sup>, Roberto MRAD<sup>2</sup>, Nicolas DEGRENNE<sup>2</sup>, Stefan MOLLOV<sup>2</sup>

<sup>1</sup>Laboratoire Ampère, Lyon, France <sup>2</sup>Mitsubishi Electric Research Centre Europe, Rennes, France

27/6/18

Introduction

State of the Art of PCB embedding

Proposition – Design Tools for Power Electronics

Conclusions

# Introduction

State of the Art of PCB embedding

Proposition – Design Tools for Power Electronics

Conclusions

## Power electronics – Areas for Progress

- Excellent active devices are now available (SiC, GaN)

- Many topologies introduced over the years;

- Recent changes: multicellular structures

- Integration and Packaging are the main areas for progress

- Reduce size and circuit parasitics, improve thermal management...

- Manage incresed interconnexion density

# PCB Technology

#### Printed Circuit Board is

- Mature

Large range of available design software

- Can be manufactured in large quantities, low price

- Mainly oriented towards microelectronics and low power

- Flexible ► Custom design

- Many configurations possible

- Limited

Poor thermal conductivity

## Introduction

# State of the Art of PCB embedding

# Proposition – Design Tools for Power Electronics

Conclusions

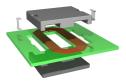

# Why Embedding?

- Optimize thermal management

- Heat sources closer to heatsink

- Dual side cooling

- Improve performance

- Shorter interconnects

- Lower inductances

- Reduce size

- Use substrate volume

- Manage complex interconnects

- Batch process

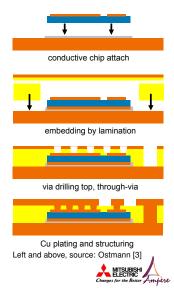

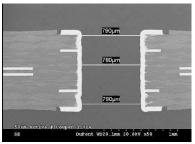

- Most embedding effort on power dies:

- Most power density

- Fastest voltage/current transients

- Requires special finish on dies

- 5-10 µm Cu (not standard)

- Buffer for UV laser

- Also for microetch in plating step

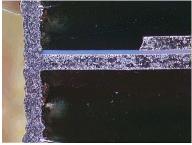

- Backside connexion by sintering or vias

- Sintering compatible with standard die

Vias require Cu finish and adhesive

- Most embedding effort on power dies:

- Most power density

- Fastest voltage/current transients

- Requires special finish on dies

- ► 5-10 µm Cu (not standard)

- Buffer for UV laser

- Also for microetch in plating step

- Most embedding effort on power dies:

- Most power density

- Fastest voltage/current transients

- Requires special finish on dies

- ► 5-10 µm Cu (not standard)

- Buffer for UV laser

- Also for microetch in plating step

- Backside connexion by sintering or vias

- Sintering compatible with standard dies

- Vias require Cu finish and adhesive

### Some alternative techniques

- Stud bumps and machining

- Foam interposer

- Mechanical drilling

Source: Hoene et al. [4]

#### Some alternative techniques

- Stud bumps and machining

- ► Foam interposer

#### Mechanical drilling

Source: Hoene et al. [4]

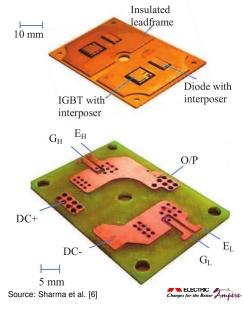

Source: Pascal et al. [5]

### Some alternative techniques

- Stud bumps and machining

- Foam interposer

- Mechanical drilling

Source: Hoene et al. [4]

Source: Pascal et al. [5]

# **Embedding of Formed Components – Capacitors**

Source: Dupont [7]

Source: Andresakis [8]

- introduction of a capacitive layer in the stack-up

- ► thin layer (8–25 µm)

- ▶ high permittivity (e.g. BaTiO<sub>3</sub> filler)

- single layer plane capacitor

- → low capacitance density

- → limited voltage strength

- ►  $\approx$  1 nF cm<sup>-2</sup> for 100 V rating

- more suited to GHz-range decoupling than to power electronics

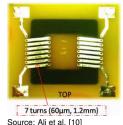

# **Embedding of Formed Components – Inductors**

#### **Magnetic Layer**

- ► Relies on magnetic/polymer film → Low  $\mu_r$

- Limited to 10 100 W

Source: Waffenschmidt et al. [9]

#### Planar magnetic components

- Very common, but not really embedded

- High performance

- Compatible with low (W) or high power (kW)

### Embedded core

- Strong industrial development (Murata, AT&S, Würth)

- Currently limited to low power (W)

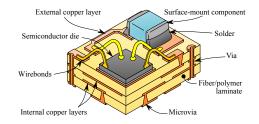

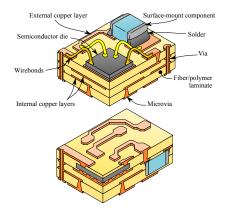

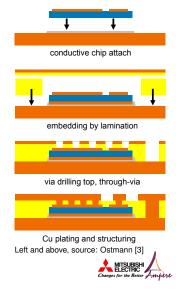

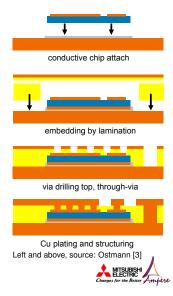

## **Embedding of Inserted Components**

#### Soldered components:

- Suits most Surface-Mount Devices

- Connexions with regular vias

#### Vias to components:

- Requires components with Cu finish

- More compact (vias on components)

Source: Ostmann [3]

## **Embedding of Inserted Components**

#### Soldered components:

- Suits most Surface-Mount Devices

- Connexions with regular vias

#### Vias to components:

- Requires components with Cu finish

- More compact (vias on components)

#### For power electronics

- Embedding of "large" capacitors (1 µF range)

- Embedding of gate driver ICs and peripheral components, control

Source: Ostmann [3]

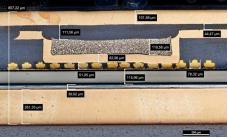

## Thermal Management of Embedded Components - 1

- Poor thermal conductivity of FR4 compared to ceramics (1-7 W m<sup>-1</sup> K<sup>-1</sup> vs 150 W m<sup>-1</sup> K<sup>-1</sup> for AIN)

- ▶ In theory better breakdown field ( $\approx$  50 kV mm<sup>-1</sup> vs. 20 kV mm<sup>-1</sup>)

## Thermal Management of Embedded Components - 1

- Poor thermal conductivity of FR4 compared to ceramics (1-7 W m<sup>-1</sup> K<sup>-1</sup> vs 150 W m<sup>-1</sup> K<sup>-1</sup> for AIN)

- ▶ In theory better breakdown field ( $\approx 50 \text{ kV mm}^{-1} \text{ vs. } 20 \text{ kV mm}^{-1}$ )

#### To improve through-plane heat conduction:

► Micro-vias (electrically conductive), Filled cores (e.g. alumina)

## Thermal Management of Embedded Components - 1

- Poor thermal conductivity of FR4 compared to ceramics (1-7 W m<sup>-1</sup> K<sup>-1</sup> vs 150 W m<sup>-1</sup> K<sup>-1</sup> for AIN)

- ► In theory better breakdown field ( $\approx 50 \text{ kV mm}^{-1} \text{ vs. } 20 \text{ kV mm}^{-1}$ )

- To improve through-plane heat conduction:

- ► Micro-vias (electrically conductive), Filled cores (e.g. alumina)

- To increase in-plane heat conduction:

- Thicker copper, Anisotropic layers (Graphite), Dual-phase

Source: left: Liew et al. [11]; right: Silvano et al. [12]

- Temperature-related issues

- Rapid degradation above 190 °C

- Hydrocarbon, polyimide-based PCBs resistant up to 250 °C

Thermal cycling issues

CTE of PCBs much higher than ceramic or semiconductor

Availability of low-CTE materials

Other PCB-specific issues

moisture absorption,

conductive anodic filaments.

→ No showstopper identified yet!

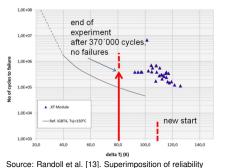

power modules

data for dies in PCB on Infineon's results for standard

Source: Perrin et al. [14]. Left: standard FR4, right: low-CTE. Magnetic core embedded, after 1000 thermal cycles (-50/200 °C) Temperature-related issues

- Rapid degradation above 190 °C

- Hydrocarbon, polyimide-based PCBs resistant up to 250 °C

- Thermal cycling issues

- CTE of PCBs much higher than ceramic or semiconductor

- Availability of low-CTE materials

- → lacks data on large components

Other PCB-specific issues

moisture absorption,

conductive anodic filaments

No showstopper identified yet!

data for dies in PCB on Infineon's results for standard

Source: Perrin et al. [14]. Left: standard FR4, right: low-CTE. Magnetic core embedded, after 1000 thermal cycles (-50/200  $^\circ\text{C})$

Temperature-related issues

- Rapid degradation above 190 °C

- Hydrocarbon, polyimide-based PCBs resistant up to 250 °C

- Thermal cycling issues

- CTE of PCBs much higher than ceramic or semiconductor

- Availability of low-CTE materials

- → lacks data on large components

- Other PCB-specific issues

- moisture absorption,

- conductive anodic filaments...

- No showstopper identified yet!

data for dies in PCB on Infineon's results for standard

Source: Perrin et al. [14]. Left: standard FR4, right: low-CTE. Magnetic core embedded, after 1000 thermal cycles (-50/200  $^\circ C)$

Temperature-related issues

- Rapid degradation above 190 °C

- Hydrocarbon, polyimide-based PCBs resistant up to 250 °C

- Thermal cycling issues

- CTE of PCBs much higher than ceramic or semiconductor

- Availability of low-CTE materials

- → lacks data on large components

- Other PCB-specific issues

- moisture absorption,

- conductive anodic filaments...

- ➔ No showstopper identified yet!

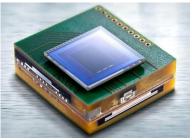

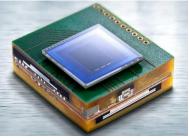

## Conclusions on Embedding Technology

#### **Application to Power Electronics**

- Many components can be embedded

- Dies require Cu finish

- Large components?

- Acceptable thermal performance

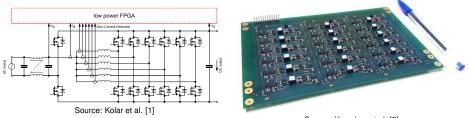

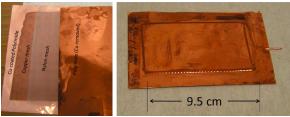

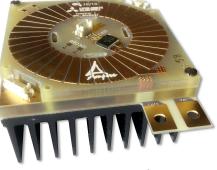

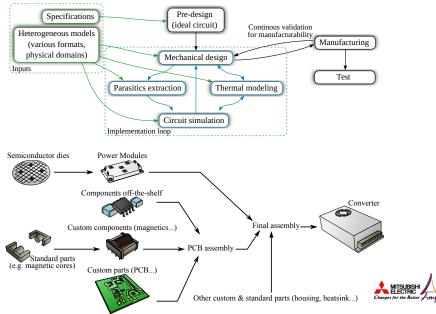

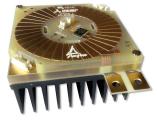

SiC PFC Cell, 750 W, PCB size  $7 \times 7 \times 1$  cm<sup>3</sup>. SiC dies, gate driver circuit, PFC inductor and temperature sensors embedded in PCB.

# Conclusions on Embedding Technology

#### **Application to Power Electronics**

- Many components can be embedded

- Dies require Cu finish

- Large components?

- Acceptable thermal performance

### **Open questions**

- ► Find the sweet spot:

- Embedding power dies only?

- Embed everything?

- Or somewhere in-between?

- Are flat converters desirable?

- How to design for embedding?

SiC PFC Cell, 750 W, PCB size  $7 \times 7 \times 1$  cm<sup>3</sup>. SiC dies, gate driver circuit, PFC inductor and temperature sensors embedded in PCB.

## Introduction

# State of the Art of PCB embedding

# Proposition – Design Tools for Power Electronics

Conclusions

17/28

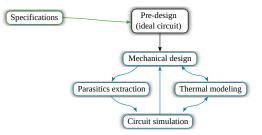

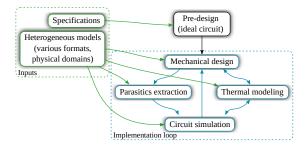

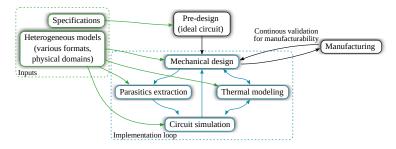

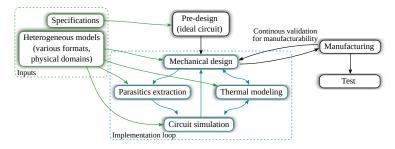

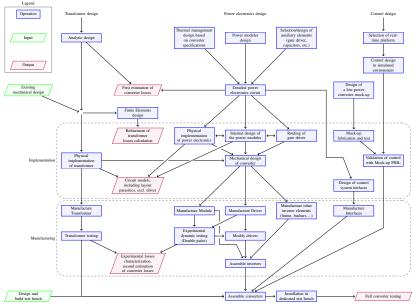

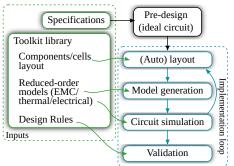

## Design in Power Electronics - Real-case example

Source: Supergrid Institute, submitted article

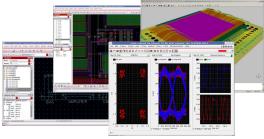

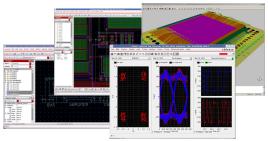

## **Design in Microelectronics**

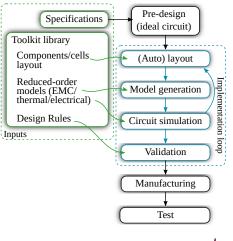

#### Integrated software for

- Circuit design

- Routing

- Simulation

- Mask generation...

Source: Cadence

# **Design in Microelectronics**

Integrated software for

- Circuit design

- Routing

- Simulation

- ► Mask generation...

Source: Cadence

Why is it not available in power electronics?

- powerful financial incentive for virtual prototyping

- ► A 45 nm mask set costs ≈ 2 M\$ (source: Electronic design, 2009)

- Limited technology variations

- Most of the circuit is monolithic

- No flexibility allowed in technology configuration

- Manufacturers supply a "design toolkit" describing the technology

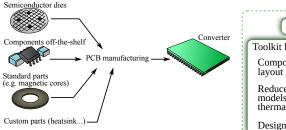

- Rationalized manufacturing

- → Reduce design variability

- Design Toolkit for simulation and validation

- → Design for manufacturing

- Rationalized manufacturing

- ➔ Reduce design variability

- Design Toolkit for simulation and validation

- → Design for manufacturing

- Rationalized manufacturing

- → Reduce design variability

- Design Toolkit for simulation and validation

- → Design for manufacturing

- Rationalized manufacturing

- → Reduce design variability

- Design Toolkit for simulation and validation

- → Design for manufacturing

- Rationalized manufacturing

- ➔ Reduce design variability

- Design Toolkit for simulation and validation

- → Design for manufacturing

20/28

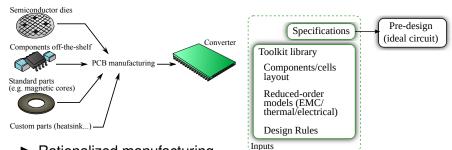

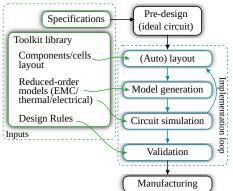

- ► Fully custom designs, as opposed to modular

- Automatic Design for Manufacturing (fabless approach)

- Single, well controlled technology:

Qualification: of technology rather than products

Scalability: same technology for test and production runs

Prototyping: share panels across projects

- ➔ Basically all the usual features in IC design.

- Reduced choice of components

- Must be in the toolkit library

- Reduced design flexibility

- The fewer degrees of freedom, the simpler the toolkit

- Fully custom designs, as opposed to modular

- ► Automatic **Design for Manufacturing** (*fabless* approach)

- Single, well controlled technology:

Qualification: of technology rather than products

Scalability: same technology for test and production runs

Prototyping: share panels across projects

- ➔ Basically all the usual features in IC design.

- Reduced choice of components

- ► Reduced design flexibility

- The fewer degrees of freedom, the simpler the toolkit.

- Fully custom designs, as opposed to modular

- Automatic Design for Manufacturing (fabless approach)

- Single, well controlled technology:

Qualification: of technology rather than products

Scalability: same technology for test and production runs

Prototyping: share panels across projects

- ➔ Basically all the usual features in IC design.

- Reduced choice of components

- Must be in the toolkit library

- Reduced design flexibility

- The fewer degrees of freedom, the simpler the toolkit.

- Fully custom designs, as opposed to modular

- Automatic Design for Manufacturing (fabless approach)

- Single, well controlled technology:

Qualification: of technology rather than products

Scalability: same technology for test and production runs

Prototyping: share panels across projects

- → Basically all the usual features in IC design.

- Reduced choice of components

- Must be in the toolkit library

- Reduced design flexibility

- The fewer degrees of freedom, the simpler the toolkit.

- Fully custom designs, as opposed to modular

- Automatic Design for Manufacturing (fabless approach)

- Single, well controlled technology:

Qualification: of technology rather than products

Scalability: same technology for test and production runs

Prototyping: share panels across projects

- → Basically all the usual features in IC design.

## At what cost?

- Reduced choice of components

- Must be in the toolkit library

- Reduced design flexibility

- The fewer degrees of freedom, the simpler the toolkit

- Fully custom designs, as opposed to modular

- Automatic Design for Manufacturing (fabless approach)

- Single, well controlled technology:

Qualification: of technology rather than products

Scalability: same technology for test and production runs

Prototyping: share panels across projects

- → Basically all the usual features in IC design.

## At what cost?

- Reduced choice of components

- Must be in the toolkit library

- Reduced design flexibility

The fewer degrees of freedom, the simpler the toolkit

- Fully custom designs, as opposed to modular

- Automatic Design for Manufacturing (fabless approach)

- Single, well controlled technology:

Qualification: of technology rather than products

Scalability: same technology for test and production runs

Prototyping: share panels across projects

- → Basically all the usual features in IC design.

## At what cost?

- Reduced choice of components

- Must be in the toolkit library

- Reduced design flexibility

- ► The fewer degrees of freedom, the simpler the toolkit

#### Better design tools

- Large choice of existing software (PCB layout, circuit simulators, EM modeling)

- Need to identify suitable modelling approach (speed/accuracy trade-off)

- Software "glue" required for automatic model generation

- Define design rules for PCB embedding

Required for automatic design validation

Long experimental work required.

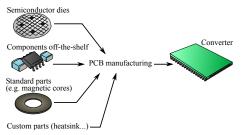

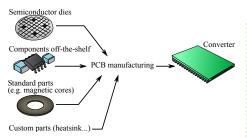

The impact on the supply chain must also be assessed

#### Better design tools

- Large choice of existing software (PCB layout, circuit simulators, EM modeling)

- Need to identify suitable modelling approach (speed/accuracy trade-off)

- Software "glue" required for automatic model generation

## Define design rules for PCB embedding

- Required for automatic design validation

- Long experimental work required.

The impact on the supply chain must also be assessed

#### Better design tools

- Large choice of existing software (PCB layout, circuit simulators, EM modeling)

- Need to identify suitable modelling approach (speed/accuracy trade-off)

- Software "glue" required for automatic model generation

## Define design rules for PCB embedding

- Required for automatic design validation

- Long experimental work required.

- The impact on the supply chain must also be assessed

## Introduction

# State of the Art of PCB embedding

# Proposition – Design Tools for Power Electronics

Conclusions

# Conclusions – Exploiting the PCB Embedding

- PCB embedding is very promising

- Provides a single, unified techology for power electronics (W to 10's of kW range)

- High performance

- Scalable, reasonable cost...

- Situation comparable to microelec. in the 70's

- Many technologies available, but no standard

- No separation between design and manuf.

- ➔ Need for Design Rules and uniformization

- Large effort required on the design tools

- Allow Design for Manufacturing

- Objective: efficient virtual prototyping

# **Bibliography I**

- J. W. Kolar, F. Krismer, and H.-P. Nee, "What are the big challenges in power electronics?," in *Proceedings of CIPS*, (Nüremberg), 2014.

L. Kerachev, A. Andreta, Y. Lembeye, and J.-C. Crébier, "Generic approach for design, configuration and control of modular converters," in *International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management*, (Nuremberg), pp. 212 – 219, VDE Verlag, May 2017.

A. Ostmann, "Evolution and future of embedding technology," in *IMAPS/NMI* workshop "disappearing die – embed your chips", 2016.

- E. Hoene, "Ultra Low Inductance Package for SiC," in *ECPE workshop on power boards*, ECPE, 2012.

Y. PASCAL, D. Labrousse, M. Petit, S. LEFEBVRE, and F. Costa, "PCB-Embedding of Power Dies Using Pressed Metal Foam," in *Power Conversion and Intelligent Motion (PCIM) Europe*, (Nuremberg, Germany), June 2018.

A. B. Sharma, D. Paul, M. Kreck, Y. Rahmoun, P. Anders, M. Gruber, and T. Huesgen, "PCB embedded power package with reinforced top-side chip contacts," in *2016 6th Electronic System-Integration Technology Conference (ESTC)*, pp. 1–5, Sept 2016.

# **Bibliography II**

Dupont., "Dupont interra embedded passives materials – interra HK04 planar capacitor laminate," tech. rep., Dupont, 2007.

J. Andresakis, "Embedded Capacitors," presentation, Oak-Mitsui Technologies, Nov. 2005.

- E. Waffenschmidt, B. Ackermann, and J. A. Ferreira, "Design Method and Material Technologies for Passives in Printed Circuit Board Embedded Circuits," *IEEE Transactions on Power Electronics*, vol. 20, pp. 576–584, May 2005.

- M. Ali, E. Labouré, F. Costa, and B. Revol, "Design of a hybrid integrated EMC filter for a DC–DC power converter," *IEEE Transactions on Power Electronics*, vol. 27, no. 11, pp. 4380–4390, 2012.

L.-A. Liew, C.-Y. Lin, R. Lewis, S. Song, Q. Li, R. Yang, and Y. Lee, "Flexible thermal ground planes fabricated with printed circuit board technology," *Journal of Electronic Packaging*, vol. 139, no. 1, pp. 011003–011003–10, 2017.

J. S. de Sousa, P. Fulmek, M. Unger, P. Haumer, J. Nicolics, M. A. Ras, and D. May, "Enhanced in-plane heat transport in embedded mini heat pipes PCB," *International Symposium on Microelectronics*, vol. 2017, no. 1, pp. 000130–000134, 2017.

R. Randoll, W. Wondrak, and A. Schletz, "Lifetime and manufacturability of integrated power electronics," *Microelectronics Reliability*, vol. 64, pp. 513 – 518, 2016.

Proceedings of the 27th European Symposium on Reliability of Electron Devices, Failure Physics and Analysis.

R. Perrin, B. Allard, C. Buttay, N. Quentin, W. Zhang, R. Burgos, D. Boroyevich, P. Preciat, and D. Martineau, "2 MHz high-density integrated power supply for gate driver in high-temperature applications," in *Applied Power Electronics Conference and Exposition (APEC)*, (Long Beach, United States), Mar. 2016.

# Thank you for your attention

cyril.buttay@insa-lyon.fr

This work was funded by Mitsubishi Electric Research Centre Europe and the French Agency for Technology and Research (ANRT). The authors thank Mr. Jean-Christophe CRÉBIER and Yves LEMBEYE, from G2ELab for their fruitful discussions.