# Spintronic Devices as Key Elements for Energy-Efficient Neuroinspired Architectures

Nicolas Locatelli, Adrien F Vincent, Alice Mizrahi, Joseph S Friedman, Damir Vodenicarevic, Joo-Von Kim, Jacques-Olivier Klein, Weisheng Zhao, Julie Grollier, Damien Querlioz

## ▶ To cite this version:

Nicolas Locatelli, Adrien F Vincent, Alice Mizrahi, Joseph S Friedman, Damir Vodenicarevic, et al.. Spintronic Devices as Key Elements for Energy-Efficient Neuroinspired Architectures. Design, Automation and Test in Europe, Mar 2015, Grenoble, France. 10.7873/DATE.2015.1117. hal-01827047

HAL Id: hal-01827047

https://hal.science/hal-01827047

Submitted on 1 Jul 2018

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Spintronic Devices as Key Elements for Energy-Efficient Neuroinspired Architectures

Nicolas Locatelli\*, Adrien F. Vincent\*, Alice Mizrahi\*<sup>‡</sup>, Joseph S. Friedman\*, Damir Vodenicarevic\*, Joo-Von Kim\*, Jacques-Olivier Klein\*, Weisheng Zhao\*<sup>†</sup>, Julie Grollier<sup>‡</sup>, and Damien Querlioz\*

\*Institut d'Electronique Fondamentale, Univ. Paris-Sud, CNRS, 91405 Orsay, France

Email: nicolas.locatelli@u-psud.fr, damien.querlioz@u-psud.fr

<sup>†</sup>Spintronics Interdisciplinary Center, Beihang University, Beijing, 100191, China

<sup>‡</sup>Unite Mixte de Physique CNRS/Thales and Universite Paris-Sud, 1 Ave. A. Fresnel, 91767 Palaiseau, France

Abstract-Processing the current deluge of data using conventional CMOS architectures requires a tremendous amount of energy, as it is inefficient for tasks such as data mining, recognition and synthesis. Alternative models of computation based on neuroinspiration can prove much more efficient for these kinds of tasks, but do not map ideally to traditional CMOS. Spintronics, by contrast, can bring features such as embedded nonvolatile memory and stochastic and memristive behavior, which, when associated with CMOS, can be key enablers for neuroinspired computing. In this paper, we explore different works that go in this direction. First, we illustrate how recent developments in embedded nonvolatile memory based on magnetic tunnel junctions (MTJs) can provide the large amount of nonvolatile memory required in neuro-inspired designs while avoiding Von Neumann bottleneck. Second, we show that recently developed spintronic memristors can implement artificial synapses for neuromorphic systems. With a more groundbreaking design, we show how the probabilistic writing of single MTJ bits can efficiently replace multi-level weighting for some classes of neuroinspired architectures. Finally, we show that a special class of MTJs can exhibit the phenomenon of stochastic resonance, a strategy used in biological systems to detect weak signals. These results suggest that the impact of spintronics extends beyond the traditional standalone and embedded memory markets.

#### I. INTRODUCTION

Emerging applications of electronics, such as Big Data and ubiquitous sensing, call for systems capable of handling large quantities of natural data with low power consumption. The relevant tasks, which rely on machine learning and can be qualified as "cognitive", have been summarized as recognition, mining and synthesis [1]. These tasks do not map perfectly to traditional computers; most machine learning algorithms suffer heavily from the von Neumann bottleneck. In recent years, many researchers have advocated a bioinspired computing paradigm as a solution for implementing cognitive tasks with high energy efficiency [2]–[5]. However, CMOS does not provide all features necessary for ideal implementation of bioinspired architectures. In particular, fast and compact embedded nonvolatile memory and efficient random number generation are not available.

In parallel, spintronics (spin electronics) has emerged as a major advance in micro and nanoelectronics since the Nobel prize of Albert Fert and Peter Grünberg in 2007. Spintronics exploits the intrinsic magnetic moment (spin) of electrons in addition to their electrical charge to achieve novel features.

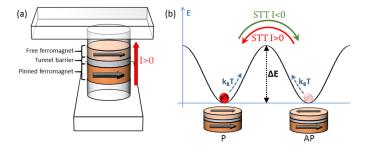

Fig. 1. (a) Schematics of a MTJ. (b) Illustration of Spin transfer torqie and thermal switching in a MTJ.

The prominent example is the magnetic tunnel junction, the flagship structure of spintronics, which exhibits a wide variety of complex and tunable behaviors [6], particularly a fast, compact and reliable binary nonvolatile memory. This memory function is envisioned for diverse applications as standalone and embedded memory, or in original logic-in-memory circuits [7]. Additionally, the features provided by spintronics share some features with biology [8]. Much recent work has investigated the use of nanotechnology for bioinspired computing [9]–[13], by mimicking biology's use of nanoscale elements. In this paper, we show how spintronics fits specially well in this vision, and may complement CMOS ideally to provide the features necessary for emerging neuroinspired applications.

Here, after introducing several features that spintronics can bring to CMOS, we present ideas for using spintronics in bioinspired design. A form of hybrid logic differentiating between volatile and nonvolatile signals can implement cognitive algorithms. Spintronics devices may also be used as "synapses". Finally, they may be used as stochastic oscillators that synchronize in a bioinspired way based on the phenomenon of "stochastic resonance"

#### II. SPINTRONIC BUILDING BLOCKS

Exploiting the spin degree of freedom of electrons permits numerous novel device features. Most spintronics devices are based on a magnetic tunnel junction structure (MTJ, Figure 1(a)). A MTJ consists in a patterned stack composed of layered magnetic and nonmagnetic materials. An MTJ consists of a patterned stack composed of layered magnetic

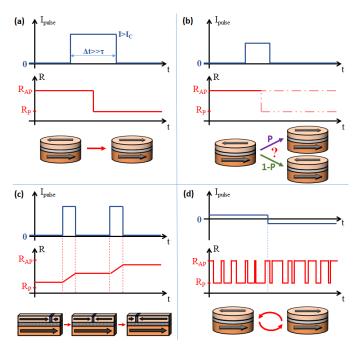

Fig. 2. Schematics of some spintronic building blocks. (a) MTJ used as binary nonvolatile memory. (b) MTJ used as a stochastically programmed nonvolatile memory. (c) Spintronic memmristor exploiting domain wall motion. (d) Superparamagnetic MTJ used as stochastic oscillator.

and nonmagnetic materials. It features a first nanomagnet with a pinned magnetization (fixed or pinned layer), and a second nanomagnet (free layer) with a magnetization that can be parallel (P) or antiparallel (AP) to the magnetization of the fixed layer. These two nanomagnets are separated by a thin tunnel barrier. The magnetization of the nanomagnets can be either in-plane, as illustrated in Figure 1, or perpendicular to the plane, in more recent designs.

Due to spin transport physics, the electrical resistance of the P and AP state differ (P is low resistance, AP is high resistance). This difference is quantified by the tunnel magnetoresistance ratio (TMR):

$$TMR = \frac{R_{AP} - R_P}{R_P}. (1)$$

In typical devices, the TMR ranges between 30% and 150%. A magnetic field can be used to switch the state of the MTJ between the P and AP states. The first generation of magnetic random access memory (MRAM) was based on this principle; however, this leads to parasitic crosstalk between MTJs when the technology is scaled. A second spin transport effect, called "spin transfer torque", allows the MTJ state to be switched using an electrical current flow through the MTJ. A positive current switches the MTJ from the AP to the P state, while a negative current switches the MTJ from the P to the AP state (Figure 1(b), Figure 2(a)). This is the basis of to the second generation of MRAM: Spin transfer torque MRAM (STT-MRAM) [14]. STT-MRAM provides compact nonvolatile memory with outstanding endurance and fast write speeds (in the range of 10ns) that can be embedded at the

core of CMOS chips. Recent results suggest that writing speed could scales in the ns range [15], providing a relatively "universal" memory that is fast, reliable and nonvolatile.

A unique feature of MTJ-based memory is the stochastic nature of its switching (Figure 2(b)) [14], [16], [17]. This effect results from thermal effects in the MTJ switching process, which is well-studied and can be modeled accurately [18], [19]. When a short programming pulse is applied to a MTJ, there is only a probability of switching the MTJ. Therefore, we need to use long programming pulses to switch MTJs reliably. On the other hand, this stochastic switching make MTJs true nanoscale random number generator, as has been proved experimentally in Ref. [20].

While simple MTJs of the form of Figure 1 possess only two stable memory states, variations are currently developed to feature multibit information storage. This spintronic "memristor" behavior is produced by engineering the MTJ such that the free layer's magnetization is divided into two domains: one domain is aligned to the fixed layer, the other domain is antiparallel to the fixed layer (Figure 2(c)). The domain position can be shifted using current pulses. This device has for example been proposed in Refs. [21], [22], and a demonstration has been realized experimentally in Ref. [23].

Another original application of MTJs is to allow switching in response to thermal noise, without applying a magnetic field or an electrical current (Figure 2(d)). These so-called super-paramagnetic junctions behave as stochastic oscillators with electrical resistance states analogous to a telegraph noise signal, with properties determined by the sizing of the MTJ. We will show that this feature of controlled telegraph noise can be useful for groundbreaking computing applications.

Finally, it should be mentioned that MTJs can be used in many additional systems not discussed in the present work: e.g. as a magnetic field detector, microwave oscillator and receiver, or spin wave emitter [6]. In summary, MTJs are simple compact device with a wide range of potential applications due to their rich physics. The rest of this paper discusses techniques for integrating spintronic devices with CMOS circuits to develop efficient neuroinspired architectures.

# III. NON-VOLATILE LOGIC GATES FOR COGNITIVE COMPUTING

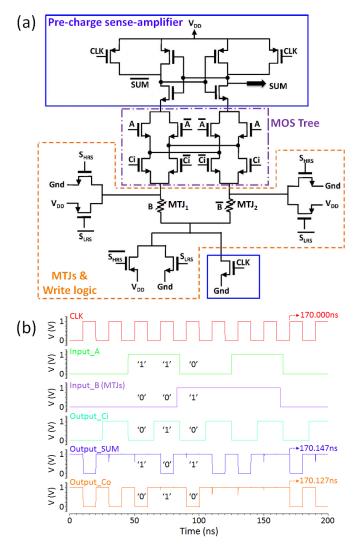

Magnetic tunnel junctions constitute a CMOS-compatible technology and can be embedded at the core of CMOS. This allows considering hybrid circuits that benefit from the advantages of both CMOS and spintronics, as its nonvolatility. An example of such approach is presented in [24] and Figure 3. Zhao et al. propose logic gates where some inputs are traditional volatile CMOS signals, and some inputs are stored in nonvolatile MTJs. Ref. [24] introduces a comprehensive methodology to design such gates. Figure 3 presents a full-adder designed using this methodology. The A and carry (Ci) inputs are volatile, the B input is nonvolatile, while outputs SUM and carry (C0) are volatile. The nonvolatile input B is stored in complementary MTJs, and can be changed by a standard MTJ write circuit. The outputs of the circuit are

Fig. 3. (a) Schematic of the part of a hybrid volatile/nonvolatile full adder generating the output SUM. The full schematic appears in Ref. [24]. The variable resistors represents MTJs. (b) Circuit simulation of this full adder using a 40 nm commercial technology design kit and the compact model of a realistic MTJ (data adapted from [18]).

read using a Precharge Sense Amplifiers (PCSA), which are fast and energy-efficient MTJ read circuit. The volatile inputs are inserted between the non volatile input and the PCSAs as part of a MOS tree that alters the MTJ read operation and implements the actual adder logic function.

Interestingly, once laid out and even including all the write circuitry for input B, the circuit is slightly more compact than a conventional CMOS full adder  $(18\mu m^2 \text{ vs. } 20\mu m^2 \text{ in a 40nm}$  technology). When input B is not changed, the circuit has nearly same delay (90ps vs. 75ps) and power consumption  $(2.0\mu W \text{ vs. } 2.2\mu W)$  as a conventional CMOS full adder [24]. However, changing input B requires more time and power, as it consists in programming a MTJ.

This class of circuit is therefore useful when some inputs are fundamentally volatile, and some inputs are parameters that are rarely changed and need to be nonvolatile. Making such a separation in a general purpose computer is a difficult task. However, for a machine learning algorithm, this separation is intuitive. Machine learning algorithms largely differentiate between model parameters and actual inputs to be processed. For example, in a deep network, neuron states need to be updated frequently, while synaptic weights are not changed once the network has been trained. Putting the parameters as nonvolatile inputs could lead to a machine learning specialized circuit that avoids issues related to von Neumann bottleneck and is instant on/off.

#### IV. SPINTRONIC DEVICES AS ARTIFICIAL SYNAPSES

#### A. Multilevel Synapses

In recent years, many research groups have focused on using memristive devices as synapses. Synapses are the connections in the brain, and also feature a form of long term memory: a synapse possesses an analog synaptic weight that modulates the transmission between neurons. Synapses are a fundamental element in neuroinspired systems; however, CMOS implementations of learning-capable synapses are volatile, and are not compact [25], [26]. Memristive devices are nonvolatile resistive memories that usually features multilevel memory, and possess the capability to naturally emulate some properties of synapses, such as the capability of learning with "spike timing dependent plasticity" [9]–[13], [27]. They might therefore implement ideally the synapses of neuromorphic systems.

The spintronic memristor introduced in section 2 can naturally implement this vision, and this idea is currently widely investigated [21]–[23]. A feature of spintronic memristor with regards to other memristive devices is that the memory states are well defined by domain wall pinning, while they are analog (and harder to control) in other technologies. Spintronic memristors, with programming times in the range of nanoseconds, also constitute a fast technology. Additionally, the separation between low and high resistance states is typically smaller for spintronic memristor than for other technologies. This might require the use of adapted differential circuits for read operation.

#### B. Stochastic Synapses

As mentioned in section 2, a distinctive feature of MTJs is stochastic switching [14], [16], [18]. This usually constitutes a nightmare for circuit engineers, which calls for long programming pulses or specialized circuits solutions such as self-enabled programming [28]. However, when using MTJs as synapses this can be turned into a useful feature: stochastic programming of a memory device can be a particularly efficient way to implement stochastic learning rules, which have proven useful in some situations [29], [30]. Synapses programmed using stochastic learning rules need not necessarily be multilevel, and we can therefore use standard binary MTJs as synapses using this concept.

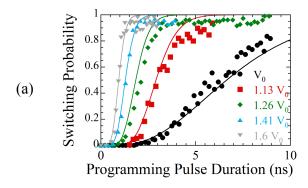

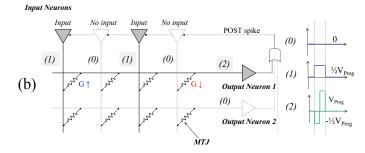

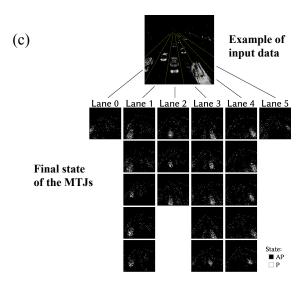

Figure 4 illustrates this breakthrough idea [31], [32]. Figure 4(a) presents experimental measurements of stochastic switching: we can see that the probability for a MTJ to switch when a programming pulse is applied can be adjusted by

Fig. 4. (a) Measurements of stochastic stochastic switching in binary MTJs. (b) Simplified architecture for implementing stochastic learning with binary MTJs. (c) Final states of the MTJs in a network that has been trained on a task of car counting (as obtained by system-level simulation).

choosing pulse duration and voltage amplitude. This effect is now fully understood and can be modeled using analytical equation [19].

Figure 4(b) presents a simplified learning architecture that implements a stochastic spike timing dependent plasticity rule, described in more detail in [32]. The MTJs, organized as a crossbar, connect CMOS input neurons to CMOS output neurons, in a manner analogous to "feed-forward" neural networks. Such a system can be trained to perform tasks in an unsupervised manner. The CMOS input neurons present the

inputs as asynchronous voltage spikes, which are transmitted to the output differently depending on the MTJ states, which therefore act as binary synaptic weight. The CMOS output neurons act as leaky integrate-and-fire neurons [5]. When an output neuron spikes, it applies a simple voltage waveform on the crossbar, as illustrated in Figure 4(b), which leads to stochastic programming of the MTJs and implements the stochastic simplified spike timing dependent plasticity learning rule.

This seemingly simple process allows the system to learn complex tasks. For example, if we present as input a video of vehicles passing on a freeway acquired from a bioinspired retina [33], each output neuron naturally specializes to a particular lane of the freeway and becomes a vehicle detector for this lane. This is illustrated in Figure 4(c). Each subimage is a two-dimensional representation of the states of the MTJs connected to one output neuron; it is apparent that each output neuron is sensitive to one lane of the freeway. More neurons are sensitive to the four inward lanes than the two outward lanes, because fewer vehicles are driving on the two outward lanes. The system can thus be used as a vehicle counter, with detection rate on the four inward lanes higher than 95%, and a number of false detection smaller than 5%.

Interestingly, such a system is extremely robust to device variation, although these variations make the switching probabilities of the devices programmed in the same conditions extremely variable [31], [32]. The robustness to device variation, a common issue in nanoscale devices, makes a strong argument for using bioinspiration to better exploit emerging spintronics devices.

## V. SPINTRONIC DEVICES FOR STOCHASTIC RESONANCE

The sensitivity of the spintronic nano-devices to thermal fluctuations can also be useful to harvest thermal noise energy in electronic systems. As already mentioned in section 2, when, by proper design, reducing the energy barrier separating the two P and AP states to a few times the thermal energy, a magnetic tunnel junction undergoes random switching between those states due to thermal fluctuations, therefore behaving as a stochastic oscillator [36], [37]. The MTJ's free layer is then said to be superparamagnetic.

Such stochastic dynamics can lead to complex behaviors, relevant to bioinspired applications. Recent works have demonstrated the capacity of superparamagnetic tunnel junctions to naturally achieve stochastic resonance [34], [35], [38]. By properly setting the barrier height in respect to the thermal noise amplitude, the system exhibits an increased sensitivity to sub-threshold inputs mediated by the noise. For small amplitude periodic excitations, the mean frequency of the system response shows a strong correlation with the input frequency, demonstrating noise-enhanced synchronization.

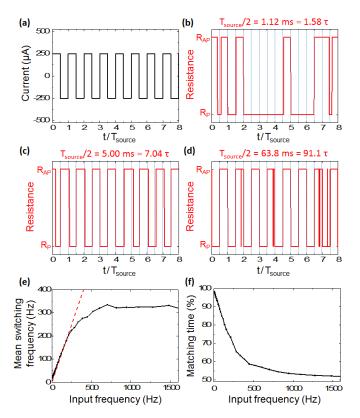

In Figure 5, a square current signal with amplitude one sixth of the MTJ critical current and varying frequency is applied to a  $60 \times 180 \ nm^2$  superparamagnetic tunnel junction [34]. When the period of the input signal is small compared to the mean switching time  $\tau$  of the MTJ (high frequency),

Fig. 5. Experimental measurements of stochastic resonance in a superparamagnetic MTJ (data from [34]). (a) Waveform of the applied Input. (b-d) Resistance of the MTJ for several input frequencies. In situation (c), quasi-deterministic synchrony between input and output is observed, consistently with stochastic resonance theory [35]. (e) Mean switching frequency of the MTJ as a function of input frequency. (f) Proportion of matching time between input and output as a function of input frequency.

there is a low probability that a switch of the MTJ occurs during a half-period (Figure 5(b)). However, when the input frequency is decreased, and the half-period compares to a few times  $\tau$ , the probability that an input oscillation triggers a single back-and-forth switch of the MTJ becomes increasingly significant (Figure 5(c)). When the frequency is decreased further, supplementary short glitches are then likely to occur due to the high instability of the device (Figure 5(d)).

As the resulting behavior, under a critical frequency, the switching frequency of the MTJ starts to correlate to the excitation frequency (Figure 5(e)) and the matching time between the input and the output gradually increases (Figure 5(f)). Last but not least, this critical frequency increases as the device stability decreases, and these results are consistent with general stochastic resonance theory [35].

Stochastic resonance and its variations have been suggested as a strategy used by the brain to achieve lowpower sensing in noisy environments [39], [40], and has also been proposed for applications [41], [42]. Nevertheless, harnessing the stochastic resonance property of superparamagnetic MTJs for applications will require further research.

### VI. CONCLUSION

In this work, we have introduced the features that spin electronics can bring to CMOS and how they can enhance functionality of neuroinspired circuits. Several ideas have been introduced, exploiting variations of the flagship device of spin electronics: the MTJ. Logic gates with hybrid volatile and nonvolatile behaviors are especially appropriate to implement cognitive systems. Spintronic memristors and binary stochastic magnetic tunnel junctions may be used as synapses for systems capable of learning. Superparamagnetic MTJs exhibit stochastic resonance that could be used for sensing systems.

There are fundamental reasons for which the MTJ in its different flavors fits especially well in a bioinspired design. As a compact nanodevice with rich physics, switching characteristics enhanced by thermal noise and nonvolatility, it is more reminiscent of the nanodevices used by biology (ion channels, synapses) than traditional electron devices. All these results and considerations suggest that the impact of MTJs on micro and nanoelectronics may go further than traditional embedded and standalone applications, although considerable work is still needed to develop the alternative paradigms of computation of the future involving spintronics.

#### ACKNOWLEDGMENTS

This work was supported by the ANR COGNISPIN (ANR-13-JS03-0004-01) and the FP7 ICT BAMBI (FP7-ICT-2013-C) projects, the CNRS/MI DEFI NANO program and the European Research Council (ERC NanoBrain 2010 Stg 259068). The authors would like to thank T. Devolder, D. Ravelosona, P. Bessiere and J. Droulez for fruitful discussions.

#### REFERENCES

- [1] Y.-K. Chen, J. Chhugani, P. Dubey, C. Hughes, D. Kim, S. Kumar, V. Lee, A. Nguyen, and M. Smelyanskiy, "Convergence of recognition, mining, and synthesis workloads and its implications," *Proceedings of the IEEE*, vol. 96, no. 5, pp. 790–807, May 2008.

- [2] P. A. Merolla, J. V. Arthur, R. Alvarez-Icaza, A. S. Cassidy, J. Sawada, F. Akopyan, B. L. Jackson, N. Imam, C. Guo, Y. Nakamura, B. Brezzo, I. Vo, S. K. Esser, R. Appuswamy, B. Taba, A. Amir, M. D. Flickner, W. P. Risk, R. Manohar, and D. S. Modha, "A million spiking-neuron integrated circuit with a scalable communication network and interface," *Science*, vol. 345, no. 6197, pp. 668–673, Aug. 2014.

- [3] B. Benjamin, P. Gao, E. McQuinn, S. Choudhary, A. Chandrasekaran, J.-M. Bussat, R. Alvarez-Icaza, J. Arthur, P. Merolla, and K. Boahen, "Neurogrid: A mixed-analog-digital multichip system for large-scale neural simulations," *Proceedings of the IEEE*, vol. 102, no. 5, pp. 699– 716, May 2014.

- [4] S. Furber, F. Galluppi, S. Temple, and L. Plana, "The SpiNNaker project," *Proceedings of the IEEE*, vol. 102, no. 5, pp. 652–665, May 2014.

- [5] G. Indiveri, B. Linares-Barranco, T. J. Hamilton, R. Etienne-Cummings, T. Delbruck, S.-C. Liu, P. Häfliger, S. Renaud, J. Schemmel, G. Cauwenberghs, J. Arthur, S. Saighi, J. Wijekoon, and K. Boahen, "Neuromorphic silicon neuron circuits," *Front. Neuromorphic Engineering*, vol. 5, p. 73, 2011

- [6] N. Locatelli, V. Cros, and J. Grollier, "Spin-torque building blocks," Nat Mater, vol. 13, no. 1, pp. 11–20, Jan. 2014.

- [7] Y. Zhang, W. Zhao, J.-O. Klein, W. Kang, D. Querlioz, Y. Zhang, D. Ravelosona, and C. Chappert, "Spintronics for low-power computing," in *Design, Automation and Test in Europe Conference and Exhibition (DATE)*, 2014, Mar. 2014, pp. 1–6.

- [8] N. Locatelli, A. Mizrahi, A. Accioly, D. Querlioz, J.-V. Kim, V. Cros, and J. Grollier, "Spin torque nanodevices for bio-inspired computing," in 2014 14th International Workshop on Cellular Nanoscale Networks and their Applications (CNNA), Jul. 2014, pp. 1–2.

- [9] A. Chanthbouala, V. Garcia, R. O. Cherifi, K. Bouzehouane, S. Fusil, X. Moya, S. Xavier, H. Yamada, C. Deranlot, N. D. Mathur, M. Bibes, A. Barthélémy, and J. Grollier, "A ferroelectric memristor," *Nat. Mat.*, vol. 11, no. 10, pp. 860–864, 2012.

- [10] D. Querlioz, O. Bichler, P. Dollfus, and C. Gamrat, "Immunity to device variations in a spiking neural network with memristive nanodevices," *IEEE Trans. Nanotechnol.*, vol. 12, no. 3, pp. 288 – 295, 2013.

- [11] S. H. Jo, T. Chang, I. Ebong, B. B. Bhadviya, P. Mazumder, and W. Lu, "Nanoscale memristor device as synapse in neuromorphic systems," *Nano Lett.*, vol. 10, no. 4, pp. 1297–1301, Apr. 2010.

- [12] B. Linares-Barranco and T. Serrano-Gotarredona, "Exploiting memristance in adaptive asynchronous spiking neuromorphic nanotechnology systems," in *Proc. of IEEE Conference on Nanotechnology*, 2009, 2009, pp. 601–604.

- [13] G. Indiveri, B. Linares-Barranco, R. Legenstein, G. Deligeorgis, and T. Prodromakis, "Integration of nanoscale memristor synapses in neuromorphic computing architectures," *Nanotechnology*, vol. 24, no. 38, p. 384010, Sep. 2013.

- [14] Z. Diao, Z. Li, S. Wang, Y. Ding, A. Panchula, E. Chen, L.-C. Wang, and Y. Huai, "Spin-transfer torque switching in magnetic tunnel junctions and spin-transfer torque random access memory," *Journal of Physics:* Condensed Matter, vol. 19, no. 16, p. 165209, Apr. 2007.

- [15] H. Yoda, S. Fujita, N. Shimomura, E. Kitagawa, K. Abe, K. Nomura, H. Noguchi, and J. Ito, "Progress of STT-MRAM technology and the effect on normally-off computing systems," in *IEDM Tech. Dig.*, Dec. 2012, pp. 11.3.1–11.3.4.

- [16] T. Devolder, J. Hayakawa, K. Ito, H. Takahashi, S. Ikeda, P. Crozat, N. Zerounian, J.-V. Kim, C. Chappert, and H. Ohno, "Single-shot time-resolved measurements of nanosecond-scale spin-transfer induced switching: Stochastic versus deterministic aspects," *Phys. Rev. Lett.*, vol. 100, no. 5, p. 057206, Feb. 2008.

- [17] D. Bedau, H. Liu, J. Z. Sun, J. A. Katine, E. E. Fullerton, S. Mangin, and A. D. Kent, "Spin-transfer pulse switching: From the dynamic to the thermally activated regime," *Applied Physics Letters*, vol. 97, no. 26, pp. 262 502–262 502–3, Dec. 2010.

- [18] Y. Zhang, W. Zhao, G. Prenat, T. Devolder, J.-O. Klein, C. Chappert, B. Dieny, and D. Ravelosona, "Electrical modeling of stochastic spin transfer torque writing in magnetic tunnel junctions for memory and logic applications," *IEEE Transactions on Magnetics*, vol. 49, no. 7, pp. 4375–4378, Jul. 2013.

- [19] A. F. Vincent, N. Locatelli, W. S. Zhao, J.-O. Klein, S. Galdin-Retailleau, and D. Querlioz, "Analytical macrospin modeling of the stochastic switching time of spin transfer-torque magnetic tunnel junctions," *IEEE Trans. Electron Dev., accepted*, 2014.

- [20] A. Fukushima, T. Seki, K. Yakushiji, H. Kubota, H. Imamura, S. Yuasa, and K. Ando, "Spin dice: A scalable truly random number generator based on spintronics," *Appl. Phys. Express*, vol. 7, no. 8, p. 083001, Aug. 2014.

- [21] M. Sharad, C. Augustine, G. Panagopoulos, and K. Roy, "Spin-based neuron model with domain-wall magnets as synapse," *IEEE Transactions on Nanotechnology*, vol. 11, no. 4, pp. 843 –853, Jul. 2012.

- [22] X. Wang, Y. Chen, H. Xi, H. Li, and D. Dimitrov, "Spintronic memristor through spin-torque-induced magnetization motion," *IEEE Electron Device Letters*, vol. 30, no. 3, pp. 294–297, Mar. 2009.

- [23] A. Chanthbouala, R. Matsumoto, J. Grollier, V. Cros, A. Anane, A. Fert, A. V. Khvalkovskiy, K. A. Zvezdin, K. Nishimura, Y. Nagamine, H. Maehara, K. Tsunekawa, A. Fukushima, and S. Yuasa, "Vertical-current-induced domain-wall motion in MgO-based magnetic tunnel junctions with low current densities," *Nat. Phys.*, vol. 7, no. 8, pp. 626–630, 2011.

- [24] W. Zhao, M. Moreau, E. Deng, Y. Zhang, J.-M. Portal, J.-O. Klein, M. Bocquet, H. Aziza, D. Deleruyelle, C. Muller, D. Querlioz, N. Ben Romdhane, D. Ravelosona, and C. Chappert, "Synchronous non-volatile logic gate design based on resistive switching memories," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. Early Access Online, 2013.

- [25] J. V. Arthur and K. A. Boahen, "Learning in silicon: Timing is everything," *Advances in neural information processing systems*, vol. 18, pp. 281–1185, 2006.

- [26] G. Indiveri, E. Chicca, and R. Douglas, "A VLSI array of low-power spiking neurons and bistable synapses with spike-timing dependent plasticity," *Neural Networks, IEEE Transactions on*, vol. 17, no. 1, pp. 211–221, 2006.

- [27] F. Alibart, E. Zamanidoost, and D. B. Strukov, "Pattern classification by memristive crossbar circuits using ex situ and in situ training," *Nat Commun*, vol. 4, Jun. 2013.

- [28] Y. Lakys, W. S. Zhao, T. Devolder, Y. Zhang, J.-O. Klein, D. Ravelosona, and C. Chappert, "Self-enabled "error-free" switching circuit for spin transfer torque MRAM and logic," *IEEE Trans. Magn.*, vol. 48, no. 9, pp. 2403–2406, 2012.

- [29] J. H. Lee and K. K. Likharev, "Defect-tolerant nanoelectronic pattern classifiers," *Int. J. Circ. Theor. Appl.*, vol. 35, no. 3, pp. 239–264, May 2007.

- [30] M. Suri, D. Querlioz, O. Bichler, G. Palma, E. Vianello, D. Vuillaume, C. Gamrat, and B. DeSalvo, "Bio-inspired stochastic computing using binary CBRAM synapses," *IEEE Transactions on Electron Devices*, vol. 60, no. 7, pp. 2402–2409, 2013.

- [31] A. F. Vincent, J. Larroque, W. S. Zhao, N. Ben Romdhane, O. Bichler, C. Gamrat, J.-O. Klein, S. Galdin-Retailleau, and D. Querlioz, "Spintransfer torque magnetic memory as a stochastic memristive synapse for neuromorphic systems," *submitted*, 2014.

- [32] —, "Spin-transfer torque magnetic memory as a stochastic memristive synapse," in 2014 IEEE International Symposium on Circuits and Systems (ISCAS), Jun. 2014, pp. 1074–1077.

- [33] P. Lichtsteiner, C. Posch, and T. Delbruck, "A 128x 128 120 dB 15 mus latency asynchronous temporal contrast vision sensor," *IEEE J. Solid-State Circuits*, vol. 43, no. 2, pp. 566–576, 2008.

- [34] N. Locatelli, A. Mizrahi, A. Accioly, R. Matsumoto, A. Fukushima, H. Kubota, S. Yuasa, V. Cros, L. G. Pereira, D. Querlioz, J.-V. Kim, and J. Grollier, "Noise-enhanced synchronization of stochastic magnetic oscillators," *Phys. Rev. Applied*, vol. 2, no. 3, p. 034009, Sep. 2014.

- [35] L. Gammaitoni, P. Hänggi, P. Jung, and F. Marchesoni, "Stochastic resonance," Rev. Mod. Phys., vol. 70, no. 1, p. 223, Jan. 1998.

- [36] G. D. Fuchs, J. A. Katine, S. I. Kiselev, D. Mauri, K. S. Wooley, D. C. Ralph, and R. A. Buhrman, "Spin torque, tunnel-current spin polarization, and magnetoresistance in MgO magnetic tunnel junctions," *Phys. Rev. Lett.*, vol. 96, no. 18, p. 186603, May 2006.

- [37] W. Rippard, R. Heindl, M. Pufall, S. Russek, and A. Kos, "Thermal relaxation rates of magnetic nanoparticles in the presence of magnetic fields and spin-transfer effects," *Phys. Rev. B*, vol. 84, no. 6, p. 064439, Aug. 2011.

- [38] X. Cheng, C. T. Boone, J. Zhu, and I. N. Krivorotov, "Nonadiabatic stochastic resonance of a nanomagnet excited by spin torque," *Phys. Rev. Lett.*, vol. 105, no. 4, p. 047202, Jul. 2010.

- [39] M. D. McDonnell and D. Abbott, "What is stochastic resonance? definitions, misconceptions, debates, and its relevance to biology," *PLoS Comput Biol*, vol. 5, no. 5, May 2009.

- [40] L. M. Ward, A. Neiman, and F. Moss, "Stochastic resonance in psychophysics and in animal behavior," *Biol Cybern*, vol. 87, no. 2, pp. 91–101, Aug. 2002.

- [41] H. Chen, P. Varshney, S. Kay, and J. Michels, "Theory of the stochastic resonance effect in signal detection: Part i—fixed detectors," Signal Processing, IEEE Transactions on, vol. 55, no. 7, pp. 3172–3184, 2007.

- [42] H. Chen, L. Varshney, and P. Varshney, "Noise-enhanced information systems," *Proceedings of the IEEE*, vol. 102, no. 10, pp. 1607–1621, Oct. 2014.