## Effective Teaching of the Physical Design of Integrated Circuits Using Educational Tools

Syed Mahfuzul Aziz, Etienne Sicard, Sonia Ben Dhia

### ► To cite this version:

Syed Mahfuzul Aziz, Etienne Sicard, Sonia Ben Dhia. Effective Teaching of the Physical Design of Integrated Circuits Using Educational Tools. IEEE Transactions on Education, 2010, 53 (4), pp.517 - 531. 10.1109/TE.2009.2031842 . hal-01816182

## HAL Id: hal-01816182 https://hal.science/hal-01816182v1

Submitted on 15 Jun2018

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés. 1

# Effective Teaching in Physical Design of Integrated Circuits using Educational Tools

Syed Mahfuzul Aziz, Senior Member, IEEE, Etienne Sicard, Senior Member, IEEE, and Sonia Ben Dhia, Member, IEEE

Abstract—This paper presents the strategies used for effective teaching and skill development in integrated circuit design using Project-Based Learning methodologies. It presents the contexts in which these strategies are applied to IC design courses at the University of South Australia and the National Institute of Applied Science Toulouse, France. Collaborations among the faculty members of the two institutions have produced a set of learning resources and design tools to support the development of industry relevant design skills and lifelong learning skills. The courses enable students to learn about the most recent technological developments and their implications using a set of user friendly tools. The project-based learning methodologies, intuitive design tools and latest technology models have consistently produced high levels of student satisfaction with the overall quality of the courses at the two institutions.

## *Index Terms*— Integrated circuit design, VLSI Design, nanometer technology, project-based learning, lifelong learning.

#### I. INTRODUCTION

THE past few years have seen the introduction of nanoscale technologies for industrial production of high performance integrated circuits (IC) [1]-[5]. Each technology scaling is characterized by a number of changes in the IC manufacturing process. The most evident changes are the decrease in layout pattern sizes such as the gate length. The processing in a new technology node also involves steps to improve the carrier mobility and the field effect beneath the gate as well as reduce leakage currents [6]. Consequently technology scaling impacts upon the operation of the ICs by improving switching speed, signal transport, and reduced DC consumption and operating voltages [2]. Shifting to a new technology node impacts the design methodology, and requires improved technology models and tools to accurately predict the performances of the circuits. The international roadmap for integrated circuits [7] gives a prospective vision of the IC technology evolution for the next 15 years, showing how future technology nodes (22

<sup>1</sup> Manuscript received Mrach, 2009. This work was partly supported by a Teaching and Learning Grant from the University of South Australia.

Syed Mahfuzul Aziz is with the School of Electrical and Information Engineering, University of South Australia, Mawson Lakes, SA 5095, Australia (phone: +61-8-83023643; e-mail: mahfuz.aziz@unisa.edu.au).

Etienne Sicard is with the Department of Electrical and Computer Engineering, National Institute of Applied Science (INSA), 135 Av de Rangueil, 31077 Toulouse, France (e-mail: etienne.sicard@insa-toulouse.fr).

Sonia Ben Dhia is with the Department of Electrical and Computer Engineering, National Institute of Applied Science (INSA), 135 Av de Rangueil, 31077 Toulouse, France (e-mail: sonia.bendhia@insa-toulouse.fr). nm, 18 nm, 7 nm) are expected to push the limits of CMOS technology further. Engineering students need to be abreast with the rapid changes in technology and design practices. Courses in IC Design must also aim to equip students with the skills of independent learning and lifelong learning. Due to time constraints in a semester long course it is often not feasible both to introduce students to complex commercial design tools and also expect them to develop practical circuit design skills and independent learning skills.

We present project-based approaches to teaching adopted in two institutions in Australia and France, both aimed at actively engaging students in stimulating learning experiences for the development chip design skills using the latest semiconductor technologies, and for the development of independent and lifelong learning abilities. The student cohorts in these two institutions differ in terms of their previous educational experience, background knowledge and diversity. The projectbased approaches at the University of South Australia (UniSA) and the National Institute of Applied Science (INSA) Toulouse, France are tailored accordingly to maximize the learning outcomes of the two cohorts. Using intuitive educational tools we have developed project-based learning methodologies which have achieved high levels of student satisfaction. In Section II we present the recent developments in CMOS technology. Section III presents the recent educational developments and teaching challenges. Section IV illustrates the proposed design flow and associated tools. In Section V, examples of project-based learning at the two institutions are given along with descriptions of the skills developed. Section VI presents anonymous evaluation of the courses by students and the feedback received from colleagues. Section VII concludes the paper.

#### II. DEVELOPMENTS IN CMOS TECHNOLOGY

#### A. General Trends

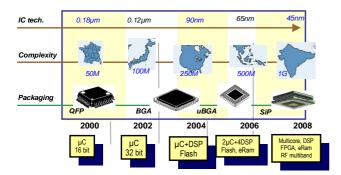

CMOS being the most dominant VLSI (Very Large Scale Integrated circuit) technology to date, first we look at the developments in this technology and the prospective future developments. The trend of CMOS technology improvement continues to be driven by the need to integrate more functions within a given silicon area (Fig. 1). In 2008, the 45 nm CMOS technology enabled designs containing one billion devices on a chip (system-on-chip, SoC), or stacked dies and packages forming systems-in-packages, with typically multi-core processors, parallel Digital Signal Processors (DSP), Field Programmable Gate Arrays (FPGA), embedded RAM, as well as wireless communication capabilities in a single chip.

Fig. 1. More and more complex ICs

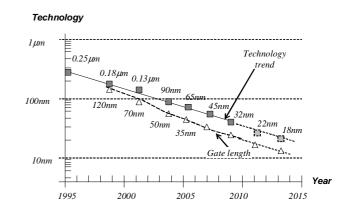

Table I gives an overview of the key parameters for technology nodes from 180 nm, introduced in 1999, down to 22 nm, which is supposed to be in production around 2011. The physical gate length is slightly smaller than the technological node, as illustrated in Fig. 2. The gate material has long been polysilicon, with silicon dioxide (SiO<sub>2</sub>) as the insulator between the gate and the channel. The thinner the gate oxide, the higher the transistor current and consequently the switching speed. SiO<sub>2</sub> has been continually scaled down over the last decade and reached a physical limit of 5 atomic layers (1.2 nm in thickness) in the 90 nm CMOS technology [8]. With the 45 nm technology, new materials such as metal gates together with high-permittivity gate oxide have been introduced [1], [3].

TABLE I

Technological Evolution and Forecast up to 2013 [7]

| Key               | 180              | 90               | 65   | 45    | 32    | 22    | 18    |

|-------------------|------------------|------------------|------|-------|-------|-------|-------|

| parameter         | nm               | nm               | nm   | nm    | nm    | nm    | nm    |

| First             | 1999             | 2003             | 2005 | 2007  | 2009  | 2011  | 2013  |

| production        |                  |                  |      |       |       |       |       |

| Gate              | 130              | 50               | 35   | 30    | 20    | 15    | 12    |

| length            | nm               | nm               | nm   | nm    | nm    | nm    | nm    |

| Gate              | Poly             | Poly             | Poly | Metal | Metal | Dual  | Dual  |

| material &        | SiO <sub>2</sub> | SiO <sub>2</sub> | SiON | High  | High  | gate? | gate? |

| dielectric        |                  |                  |      | K     | K     | -     | -     |

| Atoms             | 10               | 8                | 6    | 5-50  | 5-50  | 5-30  | 5-30  |

| stacked on        |                  |                  |      |       |       |       |       |

| the gate          |                  |                  |      |       |       |       |       |

| oxide             |                  |                  |      |       |       |       |       |

| Kgates per        | 100              | 350              | 500  | 900   | 1500  | 2800  | 4500  |

| mm <sup>2</sup>   |                  |                  |      |       |       |       |       |

| Memory            | 4.5              | 1.3              | 0.6  | 0.3   | 0.15  | 0.08  | 0.08  |

| point ( $\mu^2$ ) |                  |                  |      |       |       |       |       |

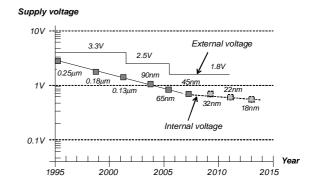

At each lithography scaling the linear dimensions are approximately reduced by a factor of 0.7 and the areas are reduced by factor of 2. Smaller cell sizes lead to a higher integration density which has risen from 100 Kilo-gates per mm<sup>2</sup> in the 130 nm technology to almost 1 million gates per mm<sup>2</sup> in the 45 nm technology. In parallel, the size of a 6-transistor memory cell such as those used in static RAM went below the 1  $\mu$ m<sup>2</sup> limit after the 65 nm technology. The supply voltage tends to decrease (see Fig. 3), to reduce power

consumption and limit the degradation mechanisms of the ultra-thin gate oxide. From 130 nm to 45 nm, the supply voltage has been reduced from 1.5 V to 0.9 V.

Fig. 2. The technology scale down towards nano-scale devices

Fig. 3. The continuous decrease in supply voltages

#### B. Improvements at transistor level

The channel length of MOS devices is automatically scaled with the technology. A scaling factor of 0.7 would lead to a 33% increase in the absolute current, with consequent increase in switching speed. However, the effective carrier mobility tends to degrade with narrower channel. Two approaches have been introduced recently to further improve transistor current capabilities:

• Decreasing oxide thickness  $t_{OX}$ : The gate oxide thickness has been reduced to 1.2 nm (5 atoms) in the 90 nm technology. Unfortunately, the gate oxide leakage is exponentially increased, which increases the parasitic leakage currents and consequently the standby power consumption. For 40 years, polysilicon gates combined with  $SiO_2$  (gate oxide) have been serving as the key enabling materials for MOS devices. Starting with the 45 nm generation so-called "metal gates" has been introduced [1]-[2], based on Nickel-Silicide (NiSi) or Titanium-Nitride (TiN). In combination with Hafnium Oxide (HfO<sub>2</sub>), a high-permittivity dielectric ( $\epsilon_r=12$ ), the metal-gate transistors feature outstanding current switching capabilities together with low leakage, as HfO<sub>2</sub> can be

made much thicker than  $SiO_2$  gate oxide for an equivalent gate capacitance effect. Increased *on* current, decreased *off* current and significantly decreased gate leakage are obtained with this novel combination. Future approaches should also include double or triple-gate devices as is illustrated in Fig. 4.

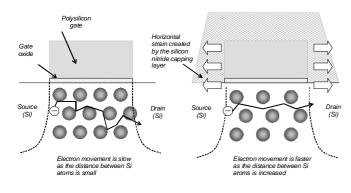

Increasing carrier mobility µ: This parameter was kept unchanged until the 90 nm generation. Starting with this generation strained silicon has been introduced to enhance the carrier mobility [4]-[6], [8]-[9], which boosts both the n-channel and p-channel transistor performances (Fig. 5).

Fig. 4. The Tri-Gate concept as proposed by Intel [10] for 32 nm and 22 nm nodes

Fig. 5. Strain generated by a silicon-nitride capping layer which increases the distance between atoms underneath the gate. This speeds up the electron mobility of n-channel MOS devices.

#### **III. TEACHING PRACTICES**

#### A. A review of recent educational approaches

The never-ending shift towards nano-scale technology raises several questions about the educational approaches for IC design courses involving CMOS technology. Numerous intuitive approaches to facilitate students' understanding of microelectronic circuit fundamentals have been proposed in the past years. At the logic level, Hacker and Sitte [11] have presented an interactive teaching suite for the design of combinatorial and sequential logic circuits, while Tseng [12] has described an effective method of generating hardware implementation from various styles of procedural description. At the mixed-mode level, Hudson et. al. [13] proposed an attractive sequence that includes digital, analog and mixedsignal aspects of IC design. To help students overcome the fears of learning analog circuit design and handle the fast pace of the course, multiple hands-on learning experiences have been employed that allow the students to learn IC design using multiple modalities and observe real-world effects of ICs. The students have appreciated these hands-on experiences and have requested more throughout the sequence.

A review of fundamental low power design techniques has been presented in [14], with examples to facilitate students' study and understanding. Switching time calculation has been specifically addressed by Kayssi [15], a topic covered in most VLSI courses. In the analog area, Mazhari [16] has proposed a representation of differential amplifier which explicitly reveals the relationships among important amplifier specifications. Karmalkar [17] has detailed the contents of a lecture for enhancing the interest of electrical engineering students in semiconductor device modeling, while Masters [18] created online animations for active learning of currents and fields in metal layers.

As for fabricating student designs, several relatively low cost options have been available for accessing CMOS IC manufacturing, such as Europractice in Europe [19] or MOSIS in USA [20]. However, the exponential increase in the costs of accessing nanoscale technologies in recent years and the steady increase in technology-driven design rules tend to limit the number of student projects effectively sent to fabrication. In addition, as the number of hours dedicated to practical training with real silicon is gradually reduced there is now a greater need for device physics related simulation tools so that students can still develop a deep understanding of designing with nano-scale technologies.

#### B. Challenges

First and foremost, it is acknowledged that the students need to develop as lifelong learners if they are to adapt to the rapid technological changes outlined in Section II and the consequent changes in design concepts and methodologies. In addition, it is necessary for them to develop the important graduate qualities of problem solving and critical thinking in order to successfully operate in a continually changing and challenging field of VLSI Design. While our role, as educators, is to ensure that the learning activities in our courses facilitate the development of up to date knowledge and industry relevant design skills, it is also important to ensure that the activities facilitate the development of the above mentioned generic skills in an interesting and stimulating way. The challenge for us is how to accomplish this within the span of a semester which typically lasts for thirteen/fourteen weeks. We must be mindful of the following issues, which have the potential to render the task difficult unless due attention is paid right from the beginning:

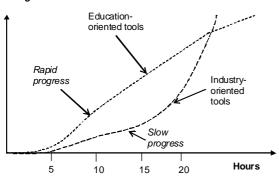

• The commercial chip design tools available today are very powerful, and are capable of capturing the design and verification needs of modern ICs. However, these tools are highly complex and take long time to learn (Fig. 6). If these commercial tools are used for student learning the focus may unintentionally shift from developing actual technical knowledge and skills in circuit design to merely the mastery of complex design tools.

Learning curve

Fig. 6. The learning curve of education-oriented and industry-oriented tools

- On the other hand it is very important for students to develop thorough understanding of the complex process technologies and their impacts on design alternatives using intuitive 2D/3D technology visualizations. Therefore it is necessary to use design tools that are not only less time consuming to learn but also provide intuitive design, simulation and visualization environments.

- The variation in background technical knowledge among the student cohorts present another challenge [21]. From a pedagogical perspective, any gap in the background technical knowledge must be addressed first before effective learning of new concepts and skills can occur.

#### C. Teaching context at UniSA, Australia

The UniSA course on VLSI Design focuses on Digital CMOS integrated circuit design. It is offered as a technical elective to final year undergraduate students in four year degree programs in Electronics and Microengineering, Computer Systems Engineering, Telecommunications, and Electrical and Mechatronic Engineering. It is also offered to students of Masters by coursework programs in relevant disciplines. Students are expected to have the necessary background knowledge and experience in digital logic design and electronics. The undergraduate students are expected to develop this background knowledge through compulsory courses on electronics and digital design in earlier years of their degree programs. However, the VLSI course is the first one to introduce them to CMOS cell design. Also majority of the students who enroll in this course in the last five years were overseas students, many of them pursuing Masters by coursework programs. These students come from diverse cultural, language and educational backgrounds [22]. They possessed bachelor degrees in various branches of Electrical, Electronics, Computer and Telecommunication Engineering with different levels of exposure to the background knowledge and skills required to undertake the VLSI Design course. This presented a challenge and required an inclusive learning environment for all students along with the use of user friendly educational tools.

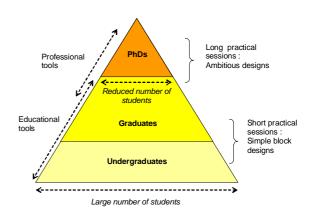

INSA offers a two-year program called Masters in Automatic Control and Electronics. In the first year of study the students do a course titled Physics and Modeling of Semiconductor Devices. It consists of 20 hours of lecture and 15 hours of laboratory work. Due to the large number of students and the unavailability of student editions of professional computeraided-design tools, educational tools are used, which cover the introductory logic and layout-level design in an interactive way. The training targets are basic CMOS cell design and simulation [23]. In the second year of the program, students attend 20-hours of lecture in the course Analog CMOS Circuit Design and Test, including several aspects of advanced CMOS cell design [24]. Students also conduct a small VLSI design project equivalent to 20 hours of practical work using educational design tools. However, the licensing requirements, cost and the time needed to learn professional CAD tools can be justifiable in advanced (postgraduate level) courses and in research degree programs (Fig. 7) because of the limited number of students and the interest of training future engineers in acquiring some knowledge of complete industrial design flow. In the Analog Circuit Design course the professional tools are only used to convert the students' layouts to industry format prior to fabrication because the educational tools cover a subset of the real process design rules.

Fig. 7. Educational tools are mostly used for undergraduate teaching while professional tools are used at Graduate and Doctorate levels

#### IV. PROPOSED DESIGN FLOW AND SOFTWARE TOOLS

Most industrial CAD tools lack the ability to show the basic functionality and various aspects of CMOS circuits in an intuitive and graphical manner. What is important for student comprehension is the ability to act on a design, to define intuitive test sequences and to immediately view the electrical response. To fulfill these requirements both UniSA and INSA mainly use a user friendly layout-level design and simulation tool called *Microwind* [25]. To create layouts of large designs easily a schematic-level design and simulation called *Dsch* is used [25]. These tools incorporate the most recent CMOS technologies and provide an interactive learning environment for the development of IC design and analysis skills. Another software called *WinSpice* [26] is used for simulation of netlists

generated from the layouts using various SPICE models incorporated within the *Microwind* tool.

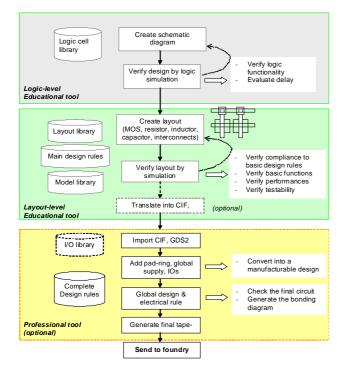

#### A. Design Flow

The design flow used by students for physical design of layout-level functional blocks is illustrated in Fig. 8. The Microwind tool is used for generating the layout blocks that compose the test IC. Microwind's layout library (MOS generators, PAD generators, cell compiler) may be used to ease the design phase. The design rule checker is used to ensure compliance with technology constraints (minimum width, minimum distance between layers etc.). Students also use the built-in analog simulator to verify that the functionality and performance comply with the specifications.

Once the layout is complete, a set of files is generated in a standard layout description format (CIF, GDS2 etc.) for transfer to a professional CAD environment. The reason why a professional layout tool is necessary prior to fabrication is that educational tools only verify a sub-set of design rules. The final circuit is built by placing and connecting layout blocks, and checking against the complete set of design rules.

Fig. 8. Design flow for teaching concepts of CMOS cell design

#### B. Design Tools

In this section we introduce the *Microwind* software, which emphasizes a user-friendly and intuitive design style for educational use. *Microwind* [25] is a CMOS circuit editor and simulation tool for layout-level design, running on Microsoft Windows. It has been developed since 1998 through several versions, and is available as a freeware for educational purpose. In short, *Microwind* allows the student to draw the masks of the circuit layout and perform analog simulation. Some textbooks on CMOS design have been published around this software in the last few years [23]-[24], [27].

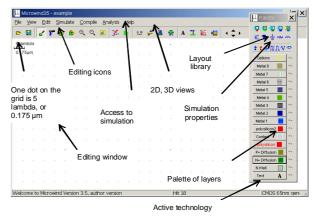

The *Microwind* main screen, shown in Fig. 9, includes two windows: one for the main menu and the layout display, and the other for the icon menu and the layer palette. The main layout window features a grid, scaled in lambda ( $\lambda$ ) units. The lambda unit is fixed to half of the minimum available lithography of the technology in use, noted as L<sub>min</sub>. For example, the default technology is a CMOS 6-metal layers 65nm technology, consequently lambda is 0.035 µm.

$$\lambda = \frac{L_{\min}}{2} \tag{1}$$

From an educational view point, the key advantages of the lambda-based system are:

- the ability to simulate the same layout with several technology files.

- the convenience of having to master only a single set of design rules (minimum gate length 2λ, minimum metal width 3λ, etc.)

Fig. 9. The MICROWIND window as it appears at the initialization stage

#### C. Tutorial on MOS device models

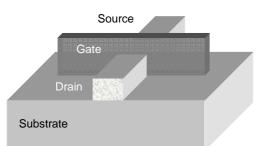

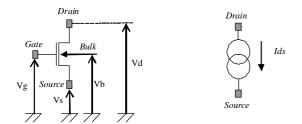

1) Traditional approach: Students often tend to miss the essentials of device modeling even after extensive discussions of the mathematical approaches for several devices [17]. Modeling the MOS device consists of writing a set of equations that link the voltages and currents, in order to simulate and predict the behavior of a single device and consequently the behavior of a complete circuit. Many books have been published about semiconductor physics and device modeling. The most common references used for education are [28] and [29]. Traditional teaching usually relies on an indepth explanation of the potentials, fields, threshold voltage, and eventually the expression of the current *Ids* which flows between the drain and the source, depending on the node voltages  $V_d$ ,  $V_g$ ,  $V_s$  and  $V_b$  as illustrated in Fig. 10.

Fig. 10. Symbolic representations of the MOS device

$$Ids = f(Vd, Vg, Vs, Vb)$$

(2)

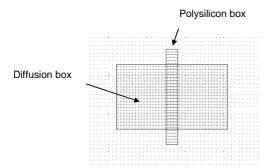

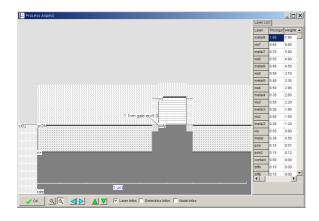

2) Our approach: Our approach is significantly different in that it aims at giving students immediate confidence to design MOS devices. The approach consists of a step-by-step illustration of the most important relationships between layout and performance. For this, the students are asked to draw a MOS device using the layout interface shown in Fig. 9. Clicking and dragging the mouse adds polysilicon boxes on the layout. Students are then asked to change the active layer in the palette to add a diffusion box. This completes the design of the MOS device (Fig. 11). The students are then asked to perform a 2D cross-section of the device. They observe the details of the layer structure (oxide, diffusion, gate), and how the gate splits the diffusion box into three regions, namely the drain, channel and the source (Fig. 12). At this stage usual questions concern the color codes, the stack of oxides (as no metal is yet present), or the scale of the device.

Fig. 11. The first MOS device designed by the student

Fig. 12. 2D cross-section of the MOS device

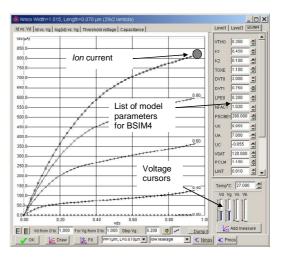

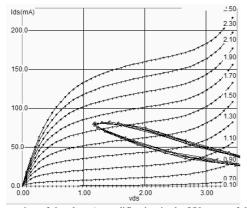

Then, the students are invited to evaluate the static electrical performance of the device. An icon gives access to the  $I_d/V_d$  curve, which is plotted for varying gate voltage  $V_{gs}$ , from 0 to  $V_{DD}$  (Fig. 13). It enables students to act on the operating point in the  $I_d/V_d$  curve. Students are asked to extract *Ion*, which gives an important indication about the maximum available current. As MOS designs differ from one student to another, waveforms and values are not identical. Once the functional point is placed at *Ion* (after some search), with for example Vg=0,  $V_d=V_{DD}$  and  $Vg=V_{DD}$ , the concept of voltage control and first-order impact on current becomes obvious to most students.

In *Microwind*, three important generations of device models are accessible from a single interface window: the MOS model 1 [30], the LEVEL 3 model [31] and the BSIM4 model [32]. The number of parameters specified in the official release of BSIM4 is as high as 500. A significant portion of these parameters is not important at early teaching phases. We therefore concentrate on the most significant parameters for educational purpose. For example, in *Microwind* the set of user-accessible parameters is reduced to around 30 for BSIM4.

Fig. 13. The tutorial on MOS devices with user accessible parameters

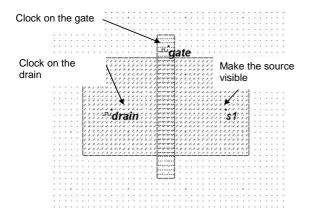

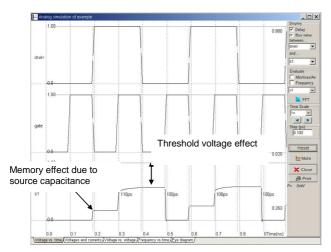

3) Interactive simulation of the layout: At this stage the students use a set of simulation properties (clocks, pulses, DC voltage sources) to build a testing scenario to validate the concept of a voltage switch controlled by a gate voltage. A usual approach followed by students consists of placing clocks on the gate and drain, and then to monitor the source (Fig. 14). This leads to the timing diagrams of Fig. 15, which stimulates the students' thoughts on the factors influencing the performance of the MOS device. Through careful investigation of the simulations students are able to gather information about the key properties and drawbacks, for example junction capacitance effect that samples undesired intermediate voltage, threshold effect that jeopardizes the high voltage levels, and ultra-fast charge/discharge (in the picoseconds range).

The students are then asked to build the pMOS device and observe the complementary behavior. The training also includes the inverter design and the analysis of sizing effects on the static transfer characteristics. Finally, students are asked

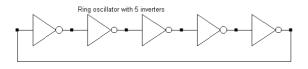

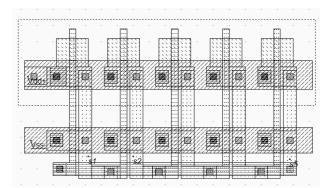

#### Proposal to IEEE Transaction on Education

to copy/paste several inverters, build appropriate interconnects in order to construct a ring oscillator (Fig. 16), which has the property of oscillating naturally. A contest is usually organized to obtain the fastest oscillating frequency, which involves several aspects of layout optimization, such as minimum gate length, suppression of spared diffusion areas, minimum distance between inverters etc.The ring oscillator circuit can be simulated easily at layout level with Microwind using various technologies. The time-domain waveforms of the output are reported in Fig. 17 for 0.8  $\mu$ m, 0.12  $\mu$ m and 70 nm technologies. Although the supply voltage (V<sub>DD</sub>) has been reduced with technology scaling (5 V in 0.8  $\mu$ m, 2 V in 0.18  $\mu$ m, and 1.0 V in 45 nm) the gain in frequency improvement is significant.

Fig. 14. Usual student approach for MOS simulation

Fig. 15. Typical time-domain waveforms of the gate, drain and source voltages obtained by analog simulation

Fig. 16. Schematic diagram and layout of the ring oscillator used for simulation

Fig. 17. Oscillation frequency improvement with technology scale down

#### V. PROJECT-BASED LEARNING

Project-based learning methods have been developed for the courses at both UniSA and INSA. In both cases the aim is to engage students in a stimulating learning experience for the development of professional design skills using the latest semiconductor technologies, and for the development of independent and lifelong learning abilities. The issue of student diversity is addressed in UniSA by following a structured project-based approach. At INSA a similar approach is adopted for the introductory course on *Physics and Modeling of Semiconductor Devices*, however a more open-ended approach is adopted in the course on *Analog CMOS Circuit Design*.

In the structured project-based learning (PBL) methodology the students do simple projects in the early stages using stepby-step *self learning guides*. Critical questions and increasingly complex tasks are gradually scaffolded within the projects. These questions and tasks are aimed at stimulating students' curiosity and thinking, thereby engaging them to carry out their own investigations [33]. The early projects, done mostly in a self learning manner, assist students in

- reviewing and/or developing the necessary

- fundamental concepts

- learning how to use the design tools

- developing problem solving and critical thinking skills

- developing independent learning skills

Students who possess relatively advanced levels of background technical knowledge can progress through the projects at their own (often faster) pace. On completion of each of the early projects the students get the satisfaction of having designed a circuit that performs some useful function. This is useful for confidence building and motivation, particularly for the students who are new to the idea of independent learning and whose previous educational experiences may have been quite different from the engaging PBL approach. This remainder of this section gives an overview of the projects used in the PBL approach in two institutions, followed by a general discussion.

#### A. UniSA

As stated previously the UniSA course on VLSI Design uses simple self-learning projects at the beginning. The projects gradually increase in complexity requiring students to engage in deeper problem solving and critical thinking. Finally there is a capstone project on designing a microprocessor which challenges students by putting the knowledge and skills they have developed to test. Students do a total of six projects, which are briefly described below.

1) First two projects - circuit analysis and optimization using WinSpice: The first two projects allow students to develop practical experience in circuit analysis and optimization using WinSpice [26], a version of the well-known SPICE (Simulation Program with Integrated Circuit Emphasis) program. While the first project handout guides the students through the simulation and optimization of a simple inverter circuit, it asks students a number of critical questions along the way requiring them to reflect on the work they do and results they obtain. The questions highlight the impacts of various MOS model parameters and device geometry on critical performance parameters such as propagation delay, switching characteristics, noise margin, dynamic power dissipation etc. The second project requires students to model a long transmission line driven by an inverter and simulate it using their experience of the first project. They are required to examine the effects of the transmission line on signal quality and propagation delay. They also develop useful insights by examining mechanisms to deal with these performance issues. In this project the students also develop practical experience on the effects of stacked and parallel transistors on the performance of logic gates.

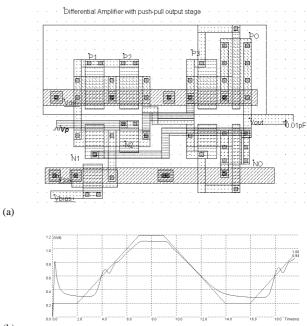

2) Project 3 and 4 - combinational and sequential circuit layouts: In the third and fourth projects the students develop

practical experience in designing simple combinational cell layouts and clocked sequential circuit layouts using a structured cell-based design methodology. They perform DRC and simulation on the created layouts. They also perform various trade-offs in relation to device geometry, layout area and performance. In the fourth project students automatically generate a four-bit dynamic shift register layout in Microwind using a one-bit inverting dynamic shift register cell layout they create manually. Students develop practical experience with two-phase non-overlapping clocks by simulating the four-bit register using the built-in simulator. Fig. 18 shows the layout of the four-bit dynamic shift register.

| BL Of AL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| 100 CIK2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | H H H                                                                              |

| El act Clhd                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                    |

| HING HING WAR IN THE STREET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                    |

| restriat recurso months excurso restrict escurso in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | the section rather section with action rather section with section                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                    |

| - El Chedra Tresdélie de Meetre Héherle Meetre                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 그 같은 것에 가장 이 가장 있는 것이 같은 것이 같은 것이 가장 있는 것이 있는 것이 있는 것이 없는 것이 없는 것이 없는 것이 없는 것이 없다. |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                    |

| - "'''''' 이 집 이 집 안 이 집 이 집 것 이 집 것 이 집 것 이 집 것 이 집 것 이 집 것 이 집 것 이 집 것 이 집 것 이 집 것 이 집 것 이 집 것 이 집 것 이 집 것 이 집 것 이 집 것 이 집 것 이 집 것 이 집 것 이 집 것 이 집 것 이 집 것 이 집 것 이 집 것 이 집 것 이 집 것 이 집 것 이 집 것 이 집 것 이 집 것 이 집 것 이 집 것 이 집 것 이 집 것 이 집 것 이 집 것 이 집 것 이 집 것 이 집 것 이 집 것 이 집 것 이 집 것 이 집 것 이 집 것 이 집 집 집 집                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                    |

| 이야히 하는 하는 아무 아무 아무 한 것 한 것 한 것 같이 않는 것 같이 한 것 같이 않는 것 같이 않는 것 같이 한 것 같이 않는 | 이번 여러는 신부 여러도 실려는 이번 수는 여러도 실려도 같다.                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                    |

| 300 CIKT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | B                                                                                  |

| Juno Cik2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                    |

Fig. 18. Four-bit dynamic shift register layout

3) Project 5 - ALU design: In the fifth project students design an arithmetic unit using a schematic design tool called *Dsch* and verify its functionality through simulation. They then automatically generate a Verilog description using the '*Make Verilog File*' command in the '*File*' menu. Finally they generate a layout in their chosen technology using the 'Compile Verilog File' command in the '*Compile*' menu of the Microwind tool. Both Dsch and Microwind have the same range of technology rules files available. Therefore the layout compiled in Microwind is implemented in the same technology as used in the original schematic design.

4) Project 6 - Capstone project on processor design: The final project on processor design challenges students to put their design skills into practice by designing a microprocessor with embedded static RAM, verifying the functionality through simulation, generating layout and performing DRC. Students follow a hierarchical cell-based design method using *Dsch*. They generate a Verlilog description of the processor and compile this in *Microwind* to generate the layout. Students aiming to achieve higher goals are inspired to conduct layout simulation or enhance the processor by incorporating additional instructions. Here the students gain valuable experience on the challenges involved in simulating large IC layouts and explore alternative solutions.

#### B. INSA

This section gives an overview of two projects conducted by INSA students in the course *Analog CMOS Circuit Design*.

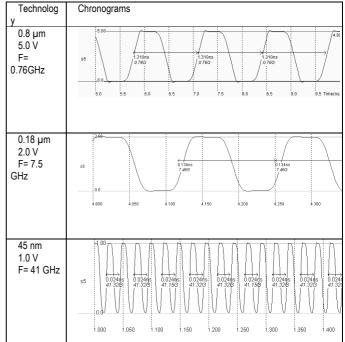

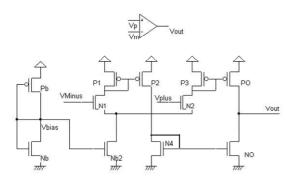

1) Project 1 - Push-Pull Amplifier: The students are given schematic diagrams of conventional CMOS amplifiers. They try to implement these circuits on their own, and optimize the layouts to satisfy predefined constraints linked to operating voltage range, DC consumption at cut-off frequency etc. The push-pull amplifier shown in Fig. 19 is built using a voltage comparator and a power output stage. The difference between Vp and Vm is amplified and produces a result, *Vout*. Transistors Nb and Pb are connected as diodes in series to

create an appropriate voltage reference  $V_{bias}$ , fixed between the nMOS threshold voltage *Vtn* and half of  $V_{DD}$ . The differential pair consists of transistors *N1* and *N2*. Three stages of current mirrors are used: *P1/P2*, *P3/PO*, *N4/NO*. The output stage consists of transistors PO and NO. These transistors are designed with large widths in order to lower the output resistance. Such a design is justified when a high current drive is required. An example of student design and its simulation are shown in Fig. 20(a) and (b) respectively. A lot of care has been taken to match device sizes and limit the silicon area.

The transient simulation of Fig. 20(b) shows some oscillation at the output which denotes an output stage drive improperly matched to the load. Virtual capacitors may be added directly to the layout to emulate the realistic loading conditions. Students are also asked to produce DC transfer characteristics to characterize the valid input range for their amplifier. Reference books such as [23] and [24] are given to the students to investigate more complex circuits.

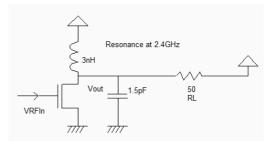

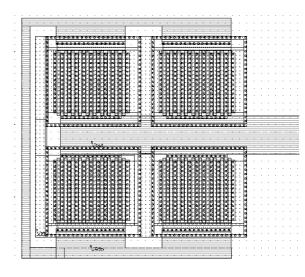

2) Project 2 - Power Amplifier: CMOS power amplifiers (Fig. 21) used in radio-frequency output stages (such as Bluetooth of WiFi) require very large current drive, which can be achieved with MOS devices in parallel. Students are asked to design MOS devices with *Ion* drive such as 100, 250 or 500 mA. As illustrated in Fig. 21(b), the metal supply must be designed with care to handle such large currents. At the start the L, R and C elements are added through virtual symbols for simplicity's sake.

Again, the dynamic plot of the functional point is one attractive way to illustrate the concept of amplifier classes. For example, Fig. 22 corresponds to a Class A regime, where the functional point is always in the linear domain. Combining onchip inductors and capacitors result in resonant systems that are tuned to the specified wireless system. For example, the integrated 3-nH inductor with 1.5 pF capacitance produces a resonance around 2.4 GHz.

Fig. 19. Schematic diagram of a push-pull operational amplifier

(b)

(a)

Fig. 20. (a) Layout and (b) time-domain simulation of a push-pull operational amplifier connected as a follower.

Fig. 21. (a) Schematic diagram of a power amplifier and (b) MOS layout featuring 250 mA *Ion* drive.

Fig. 22. Illustration of the class A amplification in the I/V curve of the power MOS

#### C. Discussion

Through the different projects the students visualize how the two design tools Dsch and Microwind can be used to design complex integrated circuits using the latest semiconductor technology. We have found these design tools to be adequate for microelectronics teaching and illustration. After two hours of practice the students develop competence in using the tools without much problem. 2D cross-sections and 3D-animated views in Microwind are extremely useful for students to visualize how the IC is built using different layers and their interconnections, and the potential sources of errors, for example missing interconnects between layers. Students develop design skills at layout level, are able to optimize the layout to increase speed, reduce the silicon area, and to check the layout for design rule violations (DRC). The students also acquire useful experience on the effects of device sizing and realize the efficiency of automatic layout generation from high level description. They gain valuable experience on the challenges involved in designing and simulating complex integrated circuits and are ready to explore professional tools available to industry.

#### VI. EVALUATION

This section provides a summary of student experience in the two institutions. Responses to anonymous course evaluation questionnaire and special questionnaire on PBL are included.

#### A. UniSA student evaluation

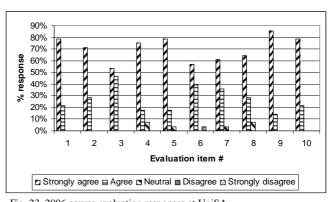

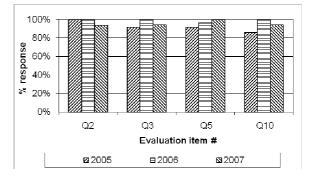

The VLSI course was evaluated anonymously by the students using UniSA's standard course evaluation questionnaire containing ten core questions and open text response. The core evaluation items are presented in Table II. Students select a response to each statement from a Likert scale of 1 to 5, where a score of 5 signifies strong agreement with the statement and 1 indicates strong disagreement. Fig. 23 presents the student responses to the questionnaire in the year 2006. Clearly the students rated the course very highly in all the evaluation items. The course achieved such high rankings in successive years since 2005 and was placed in the top quartile among the courses offered in engineering and IT disciplines in UniSA. The rankings achieved by the course in

many evaluation items were the highest among the UniSA courses. Fig. 24 presents student responses to four key evaluation items on whether the course:

- provided opportunities to pursue independent learning (Q2)

- enabled development of graduate qualities (Q3)

- developed understanding of concepts and principles (Q5)

- provided satisfaction with overall quality (Q10)

| TABLE II                        |

|---------------------------------|

| COURSE EVALUATION QUESTIONNAIRE |

|                                 |

| # | Question                                                               |

|---|------------------------------------------------------------------------|

| 1 | I have a clear idea of what is expected of me in this course.          |

| 2 | The ways in which I was taught provided me with opportunities to       |

|   | pursue my own learning.                                                |

| 3 | The course enabled me to develop and/or strengthen a number of the     |

|   | qualities of a University of South Australia graduate.                 |

| 4 | I felt there was a genuine interest in my learning needs and progress. |

| 5 | The course developed my understanding of concepts and principles.      |

| 6 | The workload for this course was reasonable given my other study       |

|   | commitments.                                                           |

| 7 | I have received feedback that is constructive and helpful.             |

| 8 | The assessment tasks were related to the qualities of a University of  |

- 8 The assessment tasks were related to the qualities of a University of South Australia graduate.

- 9 The staff teaching in this course showed a genuine interest in their teaching.

- 10 Overall I was satisfied with the quality of this course.

Fig. 23. 2006 course evaluation responses at UniSA

Fig. 24. Responses to four key evaluation items for three consecutive years (evaluation data for 2008 is not available because the course wasn't offered)

It is clear from Fig. 24 that the course consistently achieved very high levels of student satisfaction in these areas. The intuitive design tools, the PBL methodology along with the self learning project guides contributed towards the achievement of such positive outcomes. Some representative comments from the students about the course are given below:

- "(The VLSI Design course) gives the students a very good exposure to the up to date CMOS technology. It's a specialist course."

- "Quality of practical handouts is great. Material covered is highly relevant and useful. Teaching is of an exceptionally high quality."

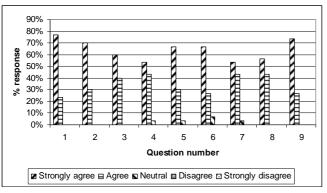

The various strategies used in the PBL approach were also anonymously evaluated by the students. The questionnaire developed for this purpose in consultation with advisers in UniSA's Learning and Teaching Unit (LTU) is given in Table III. The Likert scale responses are given in Fig. 25. Clearly the students found the PBL approach very useful for their learning. In one student's view:

"The project-based learning was very good, the first project had in depth instructions and it gradually backed off giving us time to adapt to the software and applying the theory."

TABLE III

QUESTIONNAIRE FOR EVALUATION OF THE PBL APPROACH AT UNISA

| # | Question                                                             |

|---|----------------------------------------------------------------------|

| 1 | I was able to work out how to use the CAD software by using the      |

|   | project handouts provided                                            |

| 2 | I was able to learn circuit design techniques on my own by doing the |

|   | projects using the project handouts                                  |

- 3 The handouts assisted in revisiting some of the background knowledge required for the course

- 4 The questions given in the project handouts helped me to think critically

- 5 The projects helped me put the theory of VLSI Design into practice

- 6 The final capstone project challenged me to test my learning in the course

- 7 I feel confident about completing similar capstone projects independently

- 8 The skills I learn in VLSI project work are useful to me

- 9 Overall I am satisfied with the project-based learning approach used in the VLSI Design course

Fig. 25. Student responses to evaluation of the PBL approach

#### B. INSA student evaluation

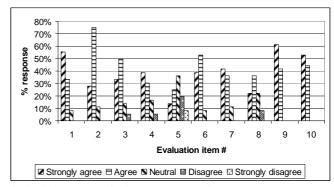

The questionnaire of Table III were also used at INSA for anonymous evaluation of the course Analog CMOS Circuit *Design* during two sessions in October 2007. The student responses are shown in Fig. 26. All respondents said that they were satisfied with the overall quality of the course (55% strongly agree, 45% agree). This is comparable to UniSA results. The feedbacks from students in 2008 were very similar to those in 2007. However, in response to item 5 some INSA students highlighted some mismatch between the theoretical part of the course, mostly related to the physics of devices, and the practical part, oriented towards layout design.

Fig. 26. 2007 course evaluation responses at INSA

Some representative comments from the students about the various aspects of PBL and the educational approach are given below:

- "From just a few logic gates, we have created a 4-stage binary counter which is ready to be realized on a silicon wafer. It also gave us the basic concepts to understand the operation of the transistors in order to extract their models and to use them in complex analog or digital circuits."

- "The 24-hours clock project was a good exercise which permitted us to see how it is inside a semiconductor and how it works."

- "Throughout this project, we learned a lot about designing integrated circuit. We learned basic design rules and we could apply these rules in a small project. We faced some practical problems, shown by the simulation, and we tried to solve them or to understand them."

- "This study allows us to understand the DAC running. In spite of some design problems, we managed to make the DAC work well."

- "Before doing this project, we hadn't thought that there are as many ways to realize an amplifier. It's an area not easy to understand. Each technique has its limit. We tried to optimize our operational amplifier design to maximize the gain."

#### C. Peer evaluation

Evaluation versions of the design tools *Dsch* and *Microwind*, the software application notes illustrating the latest nanometer technology models and the course resources are available online for faculties and students. Faculties can also obtain these materials by contacting the authors directly. The design tools are used for educational purposes by almost 500 institutions worldwide, including North America, Europe, Asia

and Australia. In India alone there are more than 200 educational institutions using full licensed versions of the above design tools. This has enabled the authors to obtain valuable feedback on various aspects of the design tools, nanometer technology models and course resources on an ongoing basis. Many faculty members have been acting as beta testers of the design tools. The critical feedback obtained from faculties and students worldwide have enabled continuing improvement and refinement of the tools and learning resources. Some representative comments from the faculty members are given below:

- "The Microwind and Dsch tools along with the projectbased course resources have assisted us to develop an educational program in Microelectronics within our Bachelor of Engineering Program. The tools offer easy to use menus for design and simulation, and the choice of a range of technology models to enable students to develop critical design and analysis skills using the latest technologies." (Lecturer, UiTM, Malaysia).

- "As far as I am aware majority of the universities in Bangladesh have been using the Microwind and Dsch tools for their VLSI teaching programs at both postgraduate and undergraduate levels. The project-based methodology supported by a variety of learning resources has made the learning of VLSI Design very stimulating." (Professor, Bangladesh University of Engineering & Technology).

- "The Microwind and Dsch programs are extremely powerful tools, and exploring them was a lot of fun. The interface is very friendly, and the program is both educational and useful for designing CMOS chips." (Late J. P. Uyemura, Professor, Georgia Institute of Technology, USA) [27].

#### VII. CONCLUSION

The use of a collection of intuitive and user friendly design tools that enable students to develop circuit design skills using modern deep submicron technology has been one of the underlying factors for the successful delivery of the digital and analog integrated circuit design courses in two institutions in Australia and France. The sharing of experience and the collaborative development of tools and resources have contributed towards deploying effective project-based learning methodologies for teaching integrated circuit design using the latest deep submicron technologies. Engaging students in design work involving a range of latest technologies have enabled them to understand the impacts of technology scale down on factors such as speed, power and noise. The important areas of modeling and simulation are covered through the utilization of simplified SPICE models for the deep submicron technologies. Using project-based learning methodologies suited to the teaching context we have successfully delivered digital and analog circuit design courses with high levels of student satisfaction. The philosophies

behind our approach have been responsiveness to the teaching context and student diversity in particular, emphasis on the development of circuit design concepts and skills rather than mastery of complex design tools, and projects that are able to stimulate student curiosity and thinking. The project-based methodology may need some adjustments based on the students' background and experience. The authors believe that these resources, tools and the project-based learning methodologies will be useful for teaching VLSI cell design in different contexts, and for developing students' technical design skills as well as the soft skills of critical thinking and lifelong learning, which are crucial in the rapidly changing field of microelectronic circuit design.

#### ACKNOWLEDGMENT

The authors would like to thank Bhupesh Purohit and Vinay Sharma of ni2designs, India for their enthusiastic support and inspiration. The authors would also like to thank the numerous academics and students worldwide who used our design tools and course resources, and sent valuable feedback. Finally the authors would like to acknowledge the partial financial support received under a UniSA teaching grant, which enabled us to employ a casual research assistant to assist with the redevelopment of some project-based learning resources.

#### REFERENCES

- S. Natarajan and et. al. "A 32nm Logic Technology Featuring 2nd-Generation High-k + Metal-Gate Transistors, Enhanced Channel Strain and 0.171um2 SRAM Cell Size in a 291Mb Array", Proceedings of IEDM 2008.

- [2] S. K. Han, "Highly Manufacturable Single Metal Gate Process Using Ultra-Thin Metal Inserted Poly-Si Stack (UT-MIPS)," IEDM 2006, pp. 621.

- [3] R. Chau, et. al. "Gate Dielectric Scaling for High-Performance CMOS : From SiO<sub>2</sub> to High-K," IEDM Technical Digest, 2004

- [4] A. Oishi, et. al. "High performance CMOSFET technology for 45nm generation and scalability of stress-induced mobility enhancement technique", IEEE International Electron Devices Meeting, 2005. IEDM Technical Digest. 2005 pp. 229 - 232

- [5] S. Tyagi, et. al. "An advanced low power, high performance, strained channel 65nm technology," in *Digest Int. Electron Devices Meeting* (*IEDM*), 2005, pp. 245 – 247.

- [6] F. Boeuf and S. Huiling, "CMOS devices mobility enhancement and low resistance source/drain," in *Digest Int. Electron Devices Meeting* (*IEDM*), 2005, pp. 128 - 128.

- [7] International Technology Roadmap for Semiconductors (ITRS), 2008, http://www.itrs.net/Links/2008ITRS/Home2008.htm

- [8] T. Ghani et. al. "A 90nm high volume manufacturing logic technology featuring novel 45nm gate length strained silicon CMOS transistors", Digest of International Electron Devices Meeting 2003, IEDM '03.

- [9] P. Bai et.al., "A 65nm logic technology featuring 35nm gate lengths, enhanced channel strain, 8 Cu interconnect layers, low-k ILD and 0.57 μm<sup>2</sup> SRAM cell", IEDM 2004, 13-15 Dec. 2004, pp. 657 – 660

- [10] R. S. Chau, "Integrated CMOS Tri-Gate Transistors: Paving the Way to Future Technology Generations", Technology@Intel Magazine, pp. 1-7, Aug. 2006, www.intel.com/technology/silicon/integrated\_cmos.htm

- [11] C. Hacker and R. Sitte, "Interactive Teaching of Elementary Digital Logic With WinLogiLab", *IEEE Trans. Education*, Vol. 47, no. 2, May 2004, pp 196-203.

- [12] C. J. Tseng "Digital System Design Using Microarchitectural Modeling", *IEEE Trans. Education*, vol. 51, no. 1, Feb. 2008, pp. 93 – 99.

#### Proposal to IEEE Transaction on Education

- [13] T. A. Hudson, E. R. Doering and L.T. Gwen, "Teaching mixed-signal integrated circuit design to undergraduates," *IEEE Trans. Education*, vol. 49, no. 1, pp. 39 – 48, Feb. 2006.

- [14] J. S. Yuan and J. Di, "Teaching Low-Power Electronics Design in Electrical and Computer Engineering", *IEEE Trans. Education*, Vol. 48, no. 1, Feb. 2005, pp 169-181.

- [15] A. I. Kayssi, "The Average Capacitor Current Method for Delay Calculation in MOS Circuits", *IEEE Trans. Education*, Vol. 47, no. 3, Aug. 2004, pp 330-339.

- [16] B. Mazhari, "Amplifier Analysis: A Tradeoff Perspective", *IEEE Trans. Education*, Vol. 48, no. 1, Feb. 2005, pp 111-117.

- [17] S. Karmalkar, "Introducing the Device Modeling Procedure to Electrical Engineering Students", *IEEE Trans. Education*, Vol. 50, no. 2, May 2007, pp 137-142.

- [18] J. Masters, T. M. Madhyastha, A. Shakouri, "Educational Applets for Active Learning in Properties of Electronics Materials", *IEEE Trans. Education*, Vol. 48, no. 1, Feb. 2005, pp 29-35.

- [19] EUROPRACTICE IC Service, www.europractice.com

- [20] MOSIS Educational Program, www.mosis.com/products/mep/

- [21] S. M. Aziz, "Teaching in a Diverse Class: A Structured Project-based Approach", in *Innovations 2006: World Innovations in Engineering Education and Research*, W. Aung et al., Eds., Arlington: Int. Network for Eng. Ed. and Res. (iNEER), 2006.

- [22] S. M. Aziz, "Internationalisation as a Change Dynamic in Engineering Education: Issues and Challenges", in *Proc. 2005 ASEE/AaeE 4<sup>th</sup> Global Colloquium Engineering Education*, Sydney, 2005.

- [23] E. Sicard and S. Ben Dhia "Basic CMOS Cell Design" McGraw Hill professional series, 2006.

- [24] E. Sicard and S. Ben Dhia "Advanced CMOS Cell Design" McGraw-Hill professional series, 2007.

- [25] E. Sicard, Microwind & Dsch User's Manual, Version 3.1, June 2007. Online at www.microwind.org.

- [26] M. Smith, WinSpice3 User's Manual, October 2003. Online at www.winspice.com.

- [27] J. P. Uyemura, Chip Design for Submicron VLSI: CMOS Layout and Simulation, Thomson Learning, 2005.

- [28] Y. P. Tsividis, "Operating and Modeling of the MOS transistor", Oxford University Press, 2nd edition, 2003.

- [29] S. M. Sze and K. K. Ng, "Physics of Semiconductor Devices", 3rd edition, John-Wiley, 2006.

- [30] W. Shockley "A Unipolar field effect transistor", Proceedings of IRE, Vol. 40, Nov. 1952, pp.1365-1376.

- [31] N. Weste, K. Eshraghian and M. Smith, "Principles of CMOS VLSI Design: A circuits & systems perspectives", Addison Wesley, 3rd edition, 2004.

- [32] W. Liu, "MOSFET Models for SPICE simulation including Bsim3v3 and BSIM4", Wiley & Sons, 2001.

- [33] S. M. Aziz, "Learner Centric Education in VLSI Design", in Innovations 2005: World Innovations in Engineering Education and Research, W. Aung et al., Eds., Arlington: Int. Network for Eng. Ed. and Res. (iNEER), 2005, pp. 69-78.

[34] F. Corsi and C. Marzocca., "An approach to the analysis of the CMOS

- [34] F. Corsi and C. Marzocca., "An approach to the analysis of the CMOS differential stage with active load and single-ended output," *IEEE Trans. Education*, Vol. 46, no. 3, Aug. 2003 pp. 325 – 328.

- [35] J. He and X. Xi, "BSIM5: An advanced charge-based MOSFET model for nanoscale VLSI circuit simulation", *Solid-State Electronics*, Vol. 51, Issue 3, March 2007, Pages 433-444.

Syed Mahfuzul Aziz received Bachelor and Masters degrees in Electrical and Electronic Engineering in 1984 and 1986 respectively. He received a Ph.D. degree in Electronic Engineering from the University of Kent (UK) in 1993 and a Graduate Certificate in Higher Education from Queensland University of Technology in 2002. He is an Associate Professor and the inaugural Academic Director of the common First Year

Engineering program at the University of South Australia. Dr. Aziz has been engaged in university teaching and research for twenty three years. In 1996, he was a visiting scholar at the University of Texas at Austin when he spent time at Crystal Semiconductor Corporation designing advanced CMOS circuits. He has received national and international recognitions for his innovative teaching methods including the Australian *Carrick Citations* for

outstanding contributions to student learning (2007) and the International Network for Engineering Education and Research *Achievement Award* (2007). His research interests include modeling and FPGA implementation of high performance processors, CMOS circuit design and testability, biomedical engineering and engineering education. He is a senior member of IEEE.

Sonia Ben Dhia received the engineering diploma in 1995, and the Ph.D. in Electronic Design from the National Institute of Applied Sciences (INSA), Toulouse, France, in 1998. She is currently at the rank of associate professor at INSA-Toulouse, Department of Electrical and Computer Engineering where she teaches digital electronics, IC testability and reliability,

and analog and RF CMOS design. Dr Ben Dhia is part of the INSA Studies Directorate board to organize transversal educational courses and take care of internal organization. She is also in charge of the promotion of IT in teaching. Her research interests include signal integrity in deep sub-micron CMOS ICs and electromagnetic compatibility of ICs. She has authored technical papers on signal integrity and EMC. She contributed to the publication of three books, two for educational purposes based on the Microwind software and one dealing with research topics on EMC of ICs.

**Etienne Sicard** received the B.Sc degree in 1984 and the PhD in Electrical Engineering from the University of Toulouse, France, in 1987. He stayed 18 months at Osaka University, Japan, and one year as an invited professor at the University of Balearic Islands, Spain. Etienne SICARD is currently a professor at INSA of Toulouse, Department of Electrical and Computer Engineering. He was a visiting professor at the electronic department of Carleton University, Ottawa, Canada in 2004. His research interests include several aspects of CAD tools for the design and electromagnetic compatibility of integrated circuits. He is the author of books, software and more than 100 technical papers in these areas. Etienne is a member of the SEE and IEEE societies.