# Novel Architecture of Smart FFT Processor

Rozita Teymourzadeh

# ▶ To cite this version:

Rozita Teymourzadeh. Novel Architecture of Smart FFT Processor. 2014. hal-01802071

# HAL Id: hal-01802071 https://hal.science/hal-01802071v1

Submitted on 28 May 2018

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# NOVEL ARCHITECTURE OF 1024-POINT HIGH EFFICIENT FFT PROCESSOR

Author: Asst. Prof. Dr. Rozita Teymourzadeh, CEng. Formatted by: Kok Wai Chan

# CONTENTS

|               |                                                                             | Page     |

|---------------|-----------------------------------------------------------------------------|----------|

| CONTENTS      |                                                                             | i        |

| LIST OF FIGUR | ES                                                                          | iv       |

| LIST OF TABLE | CS .                                                                        | X        |

| LIST OF SYMBO | DLS                                                                         | xi       |

| LIST OF ABBRE | EVIATIONS                                                                   | xii      |

| CHAPTER I     | INTRODUCTION                                                                |          |

| 11            | Background                                                                  | 1        |

| 1.2           | Problem Statement                                                           | 2        |

| 1.3           | Motivation                                                                  | 3        |

| 1.4           | Objective                                                                   | 5        |

| 1.5           | Scope of Work                                                               | 5        |

| 1.6           | Project Workflow                                                            | 6        |

| 1.7           | Methodology                                                                 | 8        |

| 1.8           | Chapter Organization                                                        | 8        |

| CHAPTER II    | AN OVERVIEW OF FFT ALGORITHM                                                |          |

| 2.1           | Discrete Fourier Transform (DFT)                                            | 10       |

| 2.2           | Fast Fourier Transform (FFT)                                                | 12       |

| 2.3           | Floating Point FFT Algorithm                                                | 13       |

| 2.4           | Floating Point FFT Application                                              | 14       |

|               | <ul><li>2.4.1 Instrumentation</li><li>2.4.2 Communication systems</li></ul> | 16<br>18 |

| 2.5           | Literature Review                                                           | 22       |

| 2.6           | Summary                                                                     | 32       |

| CHAPTER III   | FAST FOURIER TRANSFORM STRUCTURE                                            |          |

| 3.1           | Introduction                                                                | 34       |

| 3.2           | FFT type structure                                                          | 35       |

|               | 3.2.1 DIT radix_2 butterfly FFT 3.2.2 DIF radix_2 butterfly FFT             | 35<br>43 |

| 3.3           | Comparison of DIT-FFT and DIF-FFT Architecture                              | 48       |

| 3.4           | FFT Processor architecture type                                             | 48       |

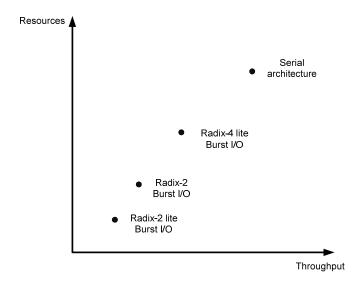

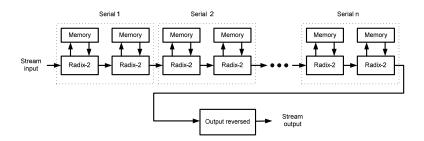

|            | <ul> <li>3.4.1 FFT processor with radix-2 pipelined serial I/O</li> <li>3.4.2 FFT processor with radix-4 burst I/O</li> <li>3.4.3 FFT processor with radix-2 burst I/O</li> <li>3.4.4 FFT processor with radix-2 lite burst I/O</li> </ul>                                                          | 50<br>51<br>52                         |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 3.5        | FFT Processor and input signal                                                                                                                                                                                                                                                                      | 53                                     |

| 3.6        | Summary                                                                                                                                                                                                                                                                                             | 55                                     |

| CHAPTER IV | THE FLOATING POINT PARALLEL PIPELINE (FRADIX-2 FFT PROCESSOR                                                                                                                                                                                                                                        |                                        |

| 4.1        | Data structure                                                                                                                                                                                                                                                                                      | 58                                     |

|            | <ul><li>4.1.1 Floating point data format</li><li>4.1.2 Biased exponent</li></ul>                                                                                                                                                                                                                    | 58<br>60                               |

| 4.2        | Stage realization of FPP-FFT processor                                                                                                                                                                                                                                                              | 60                                     |

|            | <ul> <li>4.2.1 Bit reverse</li> <li>4.2.2 Radix-2 butterfly architecture</li> <li>4.2.3 Proposed floating point adder/subtractor</li> <li>4.2.4 Proposed floating point multiplier</li> <li>4.2.5 Controller architecture</li> <li>4.2.6 Address generator</li> <li>4.2.7 Memory modules</li> </ul> | 62<br>63<br>67<br>83<br>90<br>95       |

| 4.3        | Advantages of the proposed processor                                                                                                                                                                                                                                                                | 100                                    |

| 4.4        | Summary                                                                                                                                                                                                                                                                                             |                                        |

| CHAPTER V  | FUNCTIONAL VERIFICATION OF FFT SPECIFICATION                                                                                                                                                                                                                                                        |                                        |

| 5.1        | 8-Point FFT simulation module                                                                                                                                                                                                                                                                       | 102                                    |

| 5.2        | 1024-Point FFT simulation result                                                                                                                                                                                                                                                                    |                                        |

| 5.3        | Proposed floating-point FFT application                                                                                                                                                                                                                                                             |                                        |

| 5.4        | Summary                                                                                                                                                                                                                                                                                             |                                        |

| CHAPTER VI | IMPLEMENTATION RESULT                                                                                                                                                                                                                                                                               |                                        |

| 6.1        | Hardware implementation of 1024-point FPP-FFT                                                                                                                                                                                                                                                       | 119                                    |

|            | <ul> <li>6.1.1 Top-module of radix-2 FPP-FFT processor</li> <li>6.1.2 Bit reverse implementation</li> <li>6.1.3 Radix-2 butterfly implementation</li> <li>6.1.4 Controller unit architecture</li> <li>6.1.5 RAM and ROM architecture</li> <li>6.1.6 Address generator architecture</li> </ul>       | 120<br>125<br>128<br>152<br>155<br>159 |

| 6.2        | FPGA downloading (Xilinx ISE software)                                                                                                                                                                                                                                                              | 167                                    |

| 6.3        | ASIC Implementation (Gate level synthesis)                                                                                                                                                                                                                                                          |                                        |

| 6.4         | Research contribution       | 190 |

|-------------|-----------------------------|-----|

| 6.5         | Summary                     | 192 |

| CHAPTER VII | CONCLUSIONS AND FUTURE WORK |     |

| 7.1         | Conclusions                 | 194 |

| 7.2         | Future work                 | 196 |

|             |                             |     |

| REFERENCES  |                             | 197 |

# LIST OF FIGURES

| Figure No. |                                                                                              | Page |

|------------|----------------------------------------------------------------------------------------------|------|

| 1.1        | Overall comparison framework between fixed and proposed floating point radix-2 FFT processor | 7    |

| 2.1        | Harmonic analysis of the motor using FFT processor                                           | 17   |

| 2.2        | Conventional MCM transceiver                                                                 | 21   |

| 2.3        | The 4G OFDM transceiver with FFT/IFFT modulator                                              | 21   |

| 2.4        | Radix-4 FFT architecture introduced                                                          | 23   |

| 2.5        | Floating-point FFT processor                                                                 | 25   |

| 2.6        | Pipelined FFT processor architecture                                                         | 27   |

| 2.7        | CFMR FFT processor                                                                           | 28   |

| 2.8        | Block floating point arithmetic                                                              | 30   |

| 3.1        | 8-point FFT twiddle factor                                                                   | 37   |

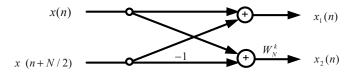

| 3.2        | 2-point butterfly in DIT FFT algorithm                                                       | 38   |

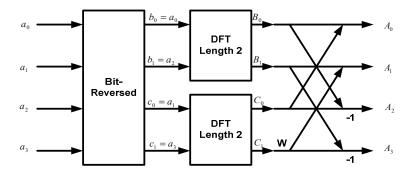

| 3.3        | Final decomposition of 8-point DIT-FFT                                                       | 38   |

| 3.4        | Flow graph of the final decomposition of 4-point DIT-FFT                                     | 40   |

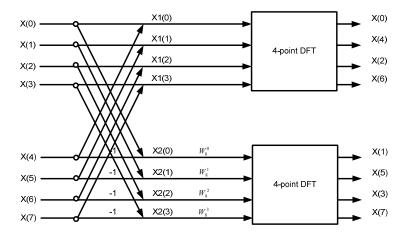

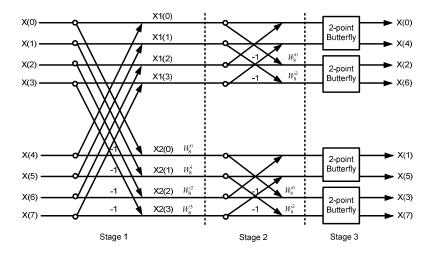

| 3.5        | Flow graph of the final decomposition of 8-point DIT-FFT                                     | 41   |

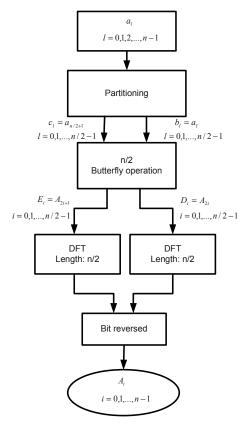

| 3.6        | Flow chart of Radix 2 DIT-FFT structure                                                      | 42   |

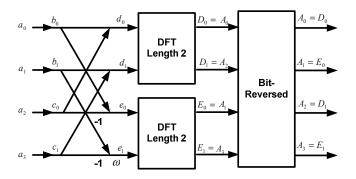

| 3.7        | 4-point Radix-2 DIT-FFT structure                                                            | 43   |

| 3.8        | 2-point butterfly in DIF-FFT algorithm                                                       | 44   |

| 3.9        | Final decomposition of 8-point DIF-FFT processor                                             | 45   |

| 3.10       | Internal calculation of 8-point DIF-FFT processor                                            | 46   |

| 3.11       | Flow chart of radix-2 DIF-FFT structure                                                      | 47   |

| 3.12       | 4-point radix-2 DIF-FFT structure                                                            | 47   |

| 3.13       | Comparison between available resources of FFT architecture                                   | 49   |

| 3.14       | FFT processor with pipeline serial I/O architecture                                          | 50   |

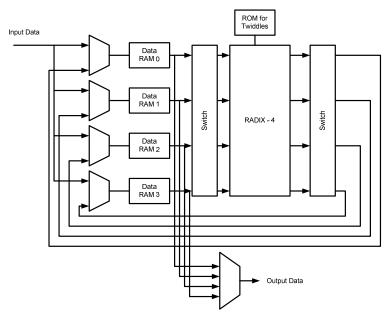

| 3.15       | FFT Processor with radix-4 architecture                                                      | 51   |

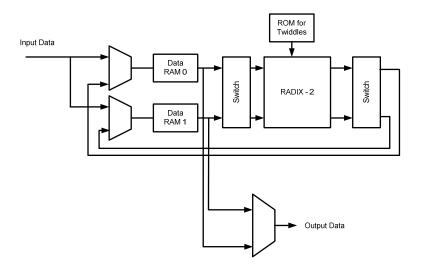

| 3.16 | FFT Processor with radix-2 burst I/O architecture                    | 52 |

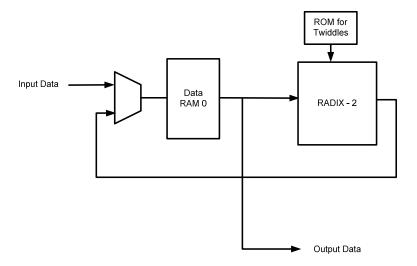

|------|----------------------------------------------------------------------|----|

| 3.17 | FFT Processor with radix-2 Lite burst I/O architecture               | 53 |

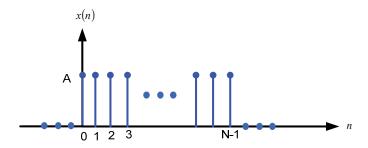

| 3.18 | Single rectangular pulse                                             | 54 |

| 3.19 | Rectangular frequency responses                                      | 55 |

| 4.1  | Hardware design methodology framework                                | 57 |

| 4.2  | 32-bit floating-point registers                                      | 59 |

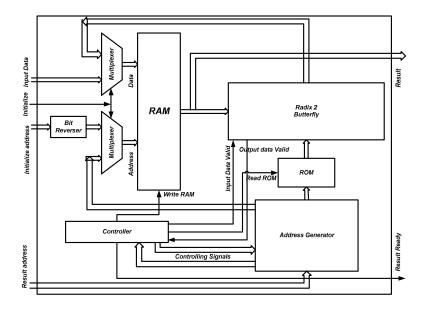

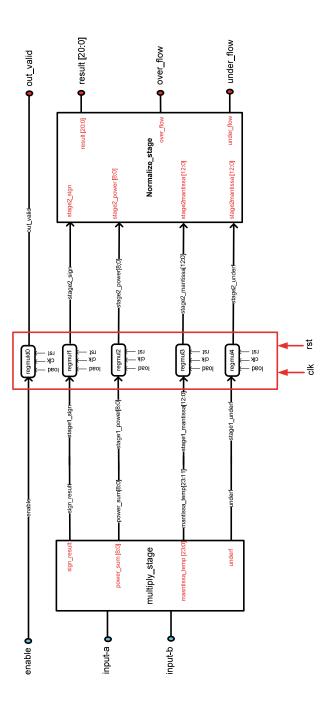

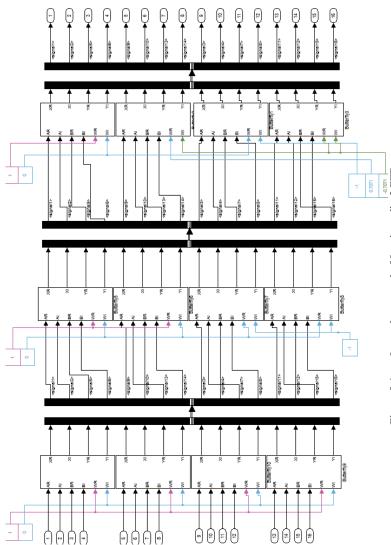

| 4.3  | 1024 point radix-2 FPP-FFT block diagrams                            | 62 |

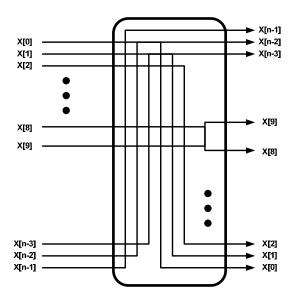

| 4.4  | Bit-reverse block                                                    | 63 |

| 4.5  | Proposed butterfly architecture                                      | 64 |

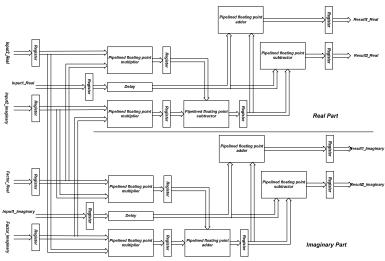

| 4.6  | Internal architecture of radix-2 butterfly                           | 65 |

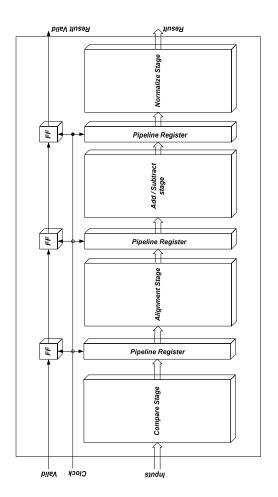

| 4.7  | The schematic diagram of floating point adder                        | 68 |

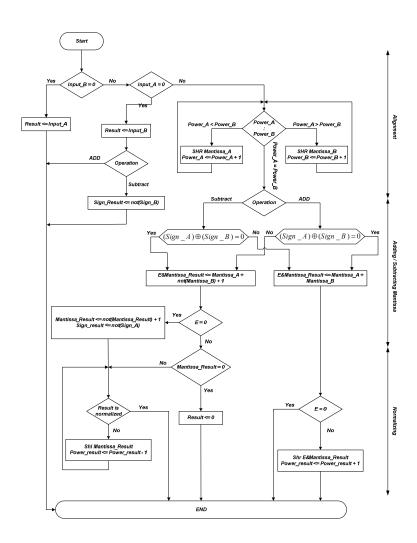

| 4.8  | Floating point adder algorithm                                       | 69 |

| 4.9  | Optimized floating point adder algorithm                             | 70 |

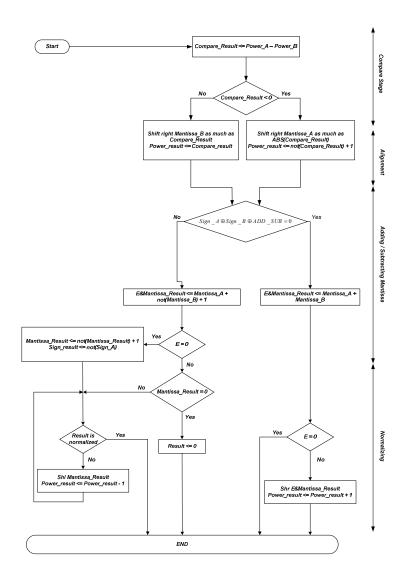

| 4.10 | The schematic of comparison stage structure                          | 72 |

| 4.11 | The internal architecture of comparison stage                        | 72 |

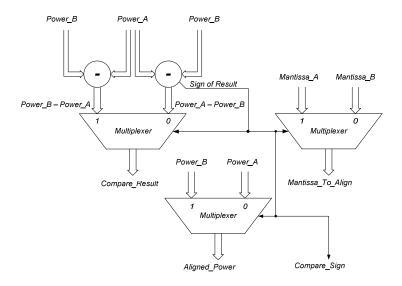

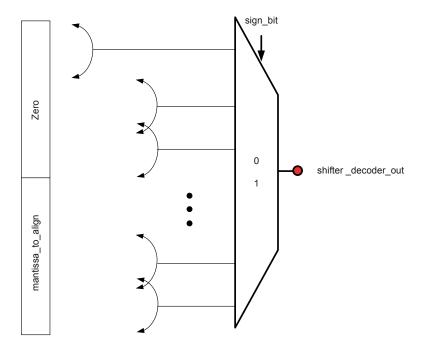

| 4.12 | The schematic diagram of the alignment unit                          | 74 |

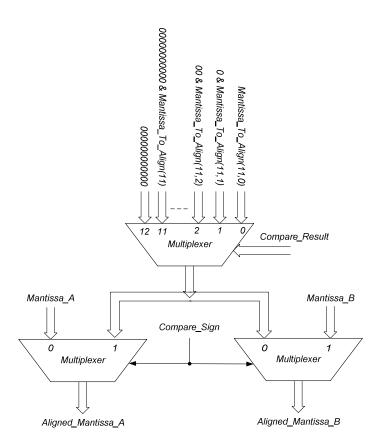

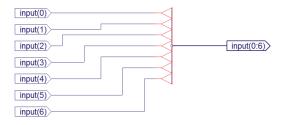

| 4.13 | The multiplexer architecture of the alignment stage                  | 75 |

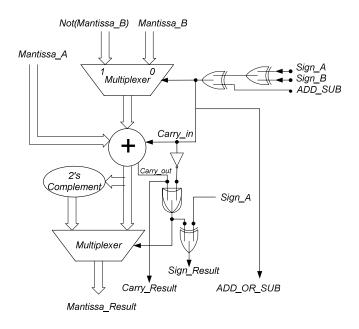

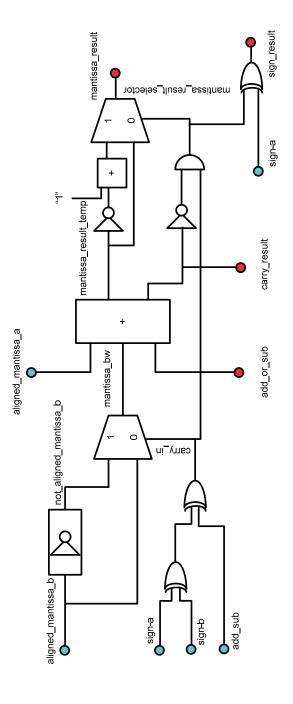

| 4.14 | The schematic of addition/subtraction unit                           | 76 |

| 4.15 | The addition/subtraction unit architecture                           | 77 |

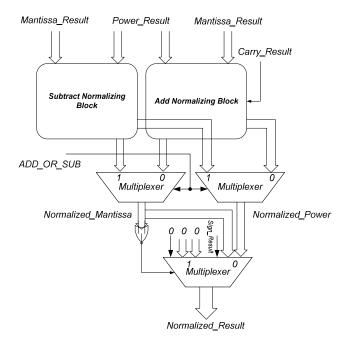

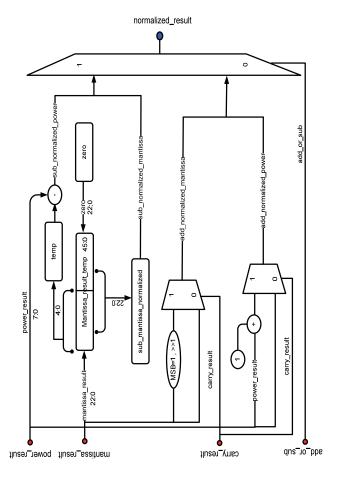

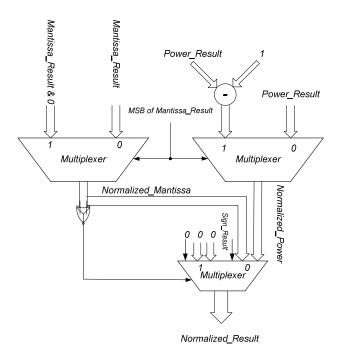

| 4.16 | The schematic of normalized unit structure                           | 79 |

| 4.17 | The internal architecture of normalized unit                         | 80 |

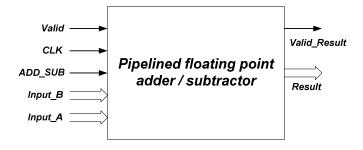

| 4.18 | I/O structure of the proposed floating point adder                   | 81 |

| 4.19 | The proposed pipeline floating point adder/subtractor architecture   | 82 |

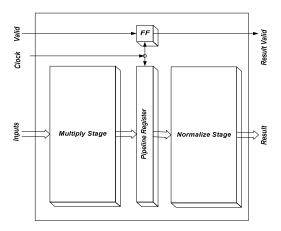

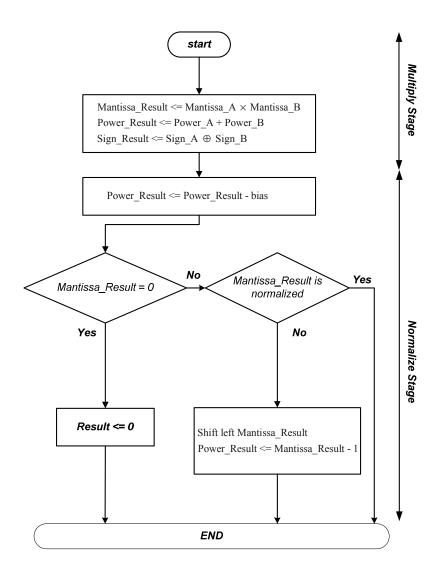

| 4.20 | The schematic diagram of floating point multiplier                   | 83 |

| 4.21 | The flow chart of floating point multiplier                          | 84 |

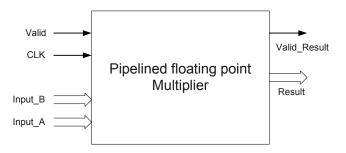

| 4.22 | The schematic symbol of the proposed floating point multiplier       | 85 |

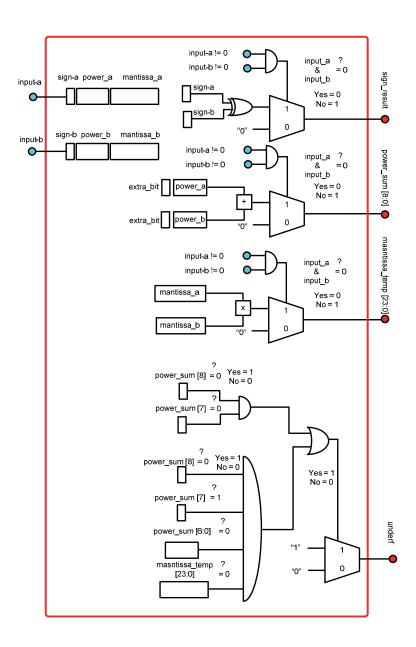

| 4.23 | The schematic architecture of the proposed floating point multiplier | 86 |

| 4.24 | The structure of the normalized stage in the proposed multiplier     | 87 |

| 4.25 | multiplier                                                                    | 88  |

|------|-------------------------------------------------------------------------------|-----|

| 4.26 | The intermediate architecture of the proposed multiplier                      | 89  |

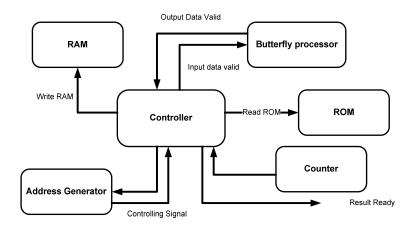

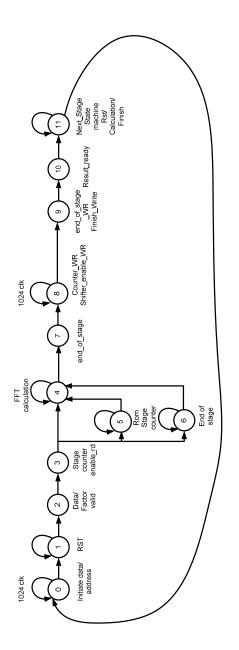

| 4.27 | Block diagram of controller unit                                              | 90  |

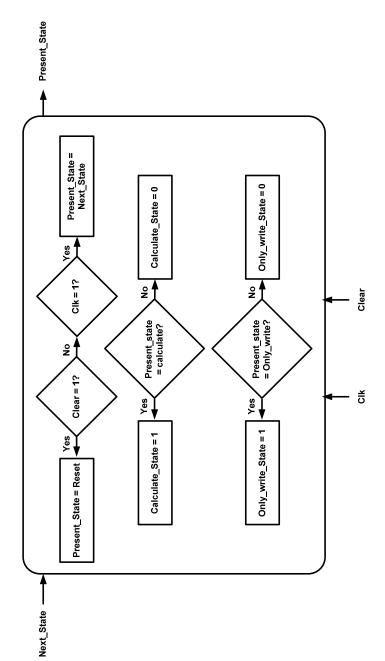

| 4.28 | State machine block diagram for controller unit                               | 92  |

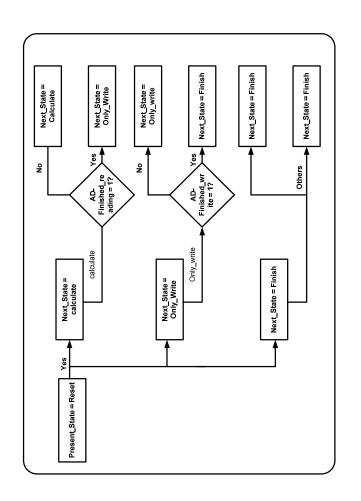

| 4.29 | Sequential algorithm of controller unit                                       | 93  |

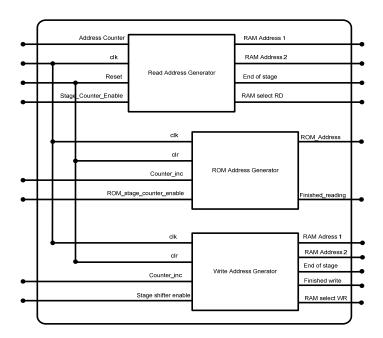

| 4.30 | Combination algorithm of controller unit                                      | 94  |

| 4.31 | Internal structure of address generator unit                                  | 96  |

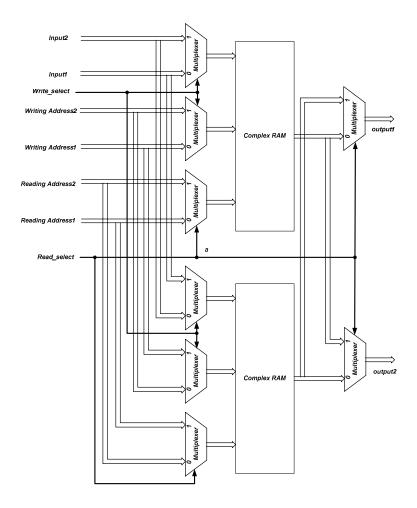

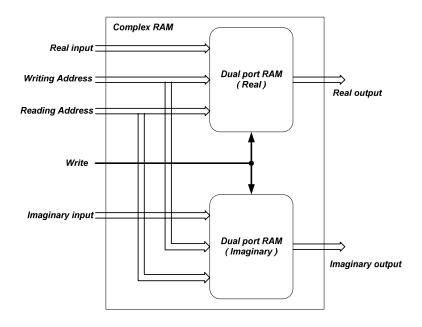

| 4.32 | Internal structure of RAM unit                                                | 98  |

| 4.33 | Internal structure of complex RAM unit                                        | 99  |

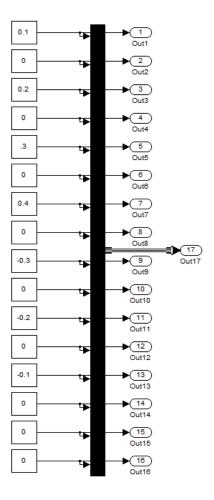

| 5.1  | The input sampled data for 8-point FFT calculations                           | 103 |

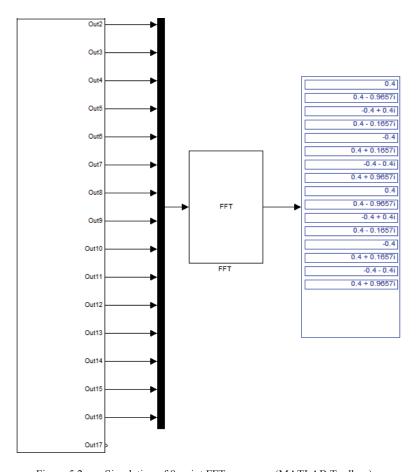

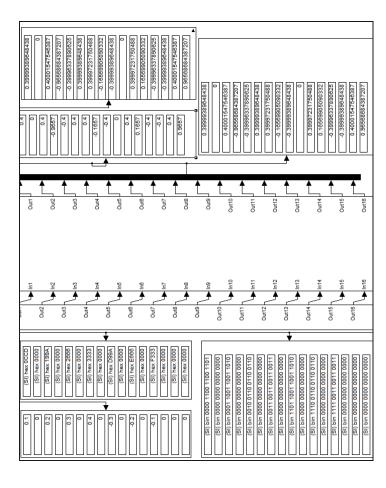

| 5.2  | Simulation of 8-point FFT processor (MATLAB Toolbox)                          | 104 |

| 5.3  | MATLAB Simulation of 8-point radix-2 FFT processor                            | 105 |

| 5.4  | Internal structural of 8-point radix-2 FFT processor                          | 106 |

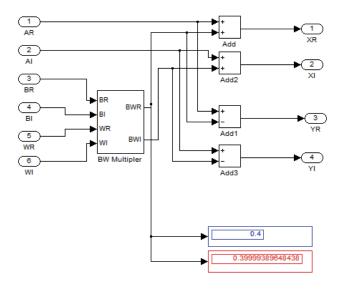

| 5.5  | MATLAB simulation of Butterfly unit in Radix-2 processor                      | 107 |

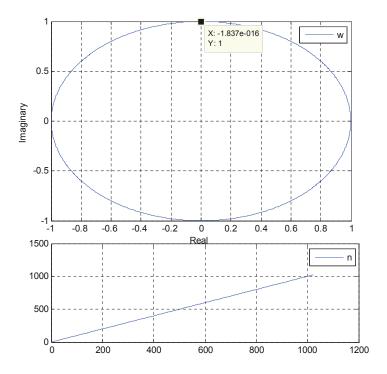

| 5.6  | Twiddle factor when $N = 1024$                                                | 108 |

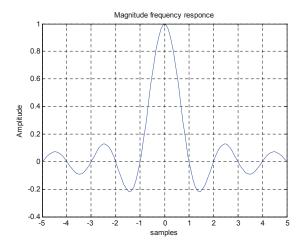

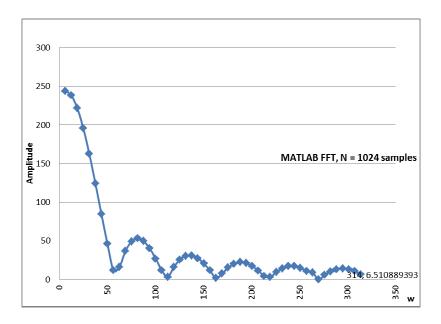

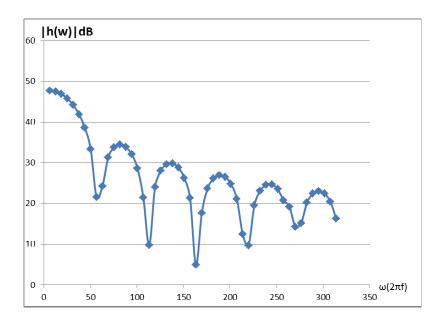

| 5.7  | MATLAB simulation of amplitude frequency response of                          | 110 |

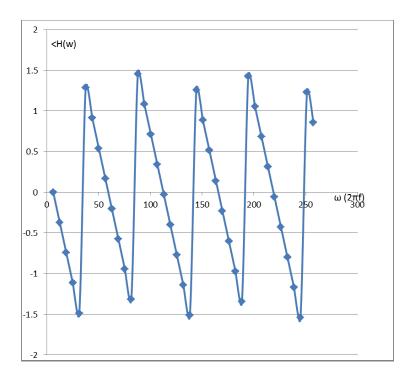

|      | the rectangular input signal MATLAB simulation of phase frequency response of |     |

| 5.8  | the rectangular input signal                                                  | 111 |

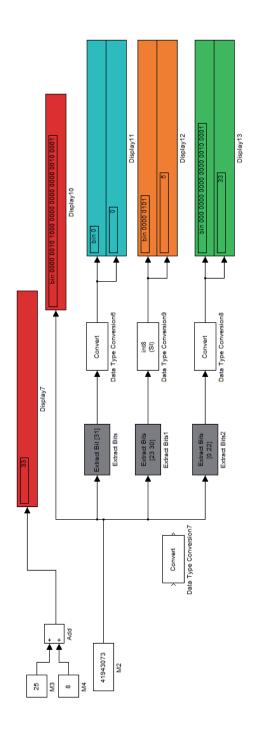

| 5.9  | MATLAB simulation of floating point data structure                            | 112 |

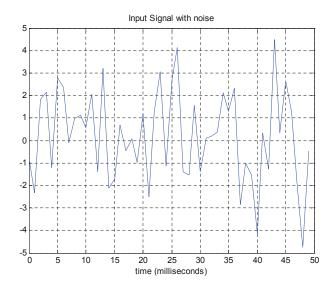

| 5.10 | The noisy input signal in time domain                                         | 113 |

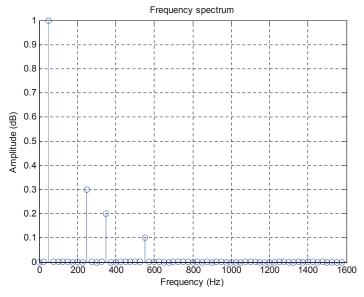

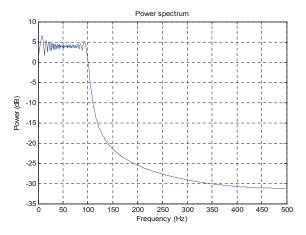

| 5.11 | The harmonic measurement of noisy signal with floating-point FFT              | 114 |

| 5.12 | The harmonic measurement of noisy signal with fixed-point FFT                 | 114 |

| 5.13 | The MATLAB simulation of power spectrum using floating-point FFT              | 115 |

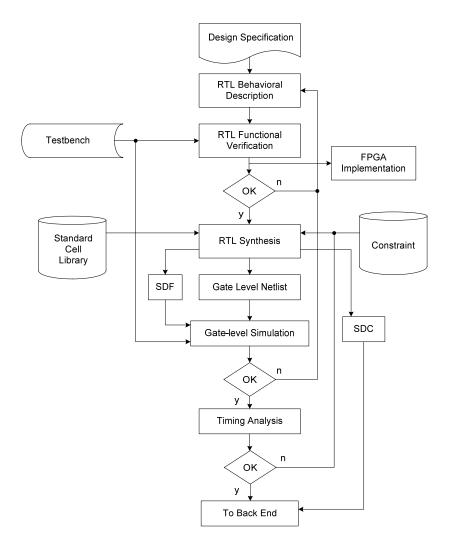

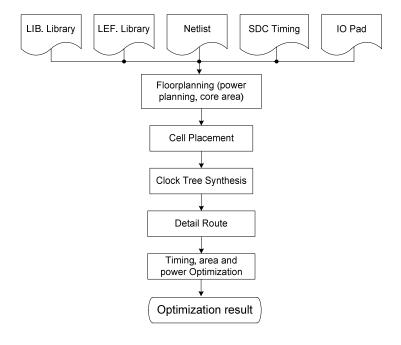

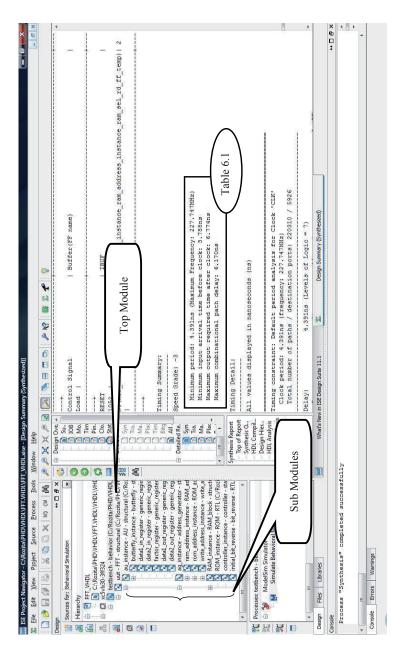

| 6.1  | VLSI Front end design flow of the project                                     | 118 |

| 6.2  | VLSI back end design flow of the project                                      | 119 |

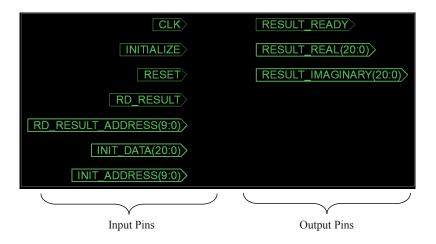

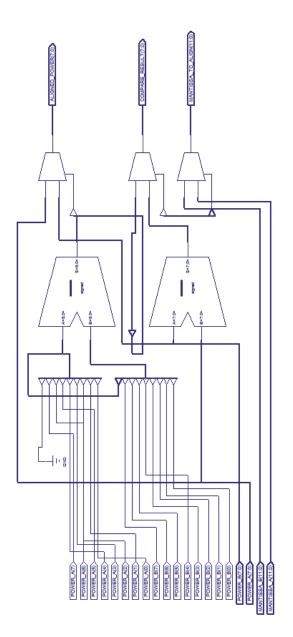

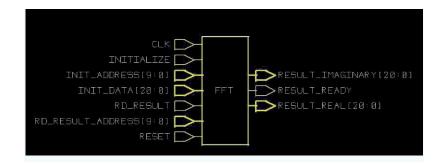

| 6.3  | Input/Output pins of the FPP-FFT processor                                    | 120 |

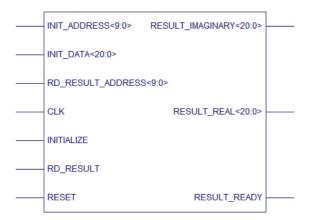

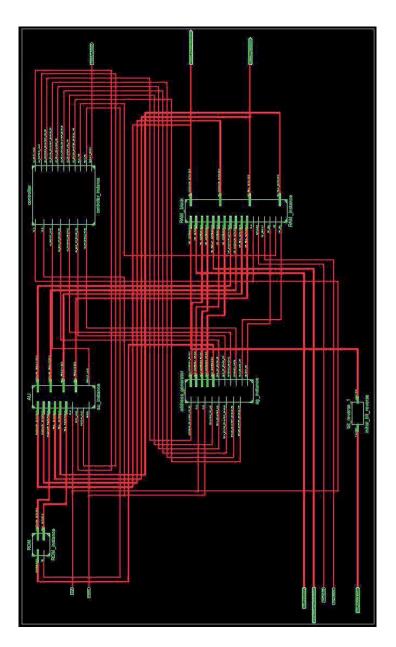

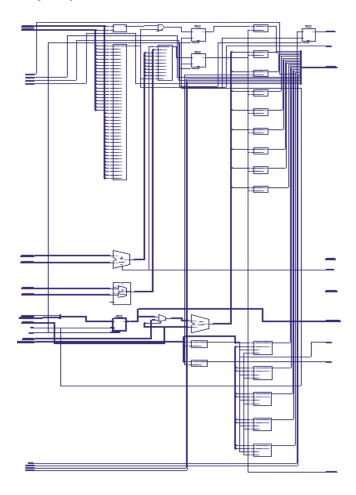

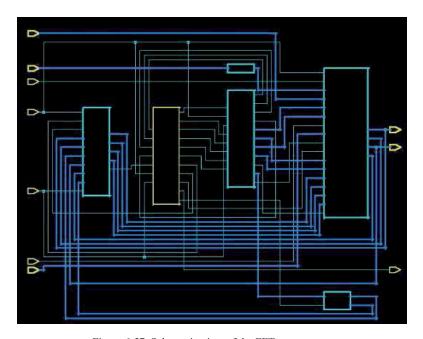

| 6.4  | FPP-FTT processor top level                                                   | 121 |

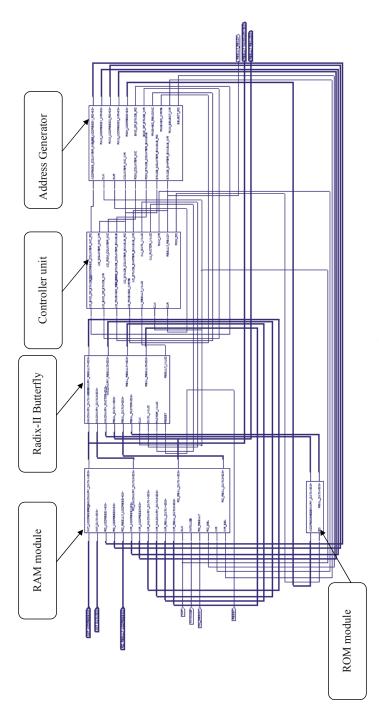

| 6.5  | Proposed 1024-point pipelined floating point FPP-FTT processor                | 122 |

| 6.6  | Behavioral layout of FPP-FTT processor                     | 123 |

|------|------------------------------------------------------------|-----|

| 6.7  | Internal behavioral layout of FPP-FTT processor            | 124 |

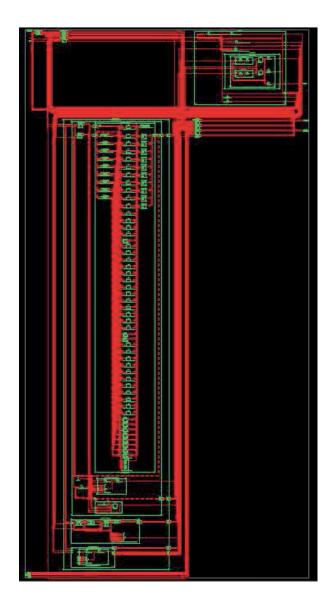

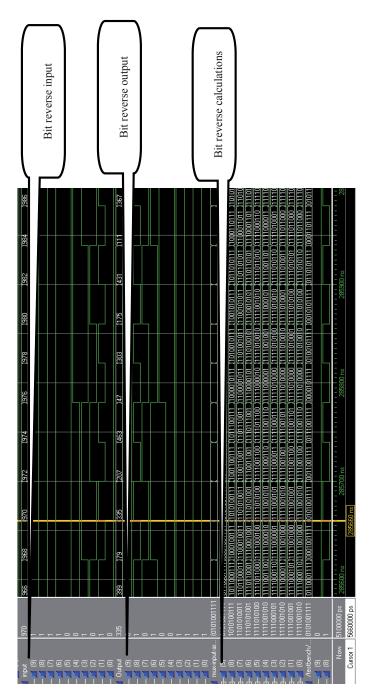

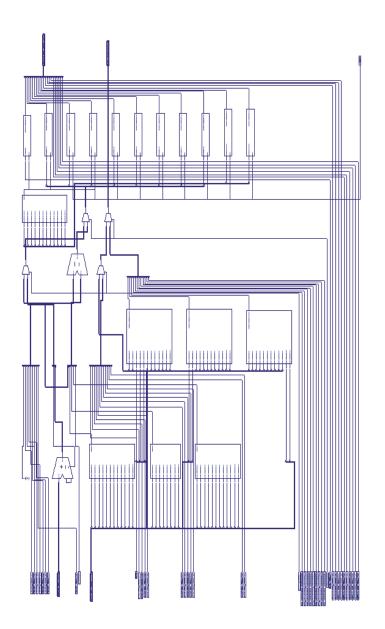

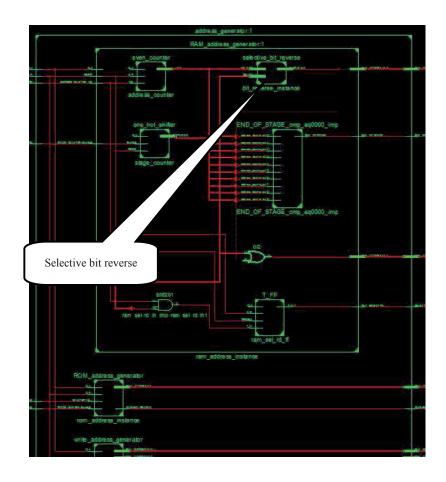

| 6.8  | Bit-reverse implementation                                 | 125 |

| 6.9  | Internal structural layout of bit-reverse                  | 126 |

| 6.10 | Bit-reverse input/output signal                            | 127 |

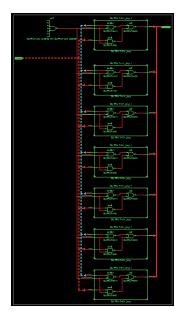

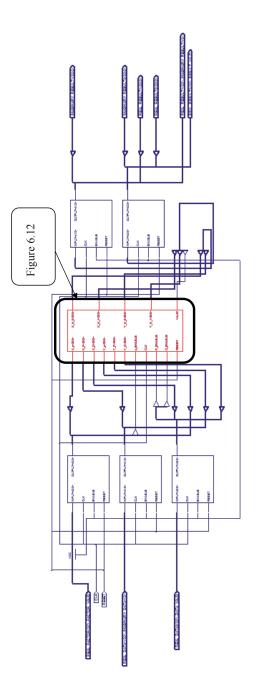

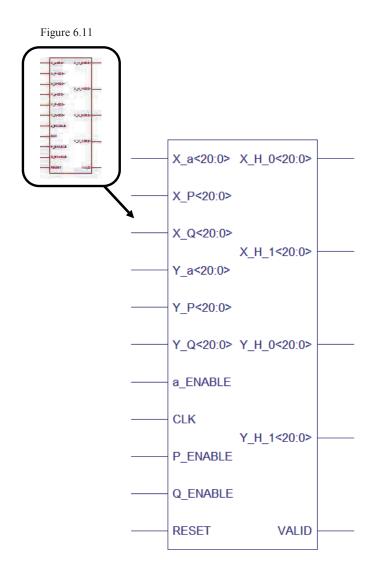

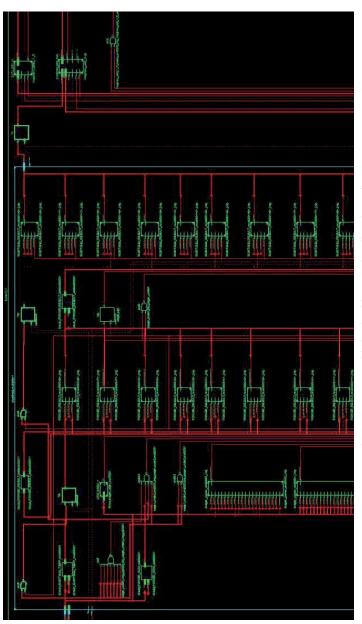

| 6.11 | Radix-2 butterfly architecture with pipeline registers     | 129 |

| 6.12 | Top- module of Radix-II butterfly architecture             | 130 |

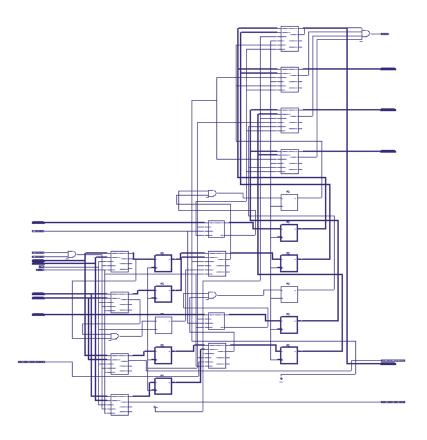

| 6.13 | Internal butterfly architecture                            | 131 |

| 6.14 | Internal behavioral layout of Radix-2 butterfly            | 132 |

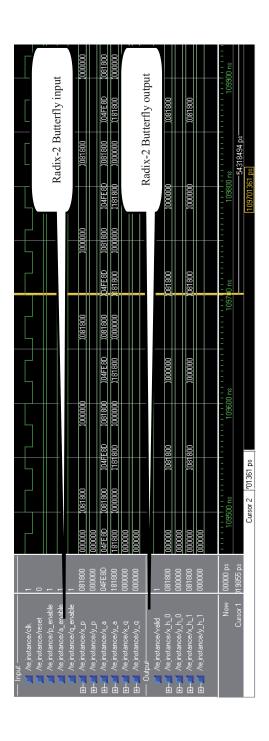

| 6.15 | Input and output signal of Radix-2 butterfly               | 133 |

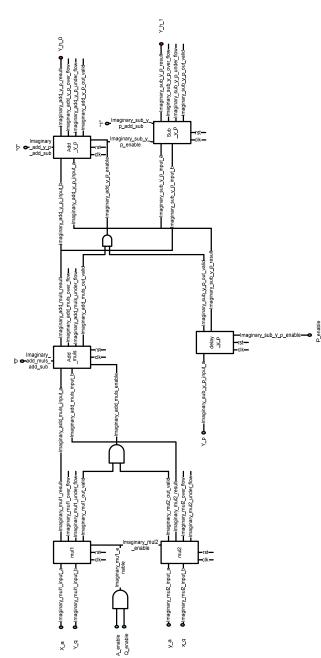

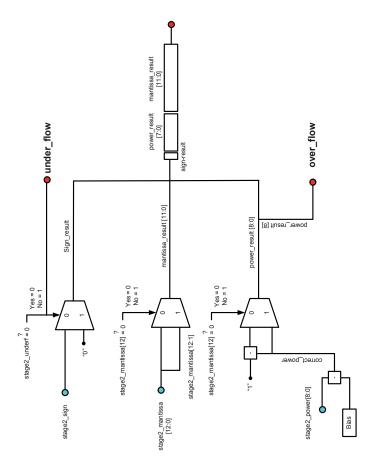

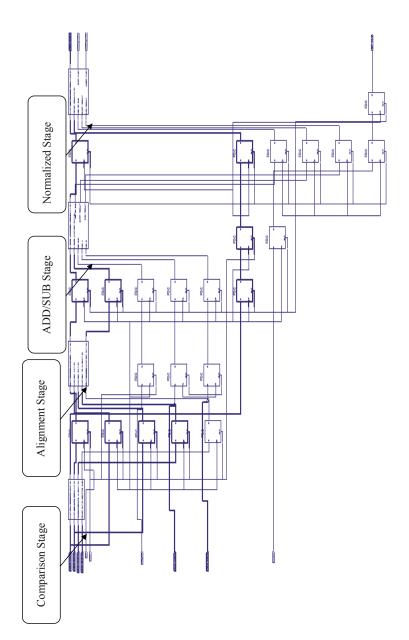

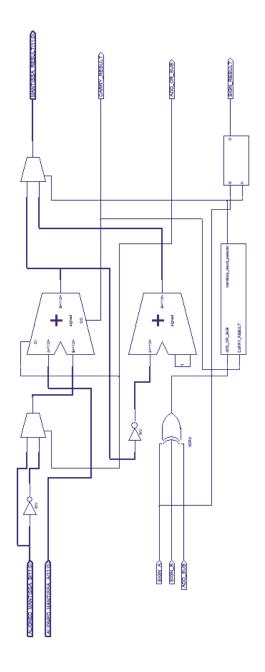

| 6.16 | Fast floating-point adder/subtractor internal architecture | 135 |

| 6.17 | Fast floating point adder/subtractor layout                | 136 |

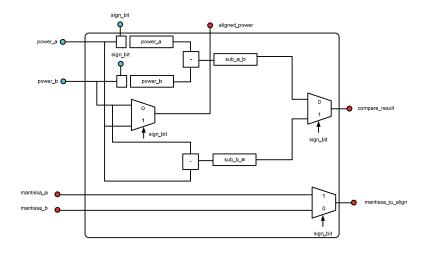

| 6.18 | Comparison stage internal architecture                     | 137 |

| 6.19 | Alignment stage internal architecture                      | 138 |

| 6.20 | Adder/Subtractor stage internal architecture               | 139 |

| 6.21 | Normalized stage internal architecture                     | 140 |

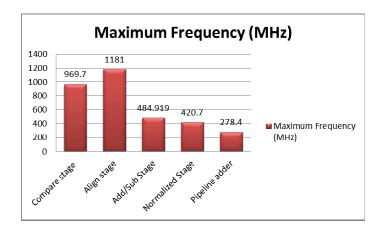

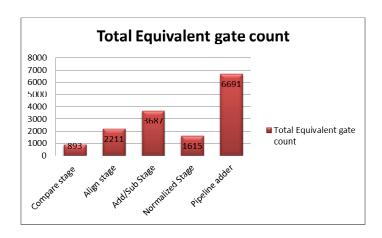

| 6.22 | Adder stage frequency comparison                           | 144 |

| 6.23 | Adder stage frequency comparison                           | 145 |

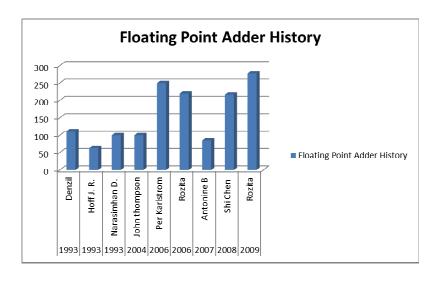

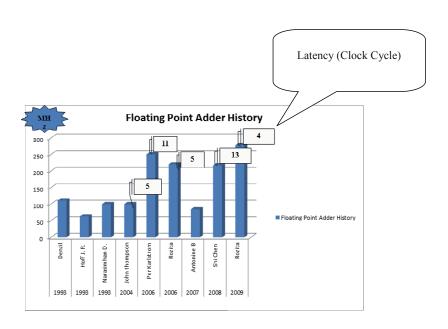

| 6.24 | Floating-point adder speed comparison                      | 145 |

| 6.25 | Floating- point adder latency comparison                   | 146 |

| 6.26 | Floating-point adder/subtractor output signal              | 147 |

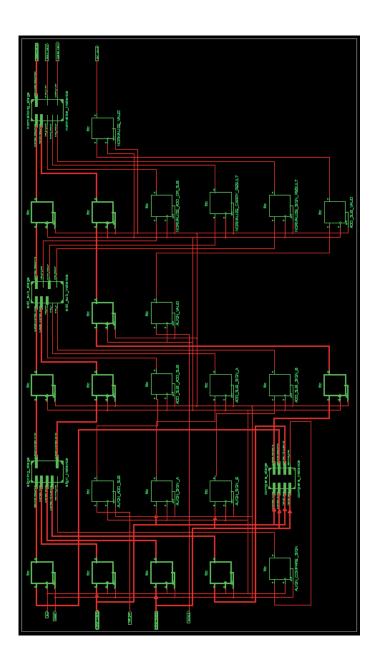

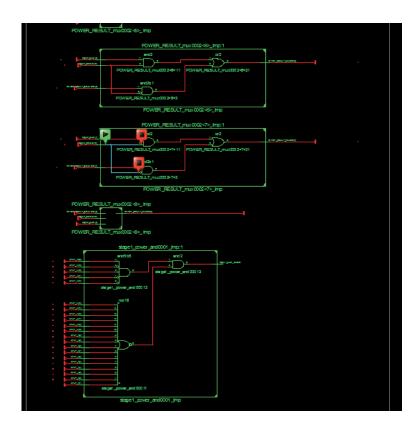

| 6.27 | Multiplier internal architecture                           | 148 |

| 6.28 | Multiplier internal architecture layout                    | 149 |

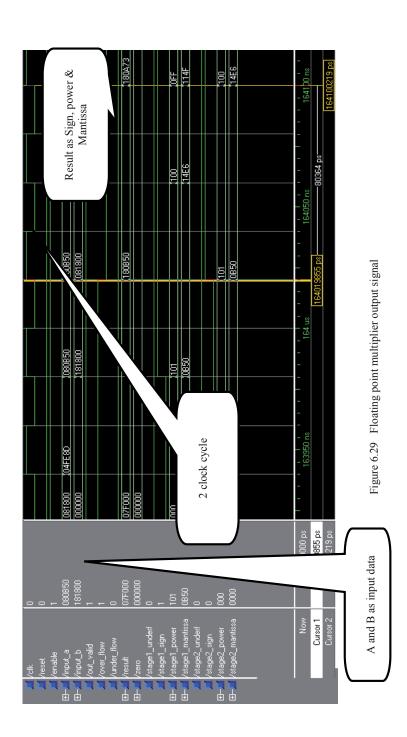

| 6.29 | Floating-point multiplier output signal                    | 151 |

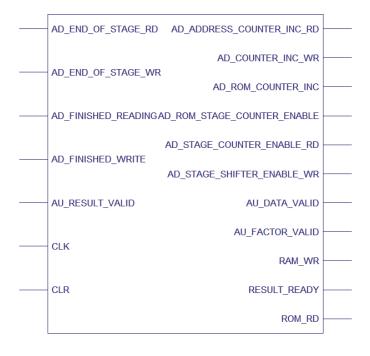

| 6.30 | Top- module of controller unit                             | 152 |

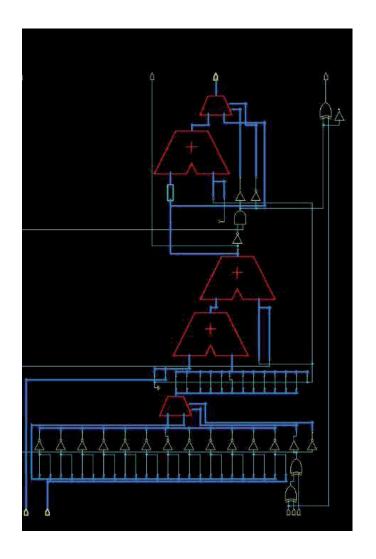

| 6.31 | Controller internal architecture                           | 153 |

| 6.32 | Controller architecture layout                             | 154 |

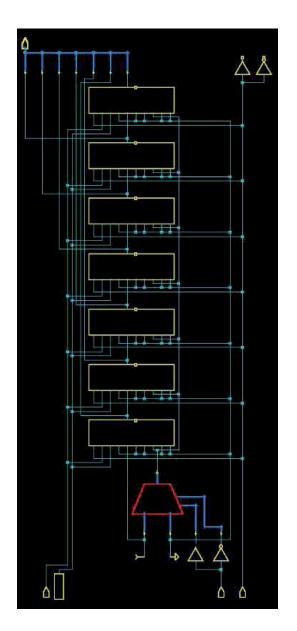

| 6.33 | ROM internal architecture                                  | 156 |

| 6.34 | RAM internal architecture                                                    | 156 |

|------|------------------------------------------------------------------------------|-----|

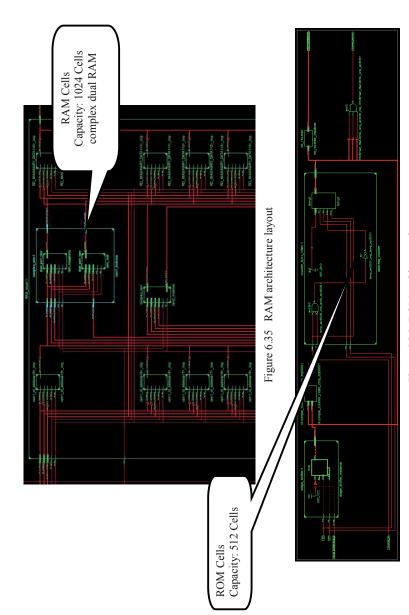

| 6.35 | RAM architecture layout                                                      | 158 |

| 6.36 | ROM architecture layout                                                      | 158 |

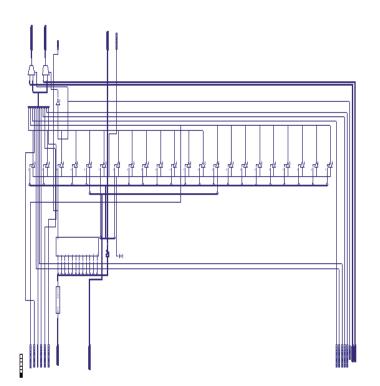

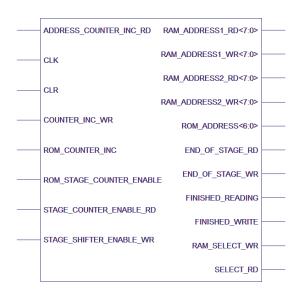

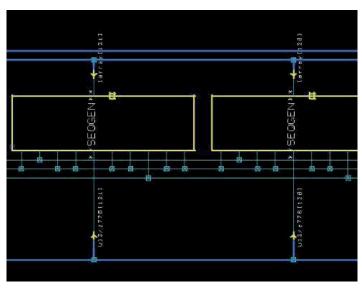

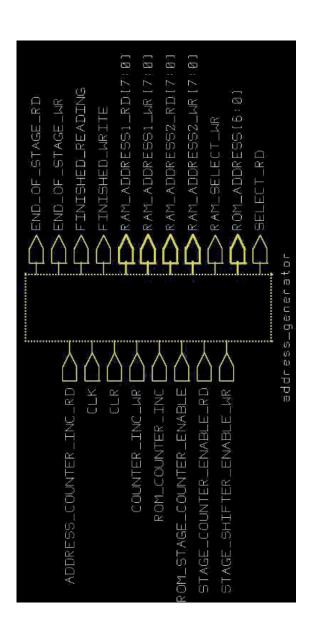

| 6.37 | Top- module of address generator unit                                        | 160 |

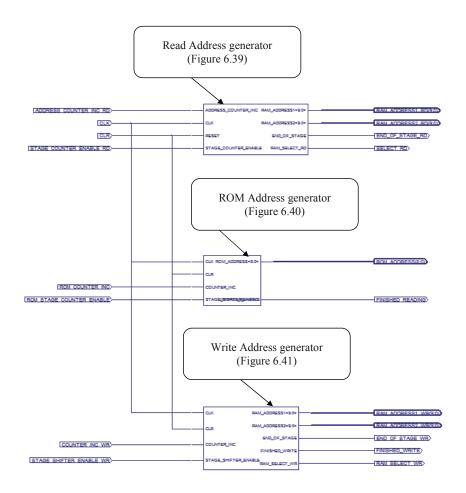

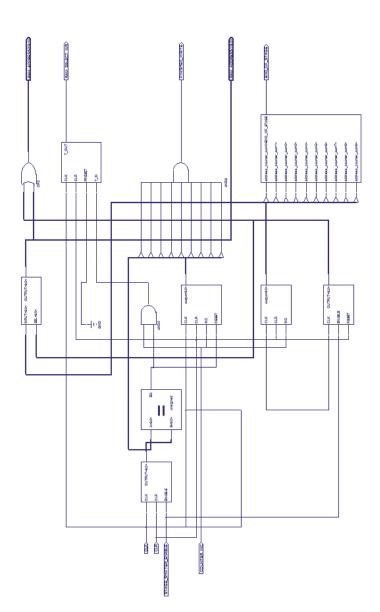

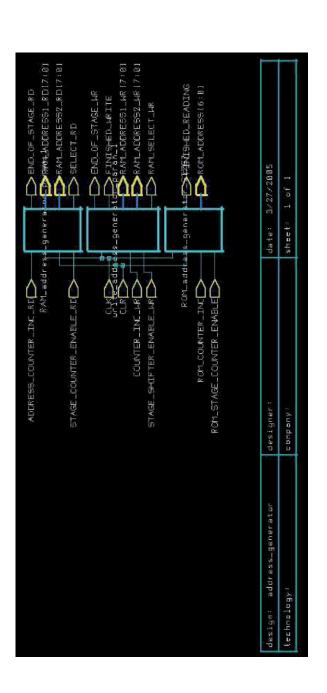

| 6.38 | Address generator internal architecture                                      | 161 |

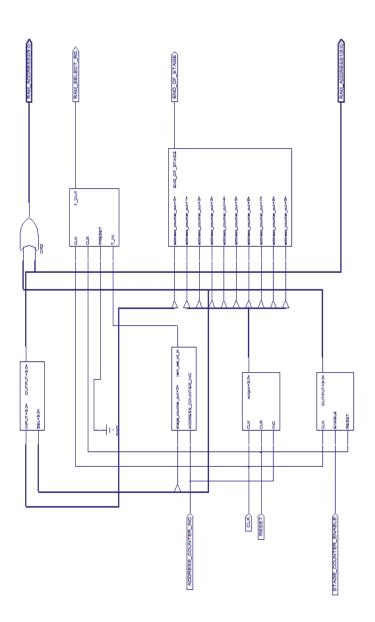

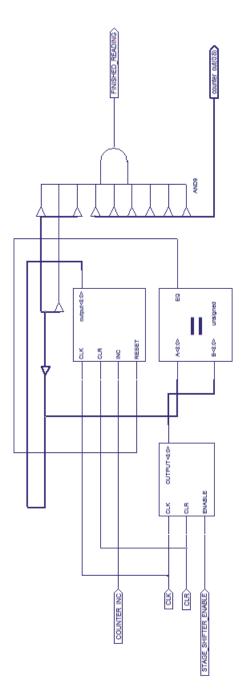

| 6.39 | Read address generator internal architecture (schematic)                     | 162 |

| 6.40 | ROM address generator internal architecture (Schematic)                      | 163 |

| 6.41 | Write address generator internal architecture (Schematic)                    | 164 |

| 6.42 | Address generator internal layout                                            | 165 |

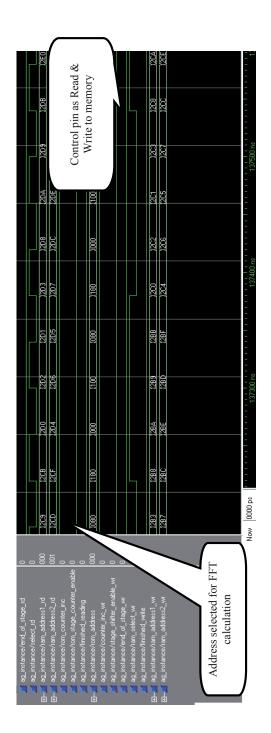

| 6.43 | Address generator output signal                                              | 166 |

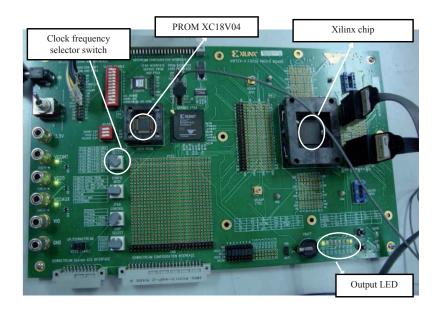

| 6.44 | Implementation of the FPP-FFT processor on the FPGA board                    | 169 |

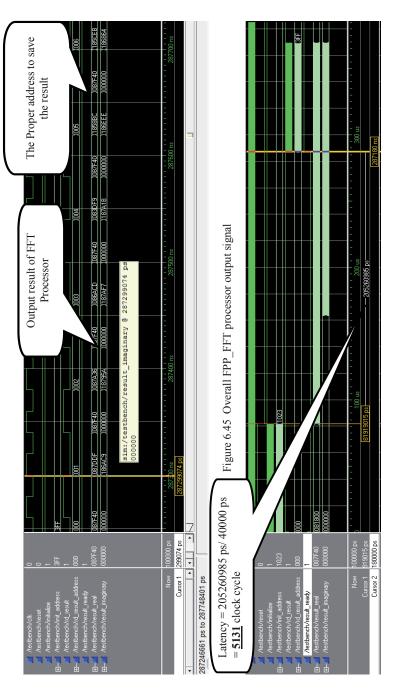

| 6.45 | Overall FPP_FFT processor output signal                                      | 170 |

| 6.46 | Overall FPP_FFT processor latency                                            | 170 |

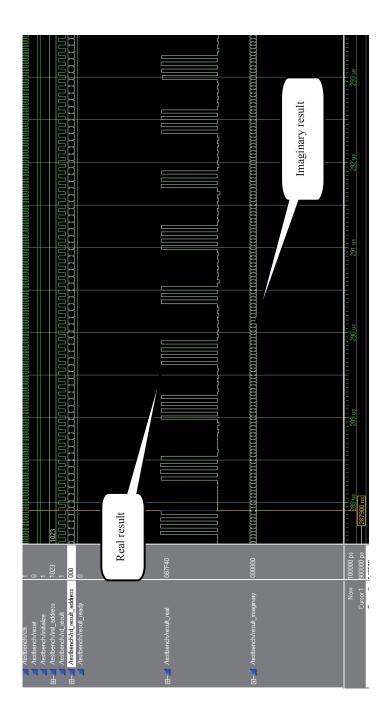

| 6.47 | 1024-point FPP-FFT processor output signal as floating-point coding          | 171 |

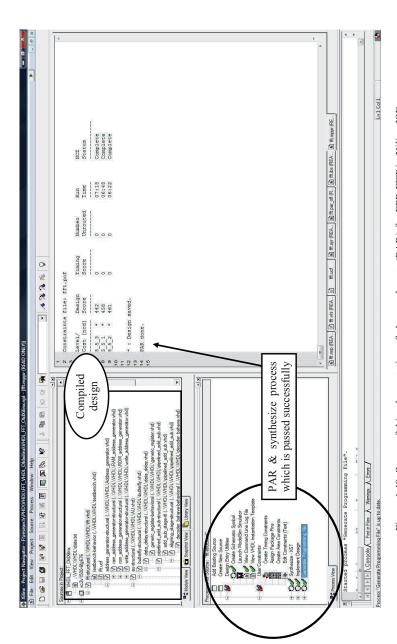

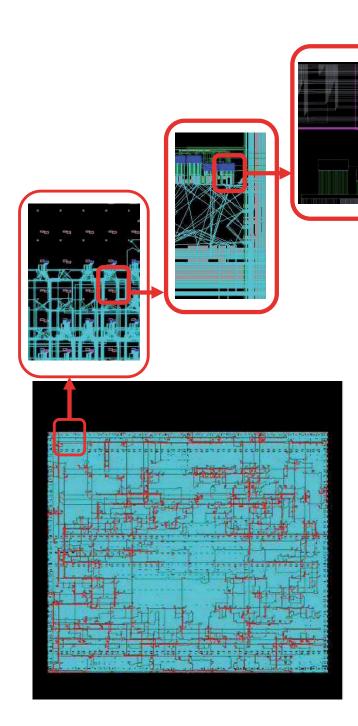

| 6.48 | Successful implementation of place and route (PAR) for FPP-FFT in Xilinx ISE | 172 |

| 6.49 | Successful synthesis process of FPP-FFT in Xilinx                            | 173 |

| 6.50 | Xilinx chip routing of the proposed FFT processor                            | 174 |

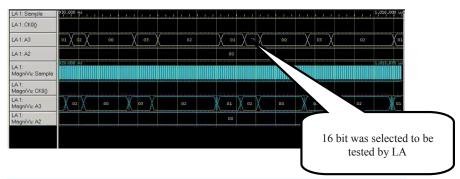

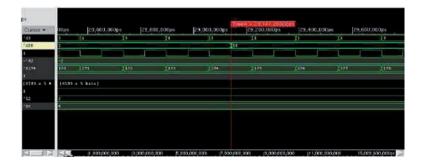

| 6.51 | FFT processor test circuit using Logic Analyzer                              | 175 |

| 6.52 | FFT processor output result displayed on Logic Analyzer                      | 175 |

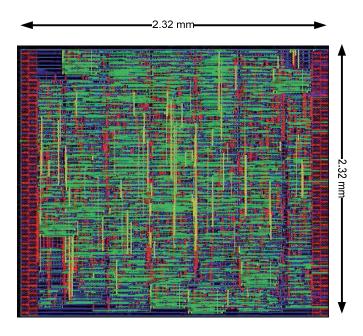

| 6.53 | Active core die of the proposed FFT processor in SILTERRA technology         | 177 |

| 6.54 | NCLaunch result of the FPP_FTT processor in the gate level                   | 178 |

| 6.55 | The output plot of gate level processor (Silicon)                            | 178 |

| 6.56 | Symbol view of the FFT processor                                             | 180 |

| 6.57 | Schematic view of the FFT processor                                          | 180 |

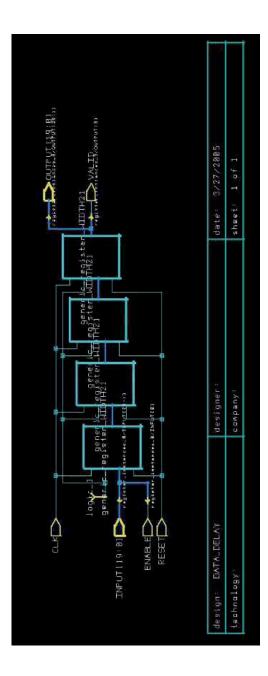

| 6.58 | Internal implementation of the data delay                                    | 182 |

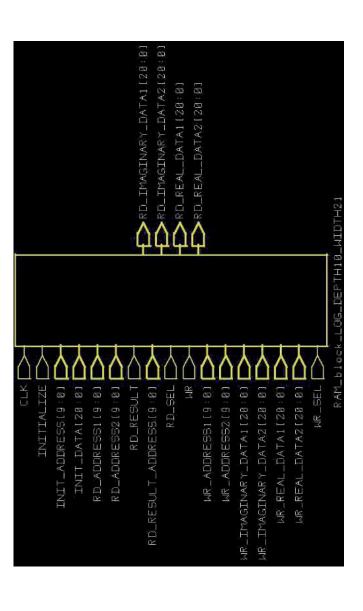

| 6.59 | Top level implementation of the RAM modules                                  | 183 |

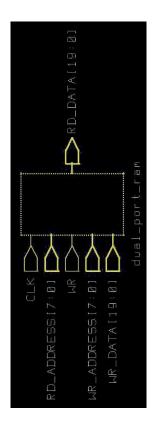

| 6.60 | Top level implementation of the dual port RAM modules                        | 184 |

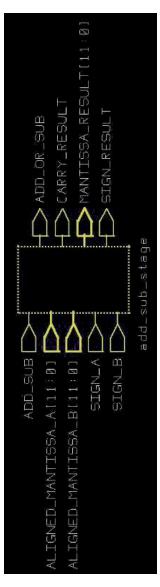

| 6.61 | Top level implementation of the floating point adder/subtractor stage        | 184 |

| 6.62 | Internal implementation of the dual port RAM modules              | 185 |

|------|-------------------------------------------------------------------|-----|

| 6.63 | Internal implementation of the add_sub_stage                      | 186 |

| 6.64 | Internal implementation of the controller                         | 187 |

| 6.65 | Top level implementation of the address generator                 | 188 |

| 6.66 | Internal implementation of the address generator                  | 189 |

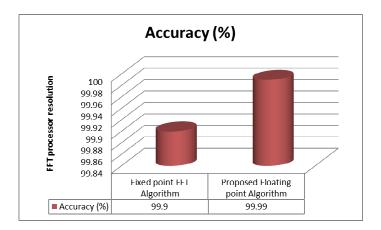

| 6.67 | Fixed-point and proposed floating-point FFT resolution comparison | 192 |

# LIST OF TABLES

| Table No. |                                                                         | Page |

|-----------|-------------------------------------------------------------------------|------|

| 2.1       | Fixed-point and floating point FFT processor efficiency                 | 14   |

| 2.2       | Fixed-point and floating-point FFT processor applications               | 16   |

| 3.1       | Comparison of calculation in DFT and FFT algorithm                      | 35   |

| 3.2       | Bit-reversal process for <i>N</i> =8                                    | 41   |

| 5.1       | Expected MATLAB simulation results for radix-2 FFT processor            | 109  |

| 6.1       | Proposed FPP-FFT Processor specifications                               | 125  |

| 6.2       | Bit-reverse for specification                                           | 126  |

| 6.3       | Proposed butterfly specification                                        | 128  |

| 6.4       | Comparison stage specifications                                         | 141  |

| 6.5       | Alignment stage specifications                                          | 142  |

| 6.6       | Add/subtractor stage specifications                                     | 142  |

| 6.7       | Normalized stage specifications                                         | 143  |

| 6.8       | Overall floating-point adder/subtractor specifications                  | 143  |

| 6.9       | Proposed floating-point multiplier specifications                       | 150  |

| 6.10      | Proposed controller specifications                                      | 155  |

| 6.11      | Proposed RAM specifications                                             | 157  |

| 6.12      | Proposed ROM specifications                                             | 157  |

| 6.13      | Proposed Address generator specification                                | 159  |

| 6.14      | Comparison of simulation and implementation result in FFT processor     | 168  |

| 6.15      | Estimated power/ area of proposed FFT in different technology libraries | 179  |

| 6.16      | Estimated power/area of conventional FFT in different technology        | 179  |

| 6.17      | Summary performance of the FPP-FFT processor                            | 190  |

| 6.18      | System improvement persentages                                          | 192  |

# LIST OF SYMBOLS

Number of exponent bit е Maximum clock frequency  $f_{s.\,\mathrm{max}}$ Micro second  $\mu s$ Ms/sec Mega sample per second Number of input samples N  $W_N^{ku}$ Twiddle factor x(n)Even input data in discrete-time  $x_e(n)$ Odd input data in discrete-time  $x_o(n)$ Input data in discrete-time  $X(\omega)$ Input data in frequency domain

$\delta(t-t_n)$  Shifted impulse signal

τ Signal domain

#### LIST OF ABBREVIATIONS

ADC Analog to Digital Converter

ASIC Application Specific Integrated Circuit

ATV Advanced Televisions

CDMA Code Division Multiple Access

CFMR Continuous Flow Mixed-Radix

CMOS Complementary Metal Oxide Semiconductor

CORDIC Coordinate Rotational Design Computer

DA Design Analyzer

DAB Digital Audio Broadcasting

DAC Digital to Analog Converter

DFT Discrete Fourier Transform

DIF Decimation In Frequency

DIT Decimation In Time

DVB Digital Video Broadcasting

DS Direct Sequence

DSL Digital Subscriber Loop

DSP Digital Signal Processing

DTFT Discrete-Time Fourier Transform

FDMA Frequency Division Multiple Access

FIR Finite Impulse Response

FFT Fast Fourier Transform

FM Frequency Modulation

FPGA Field Programmable Gate Array

FPP Floating-point Parallel Pipeline

HDTV High-Definition Television

HSPA High-Speed Packet Access

HVAC Heating Ventilation and Air-Conditioning

IC Integrated Circuit

IFFT Inverse Fast Fourier Transform

I/O Input/Output

ISE Integrated Synthesis Environment

LSB Least Significant Bit MC Multi Carrier

MCM Multi Carrier Modulation

MDC Multi-path Delay Commentator

MOS Metal-Oxide Silicon

MR Mix Radix

MSA Multiply-Sub-tract-Add

MSB Most Significant Bit

MSE Mean Squared Error

NSR Noise to Signal Ratio

OFCDM Orthogonal Frequency and Code Division Multiplexing

OFDM Orthogonal Frequency-Division Multiplexing

PAR Place And Route

PAVR Peak-to-Average Ratio PE Processing Element

RAM Random Access Memory RNS Residue Number System ROM Read Only Memory

SDF Single-path Delay Feedback SNR Signal to Noise Ratio

SQNR Signal Quantization Noise Ratio

SOC System On Chip

TCP Transmission Control Protocol

THD Total Harmonic Distortion

VHDL VHSIC hardware description language VHSIC Very High Speed Integrated Circuit

VLSI Very Large Scale Integration

WLAN Wireless Local Area Network

2D Two Dimensional 4G Fourth Generation

#### CHAPTER I

#### INTRODUCTION

#### 1.1 BACKGROUND

The need for new generation of digital processor identified as floating point fast Fourier transform (FFT) that is capable of handling new requirement in signal processing has mobilised the world of high performance digital signal processing (DSP). The FFT processor (Cooley & Tukey 1965) is the heart of signal processing which is widely used in multi-media applications (Bever et al. 1990, Jeong & Choon 1995), telecommunication systems (Le et al. 1995, Nee & Prasad 2000, Zhiqiang & Nassar 2005) and DSP processor. In the field of DSP processor, there are specific applications such as fast finite impulse response (FIR) filtering (Eniscetin et al. 1997), spectral analysis, synthesis and correlation (Jont et al. 1977). Among DSP processors, FFT algorithm is most practical processor. High performance FFT is required in this particular study due its efficient algorithm.

The current prevalent practice, there is the digital hardware with finite word-length to present and analyze DSP system. Realistic FFT implementation requires special attention due to potential quantization and arithmetic errors as well as the possibility of overflow and round off. These effects must constantly be taken into consideration in DSP system design and the implementation for sensible applications. A FFT Processor's data format determines its ability to handle signals of different precisions, dynamic ranges and signal-to-quantization-noise ratio (SQNR).

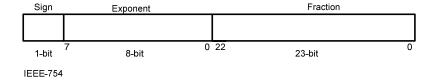

The data is represented in digital systems with different formats known as fixed point and floating-point arithmetic. In fixed-point FFT processors, a number is represented with a series of binary which the left most bit is named the most significant bit (MSB). This MSB represents sign of the number. In addition fixed point arithmetic, IEEE 754 (IEEE 1985) standard introduced a new format identified as floating-point arithmetic.

The floating-point arithmetic automatically scales the number to obtain the full range representation of the mantissa, which is done by increasing or decreasing the exponent value for small or large numbers respectively. In other words, the floating-point algorithm tracks the number and adjusts the value of the exponent. Due to the FFT processor being involved with huge calculations, its fixed-point implementation limits the dynamic range, which jeopardizes the precision. Hence, this book describes the designing of high-speed floating point FFT processor for very high-resolution applications.

#### 1.2 PROBLEM STATEMENT

It is common knowledge in the research community that the implementation of a fixed point is preferred due to its efficiency: it requires less computational complexity and less silicon area when the hardware is implemented. However, a problem arises on most current work on fixed point as it has limited accuracy, which is inherent in many FFT calculations

In order to execute fixed-point calculation in DSP processors, normalization, round off and quantization are required, which results in low precision and low dynamic range. Using fixed-point processors would cause overflow if the incoming numbers are in full scale. In addition, quantization effects also decreases SNR of the signal. Therefore, floating-point structure is rise up to function.

Floating-point arithmetic such as IEEE 754 standard promises more numerical accuracy than fixed point. Due to the fact that floating point offers high resolution it is thus adopted more as DSP applications which require high performance for signal processing.

The trade-off between fixed and floating points is the achieved resolution, speed, power consumption and core size. In order to implement in floating point architecture, there are the undesirable issues as follow:

- Although many different fixed point FFT algorithms have been developed, there are still not enough floating-point literatures as a resource for this research work

- It is a norm that the floating-point arithmetic is customarily ignored due to its complex in nature.

- iii) In the past in order to obtain high resolution, the throughput has to be sacrificed due to complex architecture.

- iv) The system latency will be raised due to the application of more components to benefit high resolution.

- Its implementation is not acceptable because of the high cost of implementation and its instability.

- vi) Most of the chip implementations reported for the implementation of fixed point and floating point FFT processors (Fox & Surace 1987, Long et. al. 2007, Morton et al. 1994, Plessey 1990) have been involved with multiple chips, which are to perform FFT calculations that resulted in high cost and low efficiency.

Hence based on the issues above, the design was proposed with the use of a novel floating point FFT architecture to achieve high resolution ( $\leq 0.01\%$  accuracy) and high speed ( $\geq 200$  MHz), low area (single chip) and low power consumption ( $\leq 1$  *W*) with reduction of latency.

## 1.3 MOTIVATION

The idea of this book is a floating point FFT processor with high speed and high resolution. The advancement of VLSI processing (60 nm) enables implementation of capable DSP architecture. Hence based on the explanations given prior to this and the

problems faced in terms of low resolution and overflow in fixed point FFT structure, it motivates us to design and investigate the floating-point FFT processor and implement it in order to provide higher precision and larger dynamic range. The designed floating-point FFT architecture claims closed parameter characteristics as well as fixed-point architecture in terms of speed and latency and single-chip implementation.

Therefore, the floating-point operation supports more accurate FFT calculations at the speed of processing integers while preventing difficult problems such as overflow, operand alignments, and signal scaling that commonly occur in fixed-point operations. Furthermore, floating point FFT processors support addressing modes and a higher degree of parallel execution. A high level hardware language is more efficient on a floating point processor with register based architectures, floating point instruction, a large address space, powerful addressing mode and a faster floating-point computing engine. These methods were utilized to achieve an intelligent controller for proposed floating-point FFT.

Additionally, with the upcoming requirement of signal processing systems and convergence of high performance DSP applications, DSP processors are needed to configure for the computation of various algorithms used in high-resolution applications. Based on the previous section, the significant incentive in this project is the design of high performance floating-point single chip FFT algorithm for signal processing. This motivation leads to design on-chip implementation of floating-point components to bring down the cost and optimize the system for the smallest size possible area to fit in the field-programmable gate array (FPGA) board and application specific integrated circuit (ASIC) implementation. Furthermore, FPGA implementation of the floating-point FFT is well suited in requirement for portable applications and low power consumption has long been the main constraint.

Several other factors were taken into consideration such as more functionality, higher workload, and longer operation time that contribute towards making the power consumption and energy efficiency even more critical and desirable for DSP application. However, in order to have low power, the implementation of FFT

algorithm is still a challenging task. (Cummings & Haruyama 1999, Dick & Harris 1999).

#### 1.4 OBJECTIVES

The overall objective of this book is to propose the high performance floating point-based FFT that are suitable for harmonic analysis applications. Specifically the proposed FFT processor must have a 32-bit resolution, a SNR of more than 100dB and a maximum clock frequency of more than 100 MHz in order to meet harmonic monitoring applications. In achieving the above objectives, it is accomplished:

- To develop a novel 1024-point radix-2 FFT algorithm DSP processor suitable for high resolution motor monitoring application.

- To optimize the architecture of a novel algorithm for high-speed and high resolution, low power consumption as well as small silicon area for VLSI implementation.

- iii) To design and test the proposed novel architecture 1024-point radix-2 FFT processor implemented on the FPGA board.

- iv) ASIC implementation of active core area for novel FFT algorithm based on 0.18  $\mu m$  SILTERRA and 0.35  $\mu m$  MIMOS technology libraries.

- v) To conduct the performance analysis of the FPGA 1024-point FFT chip.

### 1.5 SCOPE OF WORK

Our research and development scope is the designing, implementation and testing of the high-resolution novel 1024-point radix-2 floating-point parallel pipeline FFT processor in signal processing system. The proposed FFT processor must meet highresolution requirement for accurate DSP applications. The system had to be implemented on FPGA board and optimised on ASIC. The research and development will not focus on the designing of other corporation in the complete equipment and devices

## 1.6 PROJECT WORKFLOW

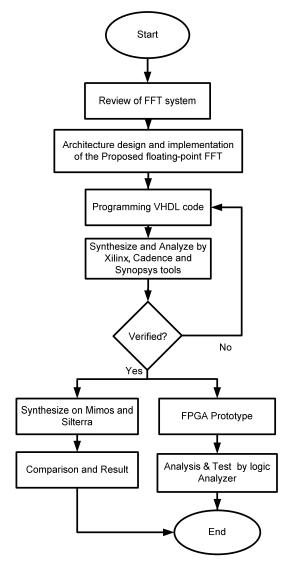

The workflow of this project is based on research, simulation, implementation and optimization. First, the problem statement and objectives of the research are formulated. Then the scope of work is determined. Once the algorithm for the proposed and conventional FFT is identified, a comprehensive MATLAB simulation was carried out to determine the functionality of the algorithm. Later, the hardware coding (using VHDL) will be derived then followed by implementation using ASIC or FPGA board to fulfill system requirement.

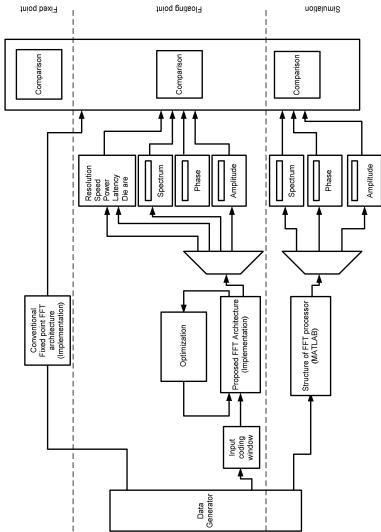

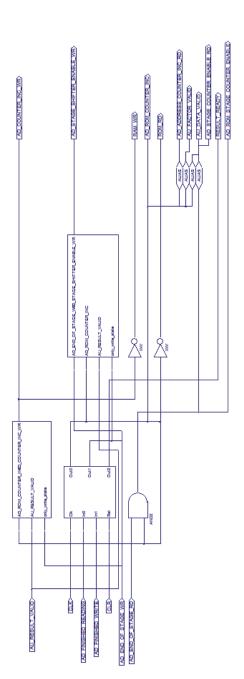

Figure 1.1 detailed the overall workflow carried out in this project. It shows the structure used to validate the simulation of the conventional 1024-point radix 2 FFT then followed by the implementation of the proposed 1024-point radix-2 floating-point parallel pipeline (FPP) FFT processor. The proposed FPP-FFT is also optimized using Xilinx, Synopsys and CAD tools. With the scope of work successfully narrowed down to realistic goals, the design and implementation of the novel floating point FFT architecture has been identified. This overall research work involves the effort of simulation and VLSI implementation of high-speed high-resolution floating point FFT structure to meet the required system functionalities.

The output result in terms of amplitude, phase, spectrum and specifications will be evaluated and the comparison will be performed using MATLAB and fixed point radix-2 FFT processor hardware implementation.

Figure 1.1 Overall comparison framework between fixed and proposed floating point radix-2 FFT processor

#### 1.7 METHODOLOGY

Based on the discussion in the previous sections, the methodology presented in this book is as follow:

- To present the novel architecture of the high-speed FFT processor.

The research also continues to achieve high efficiency in proposed algorithm.

- ii) To perform MATLAB simulation of the 3rd stage decimation in time (DIT) FFT structure to obtain the needed frequency response.

- iii) To conduct VHDL implementation of proposed novel 1024-point radix-2 FPP-FFT algorithm by synthesising and defining constrained file for the design.

- iv) To implement the design and download the design to Xilinx Virtex II FPGA board and test the FFT with a logic analyser. The FPGA board output is compared with MATLAB simulation result.

- To ASIC optimization of proposed radix 2 FFT architecture in SILTERRA and MIMOS technology libraries.

# 1.8 CHAPTER ORGANIZATION

The work in this book organized into seven chapters. The first chapter gives a brief introduction of the FFT processor.

The second chapter provides the review of FFT and DFT processor and its application. The comparison between floating-point and fixed-point processor was made in this part. This chapter also provides brief summaries of the literature review

prior to engaging the mentioned scope of work. Several topics related to this research are reviewed to give an overall picture of the background knowledge involved. The summary of the literature review is given to clarify the research rationale.

Chapter Three presents the principle of the FFT processor in detail. The different architecture of FFT based on decimation in time (DIT) and decimation in frequency (DIF) and its comparison are discussed. In addition, different architecture of FFT processor based on radix structure is considered in detail.

Chapter Four introduces the architecture of the proposed FFT algorithm followed by the introduction of floating-point data structure in detail. The proposed floating-point parallel FFT processor architecture is designed. All components of this processor are evaluated separately. New algorithm are explained and performed to increase the resolution and throughput of the FFT architecture. The structural advantage of the proposed system is discussed in detail.

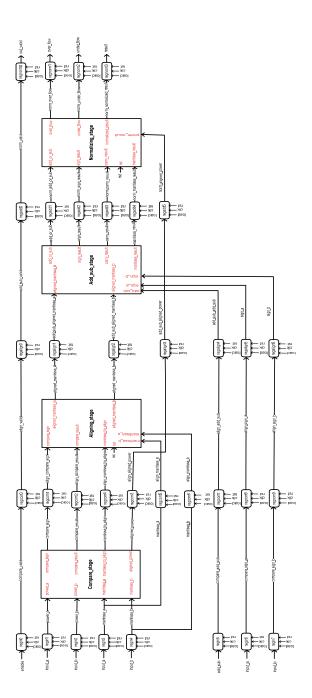

In chapter Five, simulation result of the standard radix-2 FFT processor using MATLAB tools is presented. In order to implement the FFT processor the individual block diagram is designed and simulated and a particular model was considered to perform floating-point data testing.

Chapter Six focuses on realization of the proposed FFT architecture and its implementation. The 1024-point radix-2 FPP-FFT processor are structured and implemented to increase the throughput of the processor. The implementation of advanced components such as floating-point adder/subtractor, address generator and butterfly radix-2 are investigated and performed accordingly. The system is synthesized by Xilinx ISE synthesis software then the floating point pipeline adder/subtractor and multiplier architecture are introduced to perform arithmetic calculation. Additionally, the proposed processor is also synthesized in SILTERRA 0.18 µm technology and the MIMOS 0.35 µm technology.

Chapter Seven extracts the book conclusions and proposes future work.

#### CHAPTER II

#### AN OVERVIEW OF FFT ALGORITHM

The prevalent subject of Fourier analysis encompasses a vast spectrum of mathematics with parts that may appear quite different at first glance. In Fourier analysis, the term Fourier transforms often refers to the process that decomposes a given function into the harmonics domain. This process results in another function that describes what frequencies are in the original function. However, the transformation is often given a more specific name depending upon the domain and other properties of the function being transformed. Moreover, the original concept of Fourier analysis has been extended over time to apply to general situations and the general field often known as harmonic analysis. In this project, the common approach in obtaining Fourier analysis will be discussed.

## 2.1 DISCRETE FOURIER TRANSFORM (DFT)

The main concepts of discrete Fourier transform (DFT) (Bergland 1969, Duhamel et. al. 1988) are central of most DSP processor. The DFT is a Fourier representation of a finite-length sequence which is the most important fundamental operation in digital signal processing and communication system (Gold & Radar 1969, Smith 2007). However, the computation complexity of the direct evaluation of an N-point DFT involves a long phase computational time and large power consumption. As result of these problems, it is important to develop fast algorithm. There are numerous viewpoints that can be taken toward the derivation and interpretation of the DFT representation of a finite-duration sequence. The sequence of  $\tilde{x}(n)$  that is periodic with period N so that  $\tilde{x}(n) = \tilde{x}(n+kN)$  functions for any integer value of k.

It is possible to represent  $\tilde{x}(n)$  in terms of Fourier series that is by the sum of *sine* and *cosine* values or equivalently complex exponentially sequences with frequencies that are integer multiplies of the fundamental frequencies  $2\pi/N$  associated with the periodic sequence. The same representation can be applied to finite-duration sequence.

The resulting Fourier representation for finite duration sequences will be referred to as the DFT. Sequence of length N by a periodic sequence can be represented by a periodic sequence with period N, one period of which is identical to the finite-duration sequence. The sampled sequence signal in frequency is defined as:

$$X(\omega) = \sum_{n=-\infty}^{\infty} x(n)e^{-j\omega n}$$

(2.1)

The DFT  $X(\omega)$  is a function of continuous-frequency variable  $\omega$ , and the summation in equation (2.1) extends towards positive and negative infinitively. Therefore, the DFT is a theoretical Fourier transform of a digital signal. However, it cannot be implemented for real applications. It is the sample of the signal in time domain at a particular time and can be expressed as:

$$x(n) = \int_0^\infty x(t)\delta(t - t_n)$$

(2.2)

The frequency analysis of a finite-length sequence is equal to the sample of continuous frequency variable  $\omega$  at N equally spaced frequencies  $\omega_k = 2\pi k/N$  for k = 0, 1, 2, ... N-1 on the unit circle. These frequency samples are expressed as:

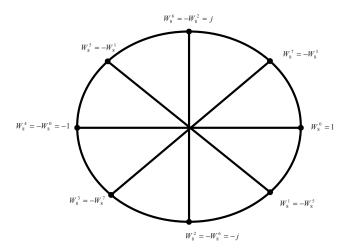

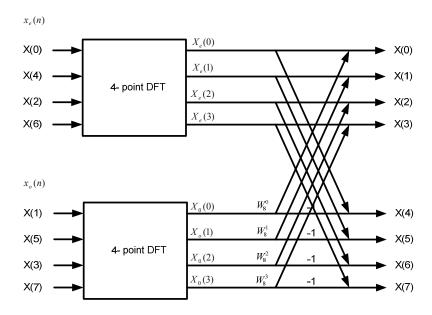

$$X(k) = \sum_{n=0}^{N-1} x(n)e^{-\frac{j2\pi kn}{N}} = \sum_{n=0}^{N-1} x(n)W_N^{kn}, k = 0,1,...,N-1$$

(2.3)

where the twiddle factors are defined as:

$$W_N^{kn} = e^{-j\left(\frac{2\pi}{N}\right)kn} = \cos\left(\frac{2\pi kn}{N}\right) - j\sin\left(\frac{2\pi kn}{N}\right)$$

(2.4)

The DFT is based on the assumption that the signal x(n) is periodic. Therefore, X(k) for k = 0, 1, ..., N-1 can uniquely represent a periodic sequence x(n) of period N. the

inverse DFT is the reversed process of the DFT. It converts the frequency spectrum X(k) back to the time domain signal x(n). (Kuo & Gan 2005).

$$x(n) = \frac{1}{N} \sum_{k=0}^{N-1} X(k) \, e^{j2\pi k n/N} = \frac{1}{N} \sum_{k=0}^{N-1} X(k) W_N^{-kn}, n = 0, 1, \dots, N-1$$

(2.5)

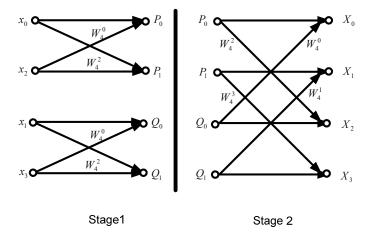

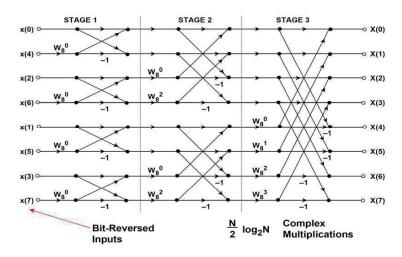

Direct computation of an *N*-point DFT according to Equation (2.3) requires N(N-1) complex additions and N(N-1) complex multiplications. The complexity for computing an *N*-point DFT is therefore  $O(N^2)$ . With the contribution from Cooley and Tukey (1965) the complexity for computation of an *N*-point DFT can be reduced to  $O(N\log_2(N))$ .

Based on the explanations given, the algorithm was developed to achieve high efficiency of DFT calculations, hence resulting in the introduction of a fast Fourier transform (FFT).

#### 2.2 FAST FOURIER TRANSFORM (FFT)

Although the DFT method is very clear and straight forward, it is quite inefficient. As the number of input data in the DFT increases, the amount of necessary mathematical calculations such as additions, multiplications or data manipulations become excessive which is undesirable in DSP processor. Hence much effort has gone into developing alternative and more efficient ways of implementing DFT.

In 1965 Cooley and Tukey developed the use of FFT in order to save time and avoid unnecessary complex calculations. Nowadays, FFT is an important tool in DSP applications. The FFT is an efficient DFT algorithm (Oppenheim & Schafer 1989). As discussed, computing a DFT of *N* points in the obvious way is reduced to *O(N log N)* operations when the *log* is to the base-2 by applying FFT technique.

If the function to be transformed is not harmonically related to the sampling frequency, the response of an FFT looks like a *sinc* function. Aliasing (leakage) also reduces the resolution and negatively affects the frequency domain. However, aliasing reduction is at the expense of broadening the spectral response. There are many distinct FFT algorithms involving a wide range of mathematics, from simple complex-number arithmetic to group theory and number theory. The next section will describe the history of FFT processor followed by expressing the other research work on different FFT structure in detail.

#### 2.3 THE FLOATING POINT FFT ALGORITHM

As discussed in Chapter I, in order to implement high performance and high efficiency DSP processor, it is imperative to increase the precision and dynamic range accordingly. Some issues make the frequency spectrum inaccurate.

The first is that the measured frequency will be subject to quantization error with respect to the real frequency. This is caused by the fact that the FFT only computes the spectrum at discrete frequencies. This error is said to affect the accuracy. The second effect is that of spectral leakage. This effect becomes very important when small amplitude harmonics are close to large amplitude ones since they become hidden by the energy distribution of the larger harmonic. Furthermore, the fixed internal arithmetic calculation of the FFT processor injects noise in the frequency spectrum. To reduce the effects, the floating-point technique was applied.

The floating-point techniques allow numbers to be represented with a large dynamic range. Therefore, floating-point arithmetic enables the reduction of overflow problems that occur in fixed-point arithmetic. Although it is at the expense of throughput and chip area size, the new architecture is designed and investigated to avoid undesired effects in floating-point FFT algorithm.

Based on IEEE 754 standards, floating-point arithmetic provides higher precision and a much larger dynamic range. Therefore, floating-point operations

support more accurate DSP operations. Table 2.1 compares the efficiency between fixed-point and the floating-point FFT processor:

Table 2.1 Fixed-point and floating point FFT processor efficiency

| Fixed-point FFT                  | Floating-point FFT     |

|----------------------------------|------------------------|

| 16-bit or 24-bit                 | 32-bit                 |

| Limited dynamic range            | Large dynamic range    |

| Overflow and quantization errors | Less error             |

| Higher frequency                 | Low frequency          |

| Less silicon area                | More silicon area      |

| Cheaper                          | More expensive         |

| Low power consumption            | High power consumption |

As illustrated in Table 2.1, implementing floating point FFT architecture scarifies the high frequency and the chip core size, which resulted in high power consumption.

## 2.4 THE FLOATING POINT FFT APPLICATION

In particular, the FFT processor is widely employed in harmonic measurement (Biswas et al. 2009, Farhang-Broujerdy & Gazor 1994), signal processing (Jain 1989, Schafer & Rabiner 1973, Jain et. al. 1979) communication system (Adams 1987, Dovel 1989, Smith et. al. 1990, Stearn & David 1988) and many more.

Generally, there are differences in application between fixed-point and floating point FFT processors. Fixed-point processors are mostly used for large-volume products such as modems and wireless phones. It is also applied in consumer audio applications such as MP3 players, multimedia gaming, digital cameras and speech coding. Among these different applications, floating point 1024-point radix-2 FFT processor is applied in image processing radar, high resolution motor monitoring, high—end audio applications such as ambient acoustics simulators, professional audio

encoding and audio mixing. It is also appropriate to be used in sound synthesis and prototyping. In this book, the implementation of high precision FFT processor was applied in the harmonic spectrum for motor monitoring applications. However, the design can be utilized in ambient acoustics, speech and signal processing systems (Schimmel et al. 2009) as well.

In general, effective performance of harmonic analysis operating in practical environments may require suppression of noise from the wave form. The design of advanced system control monitoring involves careful considerations of the rotation of the motor, transducer locations and digital signal processing. The high dynamic range in the motor vibration signals is very helpful but hard to obtain (Rabenstein & Zayati 1999).

Furthermore, many signal processing applications require algorithms that are robust to reverberation such as noise cancellation algorithms in the system aids and must function in a wide variety of reverberant conditions.

Similarly, it is often desirable that the performance of motor movement recognition systems do not suffer in presence of reverberation. Hence, it is necessary to design high precision FFT processor to recognize the signal spectrum in the authentication systems and this processor significantly affects monitoring applications in terms of high efficiency.

To conclude, Table 2.2 shows the FFT algorithm application in different fixed-point and floating-point architectures.

Table 2.2 Fixed-point and floating-point FFT processor applications

| Fixed-point FFT            | Floating-point FFT                                               |

|----------------------------|------------------------------------------------------------------|

| Low resolution disk drive  | Radar, Image processing                                          |

| Consumer audio application | High-end audio application, ambient acoustics simulators         |

| Channel coding             | Professional audio encoding /decoding and audio mixing           |

| Communication device       | Sound synthesis in professional audio and video coding /decoding |

|                            | Prototyping                                                      |

|                            | 4G OFDM Transceiver                                              |

|                            | High resolution motor monitoring                                 |

The high performance FFT processor can find application in instrumentation and communication system, which will be discussed. However, our concentration in this research work is based on instrumentation.

## 2.4.1 Instrumentation

High resolution motor monitoring and instrumentation is the major application, which is focused. Modern monitoring techniques commonly use high performance FFT processor. Vibration or current spectra are often unique to a particular series of motors or even particular motors. When a motor is commissioned or when it is in a healthy state, a reference spectrum is monitored which can be compared later with the new status of the motor spectrum (Gieras & Wing 2002).

In addition, white goods appliance with blowers and compressors, heating ventilation and air-conditioning (HVAC) systems, industrial servo drives, automotive control systems and variable speed control of AC electrical machines make use of high-resolution FFT processor (Mathwork 2010). Each motor can be used either in generator or in motor mode. Combined with linear and nonlinear elements such as transformers, lines, loads, breakers, etc., they can be used to simulate electromechanical transients in an electrical network. They can also be combined with power electronic devices to simulate drives. However, it is significantly imperative to

design a high performance motor control system while they are running. Furthermore, the harmonic study instruments are a challenging task.

Hence based on above explanation, it is needful to apply the high resolution floating point FFT processor in performing a harmonic analysis of the motors and vibration monitoring (Biswas et al. 2009). The proposed FFT unit allows computation of the fundamental component of voltage and current while the motor is active in the network. The advantages of the proposed high performance system are to:

- Enable the use of real-time algorithms for more precise and accurate control.

- Yield better power efficiency and small die core size.

- Enable spectrum analysis to be performed by using a single chip.

- Reduce system complexity and low latency

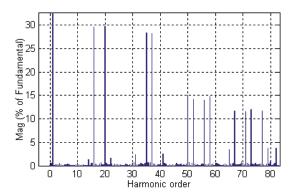

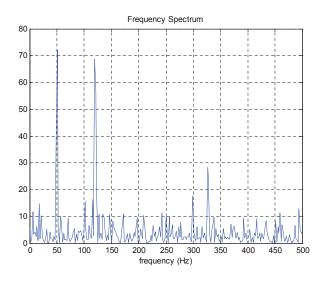

As an example, Figure 2.1 shows the fundamental component and total harmonic distortion (THD) of certain motor-based appliances on its harmonic versus the magnitude.

Figure 2.1 Harmonic analysis of the motor using FFT processor

## 2.4.2 Communication Systems

Beside the instrumentation applications, the updated version of FFT that is the floating-point FFT processor (Enis et al. 1997, Jont & Rabinner 1977) can be used in four-generation (4G) standard communication systems. The 4G refers to the cellular wireless telecommunication standard is a successor to 3Gs and 2Gs.

The 4G mobile communication systems are expected to be standardized and commercialized sometimes between 2010 and 2020. Currently 4G utilizes orthogonal frequency division multiplexing (OFDM) (Nassar 2002, Zhiqiang & Nassar 2005) as transceiver in higher data rate transmission.

In order to grasp a better understanding of the differences between 3G and 4G systems, some criteria will have to be looked at. Amongst which, speed is one that is accepted by the standards bodies with regards to the maximum data rates supported. One of the main advantages of upgrading from a 3G system to a 4G is speed. The 3G systems, which possess a high-speed packet, access (HSPA) supplies up to approximately 15-20 Mbits/s downlink and about 5-10 Mbits/s uplink. Meanwhile, the 4G systems are designed to be an improved rate that supports 5 to 10 times the existing rates of 3G, with greater than 100 Mbits/s or more in the downlink and over 50Mbits/s in the uplink (Friedmann 2007).

With the advent of fourth generation (4G) (Lefevre & Okrah 2001) communication systems, it has become increasingly important for electrical engineers to develop high standard transceiver to cover 4G requirement. Cellular phone systems have never experienced more than 30-Mbps data transmission even in the current 3G (Ojanpera and Prasad 1998) standard; therefore, as a totally new scheme, the OFDM and orthogonal frequency and code division multiplexing (OFCDM) scheme (Atarashi & Sawahashi 2001, Flock et al. C.1995) is proposed for 4G. The techniques are widely employed in data delivery systems over the phone line, digital radio and television and wireless networking systems (Wu & Zou 1995, Paiement 1994).

On the other hand, wireless LANs are already able to provide up to 54-Mbps data transmission even in the current standards, such as IEEE802.11a (IEEE 1999) and HIPERLAN/2 (ETSI TR 2000), although the service provision is still limited for stationary or low mobility users. Therefore, if a future wireless LAN standard, which might be similar to the current OFDM-based standards (Couasnon & Monnier 1994, Nee and Prasad 2000) with a bit higher transmission rate, and is able to cope with high mobility of users it can then be termed as 4G systems. The expectations from 4G are high in terms of data rates, spectral efficiency, mobility and integration. The future 4G wireless network infrastructures will consist of a set of various networks that use transmission control protocol (TCP) as a common communication protocol. Besides that, in order to satisfy the high data rate requirement efficiency in supporting multimedia services, OFDM is considered as one of the most compromising candidates for the physical layer standard of future generation mobile communications. For these reasons, a mobile system based on OFDM is being intensively considered as the next generation standard by 4G committees such as IEEE 802.16e and IEEE 802.20 (Kim & Yoon 2005), and is proving to be a possible multiple access technology to be used in 4G in terms of high performance and efficient components.

However, OFDM itself comes with its own challenges such as linearity concerns, efficient internal FFT and phase noise (Qaddour 2006). Hence, the proposed floating-point FFT is a viable choice to function in 4G OFDM transceiver due to its high efficiency. The OFDM offers several advantages over other types of modulation schemes in the improvement of transceiver reception and communication in 4G communication system as well as saving bandwidth. However, implementation of an efficient high performance IFFT/FFT is an important key issue in OFDM hardware design. In the OFDM system, the sub-carriers are created using IFFT in the transmitter, and FFT is used in the receiver to recover the data. The IFFT and the FFT complement each other in function and the most appropriate term depends on whether the signal is being received or generated. In cases where the signal is independent of this distinction then the term FFT and IFFT is used interchangeably. Hence, a high-speed high-resolution FFT/IFFT processor is required for parsing and processing the data

Furthermore, in real world applications, the resolution of ADC has continued to increase in order to obtain clear signal industry. The resolution rises from 16-bit to 32-bit to ensure signal accuracy. It is required for DSP processors such as floating-point FFT, to provide higher precision to handle signals with larger word length.

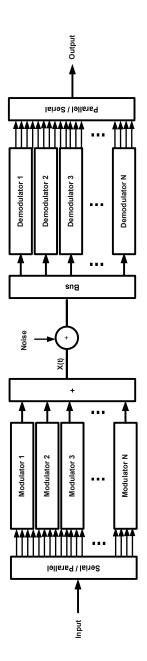

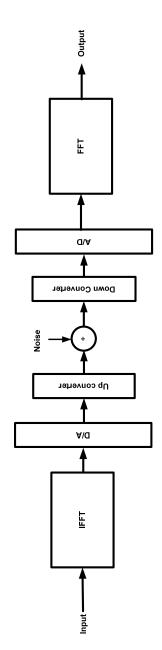

Figure 2.2 shows the conventional MCM transceiver whilst Figure 2.3 illustrates the OFDM transceiver with utilizing FFT/IFFT algorithm as modulator.

Figure 2.2 Conventional MCM transceiver

Figure 2.3 The 4G OFDM transceiver with FFT/IFFT modulator

#### 2.5 LITERATURE REVIEW

In 1965, Cooley and Tukey introduced a novel FFT algorithm. They not only reduced the computation complexity in DFT calculation, but also increased the regularity for implementation; they are very popular in modern VLSI implementation. They demonstrated the simplicity and efficiency of the 'divide-and-conquer' approach for DFT computation and made the FFT algorithms widely accepted. They applied the new technique to break down a problem into two sub-problems of the related type. The sub-problems are then independently solved and their solutions are combined to give a solution to the original problem. The conventional Cooley-Tukey radix-2 FFT algorithm requires 192 complex butterfly operations for a 64-point FFT computation. Considering that, one fixed-point FFT unit has to be computed within 4  $\mu$ s, one butterfly operation has to be completed within 20.8 ns, which leads to 96 MHz operation frequency for a single butterfly FFT unit when each butterfly operates on 2 clock cycles. The system requires a higher clock rate.

Later, in 1977, Thong and Bede investigated accumulation of round off error floating point FFT. They discussed the statistical model for round off error to predict the output noise to signal ratio (NSR) of the two common FFT algorithms, decimation in time (DIT) and decimation in frequency (DIF) algorithms. They introduced a new approach to unify error in FFT algorithm. This method was tested for radix 2 and arbitrary radix.

Tseng et al. (1979) considered the implementation of FFT structure using arrays of ROM. The arithmetic operations were based entirely on residue number system (RNS). Their research work developed optimum procedures for choosing both scaling factors and the position of scaling arrays in the structure. This design was applied for high-speed convolution filter implementation with the RNS. The filters were experimentally verified in a speech processing application.

In 1996, Hui et al. introduced a new fixed-point FFT architecture and chip design for motion compensation based on phase correlation. They designed a low

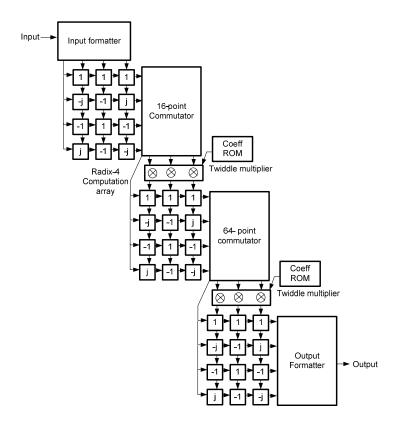

power FFT processor for use in digital television applications. The proposed 64-point FFT was fabricated using 0.6  $\mu$ m CMOS technology which comprises 0.5 million transistors in a die area  $7.8 \times 8$  mm² with 90-96 dB dynamic range at the FFT output. This processor used 24-bit internal precision at 16.1 ms/sec. The Multiplication br/sec was calculated 62.2 billion in 1 W power consumption. The maximum clock frequency at which the system operated on was 36 MHz. Figure 2.4 shows the proposed Radix-4 FFT architecture introduced by Hui (1996):

Figure 2.4 Radix-4 FFT architecture introduced Source: Hui 1996

Melander et al. (1996) presented an efficient design of 128-point radix-2 FFT processor for OFDM applications. This fixed-point algorithm implemented successfully in 0.8  $\mu m$  CMOS technology library. It was able to calculate the FFT procedure within 80  $\mu s$ . The core size was measured as 27 mm<sup>2</sup> and the total area including I/O pad 37 mm<sup>2</sup> respectively. The proposed system could operate with maximum clock frequency of 120 MHz with supply voltage of 3.0 V.

Later, the implementation of 1024 pipeline FFT processor was presented by He and Torkelson in 1998. The proposed FFT was based on Radix-2<sup>2</sup> algorithm. The chip was fabricated under 0.5 µm CMOS technology and took an area of 40 mm<sup>2</sup> with a 3.3 V power supply. The sampling frequency was 30 MHz with signal quantization noise ratio (SQNR) of 30 dB for white noise input.

Frigo and Johnson (1998) discussed adaptive software architecture for the FFT. They proposed an adaptive FFT program that tunes the computation automatically for any particular hardware. They compared their program known as FFTW, with others implementations of FFT on seven platforms. They claimed that development of an FFTW-like system requires knowledge of programming languages and compilers.

Later, Lihong et al. (1998) implemented the 8000 fixed-point 64-point FFT algorithm base on radix-2/4/8 in 0.6  $\mu m$  CMOS with power supply of 3.3 V for DVB applications. The chip was capable of computing an 8K FFT for every 200  $\mu s$ . I/O bit were 20 to 24 bits. The chip was fabricated with 1.3 M transistors with a core area of 107 mm<sup>2</sup> and chip size of 140 mm<sup>2</sup>. The power consumption was 650 mW when the input frequency is 20 MHz.

In 1999, Li and Wanhammar designed and implemented 0.35  $\mu$ m CMOS high-speed low power 1024-point pipeline FFT processor with flexible internal data length and novel processing element. The proposed FFT completed the calculation within 40  $\mu$ s.

They introduced their design for wide coverage mobile radio modem with 10 users of 2 Mb/sec each. The Radix 4 single path delay prototype commutator architecture FFT was selected to optimise the power consumption. The implemented core area was measured as 3.1mm×3.4mm and dissipates less than 200 mW at 1.5 V with throughput of 25 MHz.

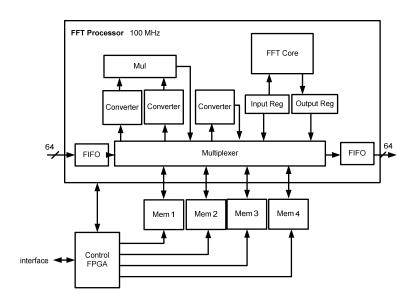

Beukelman and Bierens presented the design of the fast floating-point FFT processor in 1999. The FFT performed 1024-points floating-point complex FFT with 4 memory banks in DSP applications. The internal hybrid floating point data format (2×24 mantissa+9 bits exponents) resulted more than a single floating-point level of accuracy and dynamic range applications. The SNR for 1K complex FFT was 130 dB with the maximum clock frequency of 100 MHz. The data rate was determined as 2×50 ms/s for 2 FFT processors. The FFT processor was based on the design and there was no implementation result reported. Figure 2.5 shows the FFT processor structure introduced by Beukelman and Bierens.

Figure 2.5 Floating-point FFT processor Source: Beukelman & Bierens 1999

In 1999, Baas introduced a low power high performance 1024-point FFT processor that was fabricated by 460000 transistors under  $0.7\mu m$  CMOS standard for the DSP application. The proposed 20 to 24-bit fixed-point radix-2 FFT system operated with 3.3 V power supply in order to calculate its function within 30  $\mu s$  while consuming 845 mW. The maximum clock frequency was 173 MHz at 3.3 V power supply. The FFT processor occupied  $5.985 \times 8.204 \text{ mm}^2$  and it was fully functional on first-pass silicon.

Yeo et al. (2002) demonstrated an efficient scheme using reduced precision and word length optimization to reduce power and increase the performance of FFT in the transmitter for IEEE 802.11a WLAN applications. They claimed that with the input reduction bits during transmission, the power consumption was reduced considerably. They designed a 64-point radix-4 DIF-FFT processor. They selected the word length of input data as 10 bit. Although the power consumption measurement has not been shown in the paper, they illustrated that the number of calculation was significantly reduced.

Son et al. (2002) proposed a high-speed 256-pint FFT processor for OFDM based on Radix-4 algorithm. The 20-bit pipeline fixed-point FFT architecture was modelled by VHDL and logic synthesis and was performed using the Samsung 0.5 µm SOG cell library. The total gate count was 98326 excluding the RAM. The processor could operate with 42 MHz clock frequency. The proposed processor could calculate 256-point complex FFT in 260 clock cycles (6 µs).

Yong in 2003, proposed a method of high speed 512 complex fixed-point radix-8 FFT processor. Although there was no report of his implementation, he estimated the maximum clock frequency of 160 MHz and the latency of 4096 (12.8 µs) clock cycles in parallel FFT architecture for DSP application. The internal bit width was considered as 20 bits.

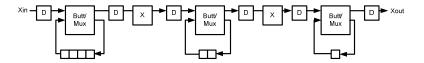

Later on, Dabbagh and Eshghi (2003) constructed the self-timed 8-point pipeline floating point FFT processor. The self-timed technique was used to overcome

a global clock overhead and distribution problem in synchronous FFT processors due to a large area size of floating-point arithmetic units. They suggested using the single shift registers instead of barrel switches in floating-point adder to reduce the required area size. Although they did not mention how much this technique could improve the area and the throughput, MATLAB simulation and VHDL implementation result comparison were given accordingly.

Figure 2.6 Pipelined FFT processor architecture Source: Dabbagh & Eshghi 2003

In recent decade Jen et al. (2003) designed and implemented a programmable 64-2048-point FFT/IFFT processor to cover the different specifications of OFDM applications. They implemented the processing element (PE) by using coordinate rotational design computer (CORDIC) algorithm to replace the multiplier based PE. Additionally, they proposed  $\pi/4$ -pre-rotation and modified EEAS-Cordic VLSI architecture to reduce the iteration number and quantization noise. Finally, the FFT processor was implemented with TSMC 0.35  $\mu$ m CMOS technology. The die area of the FFT was 12.25 mm² including 2048×32 bits memory. The chip operated under 80 MHz clock frequency and met most of the standard requirement.

In 2004, Miyamoto et al. designed and built a 36-bit FFT Processor based on the two-stage cached-memory architecture, which integrates 552000 transistors within an area of  $2.8\times2.8~\text{mm}^2$  with CMOS 0.35  $\mu\text{m}$  triple–layer-metal process. The Proposed processor could execute a 512-point fixed-point data format, one-dimensional FFT in 23.2  $\mu\text{s}$  (3063 Clock cycle). The maximum clock frequency was 133 MHz with the power consumption of 439.6 mW at 3.3 V power supply.

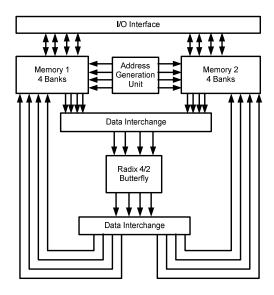

A new continuous—flow mixed-radix (CFMR) FFT processor was proposed by Byung & Myung (2005). They used the MR (radix-4/2) algorithm and a novel in-place strategy. The proposed algorithm supported fixed-point data. The pipeline CFMR FFT processor using the 0.18  $\mu$ m SEC cell library consisted of 37000 gates excluding memories, required only 640 clock cycles for 512 point FFT and run at 100 MHz. Figure 2.7 shows the proposed CFMR FFT processor.

Figure 2.7 CFMR FFT processor Source: Byung and Myung 2005

Shyue et al. (2005) designed a method for testability and fault tolerant for FFT processors based on M-testability conditions for module level systolic FFT arrays. Their M-testability conditions guaranteed one hundred percent (100%) single-module fault testability with a minimum number of test patterns, according to the proposed design fault tolerant approached at the bit level and the multiply-sub-tract-add (MSA) module level were proposed. This proved that the resulting architecture is simpler as compared with previous work and the reliability of the FFT system increases significantly.

Chin et al. (2006) constructed a low power 64-point FFT/IFFT architecture and chip adopting the retrenched 8-point FFT/IFFT (R8-FFT) and an efficient data-swapping method based output buffer unit. Their concerns were the area, power, latency and pending cycles for the application of IEEE 802.11a WLAN standard. Consequently, the design based on the new method was completed and the synthesis report illustrated the chip power consumption of 22.36 mW under 1.2 V at 20 MHz in CMOS process. The WLAN standards require the FFT calculation to be within 3.2 µs. However, the proposed design needs 72-clock cycle when the timing budget is 44.4 ns. For the post layout, the core area was 1.66 mm² and the whole chip size was 2.58 mm².

In 2006, Chin et al. proposed low multiplication complexitiy 256-point FFT architecture for WiMAX 802.16a systems. The proposed FFT architecture utilizes cascaded simplified radix-16 single-path delay feedback (SDF) structures. The proposed structure required one complex multiplier and 56 complex adders for supporting the 256-point computations. As a result of this, the output throughput rate of FFT was estimated up to 35.5 Ms/sec with 0.18  $\mu m$  standard cell technology. The system maximum clock frequency was 32 MHz in FPGA and 51.5 MHz. The total gate count and power consumption were 173875 gates and 162.7 mW respectively in 1.8 V supply voltage.

A novel 128/64 point FFT/IFFT processor for 'multiple-input multiple-output' (MIMO) OFDM based IEEE 802.11n WLAN baseband processor was constructed by Yu & Chen (2007). The unfolding mixed radix multipath delay feedback FFT architecture was applied to deal with multiple data sequences efficiency. The proposed FFT/IFFT processor was designed in a 0.13  $\mu$ m CMOS process. The core area was  $660\times2142~\mu\text{m}^2$ . At the operation clock rate of 40 MHz, the proposed processor could calculate 128-point FFT within 3.2  $\mu$ s. The maximum clock frequency was 100 MHz with the power consumption of 5.2 mW from the prime power simulator.

Ochi (2008) proposed 64-point floating-point FFT with parallel architecture for wireless application. He focused to improve the area size and dynamic range sequentially and designed a 16-bit Radix-4 FFT processor with a 64-serial data. Both

the butterfly circuit and weight multiplications were carried out in parallel in the various stages. In addition, the parallel architecture reduced the latency by 89 clock cycles whilst the conventional FFT processor has 136 clock cycles latency. In terms of speed, he implemented a 16-bit FFT with maximum clock frequency of 120 MHz and 32-bit FFT with 97.7 MHz clock rate for floating point arithmetic. Its ALUTs is 8261 and 30815 respectively. The architecture of floating-point arithmetic for his proposed design was seen in Figure 2.8:

Figure 2.8 Block floating point arithmetic Source: Ochi 2008