# Compact Modeling Solutions for Oxide-Based Resistive Switching Memories (OxRAM)

Marc Bocquet, Hassen Aziza, Weisheng Zhao, Yue Zhang, Santhosh Onkaraiah, Christophe Muller, Marina Reyboz, Damien Deleruyelle, Fabien Clermidy, Jean-Michel Portal

### ▶ To cite this version:

Marc Bocquet, Hassen Aziza, Weisheng Zhao, Yue Zhang, Santhosh Onkaraiah, et al.. Compact Modeling Solutions for Oxide-Based Resistive Switching Memories (OxRAM). Journal of Low Power Electronics and Applications, 2014, 4 (1), pp.1-14. 10.3390/jlpea4010001. hal-01737320

### HAL Id: hal-01737320 https://hal.science/hal-01737320v1

Submitted on 19 Mar 2018

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

**OPEN ACCESS**

Journal of Low Power Electronics and Applications ISSN 2079-9268 www.mdpi.com/journal/jlpea

Article

# **Compact Modeling Solutions for OxRAM memories**

M. Bocquet<sup>1,\*</sup>, H. Aziza<sup>1</sup>, W.S. Zhao<sup>2</sup> and Y. Zhang<sup>2</sup>, S. Onkaraiah<sup>3</sup>, C. Muller<sup>1</sup>, M. Reyboz<sup>3</sup>, D. Deleruyelle<sup>1</sup>, F. Clermidy<sup>3</sup> and J.-M. Portal<sup>1</sup>

<sup>1</sup> IM2NP, UMR CNRS 7334, Aix-Marseille Université, 38 rue Joliot Curie, Marseille, France

<sup>2</sup> IEF, Univ. Paris-Sud, UMR8622, CNRS, Orsay, France

<sup>3</sup> CEA-Léti, Grenoble, France

\* Author to whom correspondence should be addressed; marc.bocquet@im2np.fr

Received: xx / Accepted: xx / Published: xx

**Abstract:** Emerging non-volatile memories based on resistive switching mechanisms pull intense R&D efforts from both academia and industry. Oxide-based Resistive Random Acces Memories (namely OxRAM) gather noteworthy performances, such as fast write/read speed, low power and high endurance outperforming therefore conventional Flash memories. To fully explore new design concepts such as distributed memory in logic, OxRAM compact models have to be developed and implemented into electrical simulators to assess performances at a circuit level. In this paper, we present an compact models of the bipolar OxRAM memory based on physical phenomenons. This model was implemented in electrical simulators for single device up to circuit level.

Keywords: Compact modeling; OxRAM; design

#### 1 1. Introduction

<sup>2</sup> Memory devices based on resistive switching materials are currently pointed out as promising <sup>3</sup> candidates to replace conventional non-volatile memory devices based on charge-storage beyond <sup>4</sup> 2xnm-technological nodes [1–3]. Indeed, as compared to conventional floating gate technologies, <sup>5</sup> Resistive RAMs (so-called RRAM) gather fast write/read operations, low power consumption, CMOS <sup>6</sup> voltage compatibility and high endurance. Moreover the resistive memory element consists of a simple

7 Metal/Insulator/Metal (MIM) stack. In this way, one of the major advantages of resistive switching

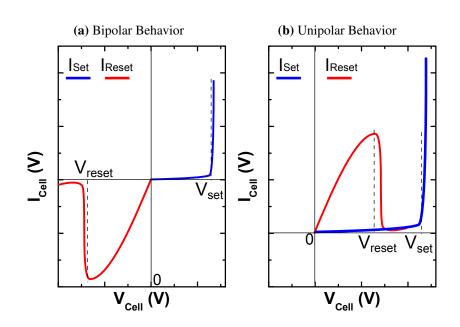

memories is their capability, whatever the underlying physics is, to be integrated in the back-end-of-line enabling NVM solutions to be distributed over CMOS logic. Relying on different based on different physical mechanisms, various RRAM technologies are now categorized in the ITRS. The Redox Memory category, covered in this study, includes Conductive Bridge RAM (CBRAM) [4] and Oxide Resistive RAM (OxRAM) [5] both of whom exhibit a bipolar behavior, (i.e. switching relying on voltage polarity) (cf Figure 1a). Conversely, RRAM technologies refered as Thermo-Chemical Memories (TCM)[6], or fuse-antifuse memories, are mostly based on nickel oxide (NiO) and exhibit a unipolar behavior (i.e.

<sup>15</sup> switching relying on voltage amplitude) as show in Figure 1b.

Figure 1. Typical I–V characteristic of Resistive memories.

For the OxRAM memory elements addressed in this paper, the MIM structure is generally composed of metallic electrodes sandwiching an active layer, usually an oxygen-deficient oxide. A large number of resistive switching oxides, like HfO<sub>2</sub>, Ta<sub>2</sub>O<sub>5</sub>, NiO, TiO<sub>2</sub> or Cu<sub>2</sub>O, are reported in the literature [7–10]. The Valency Change Mechanism (VCM) occurs in specific transition metal oxides and is triggered by a migration of anions, such as oxygen vacancies.

After an initial electroforming step, the memory element may be reversibly switched between a 21 High Resistance State (HRS) and a Low Resistance State (LRS). The electroforming stage corresponds 22 to a voltage-induced resistance switching from an initial very high resistance state (virgin state) to a 23 conductive state. In the case of bipolar switching, bipolar voltage sweeps are required to switch the 24 memory element (Figure 1a). Resistive switching in an OxRAM element corresponds to an abrupt 25 change between a HRS ( $R_{HRS}$ ) and a LRS ( $R_{LRS}$ ). This resistance change is achieved by applying 26 specific voltage to the structure (i.e.  $V_{Set}$  and  $V_{Reset}$ ). Generally, the electroforming voltage is superior 27 to these voltages. However several groups have demonstrated forming-free structures by adjusting the 28 stoichiometry of the active layer [11-13]. 29

<sup>30</sup> In this paper, an compact models of the bipolar OxRAM memory is presented. This model was <sup>31</sup> implemented in electrical simulators for single device up to circuit level.

#### 32 2. Compact model for OxRAM cells

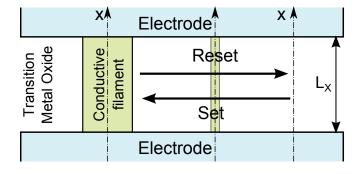

Even if OxRAM technology is still in its *infancy*, it is broadly accepted that the field-assisted motion of oxygen vacancies governs the bipolar resistance switching [14]. The proposed OxRAM modeling approach [15–17] relies on electric field-induced creation/destruction of Conductive Filament (CF) within the switching layer. The model is based on a single master equation in which both *set* and *reset* operations are accounted simultaneously and control the radius of the conduction pathway ( $r_{CF}$ ). Figure 2 depicts the proposed model for the switchable MIM structure.

**Figure 2.** Formed and dissolved conductive filament resulting from *set* and *reset* operations respectively in MIM structure.

The *set* (*resp. reset*) process can be described by an electrochemical kinetic equation relying on the Butler-Volmer equation [18]. In the LRS, where conduction is controlled by the CF, charge transport is assumed to be ohmic accordingly to previous reports in the literature [19,20]. On the contrary, HRS is dominated by leakage current within the oxide layer where. To take into account a lot of trap assisted current (Poole-Frenkel, Schottky emission, Space Charge Limited Current (SCLC)), a power low between the cell current and the applied bias has been consider. The model assumes an uniform CF radius and electric field in the cell where temperature elevation (triggered by Joule effect) may accelerate redox reaction rates. In this way the local temperature of the filament is given by [15]:

$$T = T_{amb} + \frac{V_{Cell}^2}{8 \cdot kth} \cdot \left(\frac{r_{CF}^2}{r_{CFmax}^2} \cdot (\sigma_{CF} - \sigma_{OX}) + \sigma_{OX})\right)$$

(1)

where  $T_{amb}$  is the ambient temperature, where  $V_{Cell}$  is the voltage applied between the top and the bottom electrodes,  $k_{th}$  is the thermal conductivity and  $\sigma_{CF}$  (*resp.*  $\sigma_{OX}$ ) is the electrical conductivity of the conductive filament (*resp.* oxide

The *Set* operation is modeled based on the Butler-Volmer equation through the electrochemical reduction rate ( $\tau_{Red}$ ):

$$\frac{1}{\tau_{Red}} = A_{RedOx} \cdot e^{-\frac{E_a - q \cdot \alpha_{Red} \cdot V_{Cell}}{k_b \cdot T}}$$

(2)

<sup>42</sup> where  $k_b$  is the Boltzmann constant.

Similarly, *reset* concerns the local dissolution of the CF and accounted by the oxidation rate  $(\tau_{Ox})$ :

$$\frac{1}{\tau_{Ox}} = A_{RedOx} \cdot e^{-\frac{E_a + q \cdot \alpha_{Ox} \cdot V_{Cell}}{k_b \cdot T}}$$

(3)

where  $E_a$  is the activation energy,  $\alpha_{Red}$  and  $\alpha_{Ox}$  are the transfer coefficient (ranging between 0 and 1),  $A_{RedOx}$  is the nominal redox rate. Hence, the growth/dissolution of the filament results from the inter-play between both redox reaction velocity through the following master equation:

$$\frac{dr_{CF}}{dt} = \frac{r_{CF_{max}} - r_{CF}}{\tau_{Red}} - \frac{r_{CF}}{\tau_{Ox}}$$

(4)

where the local CF radius  $(r_{CF})$  is comprised between zero and a maximal value  $(r_{CF_{max}})$ . To allow implementation into electrical simulation tools, a discrete writing is required. If the time step is sufficiently small,  $\tau_{Red}$  et  $\tau_{Ox}$  may be assumed as constant. The discrete form of Eq. 4 is then given by Eq. 5. Solving the differential equation 4 step by step allows a better convergence of simulation tools.

$$r_{CF_{i+1}} = \left(r_{CF_i} - \frac{\tau_{eq}}{\tau_{Red}}\right) \cdot e^{\frac{-\Delta t}{\tau_{eq}}} + \frac{\tau_{eq}}{\tau_{Red}}$$

(5)

43 where  $\tau_{eq} = \frac{\tau_{Red} \cdot \tau_{Ox}}{\tau_{Red} + \tau_{Ox}}$

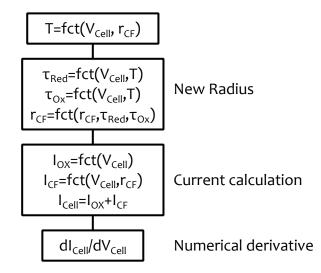

**Figure 3.** Program flowchart employed for numerical simulation of OxRAM memory devices.

Finally, the total current in the OxRAM includes two components, *i.e.* one is related to the conductive species  $(I_{CF})$  [15] the other concerns conduction through the oxide  $(I_{OX})$ :

$$I_{CF} = \frac{V_{Cell}}{L_x} \cdot \left( r_{CF}^2 \cdot \pi \cdot (\sigma_{CF} - \sigma_{OX}) + r_{CFmax}^2 \cdot \pi \cdot \sigma_{OX}) \right)$$

(6)

$$I_{OX} = A_{HRS} \cdot S_{Cell} \cdot \left(\frac{V_{Cell}}{L_x}\right)^{\alpha_{HRS}} \tag{7}$$

where  $L_x$  is the oxide thickness and  $S_{Cell}$  is the total area of the device. Finally, the total current flowing through the cell is:

$$I_{Cell} = I_{OX} + I_{CF} \tag{8}$$

These equations were then implemented within an ELDO compact model following the flowchart given in figure 3. At each call of the OxRAM instance during a transient simulation, the previous state of the filament as well as the applied voltage are provided to the model in order to take into account the

memory effect. The new filament state and the current are then computed as function of these inputs and

the time step.

#### 49 **3. Model validation**

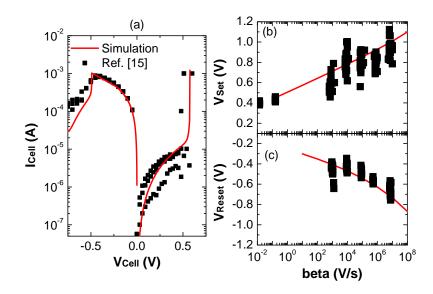

The compact model was calibrated on recent electrical data measured on HfO<sub>2</sub>-based OxRAM devices [21]. To validate the proposed theoritical approach, the model was confronted to quasi-static and dynamic experimental data extracted from the literature. Figure 4(a) shows quasi-static *set* and *reset* I(V) characteristics measured on HfO<sub>2</sub>-based memory elements. In this study, the memory elements consisted in a Ti/HfO<sub>2</sub>/TiN stack with a hafnium oxide thickness of 10 nm. The description of the cell manufacture is presented in [21]. Using the *set* parameters given in Table 1, the present model shows an excellent agreement with experimental data for both *set* and *reset* operations.

Table 1. Physical parameters used for Bipolar simulations

| $r_{CF_{max}} = 20  nm$                       | $L_x = 10  nm$                |

|-----------------------------------------------|-------------------------------|

| $Scell = 1 \mu m \times 1 \mu m$              | $T_{amb} = 300  K$            |

| $A_{RedOx} = 1 \times 10^9  s^{-1}$           | $E_a = .95  eV$               |

| $\alpha_{Red} = 0.85$                         | $\alpha_{Ox} = 0.85$          |

| $A_{HRS} = 5 \times 10^{-9}  A/(V^2)$         | $\alpha_{HRS} = 2$            |

| $\sigma_{Ox} = 0.1  m \cdot S$                | $K_{th} = 0.8  W/(K \cdot m)$ |

| $\sigma_{CF_0} = 12.5 \times 10^5  m \cdot S$ |                               |

**Figure 4.** a) Experimental I(V) ( $\blacksquare$ ) and b) *set* and *reset* voltage as a function of the programming ramp speed measured on a  $HfO_2$ -based memory structures presented in [21] and corresponding simulation results (-).

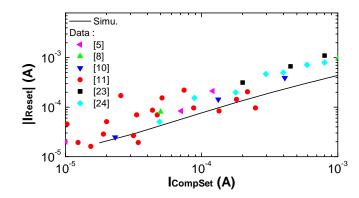

Figure 4(b) shows that the proposed model also satisfactorily catches the impact of the experimental increase of  $V_{Set}$  and  $V_{Reset}$  with the programming ramp speed. Moreover the effect of the *set* current limitation on the *reset* current is also taken into account by this compact model (Figure 5). It is interesting to note that this behavior appears for unipolar and bipolar memory [11]. But in our study, only the bipolar structures will be studied.

**Figure 5.** Maximum current during the *reset* operation ( $I_{Reset}$ ) as a function of the maximum current during the preceding *set* operation ( $I_{CompSet}$ ). Experimental data were extracted from Ref. [5,8,10,22–24].

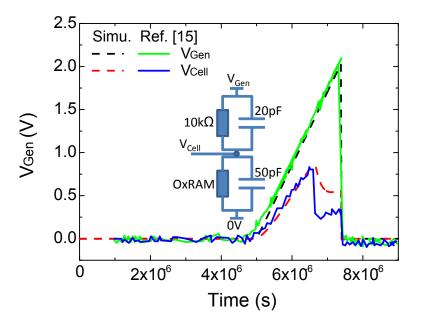

Figure 6 illustrates the transient current response of the cell when a voltage ramp is applied to the cell [Figure 4(b)]. A significant cell voltage discontinuity is observed during the *set* operation. This behavior highlights the self acceleration of *set* mechanism. Indeed, when the applied voltage is below the *set* voltage, the resistance continuously decreases. Let us mention that our model, that already includes a thermal activation of *set* operation, should be able to take into account this effect once the parasitic capacitances originating from the measurement setup are provided.

**Figure 6.** Dynamic measurement of OxRAM (HfO<sub>2</sub>-based memory) and corresponding simulation results.

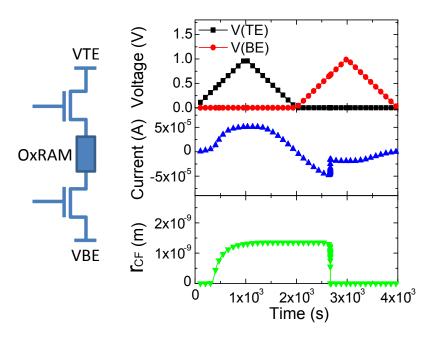

To fully validate the compact model and its integration into the electrical simulator, Figure 7 gives an example of bipolar OxRAM cells simulated at a circuit level, *i.e.* surrounded by MOS transistors.

Figure 7. electrical simulation of 2T-1R OxRAM structure

These models have been successfully used to simulate new MOS-RRAM cells like a NVM flip-flop

<sup>71</sup> [25], Non-Volatile SRAM[26] and OxRAM memory array [27].

#### 72 **4. Model application**

#### 73 4.1. OxRAM reliability evaluation versus OxRAM variability [16]

In this section, an investigation in the impact of OxRAM variability on the memory array performances is proposed [16]. Indeed, variability in advanced IC designs has emerged as a roadblock and significant efforts of process and design engineers are required to decrease its impact.

Since the cell variability is calibrated on silicon using the previous OxRAM model, only the realistically possible variations are reported in this study. A large number of Monte Carlo simulations are performed to provide the statistics needed to characterize variability. Cell variations are introduced and simulated sequentially using an electrical simulator. The goal is to track an important shift of reliability parameters.

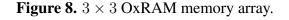

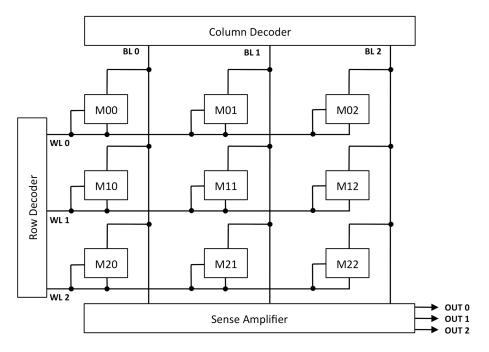

Figure 8 presents the elementary array used for simulation: it is constituted, a row decoder, a column decoder and a sense amplifier for the read operation. Memory array cells are first placed in an erase state. Then, the memory array programming is done in 2 cycles. First, all memory cells are set (logical '1'),

then the memory array is reset (logical '0'). Logical failures can be detected at the output of the sense

<sup>86</sup> amplifier during the read operation after *set/reset*.

<sup>87</sup> The best way to monitor the impact of variability on OxRAM electrical parameters is to plot the

<sup>88</sup> OxRAM hysteresis in transient mode (i.e. cell current evolution versus cell voltage difference during a

<sup>89</sup> Write/Erase cycle). Figure 9 shows the impact of the memory array cell variability (9 cells) on the circuit

90 hysteresis.

**Figure 9.** Variability impact on I - V hysteresis the memory array

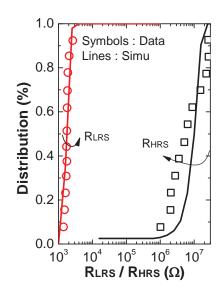

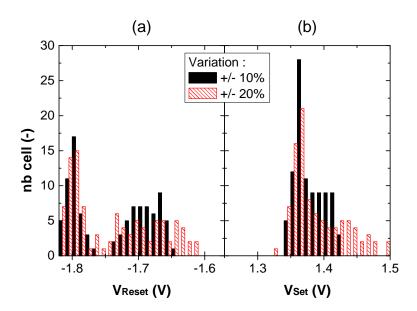

It appears clearly that  $R_{LRS}$  distribution can be severely impacted by cell variability.  $V_{Reset}$  and  $V_{Set}$ parameters can also suffer from cell variability but in a lesser extent. Notice that  $R_{LRS}$  and  $R_{HRS}$  are extracted @0.5V (read conditions). And  $V_{Set}$  and  $V_{Reset}$  are extracted @40 $\mu A$ , at a circuit level.

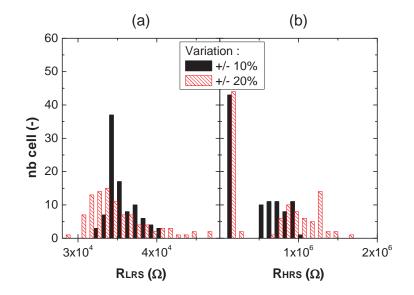

$R_{LRS}$  and  $R_{HRS}$  distributions are plotted in Figure 10. Results are presented for cell variability included in the range  $\pm 10\%$  of the median value of the considered card model parameters (solid bar). Results are also provided for cell variability included in the range  $\pm 20\%$  (dashed bar).

**Figure 10.**  $R_{LRS}$  and  $R_{HRS}$  distributions versus cell variability

At 10%, a spreading of  $R_{LRS}$  and  $R_{HRS}$  parameters is observed. The spreading increases significantly at 20%. Although these values are related to a specific OxRAM technology, a good feedback can be provided to designers to optimize the sensing circuitry according to the level of controllability of the fabrication process.

$V_{Reset}$  and  $V_{Set}$  distributions are plotted in Figure 11a-b. Here again, the initial spreading (solid bar) increases (dashed bar) according to the variability increase. These results are of the prime importance as this study predicts an increase of  $V_{Set}$  to the value of 1.5 V. Which mean that the programming signals provided to the cell needs to reach at least 1.5 V for cell to be programmed properly.

105 *4.2. SRAM Sense amplifier* [26]

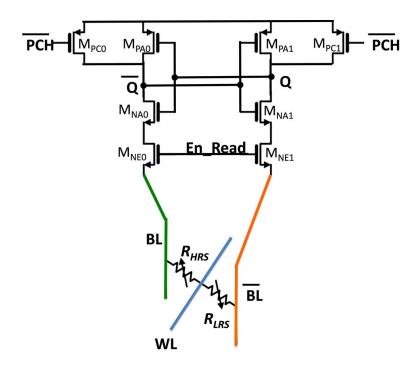

The read operation of data stored in cross-point resistive switching memory is currently one of the 106 major challenges to develop this approach. Indeed, sneak path or destructive read with complementary 107 resistive switching element are a strong limit to develop this type of architecture. Moreover, the 108 resistance ratio  $(R_{HRS}/R_{LRS})$  and the process variations have to be considered when designing a sense 109 solution. A sense amplifier performing with high reliability is then required. Figure 12 shows a 110 pre-charge based sense amplifier, which has demonstrated the best tolerance to different sources of 111 variation, while keeping high speed and low power. In this sense amplifier, the read operation is 112 performed in two phases: 113

- 1st Phase: The sense amplifier is first connected to the bit-line of the selected word with SEN set to '1' and the circuit is pre-charged with PCH equals '0'.

- 2nd Phase: The data stored in the 2R cell can be evaluated to logic level at the output Q as PCH is

changed to '1' and WL is pulled down to '0'.

**Figure 12.** Pre-Charged Sense Amplifier for data sensing. It consists of a pre-charge subcircuit (MPC0, MPC1), a pair of inverters (MNA0-1, MPA0-1), which act as an amplifier.[26, 27]

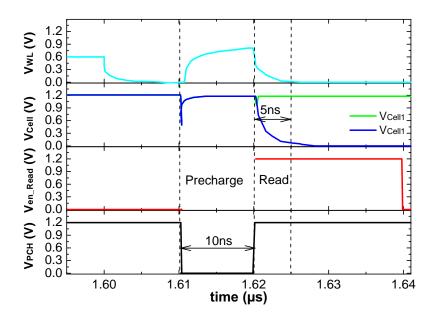

The Figure 13 validates the ability of the architecture to successfully read in parallel a full word. The model presented before has allowed us to assess the robustness of sense towards the variability of OxRAM or CMOS transistors [26]; and the validated complete crossbar architecture based on 2R

<sup>121</sup> complementary [27].

Figure 13. Simulation results with read phase of a selected cell [26,27]

#### 122 **5. Conclusion**

In conclusion, this paper deals with a compact model well suited for describing simultaneously set 123 and *reset* operations in bipolar resistive switching memories based on HfO<sub>2</sub>-based memory devise. By 124 gathering local electrochemical reactions and a thermal mechanism in a single master equation, the 125 model enables accounting for both creation and destruction of conductive filaments. The simulation 126 results satisfactorily match quasi-static and dynamic experimental data published in literature on resistive 127 switching devices. Beside, the model was implemented into circuit simulators. It has been successfully 128 used in many circuit and enabled predicting relevant trends required for designing innovative memory 129 matrix architectures or proposing distributed memories solutions. 130

#### 131 References

- Hong, S. Memory technology trend and future challenges. Proc. IEEE International Electron Devices Meeting, 2010, pp. 292–295.

- <sup>134</sup> 2. Govoreanu, B.; Kar, G.S.; Chen, Y.Y.; Paraschiv, V.; Kubicek, S.; Fantini, A.; Radu, I.P.; <sup>135</sup> Goux, L.; Clima, S.; Degraeve, R.; Jossart, N.; Richard, O.; Vandeweyer, T.; Seo, K.; <sup>136</sup> Hendrickx, P.; Pourtois, G.; Bender, H.; Altimime, L.; Wouters, D.J.; Kittl, J.A.; Jurczak, <sup>137</sup> M. 10x10nm<sup>2</sup> Hf/HfO<sub>x</sub> crossbar resistive RAM with excellent performance, reliability and <sup>138</sup> low-energy operation. Proc. IEEE International Electron Devices Meeting, 2011, pp. 729–732.

- Higuchi, K.; Iwasaki, T.O.; Takeuchi, K. Investigation of Verify-Programming Methods to

Achieve 10 Million Cycles for 50nm HfO 2 ReRAM. Proc. IEEE International Memory

Workshop, 2012, pp. 119–122.

- Kund, M.; Beitel, G.; Pinnow, C.U.; Rohr, T.; Schumann, J.; Symanczyk, R.; Ufert, K.D.; Muller,

G. Conductive bridging RAM (CBRAM): an emerging non-volatile memory technology scalable

to sub 20nm. Proc. IEEE International Electron Devices Meeting, 2005, pp. 754–757.

- Lee, H.Y.; Chen, P.S.; Wu, T.Y.; Chen, Y.S.; Wang, C.C.; Tzeng, P.J.; Lin, C.H.; Chen, F.; Lien,

C.H.; Tsai, M.J. Low power and high speed bipolar switching with a thin reactive Ti buffer layer

in robust HfO2 based RRAM. Proc. IEEE International Electron Devices Meeting, 2008, pp.

1–4.

- Baek, I.G.; Lee, M.S.J.; Seo, S.; Seo, D.H.; Suh, D.S.; Park, J.C.; Park, S.O.; Kim, H.S.; Yoo,

I.K.; Chung, U.I.; Moon, J.T. Highly scalable nonvolatile resistive memory using simple binary

oxide driven by asymmetric unipolar voltage pulses. Proc. IEEE International Electron Devices

Meeting, 2004, pp. 587–590.

- 7. Waser, R.; Aono, M. Nanoionics-based resistive switching memories. *Nature Materials* 2007, 6, 833–40.

- Seo, S.; Lee, M.J.; Seo, D.H.; Jeoung, E.J.; Suh, D.S.; Joung, Y.S.; Yoo, I.K.; Hwang, I.R.;

Kim, S.H.; Byun, I.S.; Kim, J.S.; Choi, J.S.; Park, B.H. Reproducible resistance switching in

polycrystalline NiO films. *Applied Physics Letters* 2004, *85*, 5655–5657.

- Kim, W.G.; Sung, M.G.; Kim, S.J.; Kim, J.Y.; Moon, J.W.; Yoon, S.J.; Kim, J.N.; Gyun, B.G.;

Kim, T.W.; Kim, C.H.; Byun, J.Y.; Kim, W.; Youn, T.O.; Yoo, J.H.; Oh, J.W.; Kim, H.J.; Joo,

- M.S.; Roh, J.S.; Park, S.K. Dependence of the switching characteristics of resistance random

access memory on the type of transition metal oxide. Proc. IEEE European Solid State Device

Research Conference, 2010, pp. 400–403.

- 10. Fang, T.N.; Kaza, S.; Haddad, S.; Chen, A.; Wu, Y.C.; Lan, Z.; Avanzino, S.; Liao, D.; Gopalan,

C.; Choi, S.; Mahdavi, S.; Buynoski, M.; Lin, Y.; Marrian, C.; Bill, C.; VanBuskirk, M.; Taguchi,

- <sup>165</sup> M. Erase mechanism for copper oxide resistive switching memory cells with nickel electrode. <sup>166</sup> Proc. IEEE International Electron Devices Meeting, 2006, pp. 1–4.

- 11. Nardi, F.; Larentis, S.; Balatti, S.; Gilmer, D.C.; Ielmini, D. Resistive switching by voltage-driven

ion migration in bipolar RRAM part I : experimental study. *IEEE Transactions on Electron Devices* 2012, 59, 2461–2467.

- 12. Fang, Z.; Yu, H.Y.; Singh, N.; Lo, G.Q.; Kwong, D.L. HfOx/TiOx/HfOx/TiOx Multilayer-Based

With Excellent Uniformity. *IEEE Electron Device Letters* 2011, *32*, 566–568.

- 13. Kim, W.; Park, S.I.; Zhang, Z.; Yang-liauw, Y.; Sekar, D.; Wong, H.P.; Wong, S.S. Forming-Free

Nitrogen-Doped AlO X RRAM with Sub-μA Programming Current. *VLSI* 2011, *31*, 2010–2011.

- I4. Gao, B.; Yu, S.; Xu, N.; Liu, L.F.; Sun, B.; Liu, X.Y.; Han, R.Q.; Kang, J.F.; Yu, B.; Wang, Y.Y.

Oxide-based RRAM switching mechanism: a new ion-transport-recombination model. Proc.

IEEE International Electron Devices Meeting, 2008, pp. 1–4.

- Bocquet, M.; Deleruyelle, D.; Muller, C.; Portal, J.M. Self-consistent physical modeling of

set/reset operations in unipolar resistive-switching memories. *Applied Physics Letters* 2011,

98, 263507 (1–3).

- Aziza, H.; Bocquet, M.; Portal, J.M.; Muller, C. Evaluation of OxRAM cell variability impact

on memory performances through electrical simulations. Non-Volatile Memory Technology

Symposium (NVMTS), 2011 11th Annual, 2011, pp. 1–5.

- 17. Aziza, H.; Bocquet, M.; Portal, J.M.; Muller, C. Bipolar OxRRAM memory array reliability

evaluation based on fault injection. 2011 IEEE 6th International Design and Test Workshop

(IDT). IEEE, 2011, pp. 78–81.

- 186 18. Bard, A.J.; Faulkner, L.R. *Electrochemical methods: fundamentals and applications*; 2001.

- 19. Akinaga, H.; Shima, H. Resistive Random Access Memory (ReRAM) based on metal oxides.

*Proc. IEEE* 2010, *98*, 2237–2251.

- Wong, H.S.P.; Lee, H.Y.; Yu, S.; Chen, Y.S.; Wu, Y.; Chen, P.S.; Lee, B.; Chen, F.T.; Tsai, M.J.

Metal-oxide RRAM. *Proc. IEEE* 2012, *100*, 1951–1970.

- <sup>191</sup> 21. Cagli, C.; Buckley, J.; Jousseaume, V.; Cabout, T.; Salaun, A.; Grampeix, H.; Nodin, J.F.; Feldis, <sup>192</sup> H.; Persico, A.; Cluzel, J.; Lorenzi, P.; Massari, L.; Rao, R.; Irrera, F.; Aussenac, F.; Carabasse, <sup>193</sup> C.; Coue, M.; Calka, P.; Martinez, E.; Perniola, L.; Blaise, P.; Fang, Z.; Yu, Y.H.; Ghibaudo, <sup>194</sup> G.; Deleruyelle, D.; Bocquet, M.; Muller, C.; Padovani, A.; Pirrotta, O.; Vandelli, L.; Larcher, <sup>195</sup> L.; Reimbold, G.; de Salvo, B. Experimental and theoretical study of electrode effects in  $HfO_2$ <sup>196</sup> based RRAM. 2011 International Electron Devices Meeting. IEEE, 2011, pp. 28.7.1–28.7.4.

- <sup>197</sup> 22. Nardi, F.; Ielmini, D.; Cagli, C.; Spiga, S.; Fanciulli, M.; Goux, L.; Wouters, D.J. Control of <sup>198</sup> filament size and reduction of reset current below  $10\mu$ A in NiO resistance switching memories. <sup>199</sup> *Solid-State Electronics* **2011**, *58*, 42–47.

- 23. Kinoshita, K.; Tsunoda, K.; Sato, Y.; Noshiro, H.; Yagaki, S.; Aoki, M.; Sugiyama, Y. Reduction

in the reset current in a resistive random access memory consisting of NiOx brought about by

reducing a parasitic capacitance. *Applied Physics Letters* 2008, *93*, 33506 (1–3).

- 203 24. Tsunoda, K.; Kinoshita, K.; Noshiro, H.; Yamazaki, Y.; Iizuka, T.; Ito, Y.; Takahashi, A.; Okano,

204 A.; Sato, Y.; Fukano, T.; Aoki, M.; Sugiyama, Y.; Jizuka, T. Low power and high speed

205 switching of Ti-doped NiO ReRAM under the unipolar voltage source of less than 3V. Proc.

206 IEEE International Electron Devices Meeting, 2007, pp. 767–770.

- 207 25. Portal, J.M.; Bocquet, M.; Deleruyelle, D.; Muller, C. Non-Volatile Flip-Flop Based on Unipolar

ReRAM for Power-Down Applications. *Journal of Low Power Electronics* 2012, *8*, 1–10.

- 209 26. Hraziaa.; Makosiej, A.; Palma, G.; Portal, J.M.; Bocquet, M.; Thomas, O.; Clermidy, F.;

210 Reyboz, M.; Onkaraiah, S.; Muller, C.; Deleruyelle, D.; Vladimirescu, A.; Amara, A.; Anghel,

211 C. Operation and stability analysis of bipolar OxRRAM-based Non-Volatile 8T2R SRAM as

212 solution for information back-up. *Solid-State Electronics* 2013.

- 27. Zhao, W.S.; Zhang, Y.; Klein, J.O.; Querlioz, D.; Chabi, D.; Ravelosona, D.; Chappert, C.; Portal,

J.M.; Bocquet, M.; Aziza, H.; Deleruyelle, D.; Muller, C. Crossbar Architecture Based on 2R

Complementary Resistive Switching Memory Cell. Procs. of ACM/IEEE Nanoarch, 2012.

<sup>216</sup> © 2013 by the authors; licensee MDPI, Basel, Switzerland. This article is an open access article

<sup>217</sup> distributed under the terms and conditions of the Creative Commons Attribution license

<sup>218</sup> (http://creativecommons.org/licenses/by/3.0/).