## Fully tunable UWB pulse generator with zero DC power consumption

R. Vauche, Sylvain Bourdel, N. Dehaese, O. Fourquin, Jean Gaubert

#### ▶ To cite this version:

R. Vauche, Sylvain Bourdel, N. Dehaese, O. Fourquin, Jean Gaubert. Fully tunable UWB pulse generator with zero DC power consumption. 2009 IEEE International Conference on Ultra-Wideband, Sep 2009, Vancouver, France. 10.1109/ICUWB.2009.5288788. hal-01704302

### HAL Id: hal-01704302 https://hal.science/hal-01704302v1

Submitted on 20 Dec 2021

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Fully Tunable UWB Pulse Generator with Zero DC Power Consumption

R. Vauché<sup>1</sup>, S. Bourdel<sup>1</sup>, N. Dehaese<sup>1</sup>, O. Fourquin<sup>1,2</sup>, J. Gaubert<sup>1</sup>

<sup>1</sup> Aix-Marseille University, IM2NP, and CNRS, IM2NP (UMR 6242), Campus de Saint-Jérôme, Avenue Escadrille Normandie Niemen - Case 142, F-13397 Marseille Cedex, France

<sup>2</sup> Insight SiP, Campus Agora Einstein, 905 rue Albert Einstein, BP 60247, 06905 Sophia-Antipolis Cedex, France

Abstract—The design of a fully tunable pulse generator using only logic cells is presented and simulated with 0.13 $\mu$ m standard CMOS process. The generator is based on the elementary pulse combination and can synthesize different UWB pulse shapes. The generator uses logic gates to achieve the elementary pulses and a H-bridge to make the combination which leads to a zero DC power consumption. To achieve FCC compliant pulse having  $2V_{PP}$  magnitude the generator consumes 140 pJ by pulse using 1.2V supply voltage.

UWB; Tunable Pulse Generator; H-Bridge; Pulse Shape;

#### I. Introduction

As a result of mounting need for wireless communications in North America, Federal Communication Commission (FCC) has regulated 3.1-10.6GHz band in 2002 for Ultra-WideBand (UWB) transmission [1]. Other local regulation organizations in telecommunications allocated later frequency bands, in particular 6-8.5GHz in Europe, and 3.4-4.8GHz, 7.25-10.25GHz in Japan. Width of these bands allows the use of Impulse Radio (IR-UWB) techniques which require very simple transceiver architecture [2]. Opposed to classical wireless systems, UWB systems do not involve integration of costly functions in terms of consumption and die area as frequency synthesizer and mixer.

In order to be suitable for IR-UWB low cost applications, the pulse generator must be as small as possible and consume a small amount of power while achieving high pulse magnitude in order to be used in low cost systems based on energy detection [3]. Moreover, the tuning capability of the generator is very important in addressing different applications and different frequency bands.

Several techniques are employed in order to generate UWB pulses such as filter impulse response [4] or Step-Recovery Diode (SRD) [5]. The main disadvantage of the first method is that it requires inductors which occupy a large silicon area whereas the second needs diodes not available in standard CMOS design kit. Moreover, previous methods create frozen pulse shape which can't be modified or tuned. Actually, two main techniques are used to achieve tunable pulse generator. The first one consists of using Local Oscillator (LO) to transpose different baseband pulses in different frequency bands [6]. The tuning capability of this technique is efficient

but it is limited by its starting time which impairs the maximum amplitude and bandwidth [7]. Moreover, due to the consumption of the LO and the mixer, the consumed energy by pulse regarding the pulse magnitude is high. Due to increases in technology performances, elementary pulse combination is often used to achieve fully digital pulse generator [8][9][10]. The main limitation of those generators is the limitation of the pulse magnitude in the upper bandwidth (>5GHz).

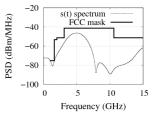

In this paper, we propose a fully integrated and tunable UWB pulse generator using H-Bridge principle. The generator structure allows a large variety of pulses to be synthesized. The main limitation is the number of elementary pulse needed which impact the size and the power consumption. Presented version of the generator can create pulse waveform composed by 6 elementary pulses which respects FCC regulation mask and drives  $50\Omega$  differential load. Simulation with a  $0.13\mu m$ CMOS technology design kit shows the generator's ability to achieve 2V<sub>pp</sub> pulse magnitude with 1.2V voltage supply in a 10dB bandwidth of 5.3 GHz centered at 7.3 GHz and to use pulse repetition frequency (PRF) of 500MHz. Furthermore, the generator contains only custom-made standard CMOS logic cells and an H-bridge driver which implies zero DC consumption and steady energy dissipation around 140pJ by pulse without turning off the generator.

This paper is organized as follows. In Section II, the pulse combination method is explained. Section III introduces the proposed tunable UWB pulse generator based on H-Bridge. Simulation results obtained with 0.13µm CMOS technology are shown in Section IV and compared to others design results.

#### II. Pulse Combination Method

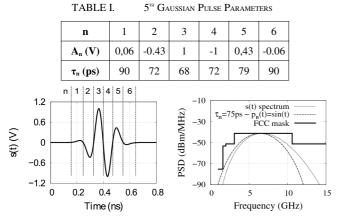

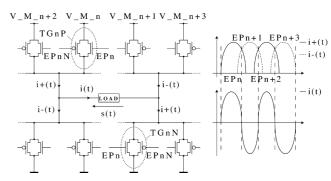

As shown in Fig. 1[11], UWB pulses can be parsed by a sequence of elementary pulse. Also, an UWB waveform s(t) can be approximated by a sum of elementary pulse where the  $n^{th}$  elementary pulse is characterized by a magnitude of  $A_n$  and a width of  $\tau_n$ . Sequentially it is possible to synthesize a pulse by combining elementary pulse shapes  $p_n(t)$  of width  $\tau_n$  multiplied by their appropriated magnitude  $(A_n)$ . Resulting UWB pulse s(t) can be written with  $\tau_0$ =0 as follows:

$$s(t) = \sum_{n=1}^{N} A_n \cdot p_n \left( t - \sum_{p=1}^{n-1} \tau_p \right). \tag{1}$$

Figure 1. 5th Gaussian pulse [11] with its approximated spectrum

Such method of generation is the more interesting since it is robust against  $\tau_n$  or  $p_n(t)$  variation. As shown in Fig. 1, a good approximation of  $5^{th}$  Gaussian pulse in TABLE I can be achieved with constant  $\tau_n$  and sinusoidal  $p_n(t).$  This allows easy generator settings and the number of necessary elementary pulse N to be easily predicted. Central frequency spectrum  $f_0$  is equal to pulse pseudo-period and can be estimated from the average  $\tau_n$  as follows :

$$f_0 \simeq \frac{N}{2 \cdot \sum_{n=1}^{N} \tau_n}$$

(2)

Moreover, 10dB pulse bandwidth (BW) can be approximated as the invert of pulse length and expressed as follows:

$$BW \simeq \frac{2}{\sum_{n=1}^{N} \tau_n} \,. \tag{3}$$

Finally, the minimum number of necessary elementary pulse  $N_{\text{min}}$  to respect a given mask can be written as follows:

$$N_{min} \simeq \frac{4 \cdot f_0}{BW} \tag{4}$$

Therefore, the more UWB spectrum to generate is narrow, the more number of elementary pulse to combine is high. For example, FCC mask requires at least 4 elementary pulses whereas the first 500MHz channel centered on 3.5GHz of 802.15.4a IEEE norm needs more than 28 pulses.

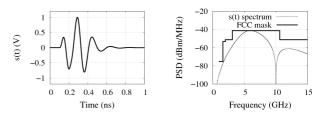

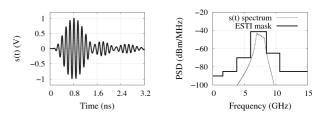

To illustrate this point, Fig. 2 and Fig. 3 show respectively a pulse shape in time and frequency domains which can be used respectively to match with FCC and ESTI mask. The first UWB pulse is obtained with an ideal 3<sup>rd</sup> order Bessel filter driven by a triangular generator. Its bandwidth (BW) is tuned to 2.5GHz with an attenuation of 1dB and its central frequency is set to 8GHz. The second pulse is the response of an ideal 3<sup>rd</sup> order Chebyshev filter centered on 7.55GHz. Its bandpass is equal to 1.2Ghz with a ripple of 1dB and its bandstop is tuned to 2.1 GHz with an attenuation of 30dB. The impulse response of Bessel filter for FCC mask need 7 elementary pulses to be synthesized and the impulse response of Chebyshev filter for ESTI mask needs more than 30 elementary pulses.

Figure 2. Response of an ideal 3rd order Bessel filter set for FCC band

Figure 3. Response of an ideal 3<sup>rd</sup> order Chebyshev filter set for ESTI band

#### III. FULLY TUNABLE PULSE GENERATOR DESIGN

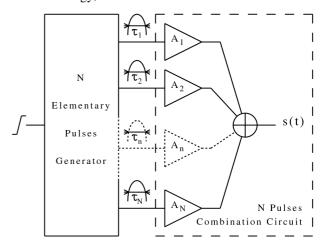

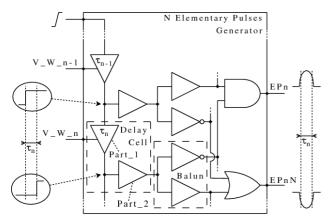

A UWB pulse generator based on the pulse combination method uses two main functions. The first is it generates all elementary pulses with their associated width and the second is it combines each pulse at the output stage with a desired magnitude. A bloc diagram schematic is shown in Fig. 4.

#### A. Gaussian-like Generator Design

As shown in Fig.5, elementary pulses are generated by digital triangular generator [4][8] which uses a digital delay line to propagate a positive edge. Two consecutive edges are then combined using logic gate (OR and AND) to generate an elementary pulse (EPn) and its opposite (EPnN) needed to command the H-Bridge. The delay between two consecutive edges sets the width of the elementary pulse  $(\tau_n)$  and must be tunable. Particular attention must be paid to the matching between an elementary pulse and its opposite because mismatch between EPn and EPnN degrades the combination in the H-Bridge. Moreover, the elementary pulse generator must achieve pulse width less than 60ps with the  $0.13\mu m$  used CMOS technology, to cover the full FCC band.

Figure 4. Bloc diagram of pulse generator using combination method

Figure 5. Simplified schematic of elementary pulses generator

Figure 6. Electrical structure of the used delay cell

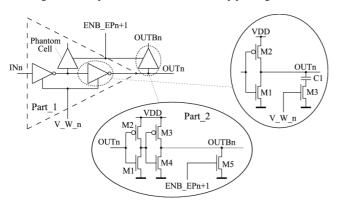

Achievement of a triangular generator is directly bound up by the design of Voltage Control Delay Line (VCDL) which consists of tunable delay buffer. As shown in Fig. 6, a delay cell is built up of two parts (Part\_1 and Part\_2). Part\_1 consists on two stages based on CMOS inverter loaded on a capacitor (C1) in series with a NMOS analog "switch" (M3) and it drives the next delay cell. Variation of voltage applied on M3 (V\_W\_n) changes the current in C1 and allows elementary pulse width (τ<sub>n</sub>) to be modified. C1 is sized to achieve delay from INn to OUTn, between 50ps and 100ps (C1=500fF). The main advantage of this delay cell structure is its low sensitivity to control voltage variation. The second part of the cell (Part\_2) is made up of two CMOS inverters and one "reset transistor" (M5), which enables the propagation through the delay line to limit the number of elementary pulses in case of short pulse generation. As shown in Fig. 6, a phantom cell is inserted to ensure a constant load between each elementary delay cell.

Final stage of elementary pulse generator is achieved by standard NAND and NOR logic gates with an inverter at their output. To achieve complementary elementary pulses these gates need to be driven by two complementary command signals issued by the delay line. To generate those signals, buffers based on CMOS inverter are used. The first and the last inverters are sized with the fan out law in order to optimize signal propagation. To obtain synchronized balanced signals, an intermediate series inverter and an intermediate parallel inverter is inserted respectively in the unbalanced and the balanced path as represented in Fig. 7.

Figure 7. Electrical structure of the designed balun

#### B. H-Bridge Design

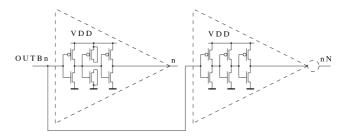

To maximize the pulse's magnitude, the presented design uses a customized H-Bridge to drive the  $50\Omega$  output antenna. As shown in Fig. 8, the driver circuit consists of CMOS transmission gate and allows the peak to peak magnitude of the UWB pulse to stretch a theoretical value of 2VDD. Each elementary pulse (EPn) and its complementary (EPnN) command two transmission gates (TGnN and TGnP). The magnitude of each elementary pulse (An) is set by the DC voltage (V\_M\_n) of each branch. Positive and negative elementary pulses are combined by current sum in the load [12]. In comparison with classical differential structure, the impact of this driver on the power consumption is minimized because it consumes zero DC power. Moreover, pulse combination method using H-Bridge enables to synthesize UWB pulse composed by a high number of elementary pulses which allows a large tuning of the pulse spectrum. If some transmission gates are not needed (to synthesize short pulse), they are on high impedance state because they are disabled.

As shown in Fig. 8, transmission gates are achieved by a NMOS in parallel with the associated balanced PMOS transistor. For sizing the NMOS transistor width, it is necessary to make a tradeoff between the maximum pulse magnitude and H-bridge power consumption. To achieve pulse magnitude of 2V (peak to peak) on  $50\Omega$  load, the width is around  $200\mu m$  for the  $0.13\mu m$  used CMOS technology. The PMOS transistor associated is a  $460\mu m$  width which can lead to a large silicon area in the case of narrow band pulse. Considering the large size of the transmission gate transistors, it is necessary to insert, between the elementary pulse generator and the H-bridge, a buffer based on four CMOS inverter designed using the fan out laws.

Figure 8. H-Bridge combination principle

Due to the shape of the elementary pulse which commands the transmission gate and due to the time response of the gate, there is an aliasing in the conduction time between TGn gates (TGnN and TGnP) and TGn+1 gates (TGn+1N and TGn+1P) which results in narrower generated elementary pulse. This phenomenon is represented in Fig. 8. It implies that delay cells which generate the first and the last effective elementary pulses have to be tuned separately, in order to apply the width reduction to these pulses.

Finally an additional transmission gate stage is added. For a pulse generation using N elementary pulses, this stage is commanded by a N+1 elementary pulse which occurs at the end of the pulse. This stage is tuned at 0V in order to short-circuit the load at the end of the UWB pulse to discharge the parasitic capacitors and avoid a time spreading of the pulse.

#### IV. SIMULATION

#### A. Simulation Results

The proposed UWB pulse generator is designed with standard  $0.13\mu m$  CMOS technology design kit and simulation results are obtained with the software ADS for a supply voltage of 1.2V.

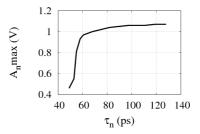

Pulse generation is based on a tunable delay line. One advantage of this architecture is the delay per stage could be tuned to set the delay in presence of Process Voltage Temperature (PVT) variation and hence the center frequency of the pulse. The elementary pulse generator simulations shows in Fig. 9 its ability to generate a minimum pulse width of 60ps (narrower pulse width leads to lower pulse magnitude and can not efficiently command the transmission gates) which is sufficient to cover the FCC band. This allows pulse to be centered on 8.33GHz.

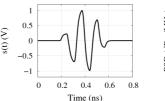

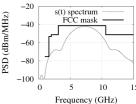

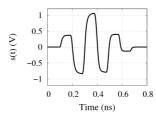

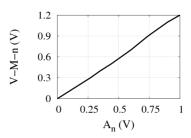

A six order pulse generator has been designed for the FCC band. A first example of pulse generation is given in Fig. 10. The generator is set to synthesize a Gaussian pulse modulated by a sinusoid. In this case all the elementary pulses have the same width which limits the amount of input of the final circuit and simplifies the circuit measurement. The setting of the different control voltages needed to generate this pulse and the different values of  $A_n$  and  $\tau_n$  are summarized in Table II. The pulse is compliant with the FCC spectral mask and it 10dB bandwidth is 5.3GHz centered on 7.3GHz. The pulse magnitude is  $2V_{pp}$  and its duration 0.42ns. The control voltage used to set the programmable generator is linearly extrapolated from the value of A<sub>n</sub> as shown in Fig. 12. This shows the very small distortion involved by the H-bridge and the ease of tune of the generator. Fig. 11 underlines the generator's ability to generate different UWB pulse shapes. In this case, a Bessel filter response is generated with the values shown in Table III resulting in narrower pulse bandwidth and a different pulse shape.

An approximation of the silicon area of this generator can be made from the size of the transmission gate and the number of elementary pulses needed to synthesize the pulse. In the technology used, a  $200\mu m$  NMOS transistor and a  $460\mu m$  PMOS transistor with  $10\mu m$  finger occupy a silicon area of

respectively  $170\mu m^2$  and  $460\mu m^2$ . The designed generator will occupy  $0.02mm^2$  and a pulse generator for ECC band having 20 elementary pulses would occupy  $0.05mm^2$ .

Figure 9. Maximum elementary pulse magnitude versus it width

Figure 10. Pulse obtained with the proposed generator on  $50\Omega$  (Table II)

Figure 11. Pulse obtained with the proposed generator on  $50\Omega$  (Table III)

Figure 12. Control voltage  $V_M_n$  versus pulse magnitude  $A_n$  on  $50\Omega$

TABLE II. Pulse Parameters of Sine Modulated by Gaussian

| n                   | 1    | 2     | 3  | 4  | 5    | 6     |

|---------------------|------|-------|----|----|------|-------|

| A <sub>n</sub> (V)  | 0.22 | -0.69 | 1  | -1 | 0.69 | -0.22 |

| τ <sub>n</sub> (ps) | 71   | 71    | 71 | 71 | 71   | 71    |

TABLE III. Pulse Parameters of Bessel Filter Response

| n                   | 1    | 2    | 3   | 4     | 5    | 6     |

|---------------------|------|------|-----|-------|------|-------|

| A <sub>n</sub> (V)  | 0,35 | -0.8 | 1   | -0,75 | 0.37 | -0.12 |

| τ <sub>n</sub> (ps) | 101  | 101  | 101 | 101   | 101  | 101   |

#### B. Performances Comparison

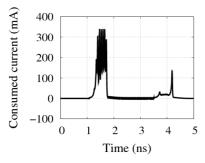

The simulated power consumption is 26.8mW for a Pulse Repetition Frequency of 200MHz. The energy consumed by pulse is then 140pJ. In comparison to previous published works, this consumption is high, as shown by Table IV. But, it is important to emphasize the fact that the energy by pulse criterion suppose that the power supply is turned off between two consecutive pulses to be independent of frequency. The total power consumption depends on the performances of the power manager circuit and the power consumed during the time needed to turn on and off the system can not be evaluated. As shown in Fig. 13, the presented pulse generator consumes zero DC current. This generator does not need power management to achieve a consumption of 140pJ by pulses. It's high in comparison with other generators but energy efficiency is better than previous works thanks to maximum pulse magnitude.

Moreover, the power consumption of the presented generator is essentially due to the size of the transmission gates. Such widths are used to achieve large pulse magnitudes in order to increase the transmission range. It is trivial to say that smaller pulse magnitude would lead to a smaller transmission gate and smaller consumed energy by pulses. To achieve a comparison of the energy by pulse regarding the pulse magnitude the following figure of merit is introduced:

$$\eta = \frac{E}{V_{PP}} \tag{5}$$

where E is the consumed energy by pulse and  $V_{pp}$  the peak to peak pulse magnitude. Simulated pulse generator performances are summarized and compared with others generators in Table IV. The consumed energy by pulses by volt is 70pJ.

TABLE IV. PERFORMANCE SUMMARIZE OF PROPOSED GENERATOR AND COMPARISON WITH PREVIOUS WORKS

| Reference   | Technology<br>(µm) | V <sub>DD</sub> (V) | V <sub>PP</sub> (V) | E<br>(pJ/pulse) | η<br>(pJ/pulse/V) |

|-------------|--------------------|---------------------|---------------------|-----------------|-------------------|

| [6] - 2007  | CMOS-0,18          | 1,5                 | 0,18                | 18pJ            | 100               |

| [13] - 2006 | CMOS-0,18          | 1,8                 | 0,9                 | 180pJ           | 200               |

| [9] - 2007  | CMOS 0,09          | 1                   | 0,65                | 47pJ            | 72.3              |

| [7] - 2008  | CMOS 0,18          | 1,5                 | 0,16                | 16,8pJ          | 105               |

| This Work   | CMOS 0 13          | 12                  | 2                   | 140nI           | 70                |

Figure 13. Consumed current at PRF=200MHz

#### V. Conclusion

The use of a H-Bridge as pulse combination circuit in fully tunable generator is proposed and simulated with 0.13µm CMOS technology. Simulation results show the circuit ability to generate different pulse shapes with peak to peak pulse magnitude of 2V with supply voltage of 1.2V. The pulse generator consumes zero DC power and 140pJ by pulse. Finally, the performances of the H-bridge allow the generation of pulse spectrum close to the predicted one which allows simple pulse tuning.

#### REFERENCES

- [1] Federal Communications Commission, "FCC rules and regulations," Part 15, July 2008.European Telecommunications Standards Institute, "Harmonized European Standard," February 2008.

- [2] Datta, P.K.; Xi Fan; Fischer, G. "A Transceiver Front-End for Ultra-Wide-Band Applications"; Circuits and Systems II: Express Briefs, IEEE Transactions on; Volume 54, Issue 4, April 2007 Page(s):362 366.

- [3] Duenas, S.R.; Xinzhong Duo; Yamac, S.; Mohammed Ismail; Li-Rong Zheng; "CMOS UWB IR Non-Coherent Receiver for RF-ID Applications; Circuits and Systems, 2006 IEEE North-East Workshop on; 18-21 June 2006 Page(s):213 - 216

- [4] Bachelet, Y.; Bourdel, S.; Gaubert, J.; Bas, G.; Chalopin, H.; "Fully integrated CMOS UWB pulse genrator", Electronics Letters, Volume 42, Issue 22, Oct. 26 2006, Page(s):1277 – 1278.

- [5] Jeongwoo Han; Cam Nguyen "Ultra-wideband electronically tunable pulse generators"; Microwave and Wireless Components Letters, IEEE; Volume 14, Issue 3, March 2004 Page(s):112 – 114

- [6] Tuan-Anh Phan; Jeongseon Lee; Krizhanovskii, V.; Seok-Kyun Han; Sang-Gug Lee;" A 18-pJ/Pulse OOK CMOS Transmitter for Multiband UWB Impulse Radio"; Microwave and Wireless Components Letters, IEEE; Volume 17, Issue 9, Sept. 2007 Page(s):688 – 690

- [7] Phan, A. T.; Lee, J.; Krizhanovskii, V.; Le, Q.; Han, S.-K.; Lee, S.-G.; "Energy-Efficient Low-Complexity CMOS Pulse Generator for Multiband UWB Impulse Radio"; Circuits and Systems I: Regular Papers, IEEE Transactions on; Volume 55, Issue 11, Dec. 2008 Page(s):3552 – 3563

- [8] H. Kim, D. Park, and Y. Joo, "All-Digital Low-Power CMOS Pulse Generator for UWB system," Electronic Letters, vol. 40, no.24, 25 November 2004.

- [9] Wentzloff, D.D.; Chandrakasan, A.P.;" A 47pJ/pulse 3.1-to-5GHz All-Digital UWB Transmitter in 90nm CMOS"; Solid-State Circuits Conference, 2007. ISSCC 2007. Digest of Technical Papers. IEEE International; 11-15 Feb. 2007 Page(s):118 591.

- [10] S. Bourdel, Y. Bachelet, J. Gaubert, M. Battista, M. Egels, N. Dehaese, "Low-Cost CMOS Pulse Generator for UWB Systems," Electronic Letters, vol. 43, issue 25, pp. 1425-1427, 6 December 2007.

- [11] H. Kim, Y. Joo, "Fifth-derivative Gaussian pulse generator for UWB system," IEEE Radio Frequency Integrated Circuits (RFIC) Symposium 2005, Digest of Papers 2005, pp. 671-674, 12-14 June 2005.

- [12] S. Bourdel, J. Gaubert, O. Fourquin, R. Vauche, and N. Dehaese, "CMOS UWB Pulse Generator Co-Designed with Package Transition," IEEE Radio Frequency Integrated Circuits (RFIC) Symposium 2009, in press.

- [13] Barras, D.; Ellinger, F.; Jackel, H.; Hirt, W.;" Low-power ultrawideband wavelets generator with fast start-up circuit"; Microwave Theory and Techniques, IEEE Transactions on; Volume 54, Issue 5, May 2006 Page(s):2138 – 2145.