# Evaluation of thermo-mechanical stresses of a power module dedicated to high temperature applications

Laurent Dupont, Régis Meuret, Zoubir Khatir, B<br/> Parmentier, Stéphane Lefebvre, Serge Bontemps

# ▶ To cite this version:

Laurent Dupont, Régis Meuret, Zoubir Khatir, B<br/> Parmentier, Stéphane Lefebvre, et al.. Evaluation of thermo-mechanical stresses of a power module dedicated to high temperature applications. HITEN 2005 - International Conference on High Temperature Electronics, Sep 2005, Paris, France. 6p. hal-01704218

# HAL Id: hal-01704218 https://hal.science/hal-01704218

Submitted on 8 Feb 2018  $\,$

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## **Evaluation of thermo-mechanical stresses** of a power module dedicated to high temperature applications

L. Dupont INRETS-LTN, SATIE dupont@inrets.fr

> Z. Khatir INRETS-LTN, khatir@inrets.fr

S. Lefebvre SATIE, UMR CNRS 8029 lefebvre@satie.ens-cachan.fr R. Meuret HISPANO SUIZA regis.meuret@hispano-suiza-sa.com

B. Parmentier SCHLUMBERGER bparmentier@clamart.oilfield.slb.com

S. Bontemps APT EUROPE SBontemps@AdvancedPower.com

#### Abstract

In avionic area, the trend is to a growing use of power electronics systems. In this context, we will present results concerning test vehicles (power modules) in order to improve a device assembly technology dedicated to be located "on the engine", in harsh operating conditions with thermal cycling from -50°C to 200°C in the worst case. The paper focuses on failure modes observed under high operating temperature and high temperature cycles, especially ceramic cracks, conchoidal fracture under the copper lead-frame and solder crack initiation. Numerical thermo-mechanical simulations of the assembly allow to understand the origin of the failures and to improve the assembly lifetime under such severe operating conditions. The objectives of the study are to assess the lifetime behaviour of these modules towards both high temperature and thermal cycling effects.

## **1. Introduction**

Temperature and thermal cycling are generally considered to be the key factors in the reliability of power semiconductor devices [1]. Avionic applications lead to use power converters in harsh environment with high temperature cycles and elevated ambient temperature when power modules are located on the engine. The application considered in this study is concerning with a three phase inverter for a low power (< 5kW) actuator control. The power electronic part will be located on the engine with a maximum ambient temperature about 200 °C. Moreover, the mission profile results for high temperature variation during landing and takeoff phases, in the worst case from -50°C to +200°C, with a rate about  $\pm 10^{\circ}$ C/min. These extremely hard operating conditions result in thermo mechanical stresses and makes the power modules particularly exposed to fatigue failures [2]. Moreover, the required lifetime is about 50,000 hours corresponding to 5,000 to 10,000 cycles. High temperature applications for low power electronics relate to also drilling applications and research synergies between different trades are possible and desirable on these subjects.

A test vehicle (power module) was realised by APT Europe. As expected, we will show that the Direct Copper Bonding (DCB) technology (300µm copper on AlN) is not well adapted for avionic constraints, especially under high temperature cycles. Nevertheless, the test vehicles have allowed device characterisations in high temperature adapted packages and studies on the solders. These first results will be completed by investigations on more adapted ceramic substrates such as dimples on DCB, DAB or Si3N4 substrates.

In order to evaluate the ability of the power assembly to operate in high temperature environment and its reliability to undergo high temperature cycling variations according to the application requirements, thermal cycling tests have been performed on the tests vehicles. Finally, finite element analysis (FEA) results are presented in order to evaluate mechanical stresses applied to the electronic assembly and to explain the observed failure modes. The combination of experimental and numerical results allowed us to identify the failure modes and helped us to propose solutions in order to improve the device lifetime according to the mission profiles. Furthermore, the aims of these investigations are to identify the main factors that could increase the lifetime expectancy of the power module in such a harsh environment.

### 2. Power module dedicated to high temperature application

The test vehicle and module assembly developed by APT Europe are presented in Fig. 1. Materials selection is made not only to reach the lowest possible junction to case thermal resistance but also to minimize the mechanical stresses caused by thermal expansion coefficients mismatches. This is a very important issue for the reliability of the device.

### International Conference on High Temperature Electronics (HITEN) - Sept. 2005 - Paris

DCB on AlN substrates, AlSiC base plate and appropriate solder alloys were selected in order to meet these goals. These modules integrate two electrical functions: a buck chopper for electrical characterisations of each semiconductor types (Si CoolMOS transistor APT 47N60BC3 47A – 600V and SiC Diode CREE CSD1060 10A – 600V) and a phase inverter in order to evaluate electrical functionalities at high ambient temperature ( $200^{\circ}$ C). The studied power module was used as a test vehicle for evaluating both electrical performances in the 25°C to 200°C temperature range and the ability of the device assembly to undergo high temperature cycles. Si COOLMOS<sup>TM</sup> transistors and SiC Schottky diodes integrated in the test vehicle have been already characterized. Results are presented in a previous paper [3].

### **3.** Passive thermal cycling tests and results

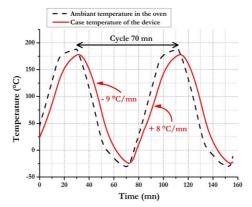

In order to evaluate the ability of the power assembly to operate in high temperature environment and its reliability to undergo high temperature cycling variations according to the application requirements, thermal cycling tests have been performed. The thermal profile of these tests is presented in Fig. 2 where the black dotted line is the ambient temperature in the oven and the red solid line is the module base plate temperature. The cycle duration is about 70mn with a device temperature rate of rise about 8°C/mn and 9°C/mn for the decreasing rate. Temperature varies from -30°C to 180°C. In a first step, in order to get the worst tests conditions, we have applied a very short dwell time (15mn). In these conditions, durations are not sufficient for the solder alloy to have a significant creep effect during dwell time. A second test campaign is under development in order to investigate the dwell time effect and elasto-plastic and creep analysis for the whole loading history will be reported later.

Figure 2: Passive thermal cycling profile applied onto the test vehicle

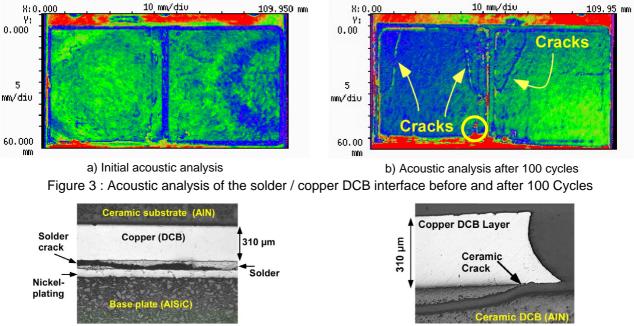

As a result, Fig. 3 shows a comparison of SAM analyses of the solder layer between base plate and ceramic between initial state and after 100 cycles. While no damages appear in the initial state (Fig. 3a), delaminations, located at some corners of the solder layer, are visible in Fig.3b. These degradations of the solder have been already observed after only 50 thermal cycles in the same proportion. After 100 cycles, acoustic analyses show furthermore longitudinal cracks in the same solder layer, which look like fractures rather than delaminations. One of such a fracture is shown in Fig.4a in its lengthwise. These defects are probably due in one hand to the fact that no stress relaxation occurs in the solder and in the other hand to the high cycling temperature range and especially because of the very low minimum reached temperature (-30°C) where the solder is mechanically hardened before to soften when the temperature rises. Concerning the die attach solder, it seems to remain safe. Another failure mode is concerning with dissociation of the copper lead-frame from the ceramic. Microsections have been performed and cracks are visible in Fig. 4b. The crack has propagated from the lead-frame edge until under the chip. This result has been already observed by others authors [6-8]. This failure leads to an increase of the thermal resistance and thermal management problems.

No lift off bond wires (100µm diameter) have been observed during the thermal cycling test, but the solder of external connectors have been damaged by the increasing of intermetallic and keep off to realise all electrical characterizations.

We nevertheless could measure some parameters like threshold voltage, leakage current and on-state voltage which weren't significantly modified after 100 thermal cycling.

a) Solder between base plate and the copper DCB layer

Figure 4: Solders and analysis of the DCB ceramic (AIN) - lead frame lift up after 100 thermal cycles

#### 4. Thermomechanical finite element analysis

In order to understand and to corroborate the experimental results such as the ceramic substrate cracks or the solder fracture, the thermomechanical behaviour of the test vehicle during thermal cycling has been simulated. These simulations have been performed by Finite Element Analysis (FEA) with ANSYS 8.0 [9]. Because of high thermal cycling amplitude, the physical parameters are modelled with temperature dependence. Finally, according to the very small time constants of the mechanical stress-strain variables and the rate dependent plasticity of the solder, quasi-static with transient effects calculations have been performed during the simulated thermal cycles.

#### 4.1 Finite Element Model

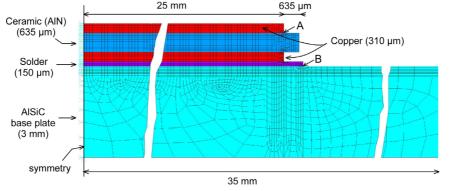

A simple model representative of the power module has been used in a 2D axisymmetric model (Fig. 5).

Figure 5 : Finite Element Model of the assembly.

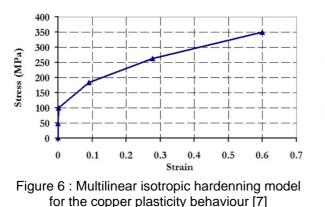

The power module is made of an AlSiC base plate where a DCB substrate is soldered with a solder material (92.5Pb5Sn2.5Ag). Such a model is rather complex and consequently material properties have to be considered carefully. Both the AlSiC base plate and the AlN ceramic are assumed to be linear elastic. Concerning the 92.5Pb5Sn2.5Ag solder, which has a liquidus temperature near 290°C, it has been considered viscoplastic in order to take into account the rate dependent plasticity (creep behaviour) which occurs over time. Finally, a rate independent plasticity has been considered for the copper layers of the DCB substrate with a multilinear isotropic hardenning

behaviour (see Fig.6) because the very high temperature swings. Material properties are given in Table 1 and the Anand law [10-12] was used for the viscoplastic behaviour of the solder with the parameters given and defined in [12]. One of the modelling difficulties is due to the geometry where layer thicknesses are very small compared to their areas. The whole model has been meshed with PLANE42 elements except for the solder material which has been meshed with VISCO106 elements for highly non-linear behaviour such as creep. The finite element model required a total of 9514 elements and 9729 nodes.

| Materials             | Thickness | СТЕ  | Youg's<br>Modulus              | Poisson<br>ratio | Specific<br>Heat                    | Thermal conductivity               | Tensile<br>strength |

|-----------------------|-----------|------|--------------------------------|------------------|-------------------------------------|------------------------------------|---------------------|

|                       | Mm        | ppm  | Мра                            | -                | J.Kg <sup>-1</sup> .K <sup>-1</sup> | W.m <sup>-1</sup> .K <sup>-1</sup> | MPa                 |

| AlSiC                 | 3         | 8    | 200                            | 0.24             | 740                                 | 190                                |                     |

| Solder 92.5Pb5Sn2.5Ag | 0.15      | 29   | 24.1-28×10 <sup>-3</sup> T(°C) | 0.4              | 130                                 | 23                                 |                     |

| Copper DCB            | 0.31      | 14.5 | 130                            | 0.34             | 390                                 | 390                                |                     |

| Ceramic (AlN)         | 0.635     | 5    | 320                            | 0.23             | 730                                 | 170                                | 270                 |

Table 1 : Materials proprieties used in thermomechanical simulation

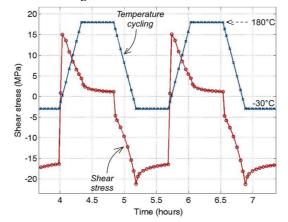

Figure 7 : Simulated passive thermal cycling

The methodology consists to compute, in a first step, the initial mechanical stresses induced by the assembly process when cooling down the solder material from  $287^{\circ}$ C to  $20^{\circ}$ C (room temperature). The highest temperature is the liquidus value of the solder for which this material is assumed stress-free. Then, a simulated thermal cycling is applied to the assembly model as presented in Fig.7. The model is first uniformly cooled from  $20^{\circ}$ C to  $-30^{\circ}$ C with a negative ramp of  $10^{\circ}$ C/mn, then 30 minutes dwell time followed by heating phase ramp of  $10^{\circ}$ C/mn until  $180^{\circ}$ C and 30 mn dwell time and so on.

#### **5.2** Numerical results

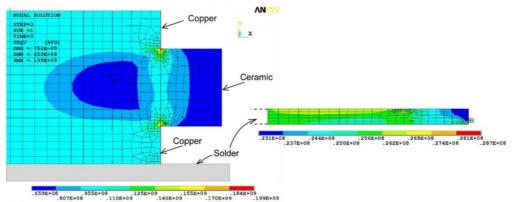

The Von Mises residual stresses distribution, after the module has been cooled down from soldering temperature  $(290^{\circ}C)$  to room temperature  $(20^{\circ}C)$ , are shown in Fig.8, where only a part of solder material layer and the DCB substrate are visible.

Figure 8: Residual stresses (Von Mises in MPa) in the solder layer and DCB substrate

As expected, the stress levels are more important in the DCB substrate than in the solder material, with a maximum value of 199 MPa localized at point A in the ceramic (see Fig.5). This is due to the strain hardening of the copper and the high CTE mismatch between the copper lead-frame (14.5 ppm) and AlN ceramic (5 ppm). Indeed, the plastic

yielding of the copper metalisations has been reached during the soldering process and this material has hardened leading to high residual stresses in the ceramic. Nevertheless, we did not take into account all the stress history of the metalization such as the DCB process itself and only the soldering process has been simulated in this paper. Lower residual stresses are visible in the solder (Fig.8) which was stress-free at 290°C but its cooling down increases the stress levels until around 28 MPa at the corner edge (point B of Fig.5).

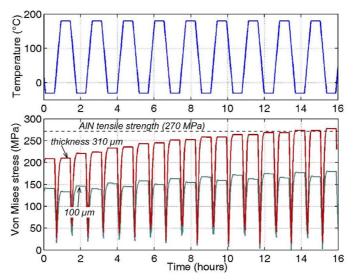

The maximum value of stress in ceramic (point A) is plotted with time dependence during thermal cycling in the lower graph of Fig.9 in red solid line (the copper thickness is  $310 \,\mu$ m), whereas the temperature cycles are shown in the upper graph between -30°C and 180°C. From the initial value of 199 MPa (Fig.8), the stress level increases at every cycle, according to the strain hardening of the copper layers, and reaches, at the 9<sup>th</sup> cycle, the AlN tensile strength which is about 270 MPa [13]. This theoretical result means that the ceramic would have cracked. These simulated results confirm the experimental observations described above (Fig.4b).

Figure 9: Von Mises stresses evolution in ceramic (point A) and copper thickness effect.

Such DCB assembly, which is used in the power module presented above (Fig.1), is clearly unsuited for high temperature applications. In order to reach at least  $180^{\circ}$ C-200°C maximum temperature with aluminum nitride, one must use thinner copper lead-frames while remaining compatible with the current rating of the module. As illustration, we can see in the lower graph of Fig.9, in green line, the Von Mises stress evolution, at the same location of the ceramic, for 100 µm thickness of copper in both sides of AlN. As a result, the initial stress are significantly lower, around 140 MPa instead of 199 MPa, and the stress increase is smaller and reaches only 178 MPa at the 9<sup>th</sup> cycle. In these conditions, the assembly may undergo much more thermal cycles before ceramic failure. In another way, the use of dimples along the copper edges may reduce the ceramic stresses, but this must be analysed carefully. Other potential solution could be the use of aluminium metalisation for Direct Aluminum Bonding (DAB) that provides much lower yield strength and no significant strain hardening.

Figure 10: Shear stresses evolution in solder (point B) and temperature cycling.

We can see, in Fig.10, during two thermal cycles (blue line), the shear stress evolution (red line) in the solder material located in point B (Fig.5), where the stresses reach the maximum value. At the end of the dwell time at low temperature

(-30°C), stresses are around -16 MPa in this corner location. Then, as soon as the temperature begins to rise from -30°C to 180°C, shear stress varies quasi-instantaneously from -16 MPa to 15 MPa, in such a way that a shear stress variation of more than 30 MPa is applied to the solder. This may explain the fractures obtained experimentally in the power module and visible in Fig.3b and Fig.4a. Further investigations have to be performed in order to confirm this hypothesis. Then, during the rise period of the temperature, stresses are relaxed in the solder due to the viscoplastic behaviour until a low value of 1.2 MPa. During the 30 mn dwell time at 180°C, stresses continue to decrease lightly in the solder at constant temperature. When temperature decreases from 180°C to -30°C, stress increases to -20 MPa. Then, during dwell time at -30°C, we observe once again a stress relaxation in the solder. Contrarily at the high temperature behaviour, this last relaxation is very light (from -20 MPa to -17 MPa) due to strengthening of the solder material at low temperature. As a result, a large amount of plastic strain occurs in the solder that can lead to the delamination of this very large layer area. Fig. 10 gives the shear stress distributions in the solder layer in the vicinity of point B during the dwell times both at -30°C and 180°C.

## 6. Conclusion

In this paper, it has been presented some results of thermal cycling tests applied to a test vehicle. Thermal cycling of high amplitude have been applied between -30°C and 180°C with high temperature variations about 8.5°C/mn. After only 100 cycles, microsection analyses have shown that ceramic cracks occurred and have lead to conchoidal fractures of the ceramic under the copper metalisation. This is due to the strain hardening of the copper layers that lead to increase stress levels in the ceramic at high temperature during the thermal cycling until its tensile strength. Furthermore, acoustic analyses have shown longitudinal cracks in the solder layer, which look like a fracture rather than a delamination.

Finite element modelisations have been performed in order to evaluate the stress and strain levels applied to the test vehicle during thermal cycling. The numerical results have allowed understanding the observed failures. In particular, the hardening behaviour of the copper matalisation that leads to the ceramic fracture has been shown. Further experimental and numerical investigations must be done in order to investigate the dwell time and the creep effect. In an other way, in order to lower the stresses in the ceramic at high temperature values, near 200°C, and avoid the conchoidal cracks, dimples associated with DCB substrates or more adapted ceramic materials, such as Si3N4 or Direct Aluminum Bonding (DAB) will be fully investigated.

## 7. Acknowledgments

The authors acknowledge contributions from TRONICO company for the thermal passive cycling tests as well as STRUERS company who helped us to realise a microsection of the test module after thermal cycling in order to analysis the failure modes.

## 8. Bibliography

[1] W. Wondrack, "Physical Limits and Lifetime Limitations of Semiconductor Devices at High Temperatures", Microelectronics Reliability, June-July 1999, Vol. 39 (6-7), p. 1113-1120.

[2] P. McCluskey and al., "Packaging of Power Electronics for High Temperature Applications", Advancing Microelectronics, Jan./Feb. 1998, p. 19-24.

[3] L. Dupont and al., "Characterisation of Silicon Carbide Schottky Diodes and COOLMOSTM Transistors at High Temperature", in PESC conference, Aachen, 2004.

[4] X. W. Liu and W. J. Plumbridge, "Thermomechanical Fatigue of Sn-37 wt.% Pb Model Solder Joints", Materials Science and Engineering A, 5 December 2003 2003, Vol. 362 (1-2), p. 309-321.

[5] B. Y. Wu and Y. C. Chan, "Electric Current Effect on Microstructure of Ball Grid Array Solder Joint", Alloys and Compounds, 21 September 2005, Vol. 392, p. 237-246.

[6] G. Mitic, R. Beinert, and al., "Reliability of AlN Substrates and their Solder Joints in IGBT Power Modules", Microelectronics Reliability, 1999, Vol. 39, p. 1159-1164.

[7] Y. Nagatomo and T. Nagase, "The Study of the "Power Modules with High Reliability for EV Use", in 17th EVS conference, Montreal, Oct. 2000.

[8] J. Schulz-Harder, "Advantages and New Development of direct Bonded Copper Substrates", Microelectronics Reliability, 2003, Vol. 43, p. 359-365.

[9] ANSYSTM, "ANSYSTM 8.0", Inc., Editor, 2002.

[10] L. Anand, "Constitutive equations for hot-working of metals", International Journal of plasticity, 1985, Vol. vol.1, p. 213-231.

[11] ANSYSTM, "Rate-Dependent Plasticity", 2005, ANSYSTM theory Book.

[12] J. Wilde and al, "Rate Dependent Constitutive Relations Based on Anand Model for 92.5Pb5Sn2.5Ag Solder", IEEE transactions on Advanced Packaging, 2000, Vol. Vol.23 N° 3, p. 408-414.

[13] J. Shackelford and W. Alexander, "The Crc Materials Science and Engineering Handbook", CRC Press, 2000, Vol. Third Edition.