# Fracture mechanics in new designed power module under thermo-mechanical loads

Camille Durand, Markus Klingler, Daniel Coutellier, Hakim Naceur, Arian Grams, Olaf Wittler

## ▶ To cite this version:

Camille Durand, Markus Klingler, Daniel Coutellier, Hakim Naceur, Arian Grams, et al.. Fracture mechanics in new designed power module under thermo-mechanical loads. JIP 2014 - Fatigue Design & Material Defects, Jun 2014, Paris, France. pp.04015, 10.1051/matecconf/20141204015. hal-01669938

HAL Id: hal-01669938

https://hal.science/hal-01669938

Submitted on 27 Apr 2022

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

DOI: 10.1051/matecconf/20141204015

© Owned by the authors, published by EDP Sciences, 2014

# Fracture mechanics in new designed power module under thermo-mechanical loads

Camille Durand<sup>1,2,a</sup>, Markus Klingler<sup>1</sup>, Daniel Coutellier<sup>2</sup>, Hakim Naceur<sup>2</sup>, Arian Grams<sup>3</sup> and Olaf Wittler<sup>3</sup>

**Abstract.** Thermo-mechanically induced failure is a major reliability issue in the microelectronic industry. On this account, a new type of Assembly Interconnected Technology used to connect MOSFETs in power modules has been developed. The reliability is increased by using a copper clip soldered on the top side of the chip, avoiding the use of aluminium wire bonds, often responsible for the failure of the device. Thus the new designed MOSFET package does not follow the same failure mechanisms as standard modules. Thermal and power cycling tests were performed on these new packages and resulting failures were analyzed. Thermo-mechanical simulations including cracks in the aluminium metallization and intermetallics (IMC) were performed using Finite Element Analysis in order to better understand crack propagation and module behaviour.

# 1. Design of the power module

The power module used in this study is a newly designed MOSFET package. It has an electric connection achieved by a copper clip soldered on top of the chip instead of using a wire bond.

### 2. Experimental tests

Thermal cycle testing refers to situations where the environmental surrounding of the power module undergoes cyclic thermal variations. Here, accelerated passive thermal cycles were performed. These consist of a dwell at a high temperature, a ramp to a low temperature, a dwell at the low temperature, a ramp to the high temperature, and then the cycle is repeated. In contrast, power cycling refers to situations where the heat source is the electronic package itself. The package has a chip that is powered and thus dissipates heat through the entire module. Both temperature and power cycling were performed on modules and the following failures were observed: cracks in chip, delamination between mold and Cu-leadframe, solder degradation, cracks in mold, delamination and degradation of chip metallization and intermetallic (IMC). Some of these failures are well known in microelectronics [1, 2]: cracks in chip

<sup>&</sup>lt;sup>1</sup>Robert Bosch GmbH, Automotive Electronics, 72762 Reutlingen, Germany

<sup>&</sup>lt;sup>2</sup>LAMIH UMR CNRS 8201, 59313 Valenciennes Cedex 9, France

<sup>&</sup>lt;sup>3</sup>Fraunhofer IZM, 13355 Berlin, Germany

<sup>&</sup>lt;sup>a</sup>Corresponding author: camille.durand@de.bosch.com

This is an Open Access article distributed under the terms of the Creative Commons Attribution License 4.0, which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

#### MATEC Web of Conferences

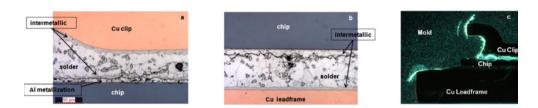

Figure 1. a) Inner structure and 1b) layer composition of a MOSFET with a copper clip.

**Figure 2.** a) Crack in chip metallization, 2b) crack in bottom solder, 2c) delamination mold-Cu leadframe, mold-solder meniscus, crack in chip metallization and cracks in mold (dye penetrant inspection with UV microscope).

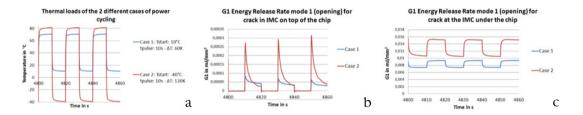

**Figure 3.** Thermal loads of the 2 cases of power cycling, 3b) energy release rate at the crack in IMC on top of the chip, 3c) energy release rate in the crack at the IMC under the chip.

induced by sawing, and delamination between mold and Cu-leadframe. Solder degradation is a critical failure induced by temperature cycling. Cracks in mold hardly ever happen, but can cause other failures in the device, like solder delamination. Degradation and delaminations in chip metallization and IMC are due to power cycling.

#### 3. Numerical simulations

In order to simulate power cycling, a 2D Finite Element Model of a MOSFET has been created with an axisymmetric condition. Cracks were included in the IMC layer on top of the chip and at the interface between the chip and the IMC below. For those cracks the Virtual Crack Closure Technique (VCCT) is used to determine the energy release rate [3]. Later, another crack will be defined in the chip metallization, and the Crack Tip Opening Displacement (CTOD) method will be used [4]. Two different cases of power cycling were simulated in order to determine the influence of test parameters (start temperature  $T_{\text{start}}$ , temperature swing  $\Delta T$  and pulse width  $t_{\text{pulse}}$ ) on failure mechanisms. For both cracks in the IMC, the power cycling case with a bigger temperature swing reaches a higher value of energy release rate. So high temperature swings are more critical for the module. Then, by comparing the criterion values for each crack, one can see that the energy release rate for the opening mode is much higher for the crack at the IMC under the chip than for the crack in the IMC on top of the chip.

#### 4. Conclusions

Simulations with different tests parameters were performed and it results in different stresses and fracture criterions. Based on that, life time models can be developed with correlation of EOL tests.

#### References

- [1] M. Ciappa, Microelectronics reliability 42, pp. 653–667 (2002)

- [2] W. Kanert, 12th Int. Conf. EuroSimE (2011)

- [3] R. Krueger, Appl. Mech. Rev. **57** (2004)

- [4] F. Ma, X. Deng, M.A. Sutton and J.C. Newman Jr, ASTM STP **1359** pp. 86–110 (1999)