### Origin and repartition of the oxide fixed charges generated by electrical stress in memory tunnel oxide

S. Bernardini, P. Masson, M. Houssa, F. Lalande

#### ▶ To cite this version:

S. Bernardini, P. Masson, M. Houssa, F. Lalande. Origin and repartition of the oxide fixed charges generated by electrical stress in memory tunnel oxide. Applied Physics Letters, 2004, 84 (21), pp.4251-4253. 10.1063/1.1756681. hal-01633146

### HAL Id: hal-01633146 https://hal.science/hal-01633146v1

Submitted on 29 Jan 2018

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Origin and repartition of the oxide fixed charges generated by electrical stress in memory tunnel oxide

Sandrine Bernardini, Pascal Masson, Michel Houssa, and Frederic Lalande

Citation: Applied Physics Letters 84, 4251 (2004); doi: 10.1063/1.1756681

View online: http://dx.doi.org/10.1063/1.1756681

View Table of Contents: http://scitation.aip.org/content/aip/journal/apl/84/21?ver=pdfcov

Published by the AIP Publishing

#### Articles you may be interested in

Charge storage properties of InP quantum dots in GaAs metal-oxide-semiconductor based nonvolatile flash memory devices

Appl. Phys. Lett. 101, 212108 (2012); 10.1063/1.4767522

Study of the relative performance of silicon and germanium nanoparticles embedded gate oxide in metal—oxide—semiconductor memory devices

J. Appl. Phys. 109, 064504 (2011); 10.1063/1.3555087

Bandgap engineering of tunnel oxide with multistacked layers of Al 2 O 3 / HfO 2 / SiO 2 for Au-nanocrystal memory application

Appl. Phys. Lett. 93, 132907 (2008); 10.1063/1.2995862

Comparison of structural and electrical properties of praseodymium oxide and praseodymium titanium oxide charge trapping layer memories

J. Appl. Phys. **102**, 074111 (2007); 10.1063/1.2786102

Conduction mechanisms and charge storage in Si-nanocrystals metal-oxide-semiconductor memory devices studied with conducting atomic force microscopy

J. Appl. Phys. 98, 056101 (2005); 10.1063/1.2010626

# Origin and repartition of the oxide fixed charges generated by electrical stress in memory tunnel oxide

Sandrine Bernardini, Pascal Masson,<sup>a)</sup> Michel Houssa,<sup>b)</sup> and Frederic Lalande L2MP, UMR-CNRS 6137, IMT Technopôle de Chateau Gombert, 13451 Marseille Cedex 20, France

(Received 10 November 2003; accepted 1 April 2004; published online 7 May 2004)

A method is proposed to determine the origin and the spatial oxide fixed charge repartition in memory tunnel oxide from Fowler–Nordheim current measurements after electrical stress. The Poisson equation resolution in the dielectric layer is required to account for the nonsymmetric tunneling barrier deformation, resulting from charges generated within the dielectric layer. From current–voltage characteristics measurements and simulations, we have determined the spatial distribution of the oxide fixed charges within the dielectric layer of metal/SiO<sub>2</sub>/metal structures. In addition, the kinetics of the oxide charge generation can be explained by a dispersive hydrogen transport model. © 2004 American Institute of Physics. [DOI: 10.1063/1.1756681]

Usually, the tunneling current flowing through the gate insulator in metal–oxide–semiconductor (MOS) structures is calculated without considering the influence of dielectric bulk charges on the shape of the tunneling barrier. However, it is well known that the electrical properties of MOS structures depend much on electrically active defects. In this work, we describe a method to determine the nonuniform dielectric fixed charge distribution induced by electrical stress of metal/SiO<sub>2</sub>/metal structures, based on the analysis of tunneling currents after electrical stress. Our approach lies in the continuity of the work of Ku *et al.*<sup>4</sup> which have performed an analytical resolution of Poisson equation in the case of a uniform fixed charge repartition. It is also shown that the kinetics for the oxide fixed charge buildup can be explained by a dispersive hydrogen transport model.

In this study, the tunneling oxide capacitor, with area  $W \times L = 1000 \times 75~\mu\text{m}^2$ , is assumed to be equivalent to three series capacitances:<sup>5</sup> a highly doped silicon electrode (n type) with  $N_{\text{Sub}} = 1.5 \times 10^{25}~\text{m}^{-3}$ , an oxide layer with  $t_{\text{ox}} = 8.3~\text{nm}$ , and a highly doped n-type polysilicon electrode (gate electrode) with  $N_G = 1.2 \times 10^{26}~\text{m}^{-3}$ . The relationship between the two surface potentials,  $\Psi_S$  and  $\Psi_G$  (for the substrate and the gate, respectively), and the gate voltage,  $V_{\text{GB}}$ , is given by

$$V_{\rm GB} = \Phi_{\rm MS} - \frac{Q_{\rm ox eff}}{C_{\rm ox}} + \Psi_{\rm S} - \Psi_{\rm G} - \frac{Q_{\rm SC}(\Psi_{\rm S})}{C_{\rm ox}},\tag{1}$$

where  $C_{\rm ox}$  is the oxide capacitance,  $\Phi_{\rm MS}$  is the gatesemiconductor work function difference,  $Q_{\rm SC}$  is the total bulk charge, and  $Q_{\rm ox\,eff}$  is the effective charge density seen from the bulk interface. For a given gate voltage and a given dielectric charge density, the spatial distribution of the dielectric potential, V, is calculated from Poisson resolution within the dielectric layer using a three-point finite difference method and the following boundary limits:

$$\begin{cases} V_{(y=0)} = 0 \\ V_{(y=t_{ox})} = -\frac{Q_{SC} + Q_{ox \text{ eff}}}{C_{ox}} \end{cases}$$

(2)

where *y* is the distance from the bulk (silicon electrode).

Then, using Wentzel-Kramer-Brillouin approximation,<sup>6</sup> we express the current, due to the tunneling of electrons from the substrate to the gate  $(I_{\rm si})$  and from the gate to the substrate  $(I_{\rm poly})$ , respectively,

$$I_{\text{si,poly}} = A_{\text{eff}} Q_{n \text{si,poly}} \times F_{\text{imp}} \left[ \exp \left( -2 \sqrt{\frac{2qm_{n \text{ox}}}{\hbar^2}} \int_0^{t_{\text{ox}}} \sqrt{\Phi_{b \text{si,poly}}} dy \right) \right],$$

(3)

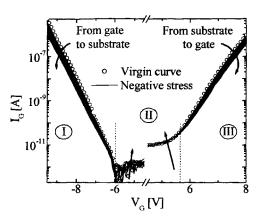

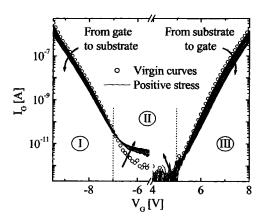

where  $A_{\rm eff}$  is the effective area of the capacitor,  $Q_n$  is the inversion charge in the substrate  $(Q_{n{\rm si}})$  and in the gate  $(Q_{n{\rm poly}})$ ,  $F_{\rm imp}$  is the impact frequency,  $\Phi_b$ , is the barrier height between the silicon,  $\Phi_{b{\rm si}}$  (or polysilicon,  $\Phi_{b{\rm poly}}$ ) conduction band and the dielectric conduction band, and  $m_{n{\rm ox}}$  is the electron mass in oxide. Figures 1 and 2 illustrate the current–voltage (I-V) characteristics of two different capacitors measured after cumulative times of negative (-9.5 V) and positive (8 V) gate voltage stress, respectively.

FIG. 1. I-V characteristics of the capacitor recorded after cumulative times of negative gate voltage stress (-9.5 V).

a) Author to whom correspondence should be addressed; electronic mail: pascal.masson@polytech.univ-mrs.fr

b)Present address: IMEC, 75 Kapeldreef, B-3001 Leuven, Belgium.

FIG. 2. I-V characteristics of the capacitor recorded after cumulative times of positive gate voltage stress (8 V).

In Figs. 1 and 2, we will only discuss parts I and III which correspond to a decrease in the Fowler-Nordheim tunneling current. This phenomenon is well known as the closure of the programmable window observed after numerous write-erase operations in EEPROM cells. We observe, in Figs. 1 and 2, a more pronounced current decrease for the injection of electrons from gate to substrate for a negative stress, and from the substrate to the gate for a positive stress. Based on this dissymmetric behavior of the tunneling current, we have compared three different negative oxide fixed charge distributions: Constant, Gaussian, and exponential. The constant oxide fixed charge distribution did not allow us to fit the experimental data for both positive and negative voltages. This result shows that the distribution of the fixed charge, generated by electrical stress within the dielectric layer, is nonuniform. In the following, we detail only our results for positive stress.

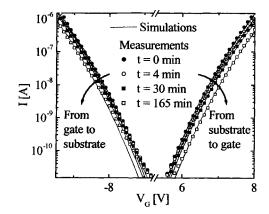

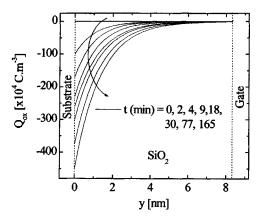

Considering a Gaussian oxide charge repartition, the maximum of charge density must be located close to the substrate/oxide interface. However, the best fits to the data (shown as solid lines in Fig. 3) have been obtained by considering a decreasing exponential charge distribution (cf. Fig. 4).

$$Q_{\text{ox}} = Q_{\text{max}} \exp\left(\frac{-y}{\lambda}\right) + Q_{\text{min}}, \qquad (4)$$

where  $Q_{\min}$  is the oxide charge in the virgin sample,  $Q_{\max}$  is

FIG. 3. Comparison of simulated and measured I-V characteristics of the capacitor after cumulative positive stress, under gate injection and substrate injection.

FIG. 4. Decreasing exponential distribution of the trapped oxide charges used to fit the measurements shown in Fig. 3.

the maximum value of the oxide trapped charges during the stress, and  $\lambda$  is the decay length. The increases in the  $|Q_{\rm max}|$  and  $\lambda$  values (from 0 to  $450\times10^4$  C m<sup>-3</sup> and from 0 to 16.25 Å, respectively) correspond to a trapped oxide charge moving away from the interface during the electrical stress. Let us remark that the determination of the oxide charge distribution using the two-level charge pumping technique on MOS transistors after electrical stress shows the same kind of spatial distribution for the oxide traps.<sup>8</sup>

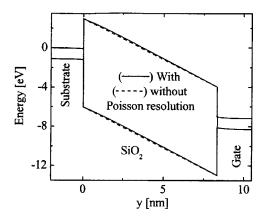

Figure 5 shows the impact of a negative fixed charge in the dielectric layer close to the silicon electrode, which induces a band diagram deformation on this area. This result can only be obtained by Poisson resolution within the dielectric layer. It clearly appears that after positive stress, electron tunneling current is more degraded for a positive voltage than for a negative voltage (cf. Fig. 2). Symmetrically, in case of negative stress (cf. Fig. 1), the induced fixed charges would be located close to the polysilicon electrode. Let us remark, that for EEPROM cells, the write—erase operations would lead to two decreasing exponential distributions of the oxide fixed charges (one on the silicon side and the other on the polysilicon side) which form one U-shaped curve.

A possible origin for the exponential negative fixed charge distribution in the oxide can be the release of hydrogen species at the Si/SiO<sub>2</sub> interface by an impacting electron during the stress. Then, the hydrogen species transport throughout the gate oxide and their subsequent trapping into

FIG. 5. Band diagram obtained with and without Poisson resolution within the  $SiO_2$  layer for the exponential negative fixed charge distribution at  $VG_1$  to  $VG_2$  after 165 min.

the oxide network lead to the generation of Si—O—H defects close to the interface. These defects are efficient electron trapping centers, forming SiO<sup>-</sup> defects which could correspond to the negative oxide charge generated during the stress. From these assumptions, the kinetics of Si—O—H precursor sites generation has been calculated within a dispersive transport model, where the charge generation is assumed to be limited by the random hopping of H<sup>+</sup> and its trapping in the SiO<sub>2</sub> layer.

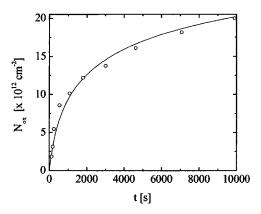

Within this model,  $^{10}$  the kinetics of charge density variation  $\Delta N_{\rm ox}$  is given by

$$\Delta N_{\text{ox}} = N_{\text{H}}^{+} \left( 1 - \int_{0}^{1} \text{SiO}_{2} G_{\text{SiO}_{2}}(y) dy \right),$$

(5)

where  $N_{\rm H+}$  is the density of protons close to the Si/SiO<sub>2</sub> interface and G(y) is a function related to the probability P(x,t) for finding a proton at a distance x at time t; the "improved trial function" described by McLean and Ausman<sup>12</sup> is used here for approximating G(y). In Eq. (5),  $\ell_{\text{SiO2}} = x_c / \ell_h t^{\alpha}$ , where  $x_c$  is the position of the hydrogeninduced defect centroid,  $\ell_h$  is the average proton hopping distance, and  $\alpha$  is a parameter characterizing the dispersiveness of the proton transport in the material. We fixed here  $\ell_h = 2.5 \text{ Å}$  and  $\alpha = 0.3$ , consistently with values reported in SiO<sub>2</sub>. <sup>10,11</sup> The kinetics of oxide charge generation derived from the data in Fig. 3 are compared to the model in Fig. 6. A very good agreement is obtained, with realistic values for  $N_{\rm H+} = 4 \times 10^{13} \ {\rm cm}^{-2}$  and  $x_c = 3 \ {\rm nm}$ , suggesting that the defect precursors for the negative charge generation could be Si-O-H centers.

To summarize, we have presented a method to determine the spatial oxide fixed charge repartition in memory tunnel oxide. This method is based on the Poisson equation resolution in the dielectric layer and presents the advantage to consider an arbitrary spatial distribution of oxide fixed charges. From I-V measurements after positive (or negative) stress and Poisson resolution within the dielectric layer, we have found a decreasing exponential distribution of the fixed dielectric charge with a maximum value at the substrate/SiO<sub>2</sub>

FIG. 6. Oxide charge kinetics comparison between the charge distribution used to fit the measurements shown in Fig. 3 (open circles) and the simulations obtained from a dispersive transport model (solid line).

(or SiO<sub>2</sub>/gate) interface. A possible explanation for this decreasing exponential distribution has been given from the generation of Si—O—H precursor defects close to the substrate/oxide interface, most probably leading to the creation of SiO<sup>-</sup> charges upon subsequent electron trapping.

- <sup>1</sup>Y. Yang, H. Niimi, and G. Lucovsky, J. Appl. Phys. 83, 2327 (1998).

- <sup>2</sup>Y. Shi, X. Wang, and T. P. Ma, IEEE Electron Device Lett. 19, 388 (1998).

- <sup>3</sup>E. M. Vogel, K. Z. Ahmed, B. Hornung, W. K. Henson, P. K. McLarty, G. Lucovsky, J. R. Hauser, and J. J. Wortman, IEEE Trans. Electron Devices 45, 1350 (1998).

- <sup>4</sup>P. S. Ku and D. K. Schroder, IEEE Trans. Electron Devices **41**, 1669 (1994).

- <sup>5</sup>S. Bernardini, P. Masson, M. Houssa, and F. Lalande, ESSDERC (2003), p. 589.

- <sup>6</sup>A. T. Fromhold, Quantum Mechanics for Applied Physics and Engineering (Dover, New York, 1981).

- <sup>7</sup>C. Papadas, G. Guibaudo, G. Pananakakis, C. Riva, and P. Ghezzi, IEEE Electron Device Lett. **13**, 89 (1992).

- <sup>8</sup>Y. Maneglia and D. Bauza, ICMTS'99 (1999), p. 117.

- <sup>9</sup>E. H. Nicollian and R. R. Brews, MOS Physics and Technology (Wiley, New York, 1982).

- <sup>10</sup> M. Houssa, V. V. Afanas'ev, A. Stesmans, and M. M. Heyns, Semicond. Sci. Technol. 16, L93 (2001).

- <sup>11</sup> M. Houssa, A. Stesmans, R. J. Carter, and M. M. Heyns, Appl. Phys. Lett. 78, 3289 (2001).

- <sup>12</sup>F. B. McLean and G. A. Ausman, Phys. Rev. B 15, 1052 (1977).