#### A bit-accurate power estimation simulator for NoCs

Erwan Moréac, Johann Laurent, Pierre Bomel, André Rossi

#### ▶ To cite this version:

Erwan Moréac, Johann Laurent, Pierre Bomel, André Rossi. A bit-accurate power estimation simulator for NoCs. DATE 2017 Design Automation and Test in Europe, Mar 2017, Lausanne, Switzerland., Design Automation and Test in Europe. hal-01576044

HAL Id: hal-01576044

https://hal.science/hal-01576044

Submitted on 22 Aug 2017

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# A bit-accurate power estimation simulator for NoCs

Erwan Moréac, Johann Laurent, Pierre Bomel Lab-STICC, Université de Bretagne Sud, Lorient, France and André Rossi

LERIA, Université d'Angers, Angers, France

http://www.lab-sticc.fr

http://www.info.univ-angers.fr/leria

http://www.cnrs.fr

### Context

Complex many-cores and SoCs contain one (if not several) NoCs. NoC power consumption can represent a significant proportion (40%) of the overall power consumption.

# Power/energy challenges

Estimate NoC power consumption at system-level, and bit accurately, without the need for electrical simulations. "Is it possible to shorten the simulation and still get good estimations?"

Design and test new coding strategies to reduce power consumption on links.

"What is the energy impact at system-level?" "Is a single coding strategy always the best fit?" "What is a good set of coding strategies?"

Design space exploration of coding strategies. "Is it realistic in terms of simulation time and precision?

### Main idea

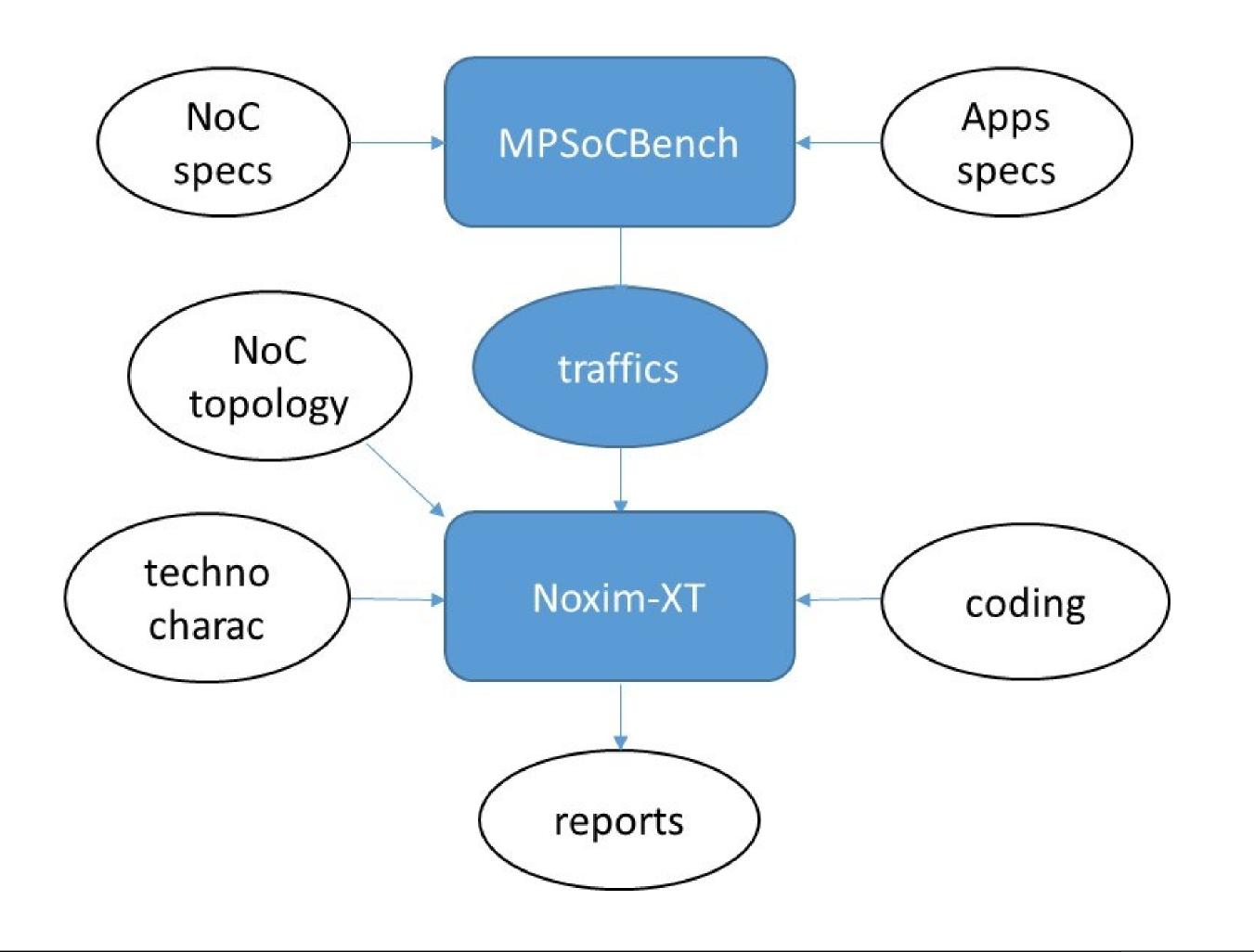

Enhance Noxim simulator and modify it to add a crosstalk-aware link power model moving towards better power estimation.

Noxim-XT

Use a SoC simulator to extract application traffics MPSoCBench

Design new coding strategies, and optionally use NoC's feedback

- coding styles: parallel, parsimonious, temporal shielding, ...

- selection strategies relying on NoC status

### Simulate with Noxim-XT

- estimate and extract power consumption

- check that application behavior is correct

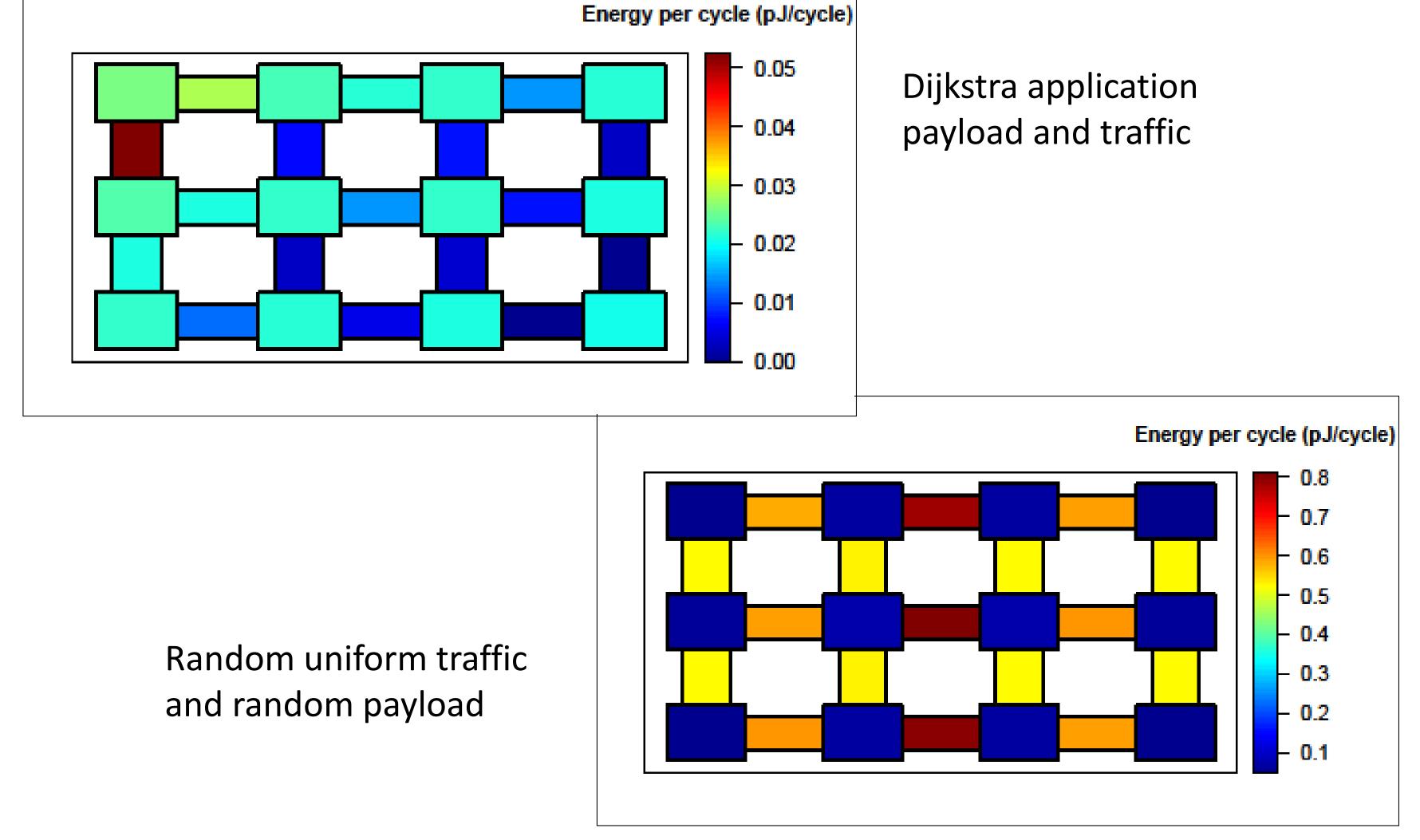

- test with various application traffics and with various codings

## Power consumption estimation tools flow

Packet injection rate = 0.012 flit/cycle/router

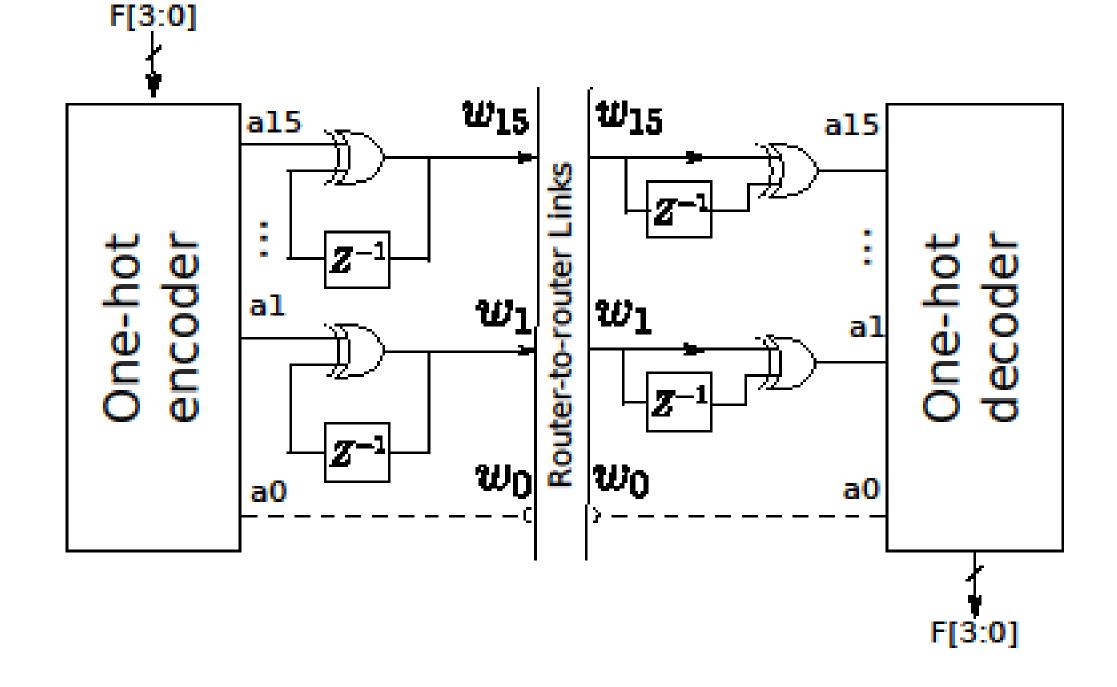

### **Encoder architecture**

Designed to be as small as possible:

- eliminates cross transitions

- reduces links activity

- but increases the flit transmission time

- ⇒Must be activated with parsimony

### Up to 35% of energy savings are possible for NoC Gains

# Applicability conditions

Need to characterize, for a given technology, the energy cost of transitions along a link.

Coding strategies have different impacts on power consumption and bandwidth and some can significantly reduce the power consumption of the NoC "raw" (no change), parsimonious, temporal shielding (we are open to the design and test of other coding strategies) Depending on the NoC's load, these new strategies can be applied, or not. Hence, a detection mechanism is necessary to enable them dynamically.

## Distance to the optimum and perspectives

Statistical study with video and random data has proven that our best shielding solutions (although very simple to implement) are as close as 95% to the optimal shielding. With the help of Dijkstra's shortest path applied to a power consumption graph, automatically build, we have observed that some optimal solutions need two successive shields, instead of one.