## IC-EMC User's Manual

Etienne Sicard, Alexandre Boyer

#### ▶ To cite this version:

Etienne Sicard, Alexandre Boyer. IC-EMC User's Manual. 2017. hal-01574395

## HAL Id: hal-01574395 https://hal.science/hal-01574395v1

Submitted on 14 Aug 2017

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# IC-EMC

## User's Manual

Version 2.9

www.ic-emc.org

Etienne SICARD

Alexandre BOYER

INSA Toulouse, France

June 2017

© Copyright INSA Toulouse France 2005-2017

INSA TOULOUSE, University of Toulouse France, 2017 INSA 2005-2011 135 Av de Rangueil 31077 Toulouse France

#### Download

- The software IC-EMC can be downloaded from www.ic-emc.org

#### **About the Authors**

Etienne SICARD was born in Paris, France, June 1961. He received the B.S degree in 1984 and the PhD in Electrical Engineering from the University of Toulouse, in 1987, in the laboratory LAAS of Toulouse. He was granted a Monbusho scholarship and stayed 18 months at Osaka University, Japan (1988-1989). Previously a professor of electronics in the Department of Physics, University of Balearic Islands, Spain (1990), Etienne SICARD is currently a professor at INSA of Toulouse, France, Department of Electrical and Computer Engineering. He is an associated researcher at IRIT, the Toulouse Institute of Computer Science Research. His research interests include several aspects of integrated circuits (ICs) for improved electromagnetic compatibility (EMC), and speech processing applied to speech therapy.

Email: etienne.sicard@insa-toulouse.fr

Web page: http://intranet-gei.insa-toulouse.fr/~sicard/

Alexandre Boyer was born in Annemasse, France, in 1981. He obtained Master degree in electrical engineering in 2004 and a PhD in Electronics from the Institut Nationale des Sciences Appliquées (INSA) in Toulouse, France, in 2004. He is currently an Assistant Professor in the Department of Electrical and Computer Engineering at INSA, Toulouse. He is also a member of the LAAS-CNRS research centre dedicated to the analysis of complex systems. His current research interests include EMC modeling at IC and PCB level. He has more than 10 years' experience in research into and training on the EMC of ICs.

Email: <u>alexandre.boyer@insa-toulouse.fr</u>

Web page: www.alexandre-boyer.fr

## **Table of Contents**

| I. Int  | [. Introduction                                                                     |         |  |  |

|---------|-------------------------------------------------------------------------------------|---------|--|--|

| II. G   | Setting started with IC-EMC                                                         | 12      |  |  |

| II.1    | Overview of the software                                                            | 12      |  |  |

| II.2    | Installing and running IC-EMC                                                       | 13      |  |  |

| II.2.1  | Download the Schematic Editor                                                       | 13      |  |  |

| II.2.2  | Download WinSPICE                                                                   | 14      |  |  |

| II.2.3  | Download LTSPICE                                                                    | 15      |  |  |

| II.2.4  | Initial Screen                                                                      | 15      |  |  |

| II.2.5  | Configure simulator options                                                         | 16      |  |  |

| II.3    | Using IC-EMC                                                                        | 17      |  |  |

| II.3.1  | Create my first model                                                               | 17      |  |  |

| II.3.2  | Save the schematic diagram                                                          | 21      |  |  |

| II.3.3  | Prepare the analysis                                                                | 21      |  |  |

| II.3.4  | Launch my first simulation                                                          | 22      |  |  |

| II.3.5  | Analysis result                                                                     | 24      |  |  |

| II.3.6  | Close IC-EMC                                                                        | 25      |  |  |

| III. V  | Vorking with IC-EMC                                                                 | 26      |  |  |

| III.1   | Simulation of the conducted emission of a microcontroller                           | 26      |  |  |

| III.1.1 | Open the example                                                                    | 26      |  |  |

| III.1.2 | Current Source Description                                                          | 28      |  |  |

| III.1.3 | Power supply Description                                                            | 29      |  |  |

| III.1.4 | Analysis Description                                                                | 29      |  |  |

| III.1.5 | Create the SPICE file                                                               | 30      |  |  |

| III.1.6 | Run SPICE Simulation                                                                | 30      |  |  |

| III.1.7 | Plot the transient waveform                                                         | 31      |  |  |

| III.1.8 | Emission simulation                                                                 | 32      |  |  |

| III.1.9 | Comparison with Measurements                                                        | 34      |  |  |

| III.2   | Impedance analysis of the power supply network of a circuit mounted in a 64 BGA pac | kage 35 |  |  |

| III.2.1 | Load the example                                                                    | 36      |  |  |

| III.2.2 | Impedance probe description                                                         | 37      |  |  |

| III.2.3 | Analysis description                                                                | 38      |  |  |

| III.2.4 | Run SPICE simulation                                                          | 38 |

|---------|-------------------------------------------------------------------------------|----|

| III.2.5 | Impedance analysis                                                            | 39 |

| III.2.6 | Comparison with measurement                                                   | 40 |

| III.3   | S parameter analysis for model construction of a bias tee                     | 41 |

| III.3.1 | Load the example                                                              | 42 |

| III.3.2 | S parameter probe description                                                 | 43 |

| III.3.3 | Analysis description                                                          | 45 |

| III.3.4 | Run SPICE simulation                                                          | 45 |

| III.3.5 | S parameter analysis                                                          | 45 |

| III.3.6 | Comparison with measurement                                                   | 47 |

| III.4   | Simulation of the conducted immunity on the power supply of a microcontroller | 47 |

| III.4.1 | Load the S parameter simulation model                                         | 47 |

| III.4.2 | Load the susceptibility simulation model                                      | 48 |

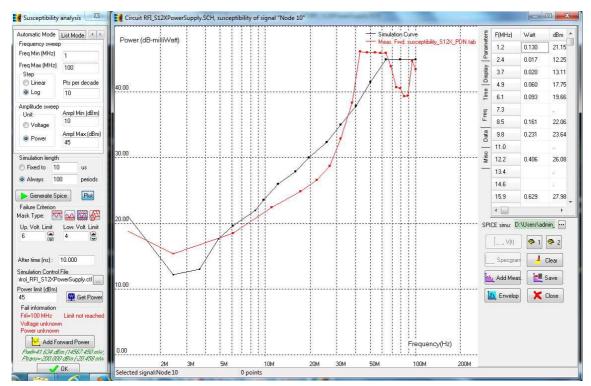

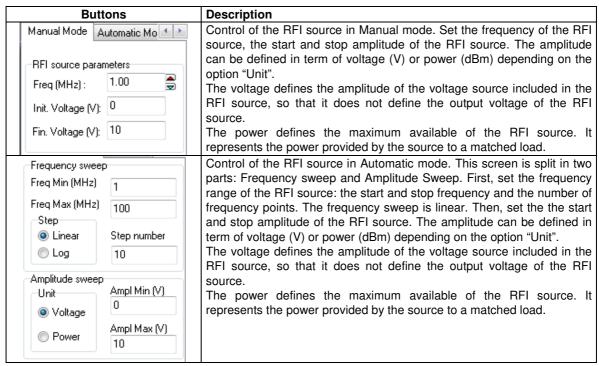

| III.4.3 | Configure the susceptibility simulation                                       | 50 |

| III.4.4 | Run SPICE simulation                                                          | 50 |

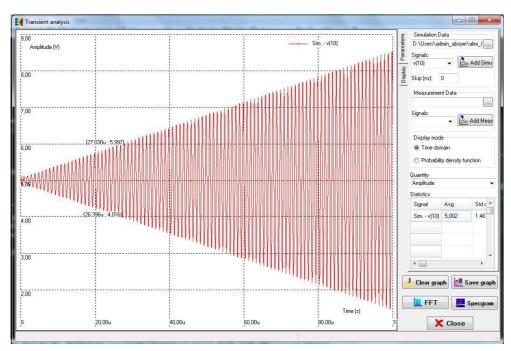

| III.4.5 | Observation of the output signal of the buffer                                | 51 |

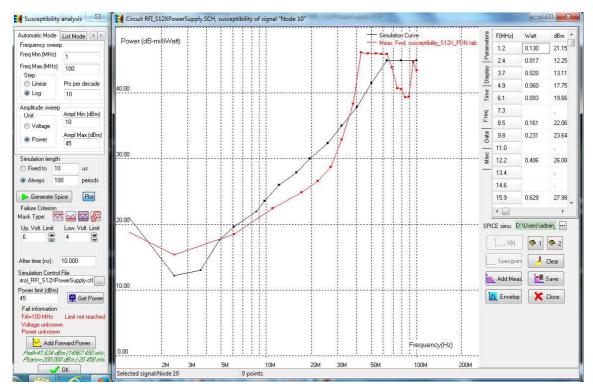

| III.4.6 | Susceptibility threshold extraction and comparison with measurement           | 52 |

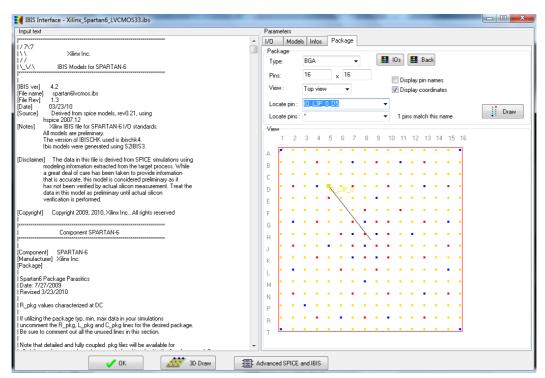

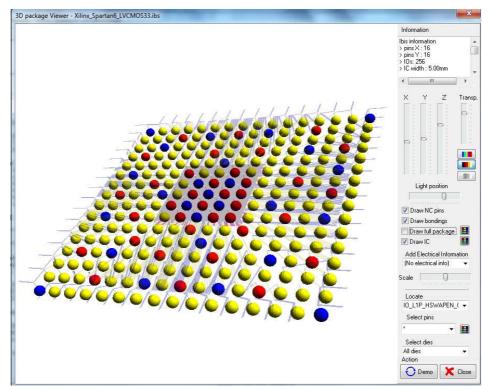

| III.5   | Load and analyze IBIS file                                                    | 53 |

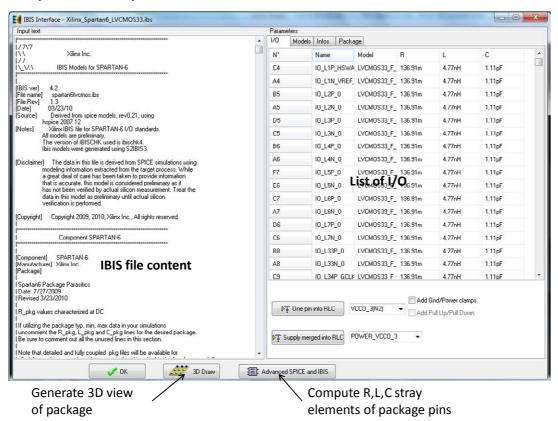

| III.5.1 | Load IBIS file                                                                | 53 |

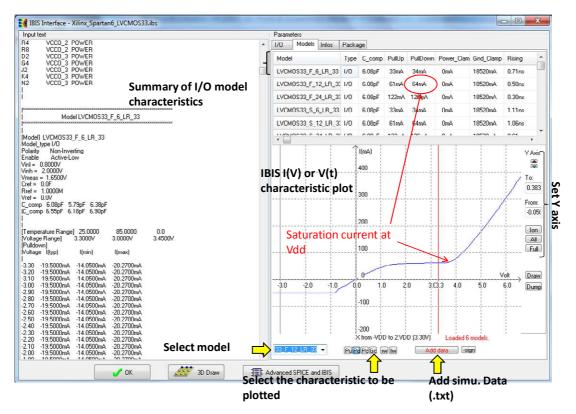

| III.5.2 | Plot I/O characteristics                                                      | 55 |

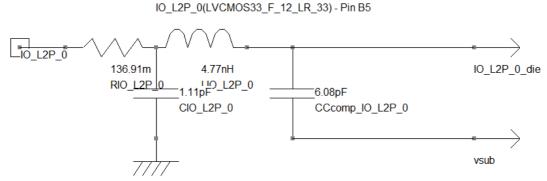

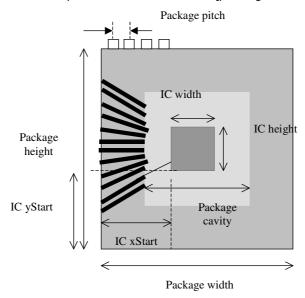

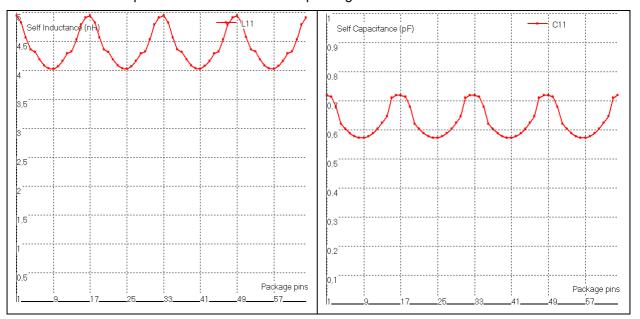

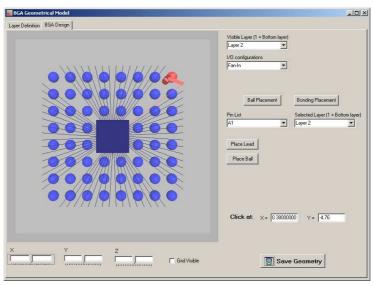

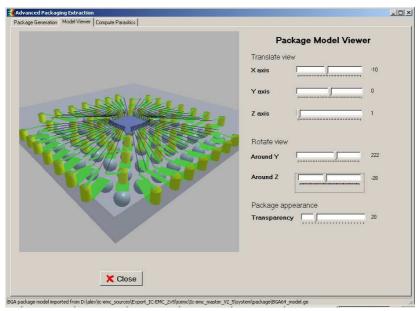

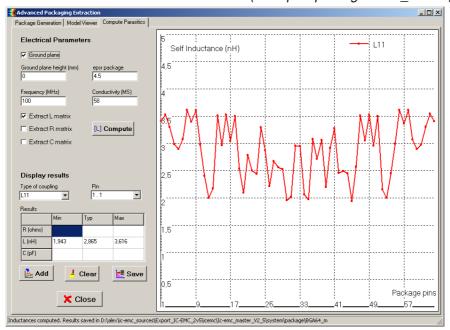

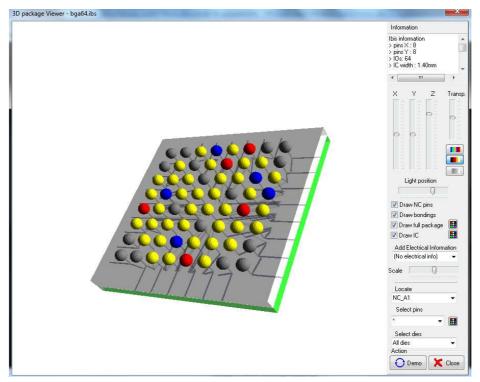

| III.5.3 | Package viewer                                                                | 56 |

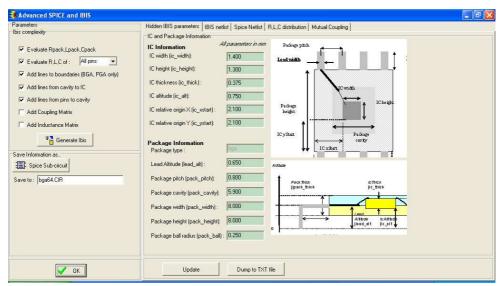

| III.5.4 | Package modeling                                                              | 59 |

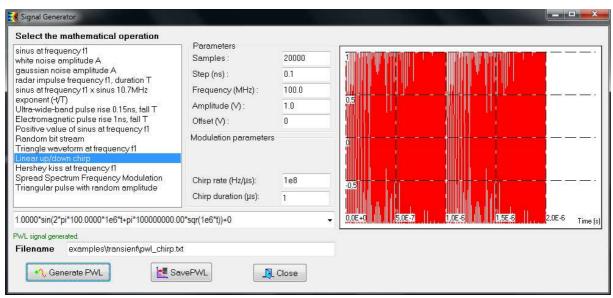

| III.6   | Transient signal analysis                                                     | 59 |

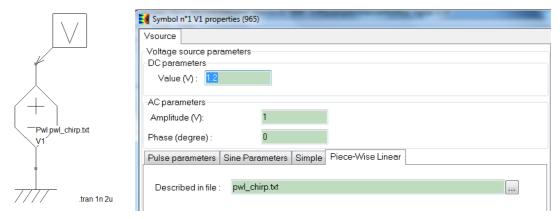

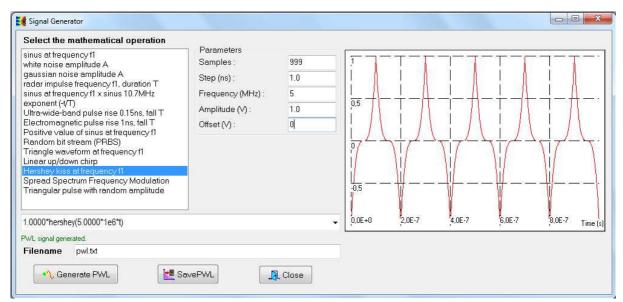

| III.6.1 | Signal generation                                                             | 59 |

| III.6.2 | Create the model                                                              | 61 |

| III.6.3 | Run SPICE simulation                                                          | 62 |

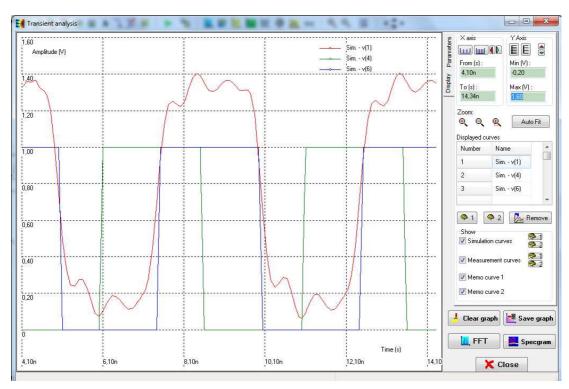

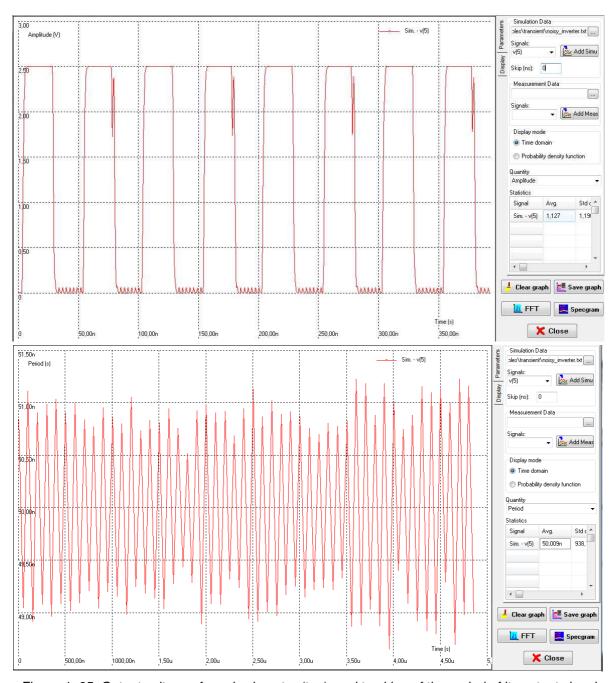

| III.6.4 | Observe the time-domain waveform                                              | 62 |

| III.6.5 | Analysis of the instantaneous frequency of the signal                         | 63 |

| III.6.6 | Spectrogram                                                                   | 65 |

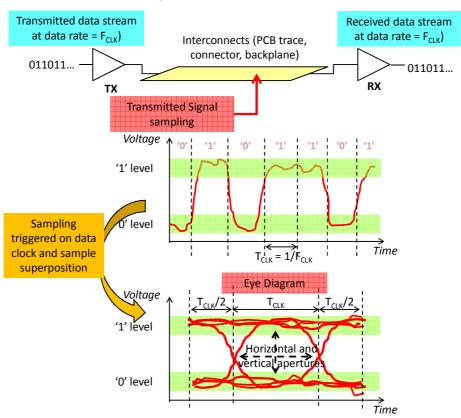

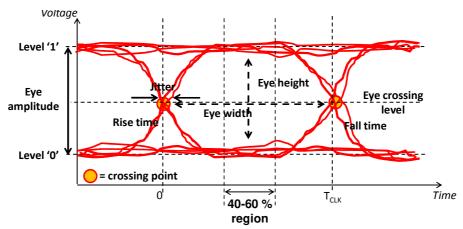

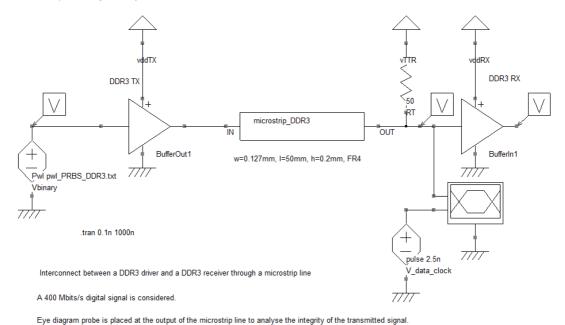

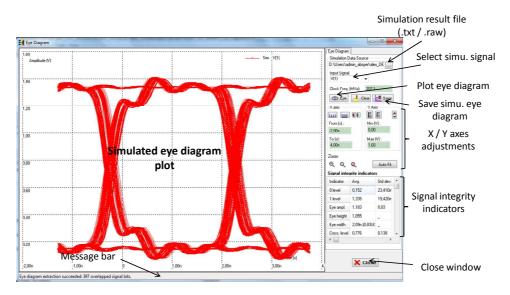

| III.7   | Plot an eye diagram                                                           | 66 |

| III.7.1 | Eye diagram                                                                   | 66 |

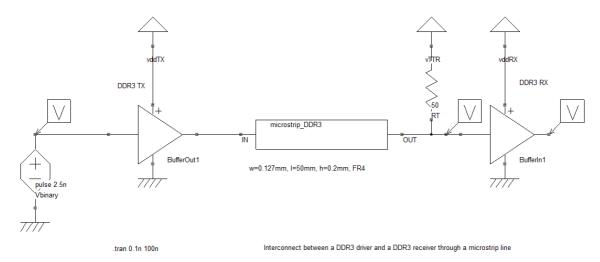

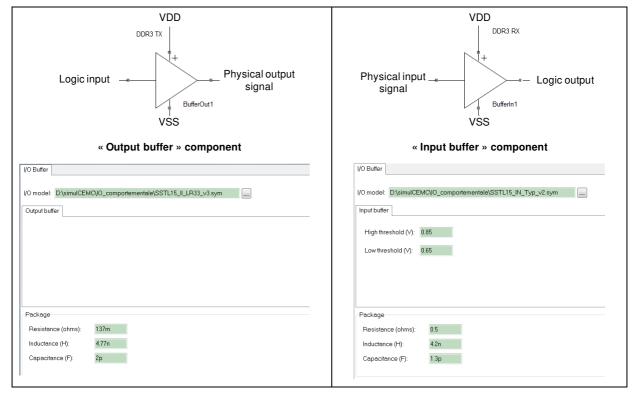

| III.7.2 | Load the example: DDR3 memory link                                            | 68 |

| III.7.3 | Eye diagram probe                                                             | 71 |

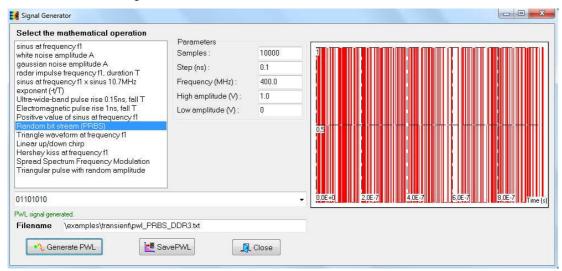

| III.7.4 | PRBS source                                                                   | 72 |

| III.7.5 | Plot the eye diagram                                                          | 73 |

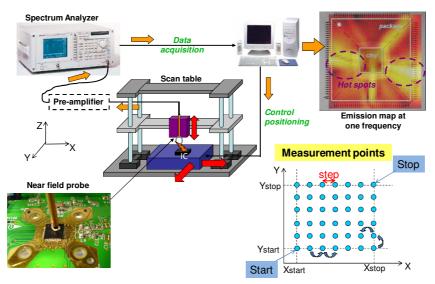

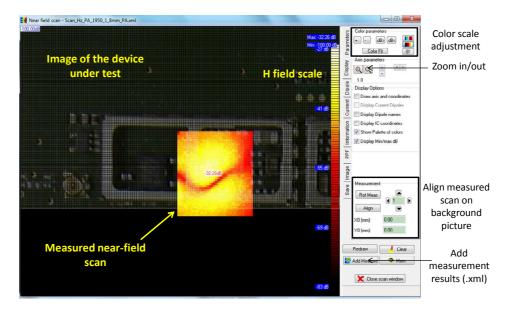

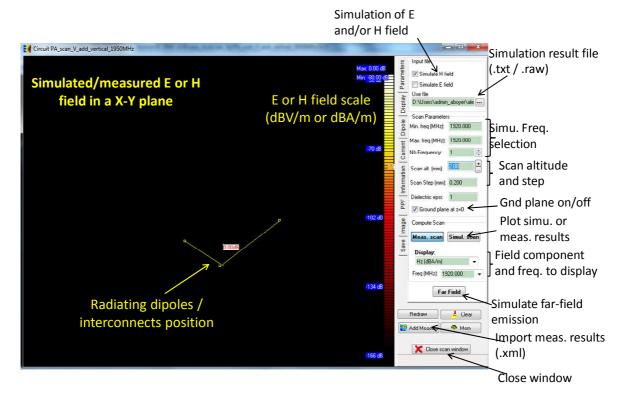

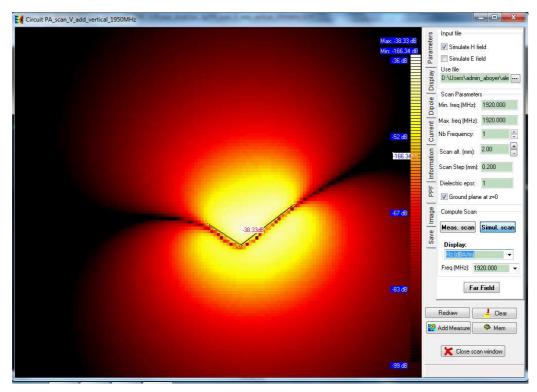

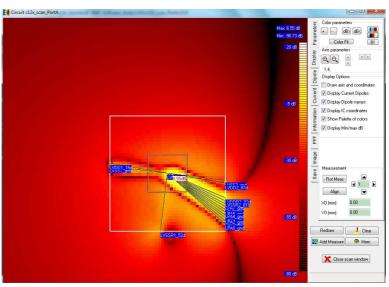

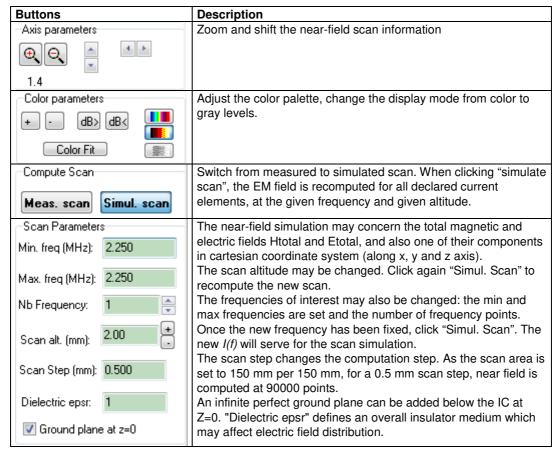

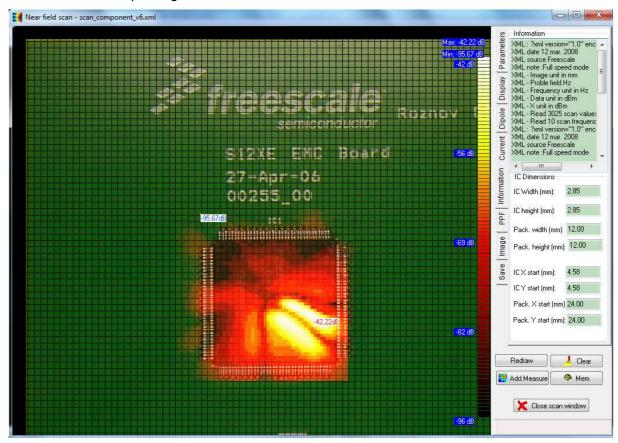

| III.8   | Near-field analysis                                                           | 74 |

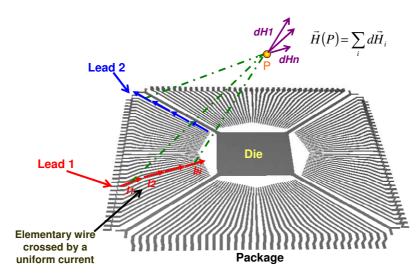

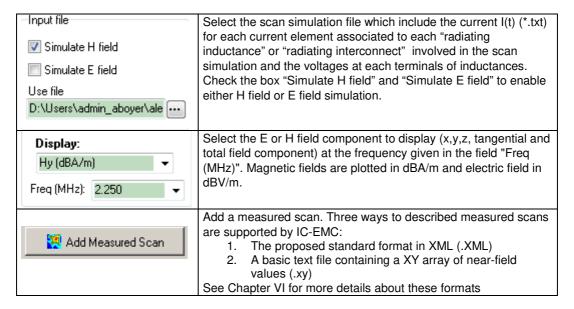

| III.8.1 | Near-field scan measurement principles                                        | 75 |

| III.8.2 | Plotting near-field scan measurement with IC-EMC                              | 75 |

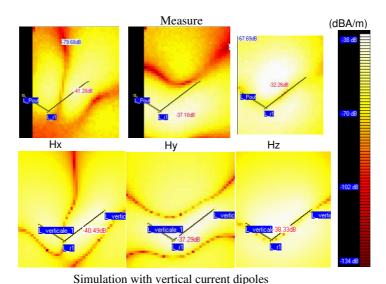

| III.8.3 | Simulating near-field emission with IC-EMC        | 77  |

|---------|---------------------------------------------------|-----|

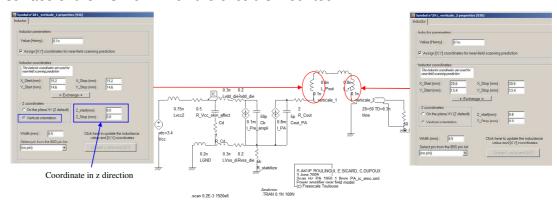

| III.8.4 | Near-Field Prediction                             | 81  |

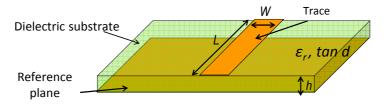

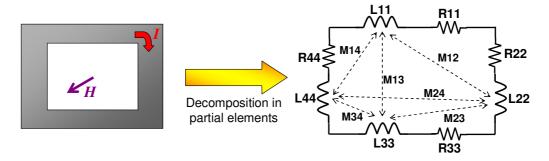

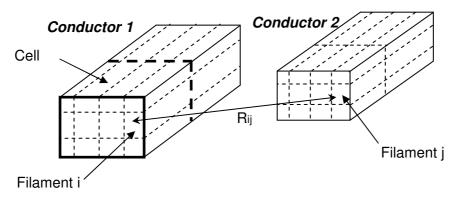

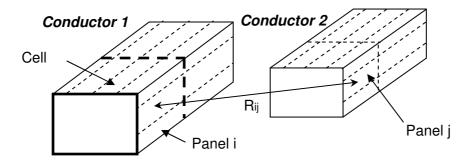

| III.9   | Interconnect modeling                             | 86  |

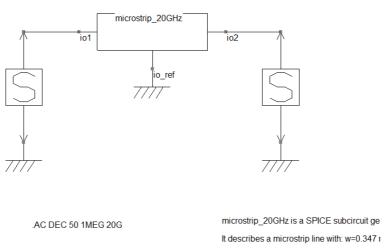

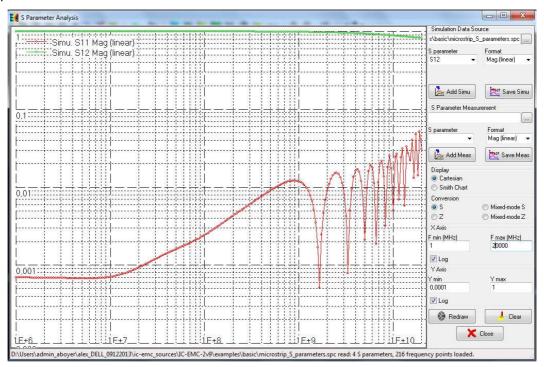

| III.9.1 | Modeling a microstrip line designed on a FR4 PCB  | 86  |

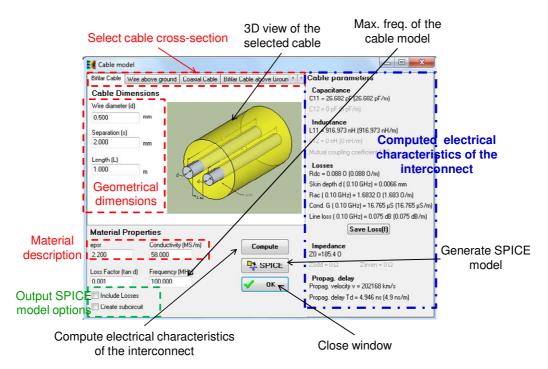

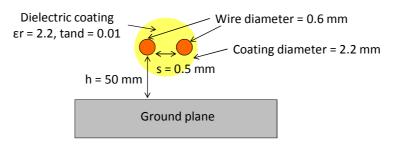

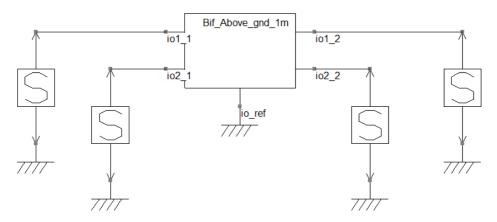

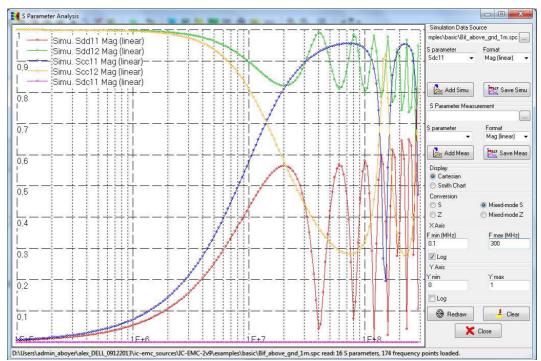

| III.9.2 | Cable modeling                                    | 91  |

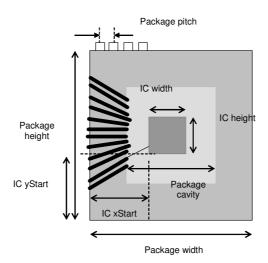

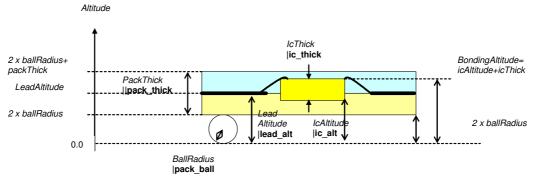

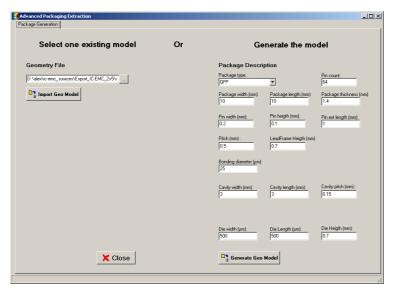

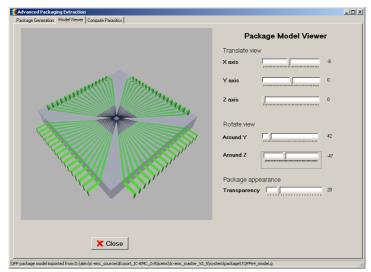

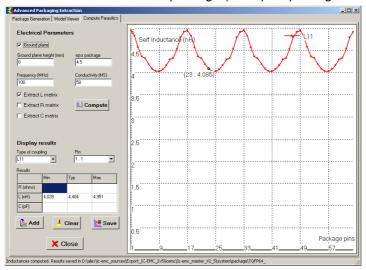

| III.9.3 | Package modeling                                  | 96  |

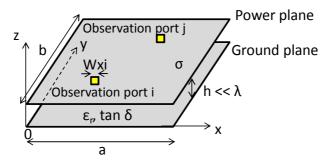

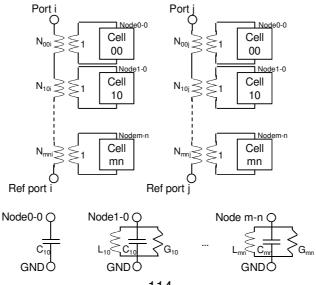

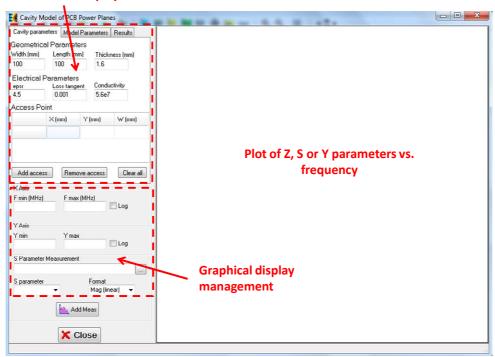

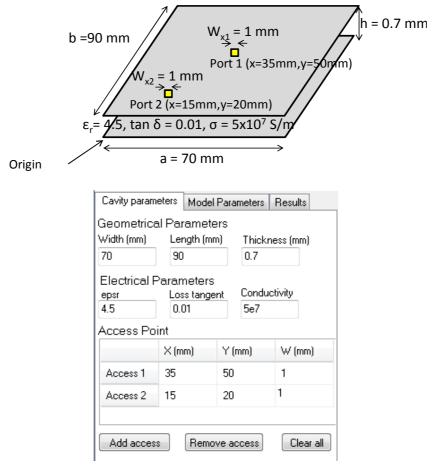

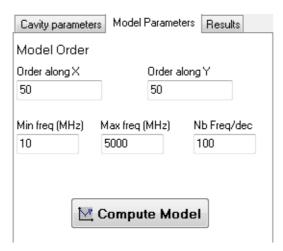

| III.9.4 | Modeling of a rectangular power-ground plane pair | 113 |

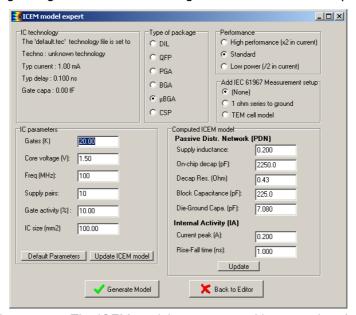

| III.10  | ICEM model expert                                 | 118 |

| III.11  | References                                        | 119 |

|         |                                                   |     |

|         | escription of the menus                           |     |

| IV.1    | Overview of the menus                             |     |

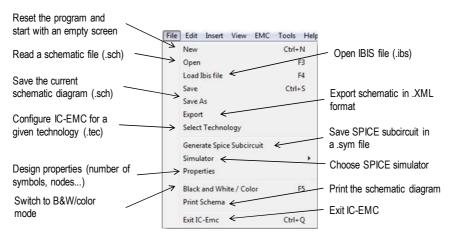

| IV.2    | Detailed commands of the menu File                | 122 |

| IV.2.1  | New $(CTRL + N)$                                  | 122 |

| IV.2.2  | Open (F3)                                         | 122 |

| IV.2.3  | Load Ibis File (F4)                               | 122 |

| IV.2.4  | Save (CTRL+S), Save As                            | 123 |

| IV.2.5  | Export                                            | 123 |

| IV.2.6  | Select Technology                                 | 124 |

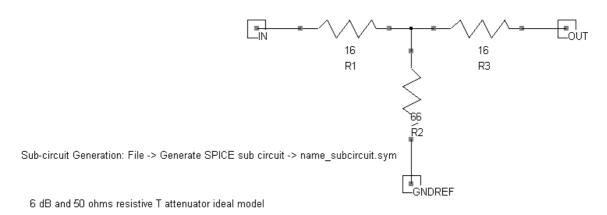

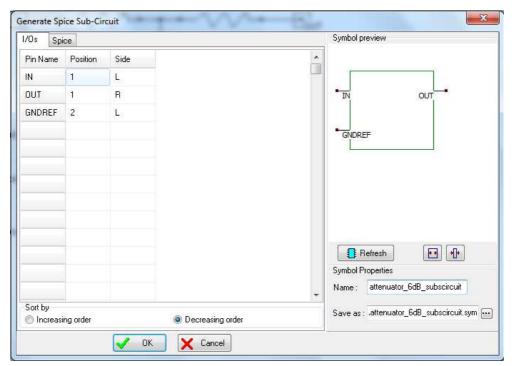

| IV.2.7  | Generate SPICE sub-circuit                        | 124 |

| IV.2.8  | Simulator                                         | 125 |

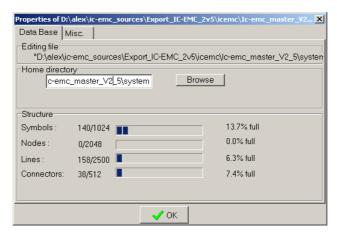

| IV.2.9  | Properties                                        | 126 |

| IV.2.10 | Black and White /Color (F5)                       | 126 |

| IV.2.1  | Print Schema                                      | 127 |

| IV.2.12 | 2 Exit IC-EMC (CTRL+Q)                            | 127 |

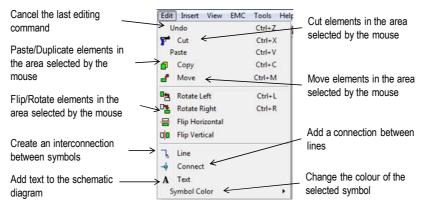

| IV.3    | Detailed commands of Menu Edit                    | 127 |

| IV.3.1  | Undo (CTRL+Z)                                     | 127 |

| IV.3.2  | Cut (CTRL+X)                                      | 127 |

| IV.3.3  | Paste (CTRL+V)                                    | 127 |

| IV.3.4  | Copy (CTRL+C)                                     | 128 |

| IV.3.5  | Move (CTRL+M)                                     | 128 |

| IV.3.6  | Rotate (CTRL+R or CTRL+L)                         | 128 |

| IV.3.7  | Flip Vertical/Horizontal                          | 128 |

| IV.3.8  | Line                                              | 128 |

| IV.3.9  | Connect                                           | 129 |

| IV.3.10 | ) Text                                            | 129 |

| IV.3.1  | Symbol Color                                      | 130 |

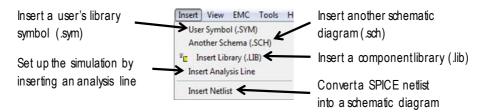

| IV.4    | Detailed commands of Menu Insert                  | 130 |

| IV.4.1  | Insert User Symbol (.SYM)         | 130 |

|---------|-----------------------------------|-----|

| IV.4.2  | Insert another Schema (.SCH)      | 131 |

| IV.4.3  | Insert Lib .LIB)                  | 131 |

| IV.4.4  | Insert Analysis Line              | 131 |

| IV.4.5  | Insert Netlist                    | 132 |

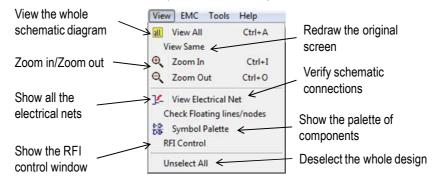

| IV.5    | Detailed commands of Menu View    | 133 |

| IV.5.1  | View All (CTRL+A)                 | 133 |

| IV.5.2  | View Same                         | 133 |

| IV.5.3  | Zoom In & Out (CTRL+I and CTRL+O) | 133 |

| IV.5.4  | View Electrical Net               | 133 |

| IV.5.5  | Check Floating Lines / Nodes      | 133 |

| IV.5.6  | Symbol Library                    | 134 |

| IV.5.7  | RFI control                       | 134 |

| IV.5.8  | Unselect All (Escape Key)         | 134 |

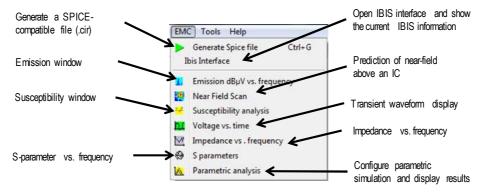

| IV.6    | Detailed commands of Menu EMC     | 134 |

| IV.6.1  | Generate SPICE File (CTRL+G)      | 134 |

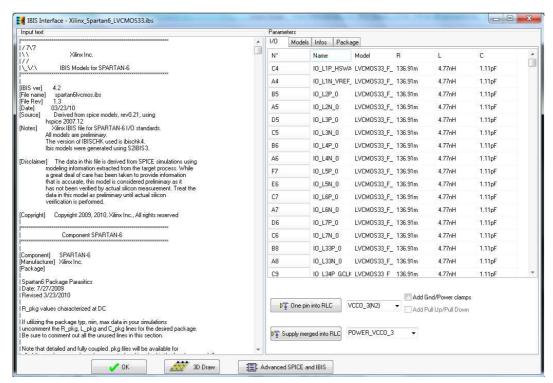

| IV.6.2  | Ibis Interface                    | 135 |

| IV.6.3  | Emission vs. frequency            | 138 |

| IV.6.4  | Near-field scan                   | 143 |

| IV.6.5  | Susceptibility dBm vs. Frequency  | 145 |

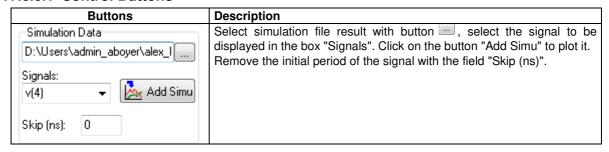

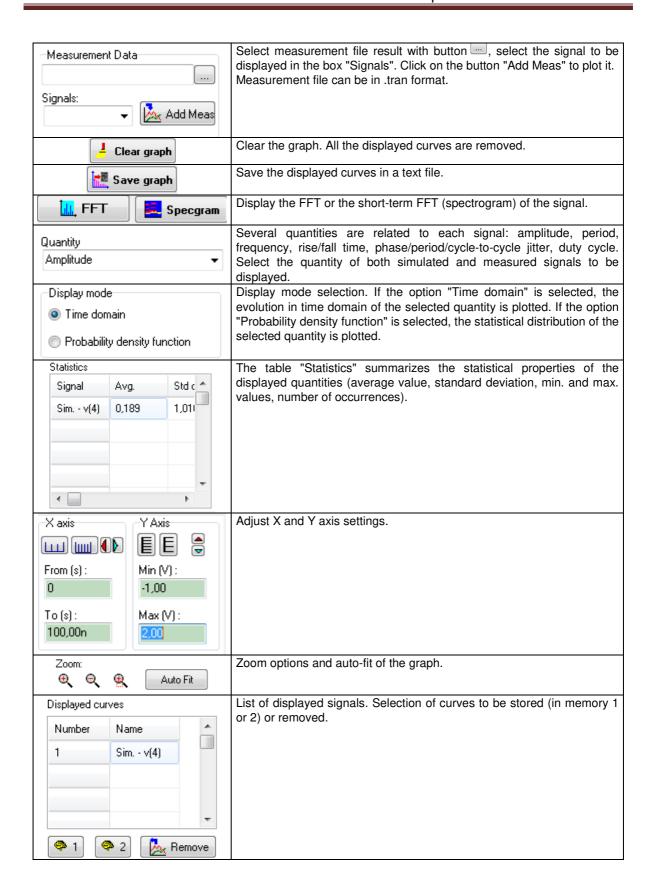

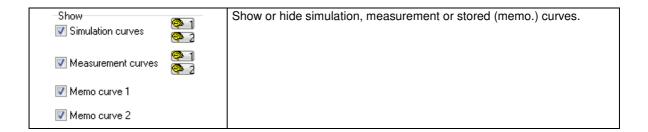

| IV.6.6  | Voltage Versus Time               | 148 |

| IV.6.7  | Impedance vs. Frequency           | 152 |

| IV.6.8  | S parameter analysis              | 154 |

| IV.6.9  | Parametric analysis               | 156 |

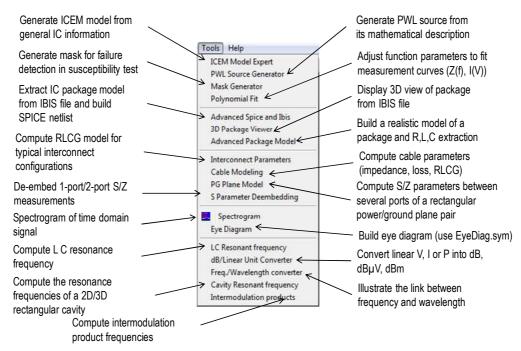

| IV.7 I  | Detailed commands of Menu Tools   | 158 |

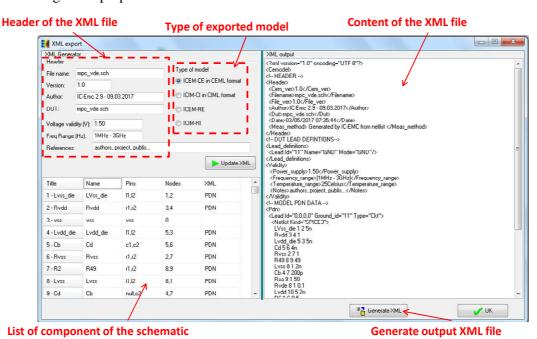

| IV.7.1  | ICEM Model Expert                 | 158 |

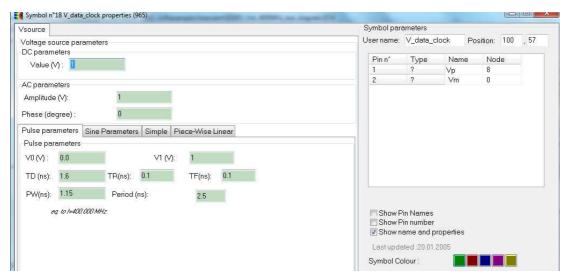

| IV.7.2  | PWL Source Generator              | 160 |

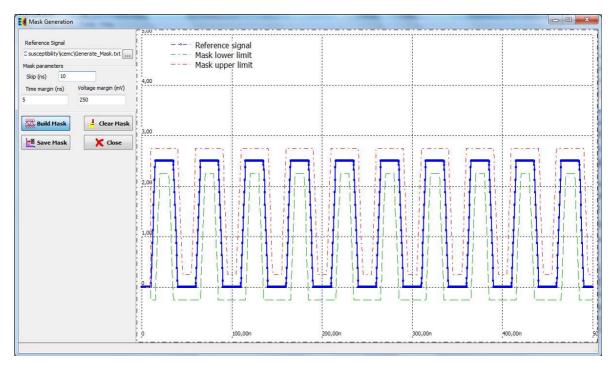

| IV.7.3  | Mask generator                    | 162 |

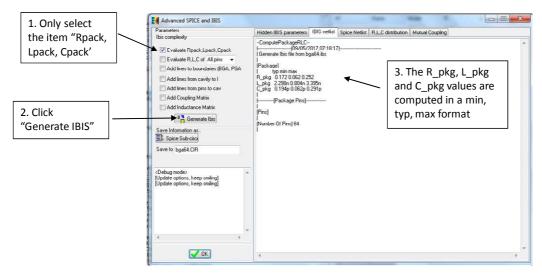

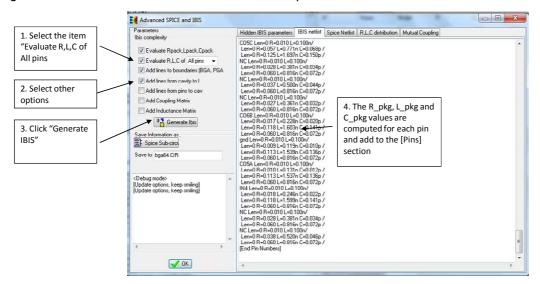

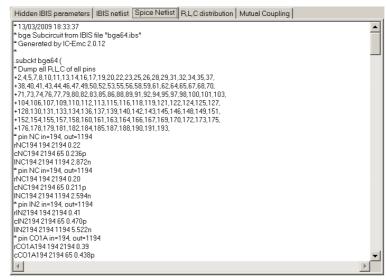

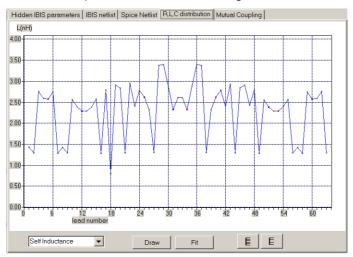

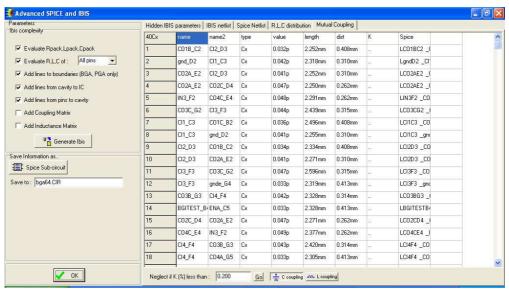

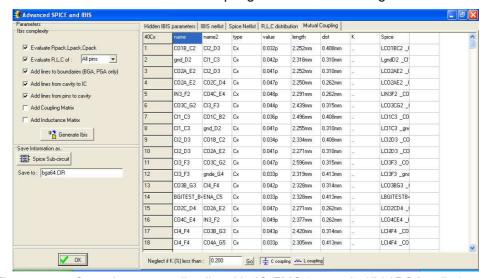

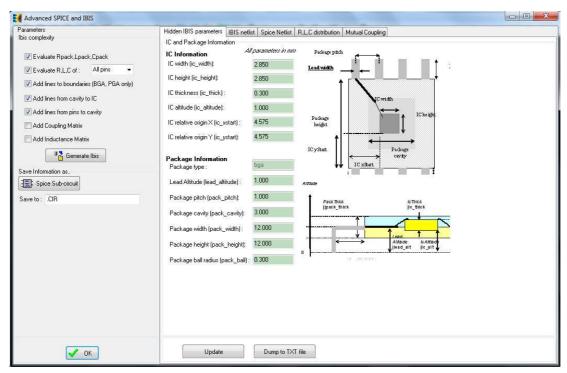

| IV.7.4  | Advanced Spice & Ibis             | 163 |

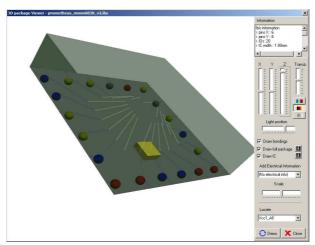

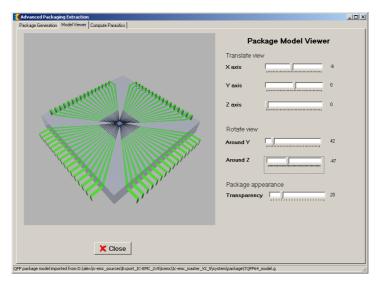

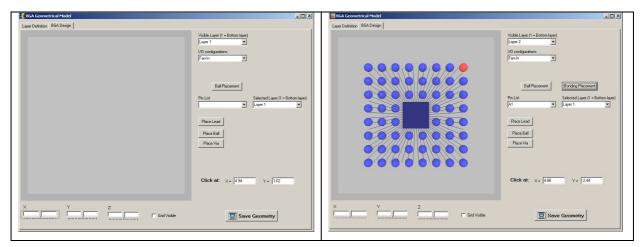

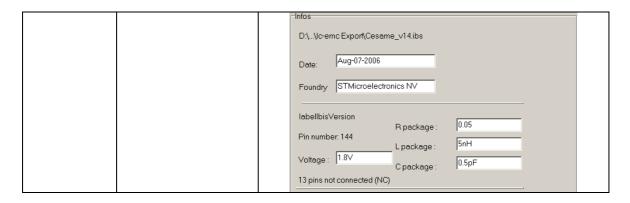

| IV.7.5  | 3D-Package Viewer                 | 164 |

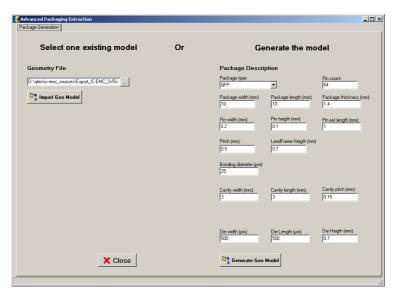

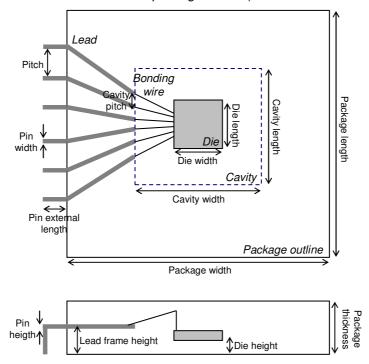

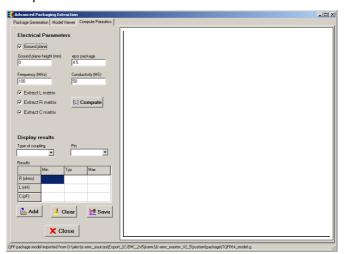

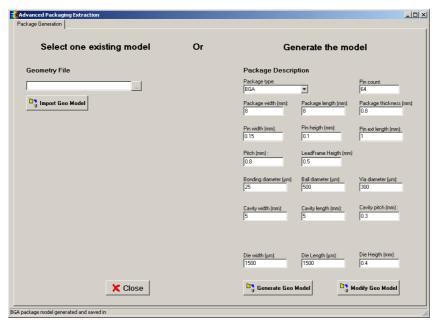

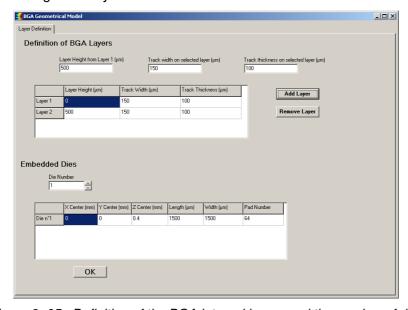

| IV.7.6  | Advanced Package Model            | 165 |

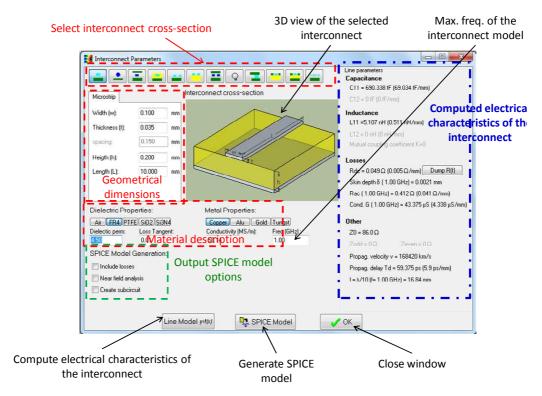

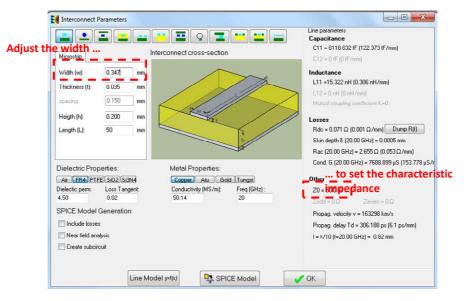

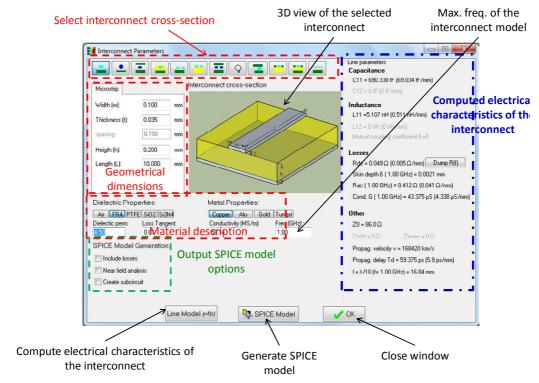

| IV.7.7  | Interconnect Parameters           | 167 |

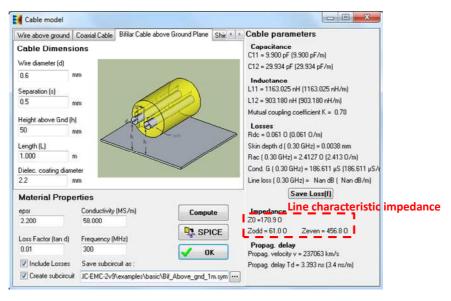

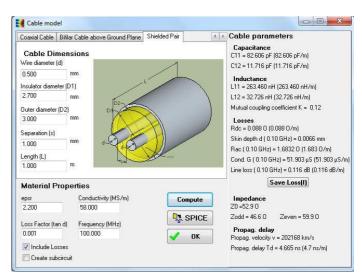

| IV.7.8  | Cable modeling                    | 169 |

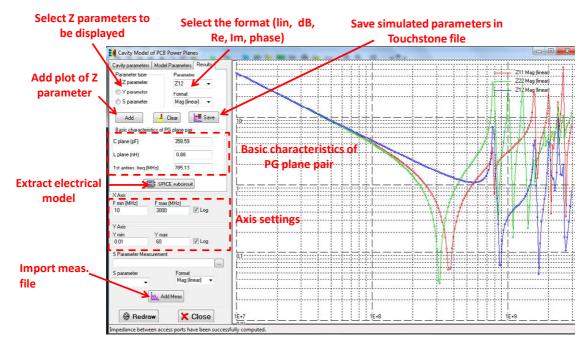

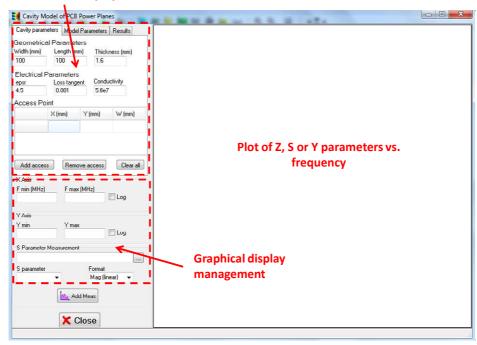

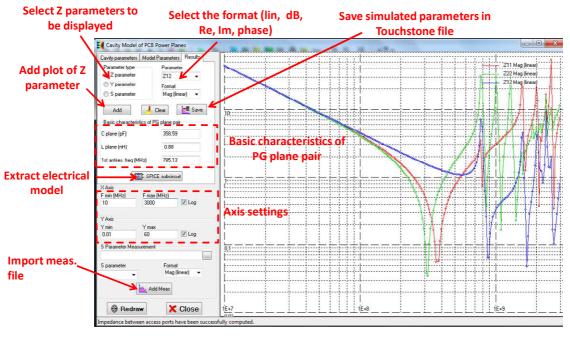

| IV.7.9  | PG Plane Model                    | 169 |

| IV.7.10 | S parameter de-embedding          | 171 |

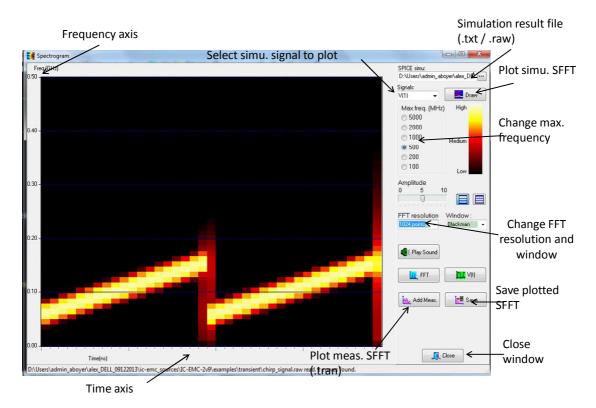

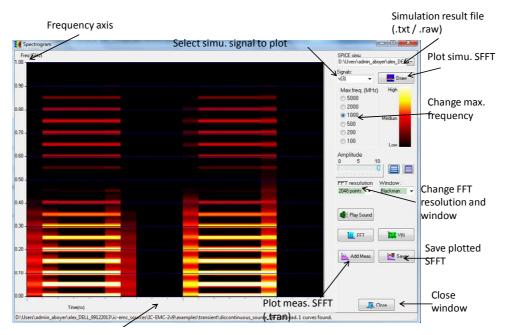

| IV.7.11 | Spectrogram                       | 173 |

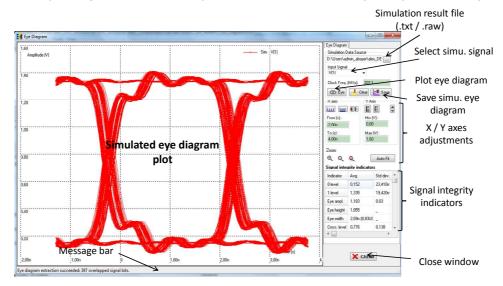

| IV.7.12 | Eye Diagram                       | 175 |

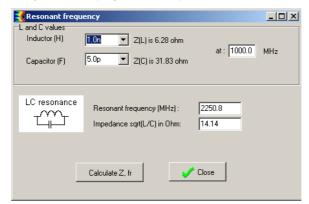

| IV.7.13 | LC Resonant Frequency             | 176 |

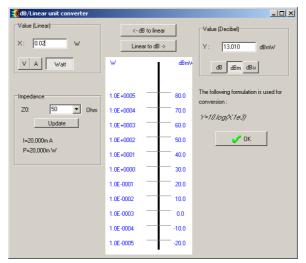

| IV.7 | 7.14 | dB/Linear Unit Converter                                   | 176 |

|------|------|------------------------------------------------------------|-----|

| IV.7 | 7.15 | Frequency/Wavelength Converter                             | 177 |

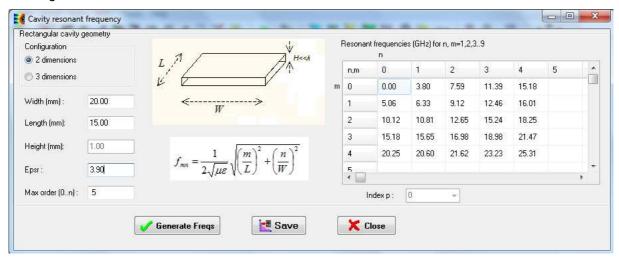

| IV.7 | 7.16 | Cavity Resonant Frequency                                  | 177 |

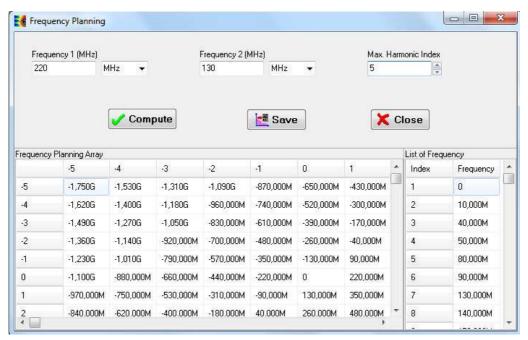

| IV.7 | 7.17 | Intermodulation products                                   | 179 |

| V.   | Des  | scription of the symbols                                   | 181 |

| V.1  | Con  | nponents of the Symbol Palette                             | 181 |

| V.2  | Con  | nponents in the subdirectory ieee                          | 183 |

| VI.  | Inp  | ut/output file format                                      | 185 |

| VI.1 | T    | AB File Format                                             | 185 |

| VI.2 | Z    | Format                                                     | 185 |

| VI.3 | T    | ouchstone file – SnP                                       | 185 |

| VI.4 | F    | ile .tran                                                  | 187 |

| VI.5 | .3   | XY format for near-field scan measurement results exchange | 188 |

| VI.6 | X    | ML Near-field Scan Standard implementation in IC-EMC       | 188 |

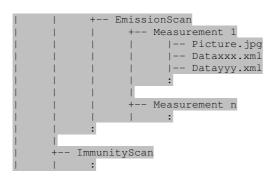

| VI.6 | 5.1  | Principles                                                 | 189 |

| VI.6 | 5.2  | XML format in IC-EMC                                       | 190 |

| VI.6 | 5.3  | Remarks about the implementation of XML in IC-EMC          | 191 |

| VI.6 | 5.4  | Notes                                                      | 192 |

| VI.6 | 5.5  | Remarks about the hierarchy description                    | 192 |

| VI.7 | T    | echno file .tec                                            | 193 |

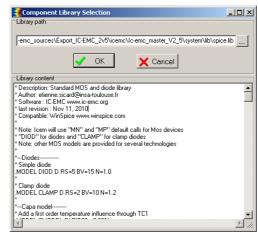

| VI.8 | L    | ibrary file .lib                                           | 194 |

### I. Introduction

This manual document describes the tool IC-EMC (acronym for Integrated Circuit Electromagnetic Compatibility) which aims at simulating parasitic emission and susceptibility of integrated circuits and eases the comparison with measurements. The tool uses the simulators WinSpice and LTSPICE® for SPICE simulation. The software can be downloaded on www.ic-emc.org.

IC-EMC is a free simulation software entirely dedicated to the EMC of ICs issues. IC-EMC is not geared to full-chip simulation coupled with a 3D electromagnetic solver and is not intended to address complex EM problems. It aims at developing simple models of ICs and its surrounding environment (IC package, PCB traces, cables) for simulation of emission, susceptibility and signal integrity. Its purpose is twofold:

- help the user to develop EMC models rapidly for an efficient evaluation of EMC performances

- illustrate EMC issues related to ICs for educational purpose of basic notions and modelling techniques related to EMC

To obtain more accuracy or to address more complex problems, we advise you to use the professional CAD tools available in your university, lab or company

This manual is organized as follows:

- The second section (Getting started) presents an overview of the software and describe how to install and launch it

- The third section (Working with IC-EMC) shows the different possibilities of the software through several practical examples

- The fourth section (Description of the menu) describes the different menus of the software

- The fifth section (Description of the symbols) lists all the symbols proposed by the software to build electrical schematic diagram

- The sixth section (Input/output file format) describes the different exchange files used by the software

The authors have dedicated around ten years to build the technical contents of this manual and software, and tried their best to improve the IC-EMC tool, trying to keep the usage simple. As the tool is in constant evolution, we encourage the reader to download the updated version of IC-EMC form the web page and we would appreciate feedback and comments.

### **Acknowledgements**

We would like to thank partners from the Medea+ "Parachute" and Pidea+ "EMCPack" European project for invaluable help in EMC expertise at integrated circuit level. The tools have benefited from the real-case experiments conducted in partnership with ST-Microelectronics Grenoble, France, Freescale Semiconductors, Toulouse, France, Infineon, Munich, Germany, Valeo Créteil, France, and Atmel Nantes France. The development of IC-EMC version 2.5 has also been supported by Aerospace Valley project EPEA.

We wish to warmly acknowledge all our former PhD students who developed numerous case studies presented in this manual: Bertrand Vrignon, Enrique Lamoureux, Cécile Labussière, Samuel Akue Boulingui, Céline Dupoux, Mickael Deobarro, Amadou Cisse Ndoye, Bihong Li, He Huang, Laurent Guibert, Veljko Tomasevic and Chaimae Ghfiri. We would also like to thank Sonia Ben Dhia and Sebastien Serpaud for their positive support and constructive remarks about IC-EMC, together with all our colleagues in the area of electromagnetic compatibility of integrated circuits who inspired us through fruitful discussions and collaborative research.

Our thanks too to all the research project leaders who co-funded our research, contributed to the development and the improvement of IC-EMC (MEDEA, EPEA, SEISME, ANR, IRT Saint-Exupéry and European program Erasmus+ Knowledge Alliance - MicroElectronics Cloud Alliance).

Toulouse, June 21, 2017

Alexandre Boyer, Etienne Sicard

## II. Getting started with IC-EMC

IC-EMC is a simulation software entirely dedicated to the EMC of ICs issues. It works only with Windows Vista and Windows 7 or 10. IC-EMC is a schematic editor interfaced with two SPICE simulators: WinSPICE and LTSPICE. By exploiting simulation results provided by these simulators, IC-EMC proposes a set of post-processing tools to extract relevant EMC information. The section aims at presenting an overview of the software and how to install and launch it.

#### II.1 Overview of the software

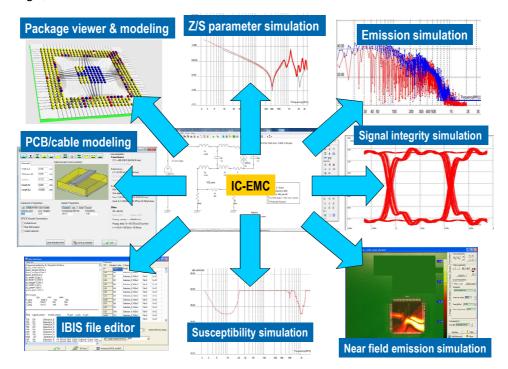

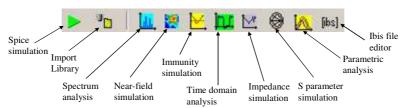

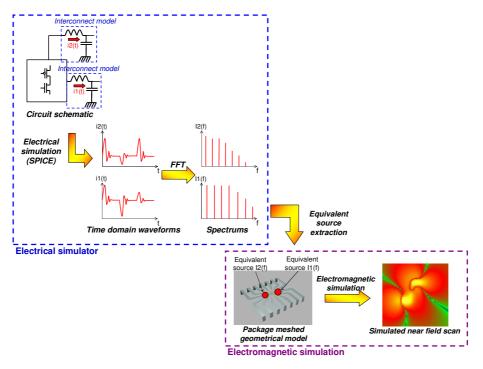

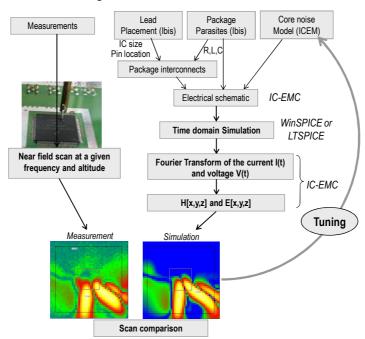

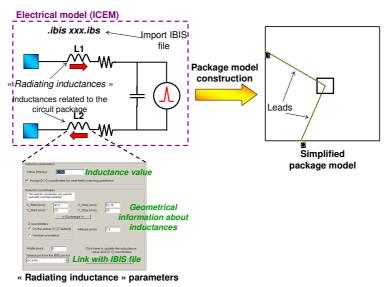

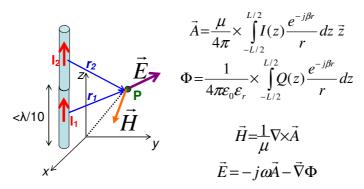

The tool IC-EMC is able to perform comparisons between measurements and simulation of conducted, radiated emission, near-field emission, S and Z parameters, immunity and signal integrity, as illustrated in Figure 2- 1. Moreover, it includes also different tools to build models of IC package, PCB traces and cables.

Figure 2- 1: Main features of IC-EMC

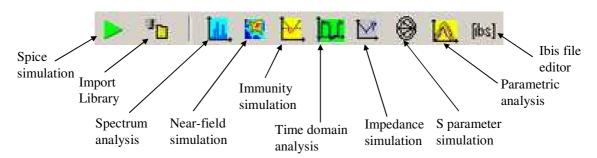

The main commands of IC-EMC are shown in Figure 2- 2. From left to right, the Spice Simulation icon translates the schematic diagram into a SPICE compatible text file, the next icons give access to the emission spectrum window, the impedance vs. frequency, the immunity simulation screen, and the near-field simulation screen.

Figure 2- 2: Main commands proposed by -EMC

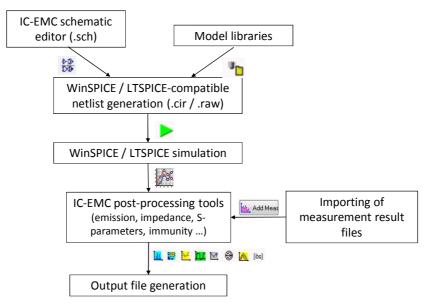

Figure 2- 3 describes the general simulation flow with IC-EMC. The process starts with the edition of the circuit schematic. Component models are provided by IC-EMC or external libraries. The netlist file generated by IC-EMC serves as input file for the SPICE simulator (WinSPICE or LTSPICE). At the end of the simulation, SPICE simulation results are exploited by IC-EMC post-processing tools. Different measurement file formats can be imported to compare simulation and measurement results and tune simulation models.

Figure 2- 3: General simulation flow with IC-EMC

## II.2 Installing and running IC-EMC

The following paragraphs detail the different steps for installing, running and exiting the software.

#### II.2.1 Download the Schematic Editor

The software can be downloaded from www.ic-emc.org. The zip file contains an executable file (icemc.exe) and folders containing libraries and examples.

After downloading and unzipping the IC-EMC software package, a main directory called "IC-EMC-2v9" is displayed. This directory contains a list of subdirectories organised as shown in Figure 2- 4.

It contains the IC-EMC executable file (ic\_emc.exe) and a further collection of subdirectories. Some of them contain examples and case studies, while others contain component libraries. Their content is briefly described in Table 2-1.

Figure 2- 4: Organisation of the main directory IC-EMC-2V9

| Subdirectory name | Contents                                                                                                                                                                                                                                                 |  |  |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| book              | The subdirectory contains the schematic diagrams and measurement results presented in the book: A. Boyer, E. Sicard, "Basis of Electromagnetic Compatibility of Integrated Circuits", Collection Pour l'Ingénieur, Presses Universitaires du Midi, 2017. |  |  |

| case_study        | The subdirectory contains schematic diagrams and measurement results related to several case studies described on the website www.ic-emc.org                                                                                                             |  |  |

| examples          | The subdirectory contains various schematic diagram related to basic notions of EMC, emission, near-field, susceptibility                                                                                                                                |  |  |

| help              | HTML pages of online help                                                                                                                                                                                                                                |  |  |

| ieee              | Symbol library used by IC-EMC (*.sym). Some are available from the palette (see 11.2.7), while others can be downloaded by clicking on "Insert → User Symbol (.SYM)".                                                                                    |  |  |

| lib               | .tec file and default non-linear device SPICE library (.lib) (e.g. a diode, BJT, CMOS transistor, non-linear capacitor, switch)                                                                                                                          |  |  |

Table 2- 1: Content of the subdirectories of the main directory IC-EMC-2v9

#### II.2.2 Download WinSPICE

The WinSPICE analogue simulation tool may be downloaded from www.winspice.com. Click

on the icon to run the WinSPICE solver wspice3.exe. It is necessary to define in IC-EMC the access path of the solver wspice3 (see II.2.5).

#### II.2.3 Download LTSPICE

The LTSPICE simulation tool may be downloaded from

http://www.linear.com/designtools/software/. Click on the icon to run the WinSPICE solver scad3.exe. It is necessary to define in IC-EMC the access path of the solver scad3 (see II.2.5).

#### II.2.4 Initial Screen

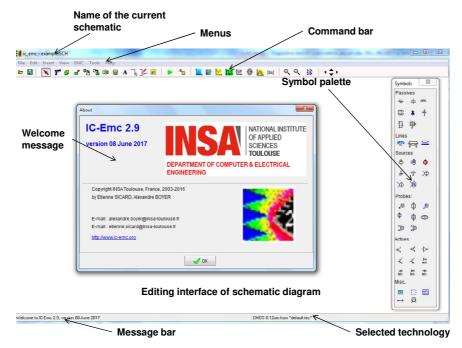

To launch IC-EMC, double-click on executable file ic\_emc.exe in the main directory of IC-EMC. The following figure presents the interface when the software opens. The editor contains a palette of symbols (Window "Symbols" situated on the right of the screen) and some basic editing icons to build the schematic diagram of the circuit and control the main EMC screens.

Figure 2- 5: IC-EMC user interface

The symbol palette gives access to the most common elements of electrical schematics, such as passive devices, voltage and current sources, transmission lines and interconnects, measurement probes for voltage, current, impedance, power, S-parameters etc., in addition to diodes, MOS devices, bipolar junction transistors and input/output buffer models extracted from an IBIS file. The components of the symbol palette are described in **Erreur! Source du renvoi introuvable.** The palette is visible as soon as IC-EMC is run. If the palette is closed accidentally, it can be reopened by clicking on "View > Symbol Palette" or clicking on the icon in the command bar.

All the components placed on schematic diagrams are described in a .sym file, which describes both the graphical aspect of the component in the schematic and the SPICE model of the component. Not all the components supported by IC-EMC are in the symbol palette. IC-EMC proposes additional components that can be inserted in the schematic through the Insert / User Symbol (.SYM) command. They can be either constructed by the user as a SPICE subcircuit (using command "File > Generate SPICE Subcircuit"), or found in the list of

symbols in the "ieee" subdirectory. More information about the symbols contained in the system/ieee directory can be found on the IC-EMC companion website.

Figure 2- 6: Symbol palette

The main commands for EMC and post-processing can be found in the EMC menu or the command bar, as shown in Figure 2-7. After editing the schematic and setting the simulation parameters, click on the 'Generate SPICE netlist' button to translate the schematic diagram into a SPICE-compatible text file. This step is necessary before any new SPICE simulation or post-processing of results. The following icons give access to the main post-processing tools (e.g. emission window, near-field simulation, immunity simulation, Z- and S-parameters etc.).

Figure 2- 7: Main simulation commands

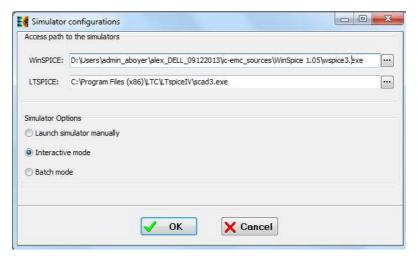

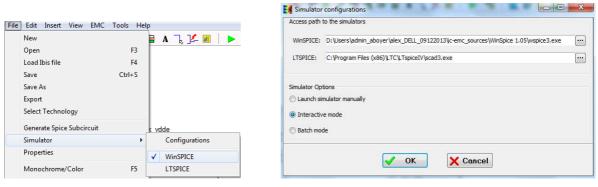

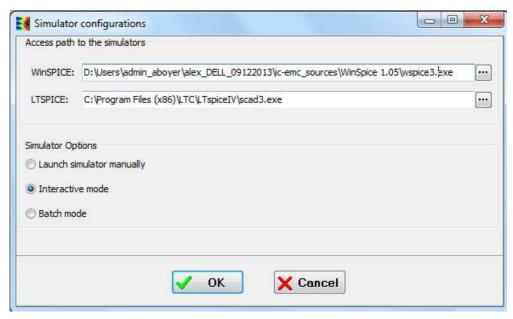

#### II.2.5 Configure simulator options

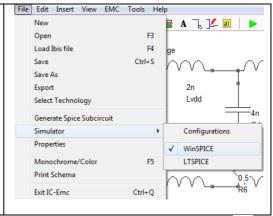

Before launching SPICE simulations, it is necessary to define the access path of the simulators (WinSPICE and LTSPICE) and the launching options. It can be configured by clicking on the command menu "File > Simulator > Configurations". The following window opens.

Figure 2- 8: Simulator configurations (File > Simulator > Configurations")

- Launch simulator manually: when the user generates SPICE netlist , he has to launch the simulator, opens the circuit netlist (.cir file) and launch the simulation

- Interactive mode: when the user generates SPICE netlist, the simulator is automatically launched and remains opened at the end of the simulation to analyze the result

- Batch mode: when the user generates SPICE netlist →, the simulator is automatically launched but is closed directly at the end of the simulation

## II.3 Using IC-EMC

#### II.3.1 Create my first model

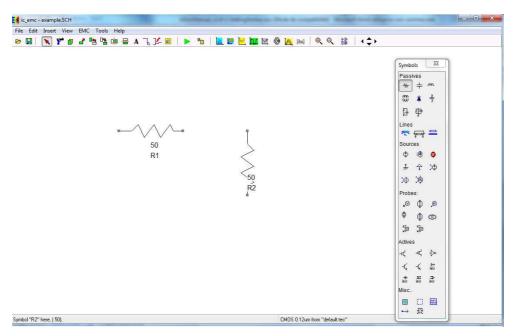

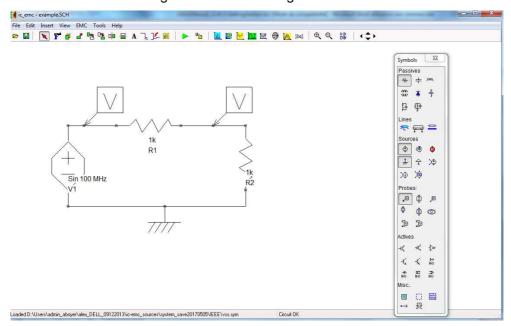

As first simple example, we consider a resistive voltage divider excited by a sine waveform signal at its input. The divider is made of two resistance of 1 K $\Omega$ . The amplitude of the signal is 1 V and its frequency is set to 100 MHz. The simulation aims at predicting the transient waveform of the voltage at the output of the resistive divider.

Double-click on executable file ic\_emc.exe to launch the software. if it is already opened, click on the command "File > New" or "CTRL+N" to create a new schematic diagram.

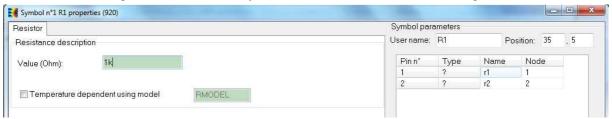

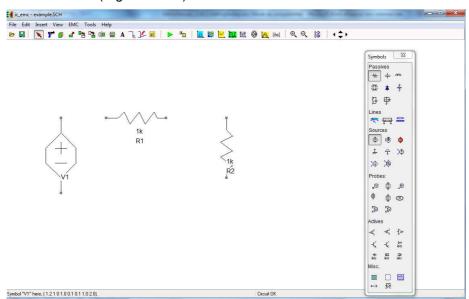

Pick two resistor symbols in the Symbol palette, drag and place them on the schematic. These symbols are called R1 and R2 by default. Their default resistance is  $50~\Omega$ . Click on the icon to rotate to the right the resistor R2. The result is shown in Figure 2- 9. To change the properties of the symbols (name and resistance), double-click on the symbol. The window shown in Figure 2- 10 opens. Change the resistance value of both resistors to 1 K in the field "Value". To change the name of a symbol, write the new name in the field "User name". To validate the change, click on the button OK or type "Enter" key.

Figure 2- 9: Place two symbols of resistor on a schematic diagram

Figure 2- 10: Change the resistance value of a resistor symbol

Then, pick the voltage source symbol in the Symbol palette and place it on the schematic diagram on the left of R1 (Figure 2- 11).

Figure 2- 11: Place one voltage source symbol on a schematic diagram

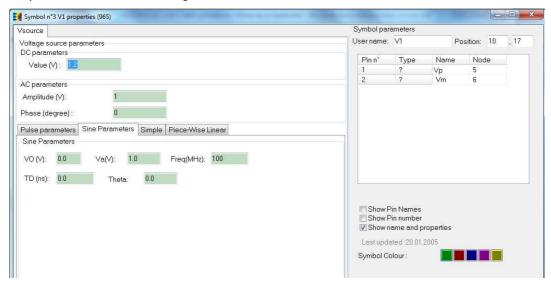

Double-click on the voltage source symbol to edit its properties. Click on the tab "Sine Parameters" to set a sine waveform generator. The following parameters are proposed:

- VO: offset voltage (V)

- VA: amplitude of the sine waveform (V)

- Freq: frequency (MHz)

- TD: delay (ns)

- Theta: damping factor (1/s)

Use the parameters shown in Figure 2- 12 and click on the button OK

Figure 2- 12: Edit the properties of a voltage source

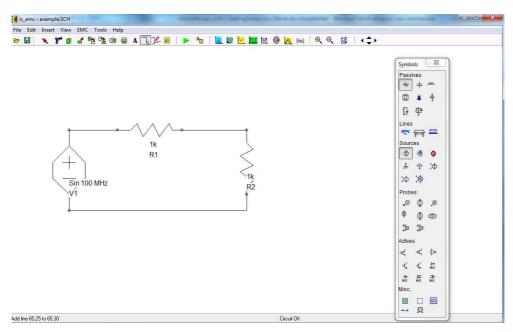

All the electrical components of the circuit have been placed. Now, they have to be interconnected. Interconnections between symbol's nodes are ensured by wires. To add wire, click on the icon "Line" or on the menu "Edit > Line". Line edition mode is activated and wires are created between two points selected on the schematic with the left button of the mouse. The line edition mode is deactivated by clicking on the icon "Select" or hitting the ESC key. Alternatively, line edition mode can be activated by clicking on the schematic with the left button of the mouse. Place wire between the different terminals of the symbols. Terminals are highlighted by square symbol \(\Pi\). The result is shown in Figure 2- 13. Before simulation, it is necessary to indicate the voltages and currents that we want to observe by placing voltage and current probes on the schematic diagram. Voltage probes are connected on one node of the diagram while current probe are placed within one circuit branch. In this example, place two voltage probes: one at the divider input (between V1 and R1), the other at the divider output (between R1 and R2).

Figure 2- 13: Place wire to interconnect the different symbols of the schematic diagram

The schematic diagram is nearly terminated, but an important element has been forgotten. In any SPICE netlist, a '0' or reference node has to be defined. Forgotting such reference node will result in simulator error. Place the symbol "Ground" on the schematic, between V1 and R2. The final schematic diagram is shown in Figure 2- 14.

Figure 2- 14: Place voltage probes and the ground symbol

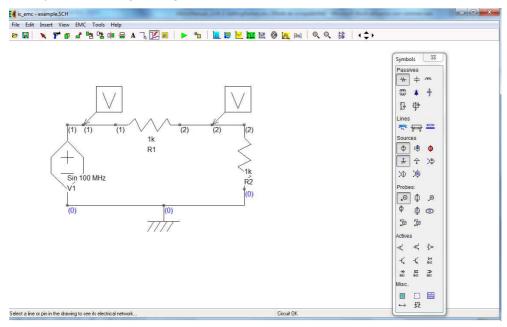

Before launching the SPICE simulation, IC-EMC converts the schematic diagram into a netlist (file .cir) compatible with WinSPICE or LTSPICE. This netlist describes the circuit in components whose terminals are referenced by number. Each number indicates a node of the schematic diagram. All the terminal with the same node number are connected electrically. To see the number of the different nodes forming the schematic diagram, click on

the icon or on the menu "View > View Electrical Net" (Figure 2- 15). Voltage probes have been placed on nodes 1 and 2. This view can be convenient to verify electrical connections between the symbols during debug.

Figure 2- 15: View the nodes of the schematic diagram (icon  $\frac{1}{2}$ )

#### II.3.2 Save the schematic diagram

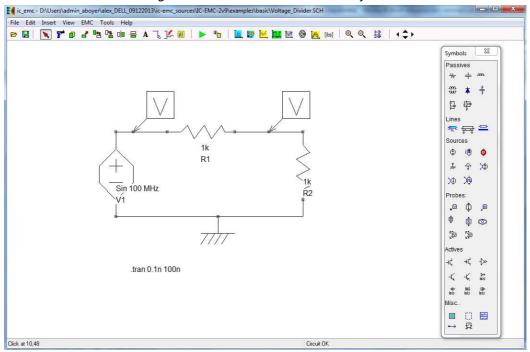

Before launching any simulation, it is extremely important to save the schematic in a known directory. Click on "File > Save as" or on the icon or CTRL+S to save the schematic diagram. They are saved in .sch file. Save it as Voltage\_Divider.sch. The final version of this schematic diagram is available in the directory "\examples\basic\FFT".

#### II.3.3 Prepare the analysis

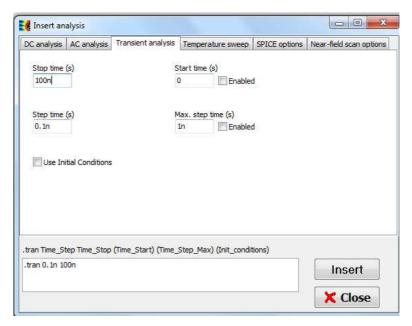

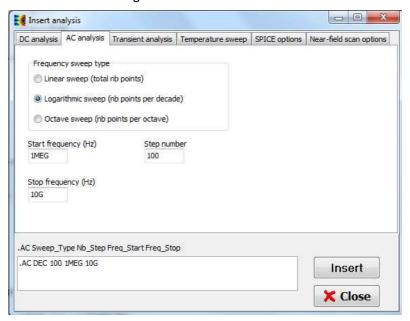

SPICE simulator proposes different analyses (DC, AC, TRAN...). The analysis is defined and configured by a analysis command line added to the schematic. Here, we want to set a transient simulation. The most convenient way to set simulation parameters for beginners is to click on "Insert > Insert analysis line". The following window open to set up the SPICE analysis. Select the tab "Transient analysis" and set:

Stop time: 100 nsStep time: 0.1 ns

The SPICE analysis command line appears at the bottom of the window and is updated each time the analysis parameters are changed. The format of the analysis line is also shown. Finally, click on the button "Insert" and click "Close". The analysis line is automatically inserted on the schematic diagram, as shown in Figure 2- 17. Alternatively, the analysis line can be directly added on the schematic by clicking on the icon A and type the command line ".tran 0.1n 100n".

Figure 2- 16: Define the SPICE analysis

Figure 2- 17: Insert the SPICE analysis line on the schematic diagram

#### II.3.4 Launch my first simulation

Before launching your first simulation, you should ensure that the access paths of the simulators have been defined as explained in part II.2.5. Two SPICE simulators are supported by IC-EMC: WinSPICE and LTSPICE. To select a simulator, click on the menu "File > Simulator" and select "WinSPICE" or "LTSPICE". In this example, WinSPICE will be used. Click on the menu "File > Simulator > Configurations" and select the option "Interactive mode": the simulator will be launched automatically when the netlist will be generated.

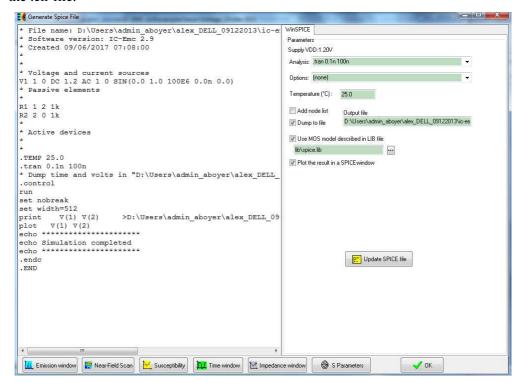

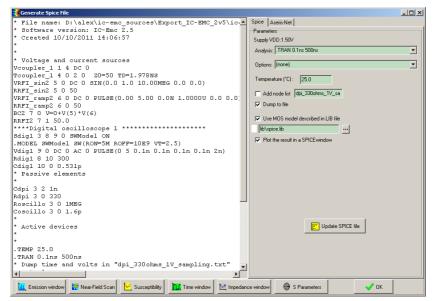

Click on the button or on the menu "EMC > Generate SPICE file" or hit CTRL+G to launch the simulation. Actually, this command is twofold:

- the electrical schematic diagram is converted in a netlist, saved in a .cir file. The netlist file has the same name than the schematic file (Voltage\_Divider.cir). The window shown in Figure 2-18 appears when the netlist file is generated to verify the content of the netlist. Click on the button "OK" to close this window.

- in "File > Simulator > Configurations", if the options "Interactive mode" or "Batch mode" have been selected, then the SPICE simulation is automatically launched. If the option "Launch simulator manually" is selected, then the user has to launch the simulator and select the .cir file.

Figure 2- 18: Generation of the netlist file

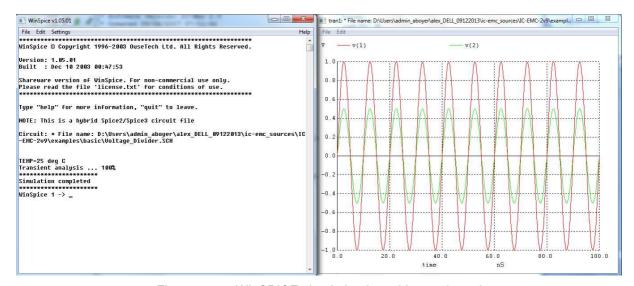

SPICE simulation is launched automatically and the WinSPICE interface opens. At the end of the simulation, the message "Simulation Completed" is displayed on the WinSPICE interface and the simulation result is displayed (Figure 2- 19). IC-EMC proposes tools to analyze simulation results, as described in the next part and the next chapter of this manual.

Figure 2- 19: WinSPICE simulation launching and result

#### II.3.5 Analysis result

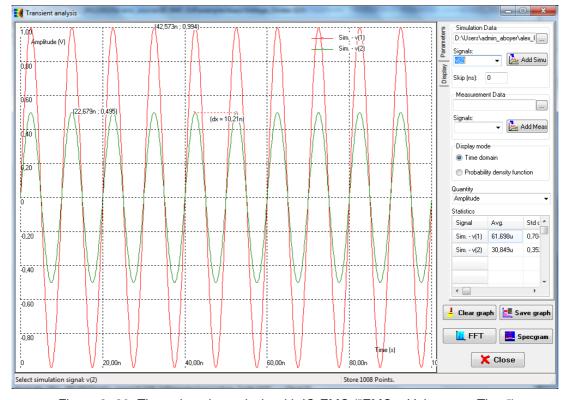

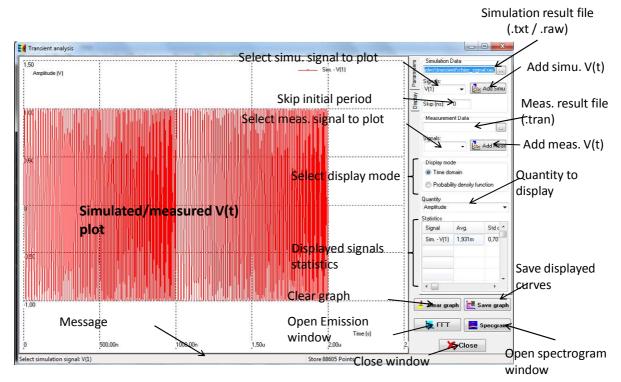

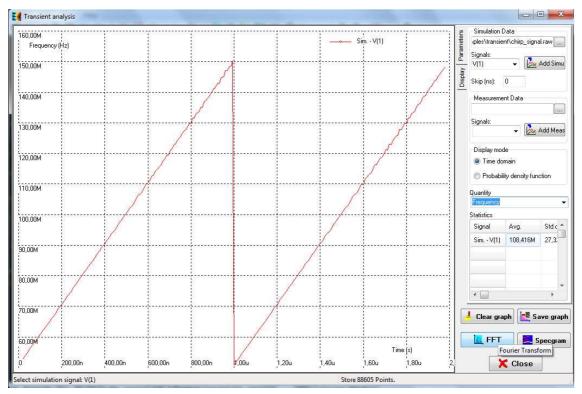

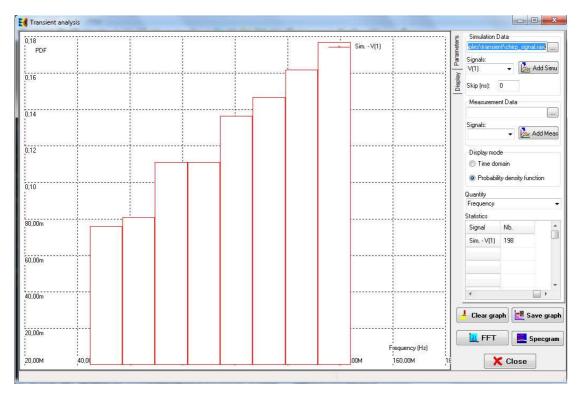

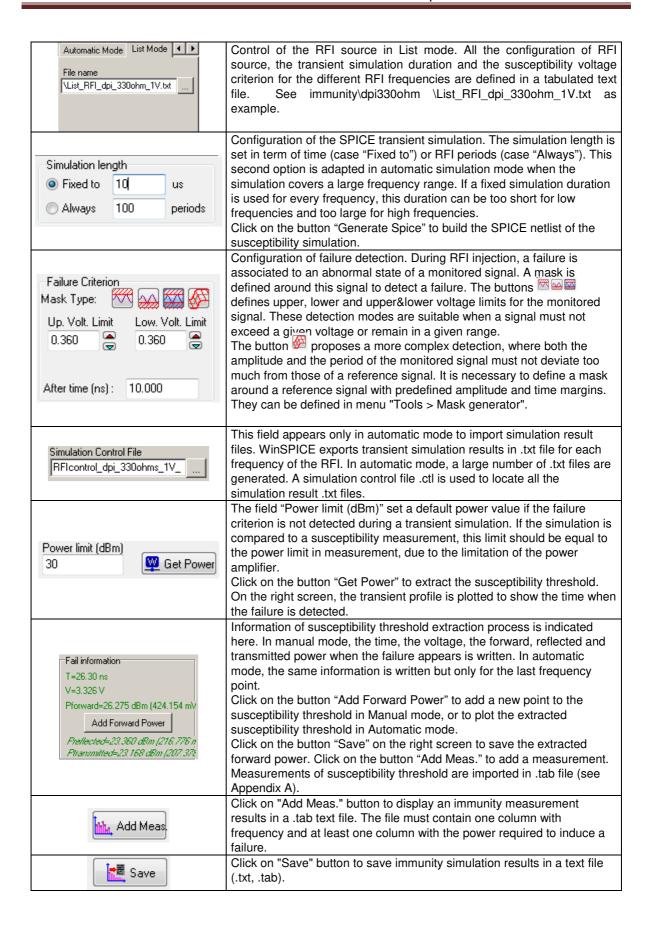

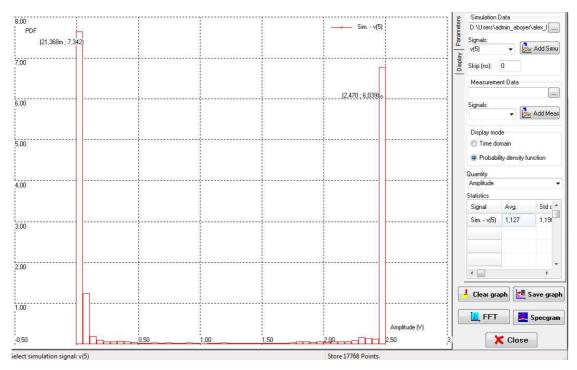

First, the transient waveforms of input and output signals are analyzed. Open the "Voltage vs. Time" window by clicking on the button or on the menu "EMC > Voltage vs. Time", presented in Figure 2- 20. The signals associated to the voltage probes added on the schematic diagram appears on the list "Signal" in the top-right part of the window. Select both signals (v(1) and v(2)) and click on the button "Add Simu" to plot them.

Figure 2- 20: Time -domain analysis with IC-EMC ("EMC > Voltage vs. Time")

In the tab "Display", different options are proposed to change the axes settings. Amplitude and period characteristics can be extracted by clicking directly on the graph. More indicators are available in this tool. They will be described in the next chapters. A practical example is shown in III.6. Close the window by clicking on the button "Close".

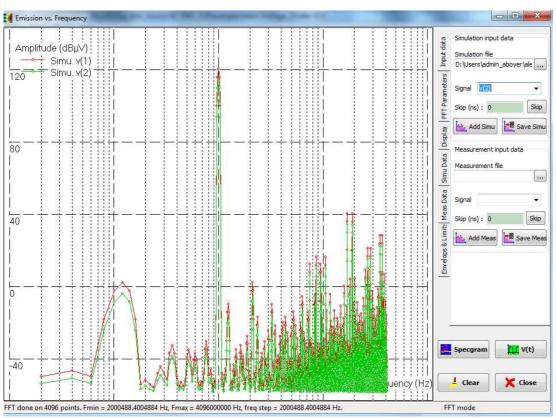

Then, the spectrum of the input signal is analyzed. Click on the icon "EMC > Emission vs. Frequency". The window shown in Figure 2- 21 opens, showing the spectrum of the input and output signals of the voltage divider. The spectrum is computed by Fast Fourier Transform (FFT). The number of points can be changed to adjust the resolution by clicking on the list "Resolution" in the tab "FFT Parameters". Select 4096 points and a

Blackman window. In the tab "Display", click on the button in the tab "Display" to set a logarithmic scale on Y axis. The voltages are expressed in dBμV, which is typical in conducted emission measurement.

The FFT result presents a large peak centered at 100 MHz. Its amplitude is equal to 120 dB $\mu$ V, i.e. 1 V. This result is consistent with the sine wave nature of the signal. Click on the button "Close" to close this window.

Figure 2- 21: Frequency -domain analysis with IC-EMC ("EMC > Emission vs. Frequency")

#### II.3.6 Close IC-EMC

Before leaving IC-EMC, save your schematic diagram by clicking on the icon by or click on the menu "File > Save". Click "File > Exit IC-EMC" or hit CTRL+Q to close the software.

## III. Working with IC-EMC

This part provides straightforward examples of how to use IC-EMC to create simple model of a circuit and perform the main analysis proposed by IC-EMC:

- simulation of electromagnetic emission based on the transient response of voltage or current

- simulation of impedance and S parameters of passive or active devices, PCB traces, cables...

- simulation of the conducted immunity of IC to harmonic disturbance

- analysis of IBIS file and extraction of equivalent models of I/O buffers

- analysis of transient signals (timing characteristics, statistical properties, short-term FFT)

- simulation of signal integrity and eye diagram plot

- simulation of near-field emission based on thin-wire approximation

- modelling of various type of interconnects (PCB traces, cables, IC package, power-ground plane pair)

- estimation of IC emission model

IC-EMC is also able to import measurement files to compare simulation with measurement results.

#### III.1 Simulation of the conducted emission of a microcontroller

This example presents the flow to simulate the conducted emission of a microcontroller, using a simplified microcontroller model. Simulated conducted emission measurements are related to the IEC 61967-4 standard's  $1/150 \Omega$  method [IEC61-4].

#### III.1.1 Open the example

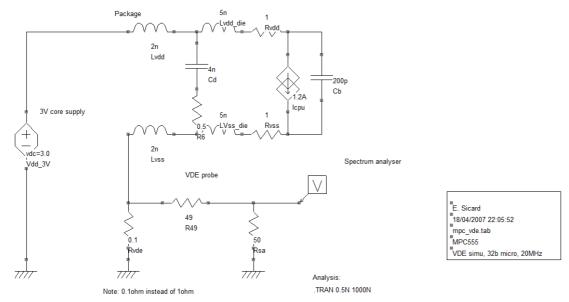

Open file "examples\emission\mpc\mpc\_vde.sch" (Figure 3- 1). The model includes a description of the microcontroller based on a set of RLC elements and a current source, according to the IEC62433-2 ICEM-CE model format [ICEM]. ICEM is an IEC standard dedicated to emission modelling. Moreover, resistances  $R_{\text{VDE}},\,R_{\text{49}}$  and  $R_{\text{SA}}$  are added as an equivalent model of the current measurement probe defined by the IEC 61967-4 standard, also known as 1  $\Omega$  method. The meaning of the components forming the circuit model is given in Table 3- 1.

Figure 3- 1: The ICEM model of a 32-bit microcontroller (examples\emission\mpc\mpc\_vde.sch)

| Parameters     | Description                                                                              | Remarks                                                                  |  |

|----------------|------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|--|

| lb             | Current source                                                                           | The Ib current is described as periodic triangle (1.2 A max)             |  |

|                | Unit: Ampere                                                                             | periodio triarigio (1.271 max)                                           |  |

|                | Description: piece-wise-linear                                                           |                                                                          |  |

| Cd             | Decoupling capacitance                                                                   | Cd is 4 nF, which is quite high du                                       |  |

|                | Unit: Farad                                                                              | to on-chip added capacitance                                             |  |

|                | Description: discrete C                                                                  |                                                                          |  |

| Lvdd_die,      | Series internal inductance                                                               | The series inductance is tuned to 5                                      |  |

| Lvss_die       | Unit: Henry                                                                              | nH, which provokes a resonance effect with Cb around 300 MHz.            |  |

|                | Description: discrete L                                                                  |                                                                          |  |

| Rvdd_die,      | Series internal resistance                                                               | Around 1 ohm series resistand due to long on-chip metal traces           |  |

| Rvss_die       | Unit: Ohm                                                                                |                                                                          |  |

|                | Description: discrete R                                                                  |                                                                          |  |

| Cb             | Block decoupling capacitance                                                             | Local block capacitance, around                                          |  |

|                | Unit: Farad                                                                              | 200 pF.                                                                  |  |

|                | Description: discrete C                                                                  |                                                                          |  |

| Rvde, R49, Rsa | Current probe, matching resistors, and input impedance of spectrum analyser respectively | usually equal to 1 ohm. To reduce voltage drops across this resistor, it |  |

|                | Unit: Ohm                                                                                | has been replaced by 0.1 ohm.                                            |  |

|                | Description: discrete R                                                                  |                                                                          |  |

Table 3- 1: Details on the circuit model's electrical components (examples\emission\mpc\mpc vde.sch)

Lvdd and Lvss concern the package, and account for the series equivalent inductance from the IC die to the physical supply source and the VDE probe. Notice that the series resistance is 0.1  $\Omega$  instead of 1  $\Omega$  due to the high current flowing inside the IC. Placing a 1  $\Omega$  series resistance would dissipate nearly 1 W and induce a voltage drop of around 1 V, which is unacceptable. The voltage measured by spectrum analyser  $V_{SA}$  across the 0.1  $\Omega$  resistor is related to IC current  $I_{gnd}$  returning to the ground through the resistance by the following theoretical relation (if PCB and passive device interferences are ignored).

$$V_{SA}=rac{1}{2}\,R_{VDE}I_{gnd}$$

Eq. 3- 1

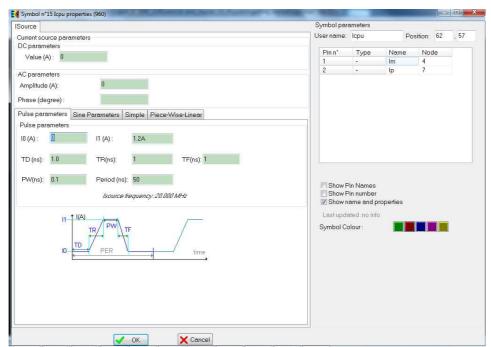

#### **III.1.2 Current Source Description**

The internal activity of a circuit corresponds to charge/discharge cycles which can be modelled by one or more current sources. The most basic description is that of a pulse waveform. This modelling approach has been adopted by the ICEM standard. A time-dependent waveform is assigned to the current source for transient analysis. There are five independent source functions: pulse, exponential, sinusoidal, piece-wise linear and single-frequency FM. In the schematic editor, the pulse is described, as shown in Figure 3- 2. The pulse description restricts the *Ib* shape to a periodic pulse, which is triangular if the pulse width parameter is set to zero.

Figure 3- 2: Current Pulse parameters in the schematic editor (mpc vde.sch)

PULSE(IO I1 TD TR TF PW PER)

Example: IIcpu 5 7 PULSE(0 1.2A 1.0n 1n 1n 0.5n 50n)

| Parameter | Description  | Unit |

|-----------|--------------|------|

| 11        | pulsed value | Amps |

| TD  | rise time   | TSTEP seconds |

|-----|-------------|---------------|

| TF  | fall time   | TSTEP seconds |

| PW  | pulse width | TSTOP seconds |

| PER | period      | TSTOP seconds |

Table 3- 2: Current source description under SPICE

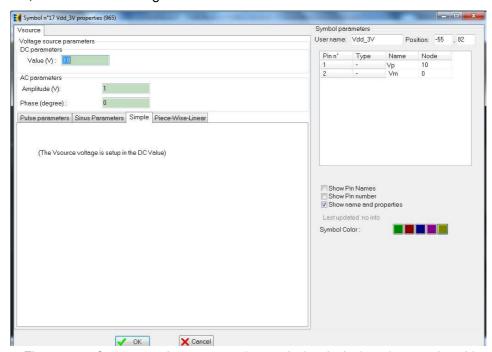

#### **III.1.3 Power supply Description**

The power supply is modelled by a constant voltage source. In **Erreur! Source du renvoi introuvable.**, the constant voltage source has a DC value of 3.0 V.

Figure 3- 3: Constant voltage source (examples\emission\mpc\mpc\_vde.sch)

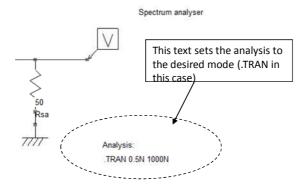

#### III.1.4 Analysis Description

In the editing window, a command line is added to set up the desired analysis. The line must start by '.TRAN' for a transient analysis. In Figure 3- 4, the time-domain analysis is set to 1000 ns, with a simulation step of 0.1 ns.

Figure 3- 4: Defining the SPICE simulation parameters

Two methods are used to insert an analysis line on the schematic:

- click on button A or in the "Edit > Text" menu, directly type the SPICE analysis command

- in the Insert menu, click on "Insert analysis line". An interface dedicated to the configuration of the SPICE simulation is opened and the analysis line is automatically inserted on the schematic with the correct syntax.

#### III.1.5 Create the SPICE file

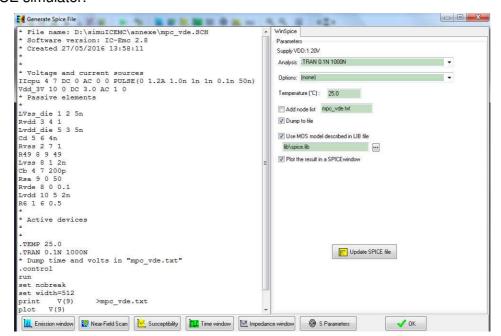

IC-EMC can build netlist files .cir compatible either with WinSPICE or with LTSPICE. The selection of the simulator is made in the menu "File > Simulator". The simulator is launched either manually by the user or automatically after the generation of the netlist, depending on the selected options in the menu "File > Simulator Configurations". In this example, we WinSPICE as simulator. It will be launched manually: in the menu "File > Simulator > Configurations", select the option simulator manually".

Use command  $File \rightarrow Generate\ Spice\ file\ or\ select\ <Ctrl>+<G>\ or\ click\ on\ the\ button\ in the command bar. The following screen appears (Figure 3- 5). This creates a file called "mpc_vde.cir", which contains the circuit's netlist description. This is the input file for the WinSPICE simulator.$

Figure 3- 5: The SPICE file generated from the schematic diagram (examples\emission\mpc\mpc\_vde.sch)

#### III.1.6 Run SPICE Simulation

As explained in III.1.5, we select WinSPICE as SPICE simulator. We also choose to launch the simulator manually. Start the WinSpice program and click on "File > Open" (Figure 3- 6). Select the desired .CIR file, i.e. the file generated by IC-EMC during the previous step

(examples\emission\mpc\mpc\_vde.cir). The simulation is performed in the time domain, and the following screen appears. The .TRAN analysis simulates the first 1000 ns of the transient evolution of the signal. The result is stored in a file called "mpc\_vde.txt". By default, the plot of the transient simulation appears in a new window shown in Figure 3-6.

Figure 3- 6: The initial WinSPICE screen (top) and transient simulation performed by WinSPICE (bottom)

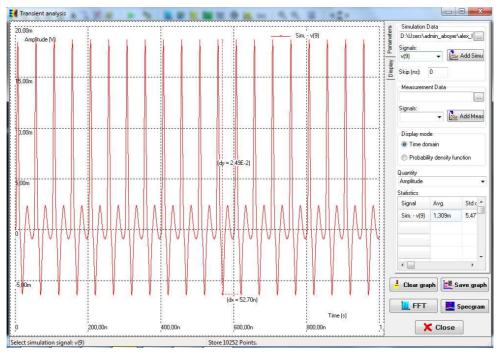

#### III.1.7 Plot the transient waveform

The transient waveform of the voltage across the 0.1  $\Omega$  resistor can be plotted in IC-EMC by clicking in the menu "EMC > Voltage vs. time" or on the button in the command bar, as shown in Figure 3-7. The list of signals saved by the simulator is given in the list Signals in the menu "Simulation Data" in the right part of the window. The signal name is "V(9)", where V indicates that we monitor a voltage, "9" is the number of the monitored node in the schematic.

Remark: click on the menu "View > View electrical net" or on the button to display all the nodes directly on the schematic.

Right-clicking on the graph returns the (time; voltage) coordinate of the clicking position. Moreover, if you move the cursor while you're right-clicking, when the right-click is released, the X-Y shift between the initial and stop positions is shown. Amplitude and period of signals may be evaluated with this method. More details about this window will be presented in III.6.

Figure 3- 7: Transient profile of the voltage induced across the 0.1  $\Omega$  resistor (examples\emission\mpc\mpc vde.sch)

#### III.1.8 Emission simulation

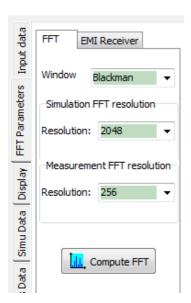

The voltage waveform computed by the analogue simulator is translated into the frequency domain according to two methods:

- FFT mode: by default with a Fast Fourier Transform (FFT)

- EMI receiver mode: the effect of the intermediate frequency (IF) filter of an EMI receiver followed by a peak detector is simulated. The parameters of this mode should be set carefully because the computation time may be long.

The X-axis should cover the 1-5000 MHz range in a linear or logarithmic scale. The energy along the Y-axis is in  $dB\mu V$  or V ( $dB\mu A$  and A if results expressed in current are imported). In

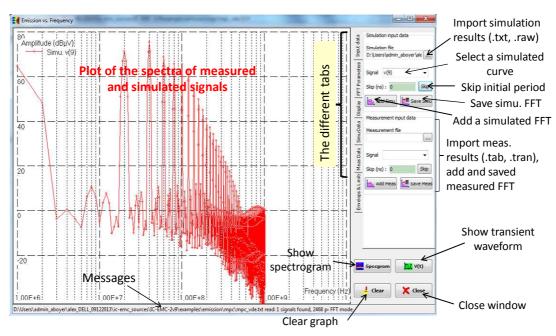

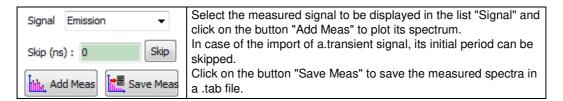

the command bar, click on button 'Emission vs. Frequency', or click "EMC > Emission vs. Frequency". A specific screen opens with Log/Log units configured to display voltage or current vs. frequency, as shown in Figure 3- 8. The main commands of this window are dispatched in several tabs:

- Input data: import of simulation (.txt from WinSPICE and .raw from LTSPICE) and measurement result files (measured spectrum .tab and measured transient waveform .tran), save FFT of simulated or measured results.

- FFT Parameters: selection of the FFT mode or EMI receiver mode, selection of the FFT and EMI receiver parameters for simulation and measurement results.

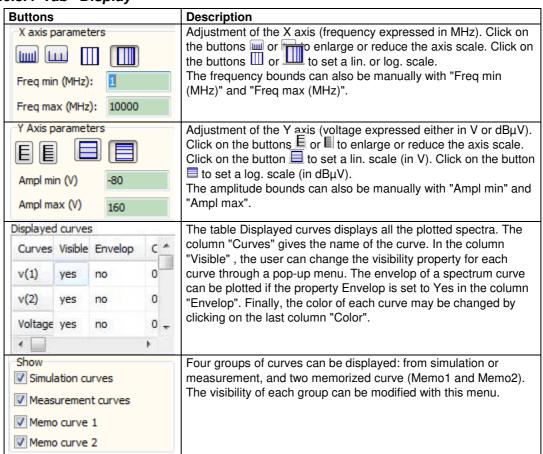

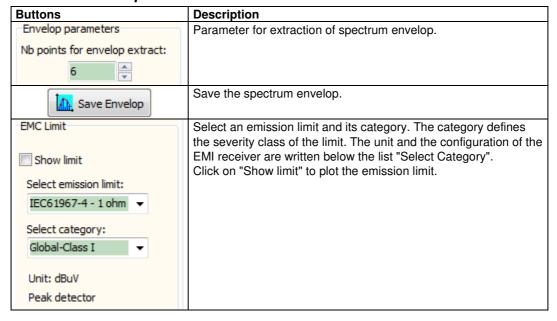

- Display: set the axis configuration (limits, lin/log mode), visibility of curves on the graph, change color of displayed curves, plot envelop of spectrum,

- Simu Data and Meas Data: list of simulation and measurement results.

- Envelop & Limits: set parameters for the extraction of envelop of simulated or envelop spectrum, add a standard EMC limit.

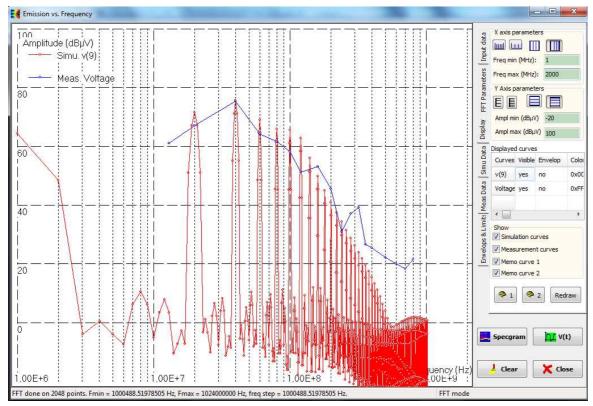

By default, if the schematic is opened and if the SPICE simulation runs correctly, the FFT mode is selected. A FFT is performed and the simulation results are directly plotted when the window opens. If the result is not displayed, click the button in "Simulation input data" part in the tab "Input data". Then select the file "mpc\_vde.txt". It is possible to remove the initial period of the simulated waveform, from 0 to the value in the field "Skip (ns)". If the simulation results are correctly imported, Figure 3-8 presents the obtained results.

Figure 3- 8: Simulation of the microcontroller's conducted emission (examples\emission\mpc\mpc\_vde.sch)

The number of points N for the FFT (the FFT resolution) is a power of two and is adapted to fit the information included in the simulation and ensure the best resolution. Two FFT parameters can be adapted:

- the number of points or resolution of the FFT (maximum 262144)

- the windowing type: rectangular, Hamming and Blackman(Blackman by default)

The FFT resolution can be adjusted for the simulation and measurement results independently. The FFT resolution for the measurement results is visible only if a transient measurement results in .tran format has been imported. The number of points which form a displayed FFT result is equal to N/2. The frequency resolution  $\Delta f$  is given by equation 3-2 and the maximum frequency  $F_{max}$  by equation 3-3.

$$\Delta f = \frac{1}{T_{\text{max}}} = \frac{1}{NT_e}$$

Eq. 3-2

$$F_{\text{max}} = \frac{1}{2T_e}$$

Eq. 3-3

where  $T_{\text{e}}$  is the sampling period of the transient signal,  $T_{\text{max}}$  the duration of the transient signal.

#### III.1.9 Comparison with Measurements

In the "Input data" tab, click the button in "Measurement input data" and select the file " examples\emission\mpc\mpc\_vde.tab". Then click on the button "Add meas." to display the measured spectrum. Figure 3- 9 shows the comparison between measurements and simulations.

The measurement curve is actually the envelop of the measured spectrum. The simulation fits the measured data up to 260 MHz except at 120 MHz, where the simulation is 10 dB above the measurement. Despite the discrepancy around this frequency, an acceptable correlation is obtained with a very simple model. Correlation with measurements may be improved, especially at high frequencies, by modifying the current profile, the IC internal power supply network and board models.

The axis settings and the curve properties can be modified by changing the options available on tab Display.

Figure 3- 9: Comparison between measured and conducted emission for a microcontroller (mpc vde.sch, mpe vde.tab)

## III.2 Impedance analysis of the power supply network of a circuit mounted in a 64 BGA package

This example presents the flow to simulate the impedance profile in frequency domain of the passive decoupling network (PDN) of a small 90 nm circuit mounted in a 64 ball grid array (BGA) package. The PDN is a macroscopic block defined by ICEM standard [ICEM] to describe the passive network which exists between several IC accesses, e.g the power supply network of a circuit. The accuracy of the PDN model is fundamental for emission and susceptibility predictions as it influences directly the noise propagation within the circuit. PDN modeling can be done either from Z parameter or S parameter representation.

In IC-EMC, impedance analysis is intended for rapid simulation of the impedance Z(f) for single port devices. For multiport analysis or conversion to S parameter, it is advised to perform S parameter simulation, which is described in part III.3.

# III.2.1 Load the example

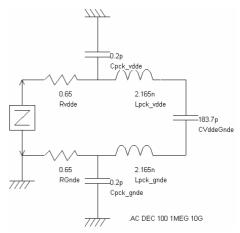

Load the file called "examples/impedance/FFIO90/FFIO\_90nm\_Z\_VDDE.sch". The electrical schematic is shown in Figure 3- 10. The schematic models the PDN of a small test chip fabricated in CMOS 90 nm containing several I/O structures [Boy08].

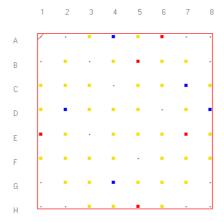

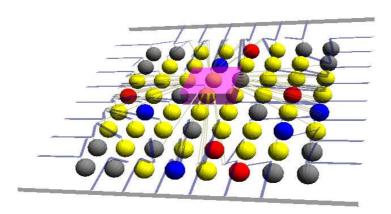

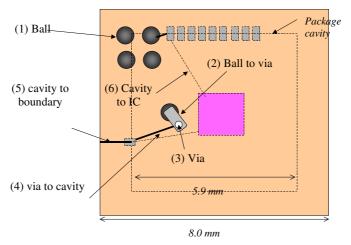

The circuit is mounted in a 64-pin BGA package, as described in Figure 3-11.

Figure 3- 10: PDN model of a test chip fabricated in CMOS 90 nm containing I/O structures (examples/impedance/FFIO90/FFIO\_90nm\_Z\_VDDE.sch)

Figure 3- 11: 64-pin LBGA package [Boy08]

Measurements have been performed using a Vector Network Analyzer (VNA) directly on the package balls with a coplanar probe placed between adjacent power pins VDDE and GNDE. The model has been extracted from the S parameter measurements. The PDN model includes two parts:

- the die contribution, i.e. interconnections and on-chip decoupling capacitances

- the package contribution, i.e inductive effects of balls, vias and bonding wires constituting the BGA package

Table 3- 3 gives details of the elements of the model.

| Parameters   | Description                       | Remarks                                      |

|--------------|-----------------------------------|----------------------------------------------|

| CVddeGnde    | Equivalent on-chip capacitance    | This element models all parasitic and        |

|              | Unit: Farad                       | intentional on-chip capacitances between     |

|              | Description: discrete capacitance | power supply VDDE and ground GNDE            |

|              |                                   | access.                                      |

| Lpck_vdde,   | Package parasitic inductance      | These 2 inductances model the contribution   |

| Lpck_gnde    | Unit: Henry                       | of all elements of VDDE and GNDE pins.       |

|              | Description: discrete inductance  | With on-chip capacitance, they are           |

|              |                                   | responsible of the first resonance.          |

| Cpck_vdde,   | Package parasitic capacitance     | These 2 capacitances model the               |

| Cpck_gnde    | Unit: Farad                       | contribution of all elements of VDDE and     |

|              | Description: discrete capacitance | GNDE pins. They are added to model the       |

|              |                                   | package self resonance which appears         |

|              |                                   | above several GHz.                           |

| RVdde, RGnde | Total power supply and ground     | These resistors represent the resistive      |

|              | resistance                        | contribution of package and on-chip          |

|              | Unit: Ohm                         | interconnections. Their effect is negligible |

|              | Description: discrete resistance  | except at resonance frequency.               |

Table 3- 3: Details of basic elements of FFIO 90nm Z VDDE.sch

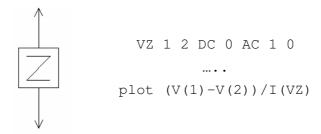

#### III.2.2 Impedance probe description

The impedance analysis corresponds to a simulation of the input impedance (also written Zin or Z11) seen from one circuit access relatively to a reference. In this example, the access is the power supply pin VDDE. The measurement is referenced to the ground pin GNDE.

Impedance simulation is allowed only if an impedance probe or Z probe is placed in the schematic diagram. The Z probe (Figure 3- 12) is accessible from the palette. If you double click on the Z probe, the property screen is displayed, but without any specific property. However, the Z probe is not a transparent symbol. When placed on the schematic, it creates a voltage source with the description below:

Figure 3- 12: Impedance probe and associated SPICE description

The voltage source associated to the Z probe is an AC source with an amplitude of 1 V. As may be found at the end of the SPICE netlist, a "plot" control is associated with an equation which computes the impedance by dividing the voltage amplitude across the probe by the current provided by the impedance probe.

**Remark:** use only one impedance probe per schematic diagram. The input impedance is linked to the current that a perfect voltage source delivers to a circuit. If a second AC voltage source is present, it will modify the current which flows along the branch of the first Z probe and hence the computed impedance.

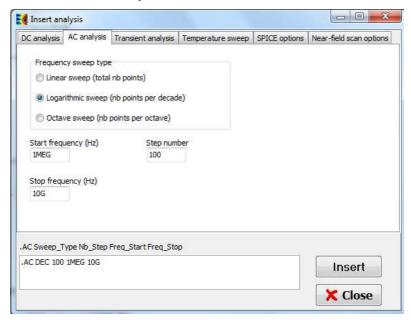

#### III.2.3 Analysis description

Impedance simulation is a small signal frequency analysis, so that it requires an AC simulation. The command line: " .AC DEC 100 1MEG 10G" is added to set up the desired analysis. The text must start by '.AC' followed by the AC simulation parameters. The frequency sampling is logarithmic (option DEC) with 100 points per decade between 1 MHz and 10 GHz. Two methods are used to insert an analysis line on the schematic:

- click on button A or in the "Edit > Text" menu, directly type the SPICE analysis command

- Click on "Insert > Insert analysis line". An interface dedicated to the configuration of the SPICE simulation is opened (Figure 3- 13) and the analysis line is automatically inserted on the schematic with the correct syntax.

Figure 3- 13: Insert AC simulation command line on the schematic ("Insert > Insert analysis line")

# III.2.4 Run SPICE simulation

In this example, WinSPICE is used as simulator. In the menu "File > Simulator", select "WinSPICE". Then, click on "File > Simulator > Configurations" to set the options of the simulators. The right window of Figure 3- 14 opens. The upper part gives the access path of the simulator. They have to be set up correctly before any simulation. In the lower part, three simulator launching options are proposed:

- Launch simulator manually: when the user generates SPICE netlist →, he has to launch the simulator, opens the circuit netlist (.cir file) and launch the simulation

- Interactive mode: when the user generates SPICE netlist, the simulator is automatically launched and remains opened at the end of the simulation to analyze the result

- Batch mode: when the user generates SPICE netlist →, the simulator is automatically launched but is closed directly at the end of the simulation

Figure 3- 14: Select simulator and configure the simulator options

In this example, select "Interactive mode" and click on the button OK. The simulator options are kept for the next simulations, until you change them.

Use command  $File \to Generate$  Spice file or click on the button in the command bar. The SPICE netlist FFIO\_90nm\_Z\_VDDE.cir is generated. WinSPICE is automatically launched and the impedance simulation is done. The following screen appears. WinSPICE can be closed at the end of the simulation.

Figure 3- 15: AC simulation performed by WinSPICE (FFIO\_90nm\_Z\_VDDE.txt)

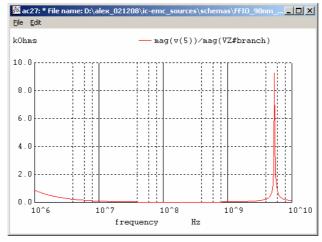

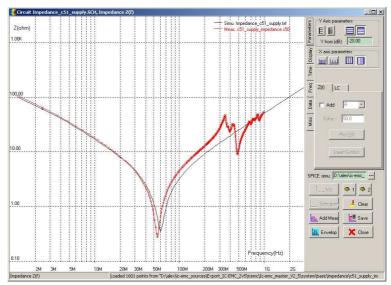

# III.2.5 Impedance analysis

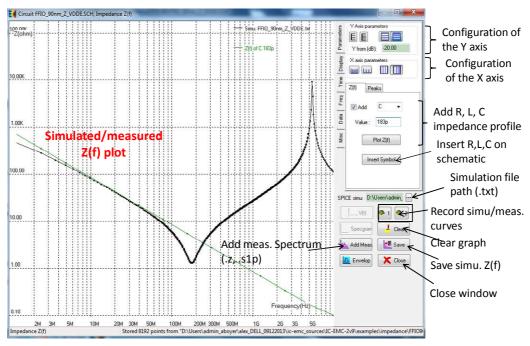

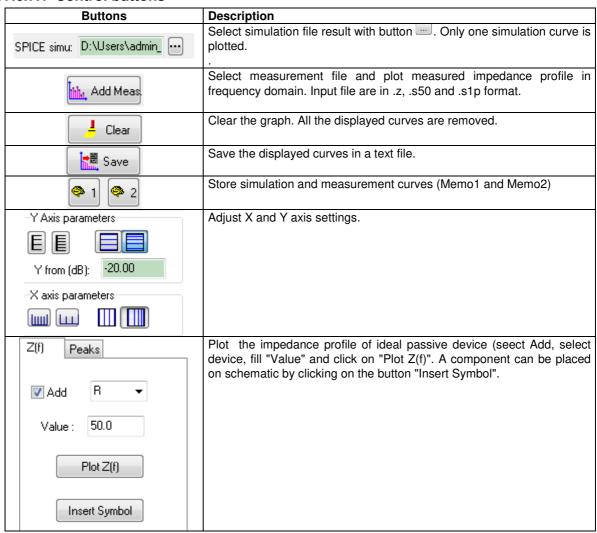

The impedance profile vs. frequency computed by WinSPICE can be displayed in a specific screen dedicated to impedance analysis. In the SPICE generator menu, click "Impedance Window", or click "EMC"  $\rightarrow$  "Impedance vs. Frequency". Alternatively, you may click the icon  $\stackrel{\text{Left}}{\longrightarrow}$ . A specific screen with Log/Log units configured to display impedance vs. frequency is proposed, as shown in Figure 3- 16.

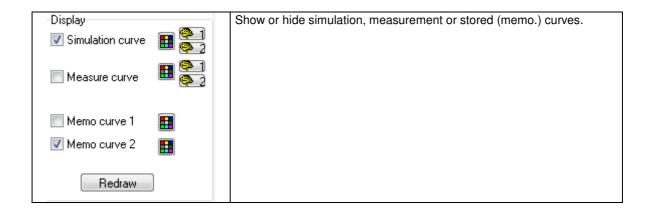

The main commands of this window are dispatched in several tabs:

- Parameters: X-Y axis configuration (lin/log display mode), add basic R, L, C impedance profile

- Display: display simulation, measurement, recorded results

- Freq: list of simulation and measurement results

By default, if the schematic is opened and if the SPICE simulation runs correctly, the Z(f) profile is plotted. If the result is not displayed, click the button on the right of "SPICE simu" and select file "FFIO\_90nm\_Z\_VDDE..txt".

Figure 3- 16: Input impedance simulation performed by WinSPICE (examples/impedance/FFIO90/FFIO\_90nm\_Z\_VDDE.sch)

At low frequency, impedance tends to decrease due to the on-chip capacitance effect. At 180 MHz, the first resonance linked to the on-chip capacitance and the package inductances appears. A second resonance due to package inductance and capacitance appears at 5.4 GHz.

To verify the on-chip capacitance of the circuit from the Z(f) profile, click on the box "Add" in the tab Z(f) and select C. Type 183 pF in the field "Value" and click on the button "Plot Z(f)". The Z(f) profile of a 183 pF is displayed and is tangent to the Z(f) profile of the circuit PDN in low frequency. It confirms that the total on-chip capacitance is about 183 pF. This basic tool can also be used with Z(f) measurement to extract equivalent resistance, capacitance or inductance.

#### III.2.6 Comparison with measurement

In the impedance window, click on the button "Add Meas" to display the impedance measurement of the PDN of the circuit. The measurement data are available in the file called "examples/impedance/FFIO90/Z11\_FFIO\_VDDE\_A4B5.z". The comparison between measurement and simulation is presented in Figure 3- 17 and proves the validity of the model up to 3 GHz.

Figure 3- 17: Comparison between measured and simulated input impedance of the PDN of the 90 nm circuit (examples/impedance/FFIO90/ Z11\_FFIO\_VDDE\_A4B5.z)

# III.3 S parameter analysis for model construction of a bias tee

A typical method to construct electrical models of components is based on equivalent R, L,C networks extracted from S parameter measurements. Here, we present an example of comparison between measurements and simulations of two-port S parameter done on a home-made bias tee. A bias tee is a three-port decoupling network used to superimpose a low frequency signal and a high frequency signals. The bias tee ensures the isolation between the low frequency and the high frequency signal sources. A bias tee is required in IEC62132-4 Direct Power Injection (DPI) test in order to superimpose a conducted aggression on a low frequency signal (input signal or power supply). The name given to the three ports of the bias tee are:

- a low frequency (LF) input

- a radiofrequency (RF) input, connected to the RF disturbance source

- the output with the signal resulting of the superposition of both inputs

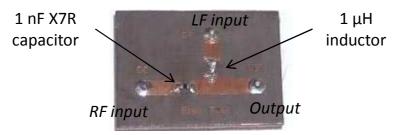

The LF input is isolated from RF signal by a resistor, inductor or ferrite which filter high frequency signal. Resistors should be avoided if DPI is conducted on a power supply because of the power dissipation. The RF input is isolated from low frequency signal by a series capacitor. Figure 3- 18 presents a bias tee dedicated to DPI test on the frequency range 10 MHz - 3 GHz. It is build with several passive devices mounted on a PTFE substrate board. Input and output SMA connectors are connected by 50  $\Omega$  microstrip line. A 1 nF capacitor and a 1  $\mu$ H inductor isolate RF and LF input from each other.

Figure 3- 18: Home-made bias tee for DPI tests

Values of inductors and capacitors are chosen in order to give the three following properties to the bias tee:

- A small reflection coefficient at RF input over all the targeted frequency range. It should be inferior to -10 dB to reduce input return loss.

- A high isolation or transmission coefficient from RF input and LF input over all the targeted frequency range. It should be less than -10 dB to prevent from RF leakage to LF source.

- A high transmission coefficient from RF input to output over all the targeted frequency range. It should be greater than -3 dB to enhance RF transmission to the output.

# III.3.1 Load the example

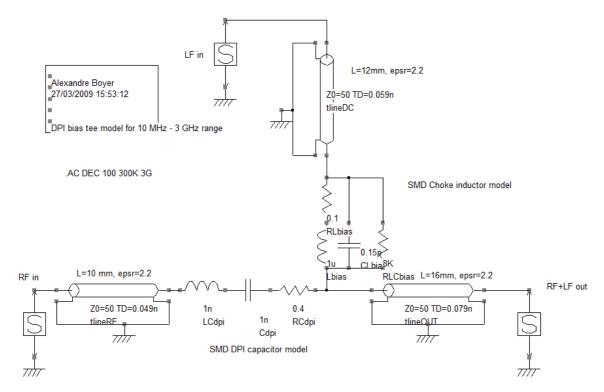

Open the file "examples\emc\_lib\3\_port\_bias\_tee.sch". The schematic is shown in Figure 3-19. Models of microstrip line are lossless 50  $\Omega$  transmission line, their delay time have been computed from physical length and dielectric constant of the substrate. The capacitor and inductor models have been extracted previously. A parasitic serial inductor is added to the capacitor while a parallel capacitor is added to the inductor to induce self-resonance. Resistances are added to reduce their quality factors. Three S parameter probes are placed at each terminal of the model so that a full  $3\times3$  scattering matrix can be simulated.

Figure 3- 19: Model of a bias tee optimized for the frequency range 10 MHz – 3 GHz (examples\EMC\_lib\3\_port\_bias\_tee.sch)

#### III.3.2 S parameter probe description

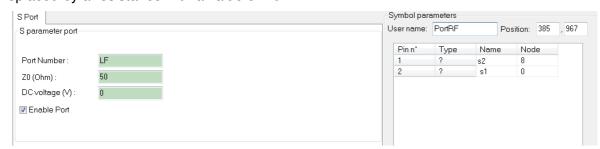

S parameter simulation is allowed only if at least one S parameter port probe is placed within the schematic. The S parameter probe is accessible from the palette with the symbol  $\$ Double clicking on the probe opens their property screen (Figure 3- 20). A S parameter probe is characterized by a user name, a unique number, a characteristic impedance Z0 (which must be common to every port) and a DC voltage. A port can be disabled so that it is replaced by a resistance with a value of Z0.

Figure 3- 20: S parameter port probe properties

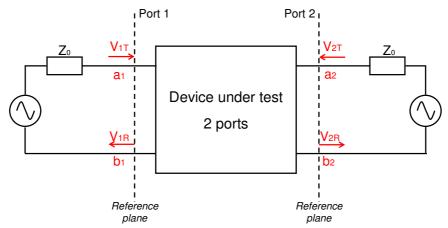

A S parameter probe is formed by a sine waveform voltage source with a series resistance Z0. The amplitude of the voltage source is equal to 0 or 1 V depending if the probe is activated or not. Figure 3- 21 presents a representation of a 2-port device characterized by S parameters. S parameter probes are composed of small signal sinusoidal source and reference impedance  $Z_0$  connected to device terminals.

Figure 3- 21: S parameter characterization of a 2 port device

The four parameters, listed below, allow a complete characterization of power exchanges between the 2 ports. They form the S parameter matrix. This principle can be extended to device with any port number.

| Input reflection coefficient                                                            | Output reflection coefficient                                                            |

|-----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

| $S_{11} = \frac{b_1}{a_1} \bigg _{a_2 = 0}$                                             | $S_{22} = \frac{b_2}{a_2} \bigg _{a_1 = 0}$                                              |

| No power fed from port 2. Port 2 terminated by Z0 to prevent from reflection at port 2. | No power fed from port 1.  Port 1 terminated by Z0 to prevent from reflection at port 1. |

| Forward transmission coefficient                                                        | Forward transmission coefficient                                                         |

| $S_{21} = \frac{b_2}{a_1} \bigg _{a_2 = 0}$                                             | $S_{12} = \frac{b_1}{a_2} \bigg _{a_1 = 0}$                                              |

| No power fed from port 2. Port 2 terminated by Z0 to prevent from reflection at port 2. | No power fed from port 1.  Port 1 terminated by Z0 to prevent from reflection at port 1. |

Table 3-4: Definition of the S parameters for a 2 port device

S parameter matrix can be converted into other forms (impedance, admittance, ABCD ...). For electrical modeling purpose, impedance is a convenient representation. The conversion between [S] to [Z] parameter matrices is given by the following equation, where [I] is the identity matrix.

$$[Z] = Z_0 \frac{[I] + [S]}{[I] - [S]}$$

Eq. 3-4

**Remarks:** if other probes (e.g. voltage, current or impedance probes) are present on the schematic, S parameter analysis is cancelled. Internal voltage source amplitude is set to 0 V, so each port is loaded by 50 ohms. The number of ports is limited to four. If more ports are added, they will be ignored and will be replaced by 50  $\Omega$  resistances.

#### III.3.3 Analysis description

S parameter simulation requires a small signal or AC simulation. A text line is added on the schematic which sets up the desired analysis. The text must start by '.AC' followed by the AC simulation parameters. In Figure 3- 19, the frequency sampling is logarithmic, with 100 points per decade between 300 KHz and 3 GHz. The analysis line can also be inserted with the command 'Insert' → 'Insert analysis line'. Two methods are used to insert an analysis line on the schematic:

- click on button A or in the "Edit > Text" menu, directly type the SPICE analysis command

- Click on "Insert > Insert analysis line". An interface dedicated to the configuration of the SPICE simulation is opened and the analysis line is automatically inserted on the schematic with the correct syntax.

# III.3.4 Run SPICE simulation

Select WinSPICE as simulator in "File > Simulator". In the menu "File > Simulator > Configurations", select "Interactive mode" to launch SPICE simulation automatically after the SPICE netlist generation >.

#### III.3.5 S parameter analysis

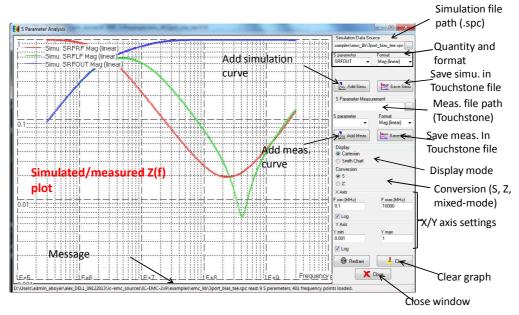

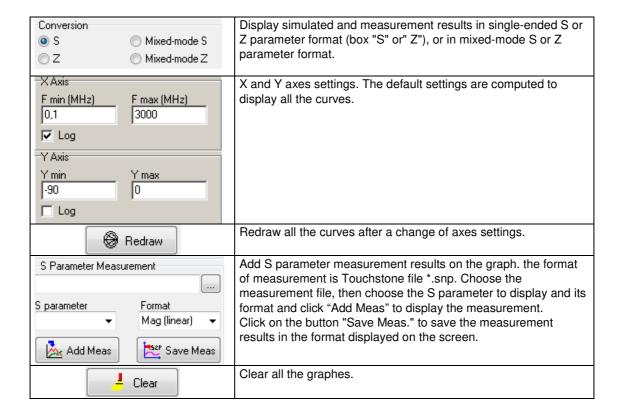

Click "EMC > S parameters" to open the [s] parameter display screen. Alternatively, you may click the icon. A specific screen with a blank screen and a menu on the right appears. Simulation results can be plotted by selecting the quantity to plot (S11, S12, ...) and its format (magnitude, phase, real or imaginary part) in the "Simulation data" part and clicking on the button "Add Simu" Add Simu. The graph can be plotted either in cartesian or Smith chart mode ("Display mode"). The result can be converted either in S or Z parameters, or mixed-mode parameters when 2 or 4 ports are placed on the schematic ("Conversion") (an example with mixed-mode S parameters is given in III.9.2). The X and Y axes boundaries and lin/log format can be set in "X axis" and "Y axis" parts.

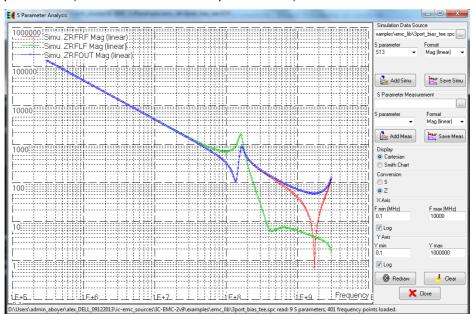

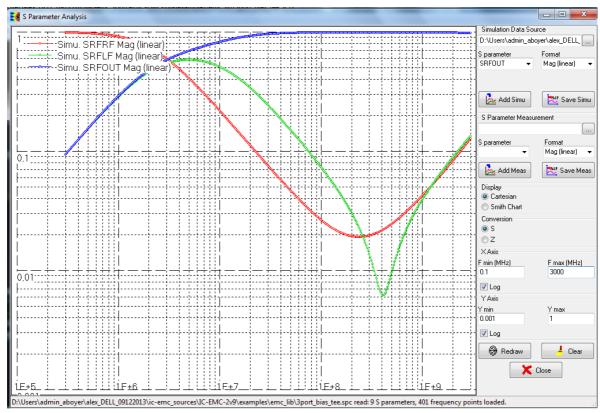

In order to check the three properties of bias tee listed in III.3, set the format to "Mag (linear)", select successively the quantities "SRFRF", "SRFLF" and "SRFOUT" an click on "Add Simu" to plot the RF input reflection coefficient, the RF-LF isolation and the RF to OUT transmission respectively. In "Display mode", select "Cartesian", and choose "S" in "Conversion" to plot S parameters. In "X axis" and "Y axis" parts, check the box "Log" to plot the axes in logarithmic mode. Figure 3- 22 shows the result that you should obtain.

Figure 3- 22: S parameter simulation of a three port bias tee (examples\EMC\_lib\3\_port\_bias\_tee.sch) The simulation shows that the RF input reflection coefficient (SRFRF parameter) is low between 10 MHz and 3 GHz while the transmission coefficient from RF to OUT terminals (SRFOUT parameter) is nearly equal to 1. The bias tee ensures an efficient transfer of the RF energy to a 50  $\Omega$  load connected to the output of the bias tee. The transmission coefficient between RF and LF terminals (SRFLF) is also small between 10 MHz and 3 GHz, proving the good isolation between the RF and LF sources.

The results can be plotted in Z parameter format if you select "Z" in "Conversion part". Click on the button "Redraw" to fit automatically the X and Y axes boundaries. The curves shows respectively the RF input impedance (ZRFRF parameter), the RF to LF and RF to OUT transfer impedances (ZRFLF and ZRFOUT parameters).

Figure 3- 23: Conversion from S to Z parameters (examples\EMC lib\3 port bias tee.sch)

The simulation results can be exported in the common Touchstone format .snp, where n is the number of ports and is limited to 4 in IC-EMC. Click on the button "Save Simu." and type the name of the exported file. As there are three ports, the file is saved in a .s3p file.

# III.3.6 Comparison with measurement

In the "S parameter measurement" part, click on the button to import measurement files. They are in Touchstone format .s1p, .s2p, .s3p or .s4p. The tool can import measurements with up to four ports. Import the file xxx, select the quantity in "S parameter" list and the format in "Format" list. Finally, click on the button "Add meas." to plot the measurement results, as shown in the figure below.

# III.4 Simulation of the conducted immunity on the power supply of a microcontroller

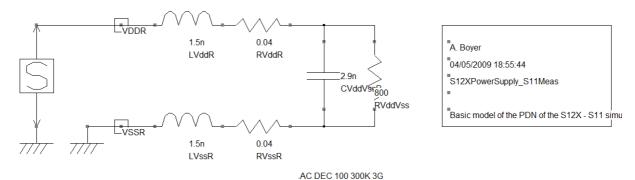

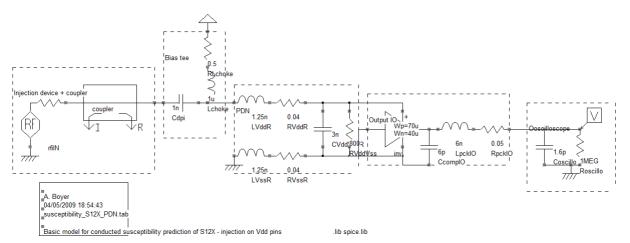

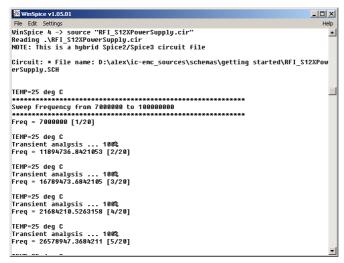

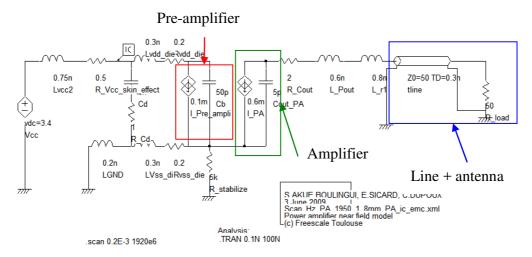

This example aims at presenting the flow to simulate the susceptibility of a circuit to radiofrequency interference (RFI). In this short case study, a sine wave disturbance is conducted on the power supply network of a digital circuit until the noise level measured on the pin of an output buffer exceeds a predefined noise margin. The circuit under test is a 16-bit microcontroller (HCS12X or S12X from Freescale Semiconductor). Conducted emission measurements are related to the standard IEC 62132-3 Direct Power Injection (DPI) method [IEC62-4]. The test covers the frequency range from 1 to 1000 MHz. The immunity model is based on an equivalent R,L,C circuit modeling the power distribution network (PDN) of the circuit, which was extracted from [s] parameter measurement.

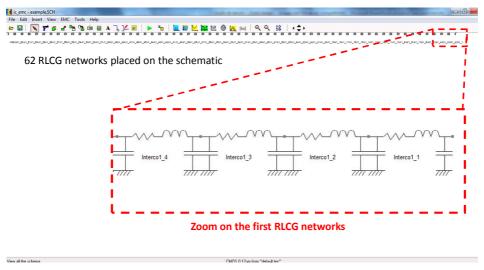

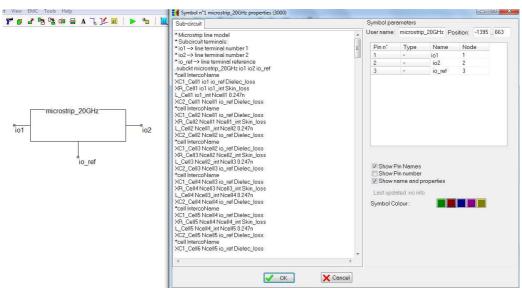

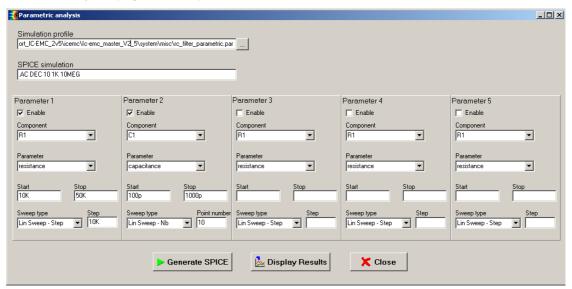

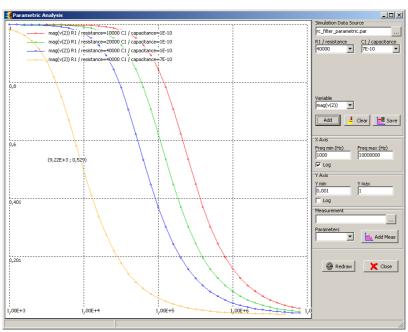

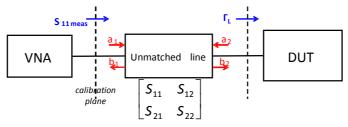

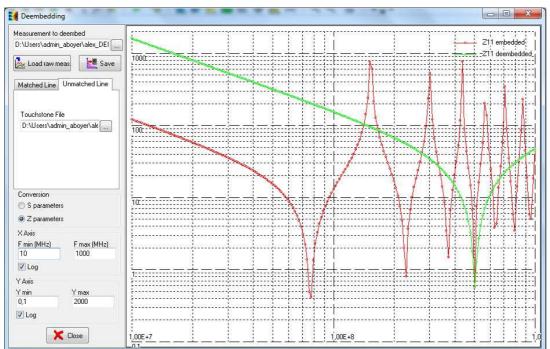

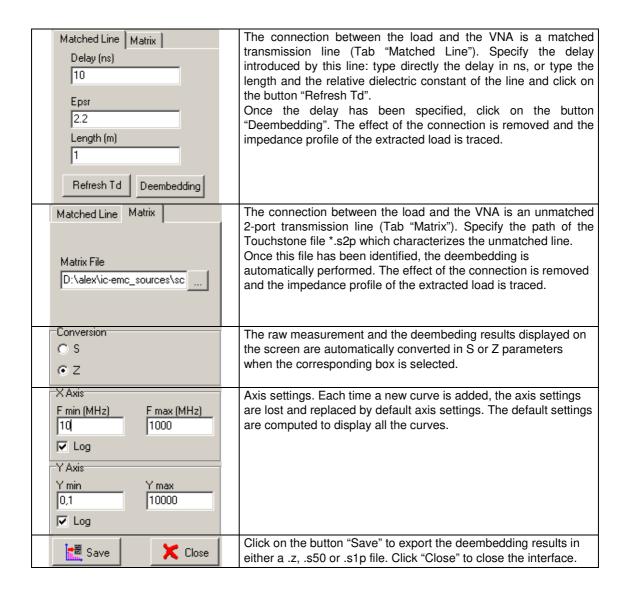

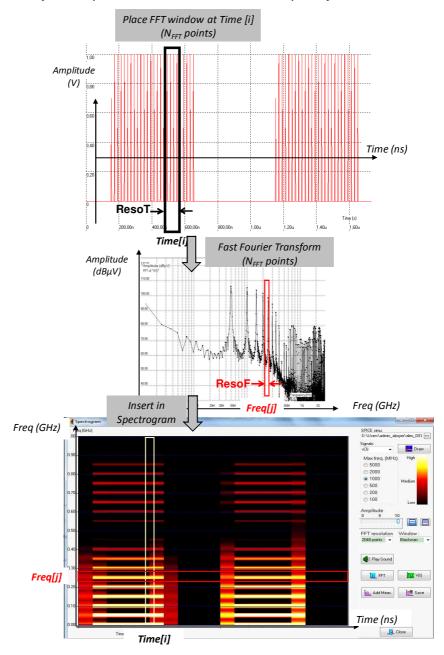

#### III.4.1 Load the S parameter simulation model