# High temperature ageing of microelectronics assemblies with SAC solder joints

Wissam Sabbah, Pierre Bondue, Oriol Aviño Salvado, Cyril Buttay, Héiène Frémont, Alexandrine Guédon-Gracia, Hervé Morel

### ▶ To cite this version:

Wissam Sabbah, Pierre Bondue, Oriol Aviño Salvado, Cyril Buttay, Hê<br/>iène Frémont, et al.. High temperature ageing of microelectronics assemblies with SAC solder joints. Microelectronics Reliability, 2017, 10.1016/j.microrel.2017.06.065 . hal-01564755

HAL Id: hal-01564755

https://hal.science/hal-01564755

Submitted on 19 Jul 2017

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## High Temperature Ageing of Microelectronics Assemblies with SAC Solder Joints

Wissam Sabbah<sup>b</sup>, Pierre Bondue<sup>a</sup>, Oriol Avino-Salvado<sup>b</sup>, Cyril Buttay<sup>b,\*</sup>, Hélène Frémont<sup>a</sup>, Alexandrine Guédon-Gracia<sup>a</sup>, Hervé Morel<sup>b</sup>

<sup>a</sup>University of Bordeaux, IMS Laboratory, UMR 5218, F-33405 TALENCE, France. <sup>b</sup>Univ Lyon, INSA-Lyon, CNRS, Laboratoire Ampére UMR 5005, F-69621, LYON, France

#### **Abstract**

In some applications, electronic systems are expected to operate at high ambient temperature (e.g. 150 °C). In this paper, we investigate the failure mechanism and microstructure evolution of solder-free (SAC) solder joints at a maximum temperature of 175 °C. It is found that no new failure mechanisms are triggered, and that ageing tests for solder can be accelerated at 175 °C. In particular, the growth rate of the interfacial intermetallic compound (IMC) is found to be consistent with that observed at lower temperatures.

#### 1. Review of high-temperature microelectronics assemblies

Electronic systems are increasingly used in harsh environment. For example, in automotive applications, some systems are expected to operate in close proximity to the engine, at ambient temperatures exceeding 120 °C [1]. Other examples include the control of power electronic systems [2]. Therefore, there is a need for microelectronics assemblies that are able to operate at 150 °C or more.

Some applications (such as down-hole data logging or aerospace) involve very high ambient temperatures (in excess to 200 or even 250 °C). They require specific assembly technologies, such as ceramic substrates, high temperature solders, etc. In particular, component attaches rely either on gold-based solder alloys, or on silver sintering [3, 4].

This paper focuses on temperatures ranges up to 175  $^{\circ}$ C, where it is desirable and conceivable to use more standard technologies such as PCBs and lead-free solders. These technologies are typically used at lower temperatures, and most papers only address temperatures up to 125  $^{\circ}$ C [5]. In some rare cases, the authors go up to 150  $^{\circ}$ C [6].

Therefore, there is a need to investigate the behaviour of lead-free solders at 175 °C. SnAg<sub>3</sub>Cu<sub>0.5</sub> (SAC305) solder is considered in this article. In particular, we will study the growth of the Intermetallic Compounds (IMCs) [7], which have an effect on the thermo-mechanical strength of the solder joints [8].

In this paper, we present such investigations, using two test conditions: temperature cycling, and isothermal ageing. They are described in the next section. The results are presented in section 3 and discussed in section 4.

#### 2. Test Protocol

The results presented in this paper were produced by two different teams. Schematically, one of the teams (Laboratoire

Ampère, Lyon) performed high temperature storage tests, while the other (IMS, Bordeaux) was in charge of the temperature cycling tests. Special care was taken at the analysis stage to produce consistent and comparable data.

#### 2.1. Sample Preparation

The results are based on Printed Circuit Board (PCB) material, on which ceramic capacitors are assembled with SAC 305 solder joints. The board material is polyimide (Arlon 85N), with a very high glass transition temperature (> 250 °C), and 6 layers of copper with a thickness of 70  $\mu$ m. Pad finish is ENIG (Ni: 6  $\mu$ m, Au: 80 nm). The boards were assembled by the company Elvia PCB (France).

The capacitors are Vishay VJ series (1210 package), with Ni terminals plated with 100 % Sn. The solder attach is a lead-free alloy (SAC305, HFA8.9 Series from Indium Corp.). Soldering was performed by the company Tronico (France). No cleaning of flux residues was performed afterwards. Ceramic capacitors were chosen for this study because they are fragile and large components, so they tend to be sensitive to thermomechanical stresses.

Before testing, the boards were cut into smaller coupons, using a diamond cut-off wheel (3000 RPM, 1 mm/s feed speed). No degradation of the PCB was observed (no burring of copper layers nor any trace of delamination). After cutting, the coupons were cleaned in water and ethanol, and dried to remove any lubricant residue. Before starting the actual tests, the samples were dried at least 6 h at 120 °C [9, 10].

#### 2.2. Characterization

The mechanical strength of the solder joints was measured through shear testing of the capacitors (5 capacitors were used for each data point). At Ampère, this was performed using a XYZTEC Condor Sigma tester, equiped with a 200 kgf load cell, a tool height of 350  $\mu$ m and a tool speed of 200  $\mu$ m/s. At IMS, a Dage 3000 tester, with a 100 kgf load cell, a tool height

Preprint submitted to Elsevier June 27, 2017

<sup>\*</sup>Corresponding author

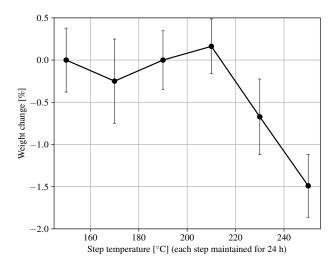

Figure 1: Weight change of unpopulated PCB test coupons during "step stress": each successive temperature step is maintained for 24 h, and one test coupon is removed from the oven at each step, for characterization (including weight measurement).

of 200  $\mu$ m and a tool speed of 100  $\mu$ m/s was used. The shear stress was calculated by dividing the rupture shear force by the maximum surface area of the solder joint (4.35 mm<sup>2</sup> per pad).

For each data point, two capacitors (i.e. 4 solder joints) were cross-sectioned and prepared for observation of the solder micro-structure. Once encapsulated and cut using a low-speed diamond saw, the samples were prepared as follows:

- at Ampère: Grit 1200 SiC paper (60 s), 10 μm diamond disk (120 s), followed by 3 and 1 μm diamond suspension on hard clothes (180 s each), and a coloidal silica finish on soft cloth (60 s). Final cleaning in water and ethanol;

- at IMS: Grits 1200 (150 s), 2400 (180 s) and 4000 (240 s) SiC paper, followed by 3 (240 s), 1 (300 s) and 1/4  $\mu$ m (180 s) diamond suspensions on hard clothes, and a colloidal silica (45 s) on soft cloth. This is specified in [6].

Observation of the micro-structure was performed mainly using SEMs (Tescan Vega 3 at Ampère, JEOL JSM-6100 at IMS, both equiped with EDS sensors for elemental analysis). One particular aspect was the measurement of the Intermetal-lic Compounds (IMC) layer thickness at the solder/capacitor and solder/PCB interfaces. For this, an interface length of 30-50  $\mu$ m was observed. At Ampère, we performed a series of 20 to 30 manual thickness measurements over this length. At IMS, the area of the IMC was identified through image processing (brightness threshold), and this area was divided by the length of the interface. Initial comparisons produced similar results for both methods.

Finally, electrical tests (capacitance measurements) were performed regularly at IMS to detect any damage to the capacitors. At Ampère, the assemblies were photographed before and after tests, using a Leica M205C binocular and a camera which settings were recalled to ensure consistent color rendering.

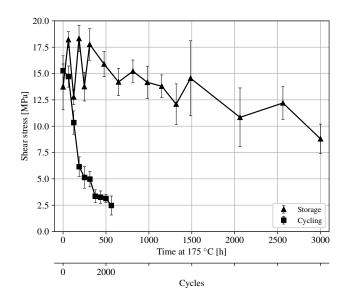

Figure 2: Shear strength of the capacitors as a function of the time spent at  $175\,^{\circ}\text{C}$ , for test vehicles submitted to storage or cycling conditions. The error bar corresponds to the standard deviation of the measurements.

#### 2.3. Reliability tests conditions

As a preliminary test, un-populated PCBs coupons were submitted to "step stressing": these coupons were placed in an oven, at a temperature of 150 °C. This temperature was increased by 20 °C every 24 h, up to 250 °C. At each step, one coupon was removed from the oven, and characterized. In particular, we measured its change in weight (Ohaus Adventurer Pro 210 scale, with a 1 mg resolution).

Fig. 1 shows that no noticeable weight loss was observed at 210 °C and below. A small weight loss (0.7 %) was observed after an additional 24 h step at 230 °C, and a slightly larger weight loss (1.5%) after 24 h at 250 °C. Overall, this weight loss remains very limited compared to that observed on FR4 boards in the same conditions (8% at 230 °C). This is confirmed by a second series of tests (not shown here), where PCBs using the same Arlon 85N material were stored in air for 1000 h at 190 °C without any noticeable weight loss. Such results are consistent with tests performed at higher temperature [11]. Therefore, one can consider that the tests presented hereafter (around 3000 h at 175 °C) should not result in degradation of the PCB material.

Based on these preliminary results, it was decided to conduct the reliability tests using the following parameters:

- Cycling tests: using a Rapid Temperature Change (RTC) chamber (Climats Excal 1423-TE), with temperature ramp-up and ramp-down slopes of 10 °C/min, a minimum temperature of -55 °C and a maximum temperature of 175 °C (both maintained for 15 min).

- Storage tests: in a forced convection oven (Nabertherm N30/45HA), at a constant temperature of 175 °C.

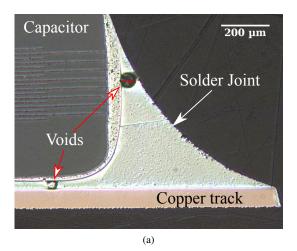

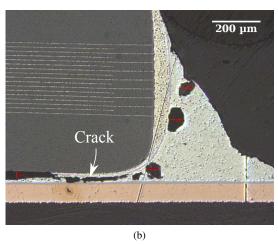

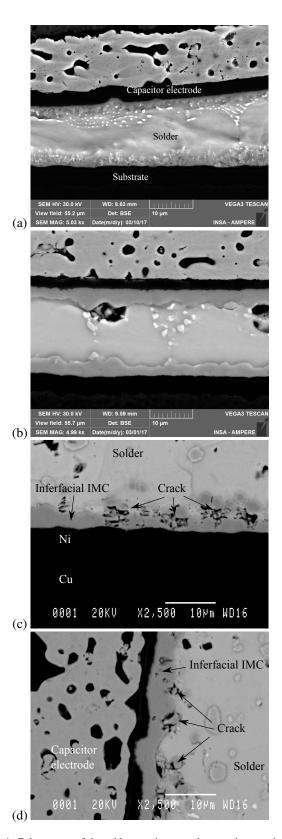

Figure 3: Cross section of solder joints, before testing (a) and after 750 cycles between -55 °C and 175 °C (b). A few voids are visible initially in Fig. (a). After cycling, a crack develops, first under the capacitor terminals, and eventually across the full solder joint.

#### 3. Results

The shear-test measurements are presented in Fig 2. Initially, the solder attach has a very good strength, as in most cases the rupture occurs partially in the capacitors. For the storage tests, the mechanical strength slowly decreases from  $\approx 15$  MPa at t=0 down to  $\approx 9$  MPa at t=3000 h.

For the cycling tests, however, the change is much more dramatic, with a strong reduction (80%) in shear strength after 2250 cycles (equivalent to 562 h at 175 °C).

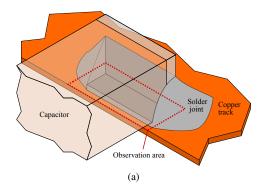

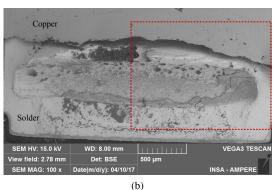

Cross-sections of some solder joints are presented in Fig. 3 (optical microscopy). In Fig. 3a, the solder joint was not submitted to any cycling test (initial conditions). This cross section is representative of the solder attaches, with some voiding. Indeed, a noticeable number of voids was found in most solder joints.

After 750 cycles (Fig. 3b), a crack is visible in the solder layer under the capacitor. Another observation is the change in the shape of the solder joint. As cycling progresses, the solder boundary roughens and becomes thinner on top of the meniscus.

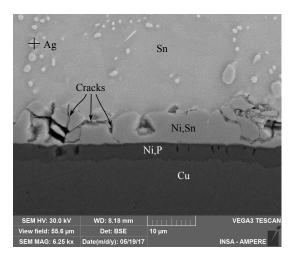

Figure 4: Enlargement of the solder area between the capacitor terminal and the PCB substrate. From top to bottom: cross section before testing (0 h), cross section after 310 h storage at 175  $^{\circ}$ C, substrate/solder interface after 1500 cycles (corresponding to 375 h at 175  $^{\circ}$ C), and capacitor (left)/solder interface, also after 1500 cycles.

SEM observations (Fig. 4) show a change in the interfacial microstructure of the solder joint: in initial conditions (Fig. 4a), the IMCs form a lamellar structure. After 310 h storage (Fig. 4b), the interfacial IMCs become continuous. In cycling tests (Figs. 4c and 4d for substrate and capacitor side, respectively) the interfacial IMCs also become continuous, but some voiding appears at the IMC/bulk solder interface. No such crack is observed in storage (310 h and 1500 cycles are equivalent in terms of time spent at 175 °C). This indicates that the cracks are generated by the thermo-mechanical stresses. This also means that the continuous IMC layers have little influence on the mechanical strength, as presented in Fig. 2.

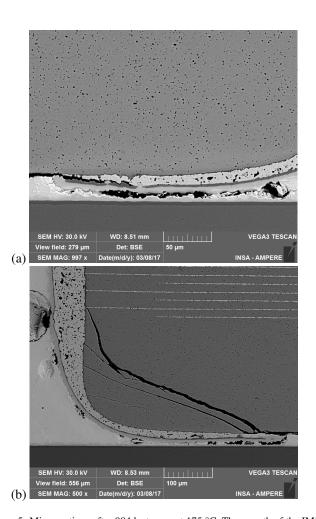

For longer storage periods, however, cracks start to appear between the capacitor and the substrate (Fig. 5). These cracks develop where the solder is the thinnest, and occur once the IMCs have grown to occupy the entire solder volume. However, this cracking has little influence on the shear strength, as visible in Fig. 2 (no drop in shear strength for samples stored for 984 h). This can be explained because the solder area under the capacitor terminals only represent a small part of the total joint. Another visible effect of storage ageing is the cracks observed on some capacitors (Fig. 5b). However, these are not observed on all capacitors. Only two capacitors were cross-sectioned per time step, so no statistics could be made regarding the effect of storage time on capacitor cracking.

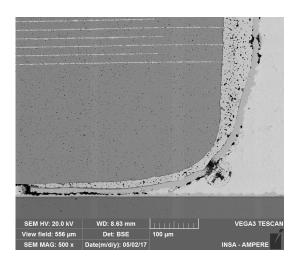

As storage time increases, the IMCs continue to grow, and voids develop all along the IMC/solder interface (Fig. 6), as was observed for the cycled samples in Fig. 4d. This is correlated with the continuous decrease in the shear strength, as plotted in Fig. 2.

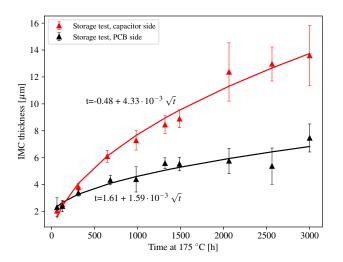

The thickness of the IMC layers, measured at the solder/substrate interface and at the solder/capacitor interface is shown in Fig. 7, as a function of storage time. The difference in the growth rate is related to the finish of the parts: the capacitors have a Sn finish, while the PCB has a NiAu finish.

Examples of some rupture surfaces observed for capacitors stored for 2062 h at 175 °C are given in Fig. 9. Several regions can be identified in Fig. 9c: region A corresponds to the solder located below the capacitor electrode. In this area, the shearing of the capacitor caused no smearing, indicating that the solder was completely separated from the capacitor electrode, as can be observed in Figs. 5 and 6. In region B, which corresponds to the "vertical" solder/capacitor interface in Figs. 5 and 6, some smearing can be observed. This indicates that the interface was not completely cracked. Also, many voids can be observed. Region C corresponds to the solder area located below the capacitor ceramic body (where no attach occured before or after ageing). Finally, in the right side, some leftovers of the capacitor electrode (Ni) can be seen. The solder layer underneath was larger (because the capacitor has rounded edges), and did not crack completely as the IMC grew, resulting in a better solder/metallization interface.

#### 4. Discussion

In thermal cycling, the capacitors showed a very fast reduction in the shear strength of their attach (6-fold reduction in 500

Figure 5: Microsections after 984 h storage at 175 °C. The growth of the IMC generated stresses that resulted in crack, either in the solder joints, in the capacitor metal finish, or in the capacitor body itself.

cycles). A large temperature swing (-55/+175 °C) was used. One objective is to determine whether the cycling tests caused the same failure mechanisms as observed at lower temperatures, or if new failure mechanisms were triggered. Storage tests were used to decouple the static and dynamic effects.

None of the the polyimide PCBs was found to be damaged by the long-term exposure to 175 °C. This is consistent with the specifications of the material, and with the preliminary tests presented in Fig. 1 with less than 1% weight loss after 24 h at 230 °C. All damages were found to be in relation with the solder layer: cracks propagated either at the solder interfaces, or in the capacitors, close to the solder joint.

The evolution of the solder interfacial microstructure is as follows: interfacial IMCs grow at different speeds at the capacitor and PCB interfaces; cracks propagate at the solder/IMC interface below the capacitor, where the solder joint is thinner and depletes quicker (Fig. 5); Finally the cracks develop along the complete Sn/IMC interface (Fig. 6). The IMC growth rate is plotted in Fig. 7. Previous tests [6] were performed at lower storage temperatures (80, 125 and 150 °C). After 1000 h, the IMC thicknesses were found to be 2.25, 2.5 and 3.6 µm respectively on a PCB with NiAu finish. This is consistent with the

Figure 6: Microsections of the solder joints after 2562 h storage at 175 °C, showing the propagation of the voiding along the IMC/solder interface.

Figure 7: Measured IMC layer thickness as a function of time spent at 175 °C, for different interfaces of the structure (capacitor terminals/solder, PCB/solder.

4 μm measured in this article. The test vehicles are, however quite different: Berthou *et al.* [6] investigated a BGA package, with SAC305 balls mounted on small PCB pads. Also, in our case, the cracks which appeared in the capacitors attach limited the growth of the IMC. With a different geometrical configuration, where the solder joint would be allowed to change in thickness without cracking, the mean IMC growth rate might be found to be faster.

The cracks occurred both in cycling and storage conditions, but they appeared sooner for cycling, and are related to two different mechanisms. For cycling, the rupture occurred along the brittle IMCs regardless of their position (Figs. 4c and d). In storage, they started under the capacitor electrodes, and were caused by the depletion of the solder joint due to the interfacial IMC growth.

Figure 8: Enlargement of the Substrate/Solder interface after 3000 h storage at  $175\,^{\circ}$ C. Many cracks appear at the interfacial IMC area. Ag forms precipitates (clear areas) in the bulk of the solder joint.

#### 5. Conclusion

In this article, we assessed the ageing of SAC305 solder joint submitted to cycling or storage conditions with a maximum temperature of 175 °C. It was found that the joints degrade rapidly, especially in cycling conditions. Except when short term operation is allowed (for example for testing purposes), the reliability of these joints is probably insufficient for most applications.

However, the ageing tests performed at 175 °C did not show any new failure mechanism compared to previous results obtained at lower temperatures. Therefore, it is possible to run ageing tests at 175 °C on SAC soldered assemblies to perform a faster reliability assessment.

The growth rate of the interfacial IMCs is consistent with the rates measured at lower temperatures, albeit on a different structure (solder bumps of a BGA package). A more accurate investigation would require testing of the same structure at different temperatures. This would allow to identify the activation energy of the ageing mechanism.

#### Acknowledgement

This work was funded as part of the GENOME-PREMICES initiative, in the scope of the "Programme d'Investissements d'Avenir" (Investment for the future) of CORAC (French Research Council for Civil Aeronautics).

#### 6. References

- J. G. Kassakian, D. J. Perreault, The Future of Electronics in Automobiles, in: Proceedings of the International Symposium on Power Semiconductor Devices and ICs (ISPSD), Osaka, Japan, 2001, pp. 15–19.

- [2] C. Buttay, D. Planson, B. Allard, D. Bergogne, P. Bevilacqua, C. Joubert, M. Lazar, C. Martin, H. Morel, D. Tournier, C. Raynaud, State of the art of high temperature power electronics, Materials Science and Engineering: B 176 (4) (2011) 283–288, microtechnology and Thermal Problems in Electronics. doi:10.1016/j.mseb.2010.10.003.

- URL http://www.sciencedirect.com/science/article/pii/ S0921510710006136

Voids

(A) Solder joint

Capacitor electrode (Ni)

SEM HV: 20.0 kV

VIew field: 1.63 mm

SEM MAG: 171 x

Date(m/dy): 04/10/17

INSA - AMPERE

(C)

Figure 9: Rupture surface on one side of the capacitor (sample stored for  $2062\,h$  at  $175\,^{\circ}\text{C}$ ): Observation area; overview of the breaking facies after shear test of the capacitor (travel direction of the shear tool was from right to left), zoom on the right area of the rupture surface.

- [3] V. Manikam, K. Y. Cheong, Die Attach Materials for High Temperature Applications: A Review, Components, Packaging and Manufacturing Technology, IEEE Transactions on 1 (4) (2011) 457–478. doi:10.1109/TCPMT.2010.2100432.

- [4] R. Khazaka, L. Mendizabal, D. Henry, R. Hanna, Survey of High-Temperature Reliability of Power Electronics Packaging Components, Power Electronics, IEEE Transactions on 30 (5) (2015) 2456–2464. doi:10.1109/TPEL.2014.2357836.

- [5] Z. Hai, J. Zhang, C. Shen, C. Zhao, J. L. Evans, M. J. Bozack, Effects on the reliability of lead-free solder joints under harsh environment, in: International Symposium on Microelectronics, Vol. 2014, International Microelectronics Assembly and Packaging Society, 2014, pp. 000471– 000476.

- [6] M. Berthou, P. Retailleau, H. Frémont, A. Guédon-Gracia, C. Jéphos-

Davennel, Microstructure evolution observation for SAC solder joint: Comparison between thermal cycling and thermal storage, Microelectronics Reliability 49 (9–11) (2009) 1267 – 1272, 20th European Symposium on the Reliability of Electron Devices, Failure Physics and Analysis20th European Symposium on the Reliability of Electron Devices, Failure Physics and Analysis. doi:http://dx.doi.org/10.1016/j.microrel.2009.07.040.

URL http://www.sciencedirect.com/science/article/pii/S0026271409002509

- [7] K. N. Subramanian (Ed.), Lead-Free Electronic Solders, Springer US, 2007. doi:10.1007/978-0-387-48433-4.

URL http://www.ebook.de/de/product/11429048/k\_n\_subramanian\_lead\_free\_electronic\_solders.html

- [8] S. Pin, H. Frémont, A. Gracia, Numerical study of thermomechanical fatigue influence of intermetallic compounds in a lead free solder joint, in: Electronic System-Integration Technology Conference (ESTC), 2016 6th, IEEE, 2016, pp. 1–6.

- [9] IPC, Ipc-1601a printed board handling and storage guidelines (2016).

- [10] I. Charrier, Y. Jouffrey, C. Villette, B. Dunn, Moisture pick-up and minimum drying conditions of epoxy and polyimide-glass printed circuit board (2005).

IJPL http://wiki.fod.do/inggg/8/89/Tactitut\_do.

- URL http://wiki.fed.de/images/8/88/Institut\_de\_

soudure.pdf

- [11] D. Shaddock, L. Yin, Reliability of high temperature laminates, in: International Conference and Exhibition on High Temperature Electronics Network (HiTEN), International Microelectronics Assembly and Packaging Society, 2015.