## Impact of Gate Drain Spacing on Low-Frequency Noise Performance of In Situ SiN Passivated InAlGaN/GaN MIS-HEMTs

Mehdi Rzin, Jean-Marc Routoure, Bruno Guillet, Laurence Méchin, Magali Morales, Cédric Lacam, Piero Gamarra, Pierre Ruterana, F Medjdoub

### ▶ To cite this version:

Mehdi Rzin, Jean-Marc Routoure, Bruno Guillet, Laurence Méchin, Magali Morales, et al.. Impact of Gate Drain Spacing on Low-Frequency Noise Performance of In Situ SiN Passivated In-AlGaN/GaN MIS-HEMTs. IEEE Transactions on Electron Devices, 2017, 64 (7), pp.2820-2825. 10.1109/TED.2017.2703809. hal-01560627

HAL Id: hal-01560627

https://hal.science/hal-01560627

Submitted on 11 Jul 2017

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

IEEE TRANSACTIONS ON ELECTRON DEVICES

# Impact of Gate—Drain Spacing on Low-Frequency Noise Performance of *In Situ* SiN Passivated InAlGaN/GaN MIS-HEMTs

Mehdi Rzin, Jean-Marc Routoure, Bruno Guillet, Laurence Méchin, Magali Morales, Cédric Lacam, Piero Gamarra, Pierre Ruterana, and Farid Medjdoub

Abstract—In this paper we investigated the gate—drain access region spacing  $(L_{GD})$  effect on electrical and noise performance of InAlGaN/GaN metal-insulator–semiconductor high electron mobility transistors (MIS-HEMTs) using in situ SiN cap layer as gate insulator. Different  $L_{GD}$  of InAlGaN/GaN MIS-HEMTs using sub-10 nm barrier layer are studied. Low-frequency noise measurements have been carried out for the first time in order to analyze the impact of the gate—drain spacing on the electrical characteristics. The noise of the channel under the gate has been identified as the dominant channel noise source for  $L_{GD} < 10~\mu m$ . Finally, the calculated Hooge parameter  $(\alpha_H)$  is equal to 3.1  $\times$  10 $^{-4}$ . It reflects the high material quality while using sub-10 nm InAlGaN layer, which is promising for high-frequency applications.

Index Terms—Channel resistance, gate—drain spacing, in situ sin passivation, InAlGaN/GaN, low-frequency noise (LFN), metal—insulator—semiconductor high electron mobility transistor (MIS-HEMT).

#### I. INTRODUCTION

AN-based high electron mobility transistors (HEMTs) have demonstrated their potential for telecommunication and power applications owing to the high electrical breakdown field (3.3 MV/cm) and the high electron mobility (2  $\times 10^3~\text{cm}^2 \cdot \text{V}^{-1} \cdot \text{s}^{-1})$  of GaN material [1]. Extensive research and technology development enabled GaN-based HEMTs to significantly improve over the last two decades.

Manuscript received March 22, 2017; revised May 6, 2017; accepted May 8, 2017. This work was supported by the Agence Nationale de la Recherche (ANR), France, under Contract ANR-14-CE26-0022 (LHOM). The review of this paper was arranged by Editor A. Haque.

M. Rzin, J-M. Routoure, B. Guillet, and L. Méchin are with Normandie Univ, UNICAEN, ENSICAEN, CNRS, GREYC, 14000 Caen, France (e-mail: mehdi.rzin@ensicaen.fr; jean-marc.routoure@unicaen.fr; bruno.guillet@unicaen.fr; laurence.mechin@ensicaen.fr).

M. Morales and P. Ruterana are with Normandie Univ, ENSICAEN, UNICAEN, CEA, CNRS, CIMAP, 14000 Caen, France (e-mail: magali.morales@ensicaen.fr; pierre.ruterana@ensicaen.fr).

C. Lacam and P. Gamarra are with the III-V Lab, Thales Research and Technology, 91767 Palaiseau, France (e-mail: cedric.lacam@3-5lab.fr; piero.gamarra@3-5lab.fr).

F. Medjdoub is with IEMN, 59650 Villeneuve d'Ascq, France (e-mail: farid.medjdoub@iemn.univ-lille1.fr).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TED.2017.2703809

Highly scaled GaN devices using the standard AlGaN barrier layer are inherently limited by short-channel effects due to low aspect ratio of the gate length to barrier layer thickness [3]. Moreover, the Al content and the thickness of AlGaN layer are limited by strain relaxation issues inducing cracks [4]. Lattice-matched AlInN has emerged as a promising alternative to AlGaN barrier layer due to the absence of stress and piezoelectric polarization [5]. AlInN spontaneous polarization is higher compared to AlGaN, allowing higher 2-DEG sheet carrier density. Also, AlInN has less surface depletion effects than AlGaN, which allows thinner barrier layers to be used while maintaining high aspect ratio down to short gate lengths with high 2-DEG charge density. The combination of AlGaN and AlInN as a quaternary (InAlGaN) allows to independently adjusting the bandgap and lattice constant to avoid the formation of cracks by controlling the builtin strain [6]. Also, the use of Al-rich InAlGaN layers has a great potential to enhance the carrier density and achieve highfrequency performances due to the increase of the spontaneous polarization [7]–[14].

One of the major factors hindering dynamic and power performance as well as the electrical reliability of GaN-based HEMTs is the gate leakage current that might increase under high electric field. In order to reduce the leakage current under the gate and/or in the gate-drain access region, the deposition of an in situ SiN passivation layer in the metal organic vapor phase epitaxy (MOVPE) reactor has been proposed and successfully applied. The insulator layer deposited in the same growth run as the III-N heterostructure reduces the relaxation, cracking and surface roughness of the barrier layer [15]. Moreover, the low growth rate and the high growth temperature of in situ SiN layer reduce the formation of surface states and improve the performance of the 2-DEG properties. The thickness of in situ SiN gate dielectric has a significant impact on the leakage current and may also affect the drain current.

Low-frequency noise (LFN) measurements are an effective tool to investigate the material/device quality and allows to study material defects [16], trapping effects and also to investigate the reliability of GaN-based HEMTs, especially when performed at various temperatures [17], [18].

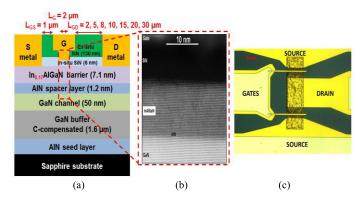

Fig. 1. (a) Schematic cross-sectional view. (b) TEM image. (c) Optical microscope image of  $Si_xN_y$ /InAlGaN/AIN/GaN HEMTs with two finger gates.

Besides, the *in situ* SiN passivation layer not only reduces significantly the gate leakage current but also potentially improves the low-frequency device noise performance [19].

In this paper, we report on the impact of the increase of gate—drain spacing ( $L_{\rm GD}$ ) on the performance of *in situ* SiN passivated InAlGaN/GaN MIS-HEMTs, grown on sapphire substrate.

A study of drain current LFN spectral density  $S_{\rm ID}$  is performed to identify the possible noise sources in the channel. By correlating the channel LFN contributions and the electrical parameters (maximum drain current, threshold voltage, transconductance, and leakage current), we point out that the *ex situ/in situ* SiN passivation layers interface is problematic for large  $L_{\rm GD}$  due to contaminants that induce trapping effects.

#### II. SAMPLE DETAILS

The InAlGaN/GaN heterostructure was grown by low-pressure MOVPE (LP-MOVPE) deposition on sapphire substrate. The devices under test have an average electron mobility of 1060 cm<sup>2</sup>  $\cdot$  V<sup>-1</sup>  $\cdot$  s<sup>-1</sup> and a sheet carrier density of 1.74  $\times$  10<sup>13</sup> cm<sup>-2</sup>, resulting in a sheet resistance of 340  $\Omega$ / $\square$ .

The heterostructure consists of a low-temperature GaN nucleation layer, a 1.6- $\mu$ m-thick highly resistive carbon-compensated GaN buffer layer, a 50-nm-thick nonintentionally doped GaN channel, followed by a 1.2-nm-thick AlN interlayer, and a 7.1-nm-thick-undoped InAlGaN layer. The given thicknesses are nominal values.

Ohmic contacts were formed directly on the top of the InAlGaN barrier layer by etching the *in situ* layer. A Ti/Al/Ni/Au metal stack was used, followed by a rapid thermal annealing at 875 °C. Device isolation was achieved by nitrogen implantation. A Ni/Au T-gate of 2  $\mu$ m length ( $L_G$ ) was defined by optical lithography. An additional *ex situ* SiN passivation layer of 130 nm is then deposited by plasmaenhanced chemical vapor deposition.

The device has two finger gates with a total gate width of  $W_G = 100 \ \mu \text{m}$ . In this paper, different gate-drain spacing from 2 to 30  $\mu \text{m}$  was studied [Fig. 1(c)]. The schematic of the HEMT heterostructure is displayed in Fig. 1(a).

High resolution annular dark field scanning transmission micrograph [Fig. 1(b)] exhibits chemical contrast and the

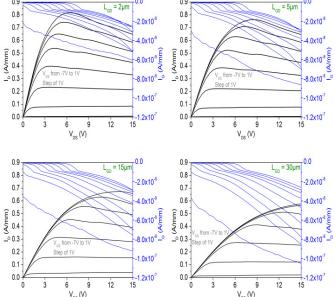

Fig. 2. Output characteristics of InAlGaN/GaN HEMTs with  $L_{\rm GD}=$  2, 5, 15, and 30  $\mu{\rm m}$  for  $V_{\rm GS}$  from -7 to 1 V.

low-z materials show a darker contrast, the observed areas are of extremely good crystalline quality with no defects [20]. As measured directly in this figure, the thickness of the layers is obtained by counting the visible (0002) lattice fringes (0.25 nm), and the agreement with the nominal thickness is attested with 1.2–1.3 nm of AlN, and 7.1–7.2 nm for the InAlGaN top layer.

#### III. RESULTS AND DISCUSSION

#### A. DC Measurements

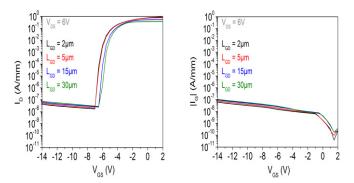

Fig. 2 shows the output  $I_D$ – $V_{DS}$  and  $I_G$ – $V_{DS}$  characteristics of InAlGaN/GaN HEMTs with  $L_{GD}=2$ , 5, 15, and 30  $\mu$ m for  $V_{GS}$  from -7 to 1 V.

The output characteristics of InAlGaN/GaN MIS-HEMTs with  $L_{\rm GD}=2\mu{\rm m}$  show a maximum drain current  $I_{D{\rm max}}(I_D$  at  $V_{\rm GS}=0$  V and  $V_{\rm DS}=10$  V) of about 800 mA/mm and drain-source resistance  $R_{\rm DS}=4$   $\Omega{\cdot}$  mm at  $V_{\rm GS}=1$  V. The increase of  $L_{\rm GD}$  from 2 to 30  $\mu{\rm m}$  induces a decrease of  $I_{D{\rm max}}$  and an increase of  $R_{\rm DS}$ . The degradation of  $I_D$  and  $R_{\rm DS}$  achieves, respectively 25% and 70% for  $L_{\rm GD}=30$   $\mu{\rm m}$  compared to  $L_{\rm GD}=2$   $\mu{\rm m}$ .

The gate leakage current ( $I_G$ ) increases with  $L_{\rm GD}$  as well, but not significantly and remains much lower than in devices with Schottky gate contact. For example,  $I_G=100$  nA/mm at  $V_{\rm GS}=-10$  V and  $V_{\rm DS}=15$  V.

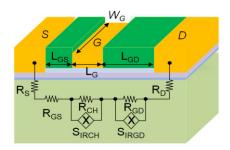

The drain–source resistance  $(R_{\rm DS})$  can be described as the sum of the source  $(R_S)$  and drain  $(R_D)$  contact resistances, the gate–source  $(R_{\rm GS})$  and gate–drain  $(R_{\rm GD})$  access region resistances, and the channel resistance under the gate  $R_{\rm CH}$  as shown in Fig. 3 and described in (1). Hereafter the resistance values are given in  $\Omega \cdot \text{mm}$  (normalized with 1-mm gate width)

$$R_{\rm DS} = R_S + R_{GD} + R_{\rm CH} + R_{\rm GS} + R_D.$$

(1)

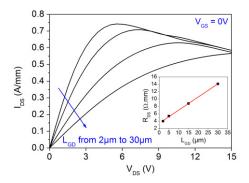

Fig. 4 shows  $I_D$ – $V_{DS}$  characteristics of InAlGaN/GaN HEMTs with  $L_{GD}=2$ , 5, 15, and 30  $\mu$ m at  $V_{GS}=0$  V and

Fig. 3. Schematic of the SiN/InAlGaN/AIN/GaN HEMT showing  $R_S$  and  $R_D$  contact resistances, channel resistance under the gate  $R_{\rm CH}$  and in access regions  $R_{\rm GS}$  and  $R_{\rm GD}$ , and current source noise of the channel under the gate  $SI_{\rm RCH}$  and in gate—drain access region  $SI_{\rm RGD}$ .

Fig. 4.  $I_{\rm D}-V_{\rm DS}$  of InAlGaN/GaN HEMTs at  $V_{\rm GS}=0$  V with  $L_{\rm GD}=2$ , 5, 15, and 30  $\mu{\rm m}$ . Inset:  $R_{\rm DS}$  as function of  $L_{\rm GD}$ .

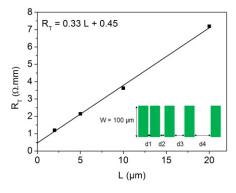

Fig. 5. Normalized TLM total resistance  $R_T$  versus lead separation L.

the inset shows the linear dependence of the drain-source resistance ( $R_{DS}$ ) on the gate-drain spacing ( $L_{GD}$ ) as follows:

$$R_{\rm DS} = \beta L_{\rm GD} + \gamma \,. \tag{2}$$

$R_S$ ,  $R_D$ , and  $R_{GS}$  are extracted from transmission line model (TLM) structures with  $W=100~\mu \text{m}$  and four lengths (L=2, 5, 10, and  $20~\mu \text{m}$ ) as shown in Fig. 5.

From the fitting of experimental data (see dotted line in the inset of Fig. 4)

$$R_{\rm DS} = 0.35 \ L_{\rm GD} + 3.42(\Omega \cdot \text{mm}).$$

(3)

The total TLM resistance  $R_T$  in ohm is described by (4) having two terms. The first term is directly proportional to L, the separation between leads, and accounts for the contribution of the sheet resistance  $R_{\text{sheet}}$ . The second term is twice the

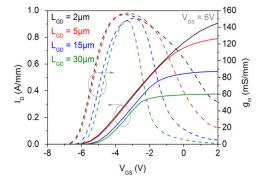

Fig. 6.  $\it I_D-V_{\rm GS}$  and  $g_m-V_{\rm GS}$  of InAlGaN/GaN HEMTs with  $\it L_{\rm GD}=2,5,$  15, and 30  $\mu\rm m$  at  $\it V_{\rm DS}=6$  V.

Fig. 7.  $I_D$ – $V_{\rm GS}$  and  $|I_G|$ – $V_{\rm GS}$  in logarithmic scale of InAlGaN/GaN HEMTs with  $L_{\rm GD}=$  2, 5, 15, and 30  $\mu{\rm m}$  at  $V_{\rm DS}=$  6 V.

contact resistance  $R_C$

$$R_T = \frac{R_{\text{sheet}}}{W} L + 2R_C. \tag{4}$$

From the fitting of experimental data (see dotted line showed in Fig. 5) the normalized  $R_T$  is as follows:

$$R_T = 0.33L + 0.45(\Omega \cdot \text{mm}).$$

(5)

From (4) and (5),  $R_C = R_S = R_D = 0.22 \ (\Omega \cdot \text{mm})$  and the sheet resistance  $R_{\text{sheet}} = 333 \ \Omega/\Box$  similar to the value obtained by Hall measurements.

Gate–source resistance is obtained by the following equation with  $L_{GS} = 1 \mu m$ :

$$R_{\rm GS} = 0.35 \ L_{\rm GS}(\Omega \cdot \rm mm). \tag{6}$$

From (3), (5), and (6), we extract the values of  $R_{\rm GS} = 0.35~\Omega \cdot {\rm mm}$  and  $R_{\rm CH} = 2.63~\Omega \cdot {\rm mm}$ .

$I_D-V_{\rm GS}$  and  $g_m-V_{\rm GS}$  characteristics of MIS-HEMTs with  $L_{\rm GD}$  from 2 to 30  $\mu$ m at  $V_{\rm DS}=6$  V are reported in Fig. 6. Devices with  $L_{\rm GD}=2~\mu{\rm m}$  show a threshold voltage of -5.4 V. The threshold voltage is shifted to positive values by increasing  $L_{\rm GD}$  to achieve -4.7 V for  $L_{\rm GD}=30~\mu{\rm m}$ . This shift occurs also at very low  $V_{\rm DS}$  ( $V_{\rm DS}<0.3$  V) at which trapping effects are minimal. Moreover, the peak transconductance and the transconductance width decrease by increasing  $L_{\rm GD}$ . The gate and drain subthreshold leakage currents remain below 100 nA/mm for all the gate–drain spacing (Fig. 7), which show the efficiency of the *in situ* SiN passivation.

Fig. 8. PSD of the drain current  $S_{\rm ID}$  of InAlGaN/GaN HEMTs with  $L_{\rm GD}=2,5,8,$  and 30  $\mu{\rm m}$  at  $V_{\rm GS}=0$  V and for  $I_{\rm DS}$  from 1 to 10 mA at room temperature.

The increase of  $L_{\rm GD}$  induces the rise of the 2-DEG channel resistance which causes the decrease of the output current and the peak transconductance. Since *in situ* SiN/InAlGaN interface is considered of high quality [21], we assume that the increase of the drain–source resistance is caused by the increase of gate–drain access resistance.

#### B. Low-Frequency Noise Measurements

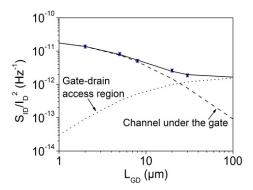

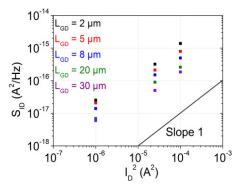

The LFN measurement is used first as a figure of merit to investigate the material and device quality. By using the measurements performed on various gate–drain spacing, it has been possible to distinguish channel and access region noise and thus to calculate the Hooge figure of merit for the channel contribution. The power spectral density (PSD) of the drain current  $S_{\rm ID}$  was measured in the linear regime at  $V_{\rm GS}=0$  V for  $I_D$  from 1 to 10 mA to identify the dominant noise sources in the channel with different gate–drain spacing ( $L_{\rm GD}$ ).

The PSD of the drain current ( $S_{\rm ID}$ ) is shown in Fig. 8 for different  $L_{\rm GD}$ .  $S_{\rm ID}$  varies as  $1/f^{\gamma}$  type spectra with  $\gamma$  close to 1. It is worth mentioning that the noise measurements were carried out on fresh devices under stationary conditions and were reproducible. No distinct generation–recombination noise components were identified.

The PSD of the drain current decreases by increasing  $L_{\rm GD}$  from 2 to 30  $\mu$ m. Chiu *et al.* [22] have reported on an increase of  $S_{\rm ID}/I_D^2$  with  $L_{\rm GD}$  extension of AlGaN/GaN HEMTs and associated the enhancement of LFN to the increase of  $R_{\rm on}$ .

The  $1/f^{\gamma}$  noise of  $S_{\text{ID}}$  is extracted from the spectrum at f=1 Hz and plotted as function of the square of

Fig. 9. Dependence of the relative PSD of the drain current  $S_{\text{ID}}/l_D^2$  on the gate–drain spacing  $L_{\text{GD}}$  in the linear regime at f=1 Hz,  $V_{\text{GS}}=0$  V, and T=300 K. Dashed line represents the channel noise contribution under the gate. Dotted line shows the noise channel contribution in gate–drain access region. Solid line shows total channel noise.

the drain current  $(I_D^2)$ . The experimental points representing the normalized PSD  $(S_{\rm ID}/I_D^2)$  of the drain current are plotted against the gate-drain spacing in the linear regime at  $V_{\rm GS}=0$  V at 300 K in Fig. 9.

The  $S_{\text{ID}}/I_D^2$  dependence on  $L_{\text{GD}}$  is analyzed by considering two noise sources in the channel: channel noise under the gate and channel noise in the gate–drain access region.

The source noise of the gate-source access region is not considered in our model since it is not dominant. Since,  $L_{\rm GS}=1~\mu{\rm m}$ , the gate-source noise contribution is similar to the one of gate-drain access region for  $L_{\rm GD}=1~\mu{\rm m}$  (Fig. 9).

Based on the assumptions considered above and that the noises originating from these regions are uncorrelated, the relative PSD of the drain current can be presented as follows:

$$\frac{S_{I_D}}{I_D^2} = \frac{R_{\text{CH}}^2}{R_{\text{DS}}^2} \frac{S_{\text{IRCH}}}{I_D^2} + \frac{R_{\text{GD}}^2}{R_{\text{DS}}^2} \frac{S_{\text{IRGD}}}{I_D^2}$$

(7)

where  $S_{IRCH}$ ,  $S_{IRGD}$  are the drain current source noise of the channel under the gate and in the gate–drain access region, respectively.

By replacing  $R_{\rm GD}$  with its dependence on  $L_{\rm GD}$  from (3), (7) becomes

$$\frac{S_{I_D}}{I_D^2} = \frac{R_{\text{CH}}^2}{(\beta L_{GD} + \gamma)^2} \frac{S_{\text{IRCH}}}{I_D^2} + \frac{\beta L_{\text{GD}}^2}{(\beta L_{\text{GD}} + \gamma)^2} \frac{S_{\text{IRGD}}}{I_D^2}.$$

(8)

Dashed line in Fig. 9 represents the channel noise contribution under the gate calculated by the first term of (8). The experimental points fit well this contribution for  $L_{\rm GD} < 10~\mu \rm m$ . The dotted line corresponding to the channel noise contribution in the gate–drain access region is obtained from the second term of (8). It allows to compensate the slight difference between the experimental points and the channel under the gate contribution for  $L_{\rm GD} > 10~\mu \rm m$ .

Solid line representing the total channel noise fits well the experimental points. This result shows that the dominant channel source noise contribution at  $V_{\rm GS}=0$  V is located under the gate and a slight contribution of gate–drain access region is noticed for  $L_{\rm GD}>10~\mu{\rm m}$ .

A dependence of  $S_{\rm ID}$  proportional to  $I_D^2$  is seen for the different  $L_{\rm GD}$  in Fig. 10. The Hooge parameter ( $\alpha_{\rm H}$ ) associated

Fig. 10. PSD of the drain current  $S_{\rm ID}$  at 1 Hz as function of drain current square with  $L_{\rm GD}=$  2, 5, 8, 20, and 30  $\mu{\rm m}$ .

with the channel noise under the gate can be written as

$$\frac{S_{I_D}}{I_D^2} = \frac{\alpha_H}{Nf} \tag{9}$$

where f is the frequency and N is the total number of carriers in the channel under the gate.

The number of carriers is given by

$$N = \frac{L_{\rm CH}^2}{q\,\mu\,R_{\rm CH}}\tag{10}$$

where q is the electron charge,  $\mu$  is the mobility in the channel,  $R_{\text{CH}}$  is the channel resistance under the gate and  $L_{\text{CH}}$  is the channel length.

The Hooge parameter has been calculated for the smallest  $L_{\rm DS}$  device for which the access region noise is negligible. It is equal to  $3.1 \times 10^{-4}$ . The value of this parameter, considered as a figure of merit for the InAlGaN/GaN interface quality, is in the range of  $10^{-3} - 10^{-4}$ , pointing out the good quality of InAlGaN/GaN interface [23]–[25]. This paper shows the first LFN measurements on InAlGaN/GaN HEMTs using sub-10 nm InAlGaN layer and *in situ* SiN passivation layer. Sub-10 nm InAlGaN quaternary barrier combined with *in situ* SiN passivation layer are promising to enhance the performance of GaN-based HEMTs.

#### IV. CONCLUSION

The effect of gate-drain spacing on the electrical and noise performance of InAlGaN/GaN MIS-HEMTs by using *in situ* SiN passivation layer was investigated by dc and LFN measurements.

The increase of  $L_{\rm GD}$  induces the degradation of the maximum drain current and the transconductance and a positive shift of the threshold voltage. The subthreshold leakage current remains very low (<100 nA/mm) and does not increase significantly with  $L_{\rm GD}$  which demonstrates the efficiency of the *in situ* SiN passivation.

The PSD of the drain current varies as  $1/f^{\gamma}$  noise without distinct generation–recombination noise components. The noise level decreases with  $L_{\rm GD}$ . The channel noise under the gate is the main contribution of the total channel noise for  $L_{\rm GD} < 10~\mu{\rm m}$  while a nonnegligible contribution of the gate–drain access region is noticed for  $L_{\rm GD} > 10~\mu{\rm m}$ . The low value of the Hooge parameter of the dominant channel noise  $(3.1 \times 10^{-4})$  indicates a high InAlGaN/GaN interface quality while using sub-10 nm InAlGaN barrier layer.

In order to use  $L_{\rm GD} > 10~\mu{\rm m}$  to enhance the breakdown voltage of this process, a careful engineering of the *in situ* SiN/ex situ passivation layers interface is needed.

#### REFERENCES

- R. Gaska et al., "Electron transport in AlGaN-GaN heterostructures grown on 6H-SiC substrates," Appl. Phys. Lett., vol. 72, no. 6, pp. 707-709, 1998.

- [2] O. Ambacher et al., "Two-dimensional electron gases induced by spontaneous and piezoelectric polarization charges in N- and Ga-face AlGaN/GaN heterostructures," J. Appl. Phys., vol. 85, no. 6, pp. 3222–3333, Mar. 1999.

- [3] G. H. Jessen et al., "Short-channel effect limitations on high-frequency operation of AlGaN/GaN HEMTs for T-gate devices," IEEE Trans. Electron Devices, vol. 54, no. 10, pp. 2589–2597, Oct. 2007.

- [4] S. Einfeldt et al., "Strain relaxation in AlGaN under tensile plane stress," J. Appl. Phys., vol. 88, no. 12, pp. 7029–7036, Dec. 2000.

- [5] F. Medjdoub, J. F. Carlin, C. Gaquière, N. Grandjean, and E. Kohn, "Status of the emerging InAlN/GaN power HEMT technology," *Open Elect. Electron. Eng. J.*, vol. 2, pp. 1–7, Jan. 2008.

- [6] Y. Liu, T. Egawa, and H. Jiang, "Enhancement-mode quaternary AlInGaN/GaN HEMT with non-recessed-gate on sapphire substrate," *Electron. Lett.*, vol. 42, no. 15, pp. 884–886, Jul 2006

- [7] Y. Liu, H. Jiang, S. Arulkumaran, T. Egawa, B. Zhang, and H. Ishikawa, "Demonstration of undoped quaternary AlInGaN/GaN heterostructure field-effect transistor on sapphire substrate," *Appl. Phys. Lett.*, vol. 86, no. 22, p. 223510, 2005.

- [8] T. Lim et al., "GaN-based submicrometer HEMTs with lattice-matched InAlGaN barrier grown by MBE," IEEE Electron Device Lett., vol. 31, no. 7, pp. 671–673, Jul. 2010.

- [9] R. Wang et al., "Quaternary barrier InAlGaN HEMTs with f<sub>T</sub>/f<sub>max</sub> of 230/300 GHz," *IEEE Electron Device Lett.*, vol. 34, no. 3, pp. 378–380, Mar. 2013.

- [10] N. Ketteniss et al., "Study on quaternary AllnGaN/GaN HFETs grown on sapphire substrates," Semicond. Sci. Technol., vol. 25, no. 7, p. 075013, Jun. 2010.

- [11] F. Medjdoub et al., "High electron mobility in high-polarization sub-10 nm barrier thickness InAlGaN/GaN heterostructure," Appl. Phys. Exp., vol. 8, no. 10, p. 101001, 2015.

- [12] E. Dogmus et al., "InAlGaN/GaN HEMTs at cryogenic temperatures," Electronics, vol. 5, no. 2, p. 31, 2016.

- [13] Y. Niida et al., "3.6 W/mm high power density W-band InAlGaN/GaN HEMT MMIC power amplifier," in Proc. IEEE Topical Conf. Power Amplif. Wireless Radio Appl. (PAWR), Jan. 2016, pp. 24–26.

- [14] R. Aubry et al., "ICP-CVD SiN passivation for high-power RF InAlGaN/GaN/SiC HEMT," IEEE Electron Device Lett., vol. 37, no. 5, pp. 629–632, May 2016.

- [15] J. Derluyn et al., "Improvement of AlGaN/GaN high electron mobility transistor structures by in situ deposition of a Si<sub>3</sub>N<sub>4</sub> surface layer," J. Appl. Phys., vol. 98, no. 5, p. 054501, 2005.

- [16] G. R. Mutta et al., "Volume charge carrier number fluctuations probed by low frequency noise measurements in InN layers," Appl. Phys. Lett., vol. 98, no. 25, p. 252104, 2011.

- [17] M. Rzin, A. Curutchet, N. Labat, N. Malbert, L. Brunel, and B. Lambert, "Schottky gate of AlGaN/GaN HEMTs: Investigation with DC and low frequency noise measurements after 7000 hours HTOL test," in *Proc. Int. Conf. Noise Fluctuations (ICNF)*, Xi'an, China, Jun. 2015, pp. 1–4, doi: 10.1109/ICNF.2015.7288607.

- [18] H. Rao and G. Bosman, "Device reliability study of high gate electric field effects in AlGaN/GaN high electron mobility transistors using low frequency noise spectroscopy," J. Appl. Phys., vol. 108, no. 5, p. 053707, 2010.

- [19] A. V. Vertiatchikh and L. F. Eastman, "Effect of the surface and barrier defects on the AlGaN/GaN HEMT low-frequency noise performance," *IEEE Electron Device Lett.*, vol. 24, no. 9, pp. 535–537, Sep. 2003.

- [20] F. Gloux, T. Wojtowicz, P. Ruterana, K. Lorenz, and E. Alves, "Transmission electron microscopy investigation of the structural damage formed in GaN by medium range energy rare earth ion implantation," *J. Appl. Phys.*, vol. 100, no. 7, p. 073520, 2006.

- [21] P. Moens et al., "An industrial process for 650 V rated GaN-on-Si power devices using in-situ SiN as a gate dielectric," in Proc. IEEE 26th Int. Symp. Power Semiconductor Devices (ISPSD), Waikoloa, HI, USA, Jun. 2014, pp. 374–377.

- [22] H.-C. Chiu, C.-W. Yang, H.-C. Wang, F.-H. Huang, H.-L. Kao, and F.-T. Chien, "Characteristics of AlGaN/GaN HEMTs with various fieldplate and gate-to-drain extensions," *IEEE Trans. Electron Devices*, vol. 60, no. 11, pp. 3877–3882, Nov. 2013.

- [23] S. L. Rumyantsev et al., "On the low frequency noise mechanisms in GaN/AlGaN HFETs," Semicond. Sci. Technol., vol. 18, no. 6, pp. 589–593, 2003.

- [24] H. Rao and G. Bosman, "Simultaneous low-frequency noise characterization of gate and drain currents in AlGaN/GaN high electron mobility transistors," J. Appl. Phys., vol. 106, no. 10, p. 103712, 2009.

- [25] H. Zhou et al., "High-performance InAlN/GaN MOSHEMTs enabled by atomic layer epitaxy MgCaO as gate dielectric," *IEEE Electron Device* Lett., vol. 37, no. 5, pp. 556–559, May 2016.

Magali Morales received the Ph.D. degree in physics from University Joseph Fourier, Grenoble, France, in 1999.

She is currently an Associate Professor with the University of Caen, Caen, France. She has authored or co-authored more than 55 papers. Her current research interests include single crystalline or textured thin films and their structural, microstructural and compositional characterization using diffraction (X-ray, neutron or electron diffraction), and X-ray

fluorescence or Ion Beam Analysis techniques.

Mehdi Rzin received the Ph.D. degree in electrical engineering from the University of Bordeaux, Bordeaux, France, in 2015.

He is currently a Post-Doctoral Researcher with the GREYC Laboratory, University of Normandie, Caen, France. His current research interests include electrical characterization and low-frequency noise analysis of GaN-based high electron mobility transistors.

**Cédric Lacam** received the master's degree in material science and engineering from the University of Saclay, Orsay, France, in 2011.

He is currently a MOCVD Process Engineer with the III-V Lab, Palaiseau, France. His current research interests include the growth and characterization of GaN-based heterostructure for electronic and optoelectronic devices, such as high-power RF HEMTs, vertical p-n diodes, and emissive microdisplays.

**Jean-Marc Routoure** received the Ph.D. degree in electronics from the University of Caen, Caen, France, in 1998.

In 2000, he joined the Electronics Team of the GREYC Laboratory, University of Caen, France. He is currently a Professor with the University of Caen. He is involved in low-frequency noise of integrated polysilicon resistors, manganese oxide compounds, and advanced CMOS and III/V devices. He has authored or coauthored 100 papers in international journals and conferences.

**Piero Gamarra** received the Ph.D. degree in material science from the University of Lyon, Lyon, France, in 2012.

He is currently a Senior Scientist in charge of the III-N growth activities with the III-V Lab and Thales Research and Technology, Palaiseau, France. He holds 2 patents and he has authored or co-authored over 20 paper in peer-reviewed journals.

Bruno Guillet received the Ph.D. degree and accreditation to supervise research in electronics-microelectronics from the University of Caen, Caen, France, in 2003 and in 2014, respectively.

He is currently an Associate Professor of Electronics with the University of Caen. He is involved in noise measurements, resistive thermometry, and bolometers. He has authored or co-authored 35 publications in peer-reviewed journals.

Pierre Ruterana is a Specialist in quantitative high-resolution electron microscopy with applications to many materials including semiconductors, ceramics, catalysts, and nanomaterials. In 1991, he joined CNRS, since then he has been trained more than 20 Ph.D. students, collaborated in national and international projects, coordinating many of them. He has authored more than 300 scientific publications in peerreviewed journals.

Laurence Méchin received the Ph.D. degree in electrical engineering from the University of Caen, Caen, France, in 1996.

She is currently a CNRS Senior Scientist with GREYC, Caen, France. She has authored or co-authored more than 100 papers. Her current research interests include the design, fabrication, and characterization of innovative materials such as functional oxides and nitrides for sensors and components.

**Farid Medjdoub** received the Ph.D. degree in electrical engineering from the University of Lille, Lille, France, in 2004.

He is currently a CNRS Senior Scientist with IEMN, Villeneuve d'Ascq, France. He is also part of the French observatory of wide-bandgap devices. He has authored or co-authored more than 100 papers. He holds several patents. His current research interests include the design, fabrication, and characterization of innovative GaN-based devices.