## Microstructuration of Silicon Surfaces Using Nanoporous Gold Electrodes

<u>E. Torralba<sup>1</sup></u>, M. Halbwax<sup>2</sup>, T. El Assimi<sup>1</sup>, V. Magnin<sup>2</sup>, J. Harari<sup>2</sup>, J.-P. Vilcot<sup>2</sup>, S. Le Gall<sup>3</sup>, R. Lachaume<sup>3</sup>, C. Cachet-Vivier<sup>1</sup>, S. Bastide<sup>1</sup>

<sup>1</sup> Institut de Chimie et des Matériaux Paris-Est, CNRS, Univ. Paris-Est, France

<sup>2</sup> Institut d'Electronique, de Microélectronique et de Nanotechnologie, CNRS, Univ. Lille 1, France

<sup>3</sup> Génie Electrique et Electronique de Paris, CNRS, SUPELEC, Univ. Paris-Sud XI, France torralba-penalver@icmpe.cnrs.fr, bastide@icmpe.cnrs.fr

Etching is a key process in the fabrication of silicon (Si) microstructures that are essential for several component families used in microelectronics, photonics and photovoltaics, among others. A large variety of microstructuring technologies exists nowadays (e.g. wet/dry etchings based on photo/electron beam lithography patterning). Their remarkable efficacy comes at the expense of several lithography (masking) /etching steps that are not suitable for all industries, i.e. when reduced cost and manufacturing time are key aspects (e.g. Si solar cells manufacturing). Hence, the development of a maskless technique with direct imprinting of patterns would dramatically simplify the fabrication process. However, eliminating the use of masks and move towards micromachining techniques has turned to be extremely challenging. Only a few achievements in the field of (electro)chemistry have been reported in the literature [1-4].

The most recent development is an electrochemical version of the *metal assisted chemical etching* method used to produce high aspect ratio nanostructures: a noble metal electrode is put in contact with a Si sample in a HF solution and polarized against a counter electrode; in the contacted areas the metal plays the role of etching tool by oxidizing/dissolving Si atoms [2,3]. The major problem encountered with this configuration lies in the intimate Si/metal contact, which hinders electrolyte supply over macroscopic distances. Hence, etching is very slow, starting from the edge of the metal tool and progressing laterally. An efficient pattern transfer has been recently demonstrated in the case of porous Si etching with a gold coated stamp, the porous Si network allowing the electrolyte to reach the Si/Au interface [4].

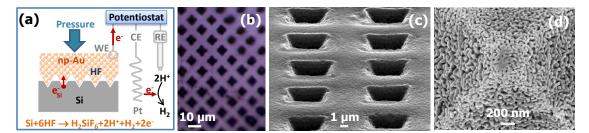

In this work, we present a new strategy to achieve pattern transfer into Si by a single step electrochemical (EC) contact etching with large dimension metal tools, as schemed in Figure 1a.

Figure 1. a) Scheme of the electrochemical contact etching process; b, c) optical and SEM images of a n-type (100) Si surface after imprinting a pattern of inverted pyramids with d) a nanoporous Au electrode.

The problematic diffusion of the electrolyte is solved by using for the first time nanoporous metal electrodes, which give access for the electrolyte to the whole Si/metal interface. Thus, etching is achieved with a priori no restriction on the dimensions of the treated surfaces.

Our first results demonstrate the transfer of a well-defined array of square inverted pyramids over a treated area of approximately 1 mm<sup>2</sup> (Figure 1b and 1c) in a single step and without any prior lithography or masking process of the substrate. The etched pyramids are not aligned with the [001] and [010] directions of the (100) oriented sample ( $21^{\circ}$  off) which clearly indicate that the pattern transfer is independent of the crystallographic orientation. This is a proof of concept for EC contact etching with nanoporous metal imprints, with a high potential for Si surface texturization (e.g. solar cells) [5].

[1] P. Allongue, P. Jiang, V. Kirchner, A.L. Trimmer, R. Schuster J. Phys. Chem. B. 108 (2004) 98.

[2] T. Sugita, C.-L. Lee, S. Ikeda, M. Matsumura ACS Appl. Mater. Interfaces 3 (2011) 2417.

[3] T. Fukushima, A. Ohnaka, M. Takahashi, H. Kobayashi Electrochem. Solid-State Lett. 14 (2011) B13.

[4] P. Azeredo, Y. Lin, A. Avagyan, M. Sivaguru, K. Hsu, P. Ferreira Adv. Func. Mater. 26 (2016) 2929.

[5] E. Torralba et al. ACS Appl. Mater. Interfaces 8 (2016) 31375.