## Discussion sur le suivi de l'état de santé des modules de puissance constitués de MOSFET en carbure de silicium

Malorie Hologne, Pascal Bevilacqua, Antoine Barrière, Bruno Allard, Jacques Jay, Guy Clerc, Hubert Razik

### ▶ To cite this version:

Malorie Hologne, Pascal Bevilacqua, Antoine Barrière, Bruno Allard, Jacques Jay, et al.. Discussion sur le suivi de l'état de santé des modules de puissance constitués de MOSFET en carbure de silicium. JCGE, May 2017, Arras, France. pp.141985. hal-01534708

## HAL Id: hal-01534708 https://hal.science/hal-01534708v1

Submitted on 8 Jun 2017

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## Discussion sur le suivi de l'état de santé des modules de puissance constitués de MOSFET en carbure de silicium

Malorie HOLOGNE, Pascal BEVILACQUA, Antoine BARRIERE\*, Bruno ALLARD, Jacques JAY\*, Guy CLERC et Hubert RAZIK

Univ Lyon, UCB Lyon1, INSA, CNRS, AMPERE, CETHIL\*

21 avenue Jean Capelle, 69100 Villeurbanne

malorie.hologne@insa-lyon.fr

RESUME – Cet article propose un tour d'horizon des potentiels modes de défaillances des modules de puissance, notamment ceux composés de MOSFET en carbure de silicium (SiC). Une approche expérimentale du suivi de ces processus de défaillance est également proposée. La fiabilité des convertisseurs de puissance par le biais des modules est devenue une question clé dans la majeure partie des industries et notamment dans le milieu aéronautique. C'est pourquoi cette étude est ancrée dans un projet Européen nommé I²MPECT, en charge de réaliser un convertisseur de puissance reposant sur la technologie SiC, le plus compact, le plus intelligent et le plus fiable possible. Le matériau carbure de silicium présente de nombreux attraits comme le gain en volume pour une même puissance commutée ainsi que de plus faibles pertes. Cependant, l'utilisation de la technologie SiC dans des modules de puissances présente encore quelques défis en termes de fiabilité. Après une brève description des modes de défaillances attendus, un banc expérimental de suivi des défaillances sera présenté. Le choix et la mise en œuvre des indicateurs de défaillance seront également discutés.

ABSTRACT – This paper deals with an overview of silicon carbide MOSFET-based power module failure modes and an experimental health-monitoring approach to detect them. A strong interest on power module reliability has emerged in industrial fields because of an increasingly frequent use of converters in power transmission systems. This study is anchored in a European project, called I²MPECT, in charge of a more integrated, intelligent and compact converter realization for aerospace use. The question of converter components reliability is so essential and require investigations. The converter designed by project members will be composed of silicon Carbide (SiC) MOSFET-based power modules, known for their performances, ten times higher than silicon technology. However, these power modules present some challenges in reliability field. In this paper, reliability issues will be described and a relevant monitoring method will be explained. Technological issues concerning health-monitoring test bench establishment will be also discussed.

MOTS-CLES - MOSFET SiC, module de puissance, health-monitoring, modes de défaillances, indicateurs de défaillance.

#### 1. Introduction

Le projet l'MPECT a été créé pour répondre à l'utilisation toujours plus importante de convertisseurs au sein des applications aéronautiques. L'équipe du projet a pour mission de réaliser un onduleur 45 kW compact et intelligent dont les aspects thermiques et CEM doivent être optimisés, mais qui doit également disposer d'un système de commande rapprochée apte à la détection de défauts en ligne qui permettra une meilleure gestion des ressources électriques.

La détection de défaut en ligne est une fonction qui est permise par le suivi de l'état de santé des modules de puissance. Ce dernier se traduit par un travail en deux temps, principalement centré sur l'observation d'indicateurs de vieillissement du module de puissance. Le premier temps, appelé phase d'apprentissage, consiste en l'observation de l'évolution des indicateurs de défauts sous un profil de mission donné tout au long de la vie du module. Une fois cette première phase analysée, l'évolution particulière d'un indicateur, pour un défaut donné, constituera la signature de celui-ci. Cela permettra une deuxième phase du travail avec la mise en place d'un diagnostic de défaut en ligne pour des profils de mission proches de l'apprentissage grâce aux signatures préalablement obtenues. Le suivi en ligne des indicateurs lors de la phase de diagnostic devrait permettre de déterminer à chaque instant la durée de vie utile restante du module et ainsi contribuer à une utilisation plus sûre des équipements électroniques dans les appareils.

L'observation de tels indicateurs soulève quelques problématiques, notamment la définition d'une limite de fonctionnement correct. Même si la réalisation de tests de vie accélérée semble être une solution, d'autres contraintes comme l'accessibilité des mesures ou la modification du circuit initial restent présentes. En effet, si la mesure d'un indicateur requière une modification topologique importante, la fiabilité générale de l'ensemble peut en être affectée. Toutes ces interrogations nécessitent une étude détaillée des indicateurs possibles afin d'en optimiser l'accessibilité, la simplicité et la précision.

Pour éclairer la discussion du suivi de l'état de santé des modules de puissance, une première partie sera consacrée à la description des modes de défaillance attendus afin de déterminer les indicateurs les plus pertinents. Il sera ensuite montré que la température et le vieillissement peuvent cependant altérer les corrélations identifiées entre indicateurs et modes de défaillances. Enfin, une dernière partie sera consacrée à la présentation d'un banc de test permettant de suivre les défaillances ciblées dans le cadre du projet.

# 2. Modes de défaillances attendus dans les modules de puissance composés de MOSFET SiC

#### 2.1 Modes de défaillances liés au module

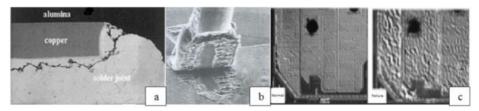

Un module de puissance est un système complexe, rassemblant dans un espace confiné différents matériaux présentant des comportements thermiques et mécaniques variés sous une même contrainte. Le composant dissipe une grande quantité d'énergie durant son fonctionnement et les matériaux annexes subissent de manière cyclique des échauffements et des refroidissements successifs. Les coefficients thermiques d'expansion (CTE) de chaque matériau n'étant pas compatibles dans un cyclage thermique certains phénomènes apparaissent à l'intérieur ou aux interfaces des matériaux comme présentés Fig.1. Musallam [5] a montré l'apparition de fissures dans les joints de soudure ainsi que la formation de « vaguelettes » au sein du substrat céramique. Les interconnections du module sont également très vulnérables, les fils d'interconnexions peuvent présenter des fissures avant de subir un décollement, comme l'a montré Bower [1]. Enfin, la métallisation supérieure étant la partie la plus proche de la zone en échauffement, Durand [3] a montré qu'un phénomène de reconstruction métallique s'y établissait sous contrainte thermique.

Figure 1 : (a) Fissures dans les joints de soudure, (b) décollement des fils d'interconnexion, (c) reconstruction de la métallisation.

#### 2.2 Modes de défaillances liés à la puce, le MOSFET SiC

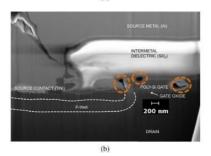

Figure 2 : Dégradation de l'oxyde de grille

De nombreux phénomènes, listés par Yang [10], peuvent mener à une défaillance du MOSFET SiC. Le mode de défaillance le plus observé sur les MOSFET SiC est la dégradation de l'oxyde de grille qui mène à un court-circuit de celle-ci et rend le composant incontrôlable. La dégradation est montrée Fig. 2. Dans l'article d'Ouaida [6], il est expliqué que des cavités apparaissent dans l'oxyde et progressivement la fonction d'isolant n'est plus assurée. Pour déclencher cette dégradation, une température de 250 °C avait été appliquée au MOSFET dans sa totalité pendant un fonctionnement de commutation nominal. Othman [7] a quant à lui mené une étude sur cette dégradation en condition de court-circuit, en imposant un courant de 200 A entre drain et source. Il remarque que 10 µs après avoir stoppé le court-circuit entre drain et source, la grille se court-circuite. Ce laps de temps correspond au temps de diffusion thermique entre le canal de conduction et la grille. Un échauffement trop important au sein du canal peut donc être responsable d'un claquage de l'oxyde.

#### 2.3 Facteurs d'accélération et indicateurs de défauts

Pour suivre les différents modes défaillances exposés précédemment, plusieurs indicateurs peuvent être utilisés. Selon Ouaida [6], la dégradation de l'oxyde de grille peut être qualifiée grâce à l'évolution du courant de fuite de grille ou de

drain et la tension de seuil. Pour déclencher rapidement un claquage de l'oxyde de grille, il a été mentionné ci-dessus qu'une haute température ou une surintensité étaient de bons facteurs d'accélération comme l'a expérimenté Schrock [9]. Cependant, une autre étude menée par Santini [8] a montré qu'une polarisation constante de la grille à une valeur supérieure à celle de fonctionnement déclenchait une dégradation très précoce.

Concernant la fatigue des interconnections et des éléments de report (soudures, frittages), l'impédance thermique et la résistance électrique à l'état passant sont de bons indicateurs de suivi. Cependant, leur évolution ne permet pas de localiser un défaut précisément, il donne juste une indication sur la perte de conduction électrique et/ou thermique d'un élément du module. Selon Durand [3], les facteurs d'accélérations pertinents pour la fatigue du module sont la haute température et les surintensités.

Pour chacun des modes de défaillance, la connaissance de la température de jonction est un élément clé de la compréhension des phénomènes en jeu. Cependant son obtention n'est pas directe et plusieurs méthodes développées dans la littérature sont discutées dans le prochain paragraphe.

#### 3. Discussion sur l'influence de la température et du vieillissement sur les indicateurs

#### 3.1 Obtention de la température de jonction

Actuellement la température de jonction peut être identifiée par au moins trois méthodes : avec un capteur intégré à la puce, avec un modèle thermique ou avec un paramètre électrique thermosensible (TSEP). La première solution est la plus précise en théorie, mais nécessite une conception sur mesure de la puce, et donc un coût plus important et une complexité plus grande. Les deux autres méthodes restent envisageables et sont discutées ci-après.

#### 3.1.1 Modélisation thermique

Pour réaliser le modèle thermique d'un module, une connaissance précise de la puce et de la composition du module est requise. A cette fin, un modèle par éléments finis du module complet est réalisé. Des simulations thermiques puis des expérimentations permettent de corréler les paramètres du modèle avec la réalité physique. Pour pouvoir être plus facilement utilisé, le modèle thermique est ensuite réduit sous forme d'un modèle électrique ou les résistances et les capacités thermiques sont les paramètres. Ce modèle précis a été utilisé par Zhong [13] pour réaliser un suivi de la température de jonction.

#### 3.1.2 Paramètres électriques thermosensibles

Dupont [2] a réalisé une étude des TSEP et a appliqué la méthode pour suivre en ligne la température de jonction de module constitués d'IGBT. Les TSEP sont attractifs car ils proposent une estimation de la température de jonction sans modification du circuit ce qui est un atout dans un suivi en ligne. Cependant, pour obtenir la température de jonction via un paramètre, il faut réaliser une phase de calibration, qui se doit d'être précise, car certains paramètres ont un intervalle de valeurs très réduit et certains phénomènes comme l'auto-échauffement viennent perturber la corrélation. Une autre étude menée par Yuan [11] précise que les paramètres ne sont pas seulement thermo-sensitifs mais dépendent du vieillissement. Pour éviter un biais dû à la dérive d'un paramètre par vieillissement, la méthode utilisée propose des calibrations régulières au cours de la vie du module. Concernant les MOSFET, les paramètres thermo-sensitifs les plus utilisées sont le courant de saturation et la tension de seuil. Ces deux éléments sont des TSEP, dit non-fonctionnels, ils sont mesurés hors du fonctionnement nominal du MOSFET. Des TSEP fonctionnels, mesurés lors du fonctionnement nominal, sont envisageables mais aucun démonstrateur n'a été établi à ce jour car les TSEP fonctionnels évoluent peu avec la température. L'utilisation de TSEP non-fonctionnels requiert donc une procédure de mesure très précise afin de ne pas s'éloigner de la température atteinte en fonctionnement.

#### 3.2 Approche méthodique de suivi de l'état de santé des modules de puissance

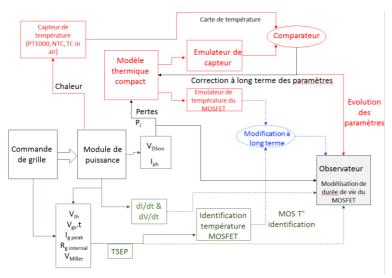

Figure 3 : Approche de « Health-monitoring » créée pour le projet

La fig. 3 présente l'approche de « Healthmonitoring » créée pour le projet. Autour du module de puissance, les aspects thermiques et électriques sont deux piliers essentiels à la création d'un modèle adaptatif et pertinent. Il a été montré dans les paragraphes précédents, qu'une évolution des paramètres des modèles thermiques et électriques est nécessaire pour qualifier les défauts sans biais. Pendant le fonctionnement du module, les paramètres électriques sont enregistrés. Certains d'entre eux vont permettre de caractériser les défaillances et peuvent être utilisés pour participer à l'établissement d'un modèle de durée de vie du module. En parallèle, certains paramètres sont utilisés pour alimenter le modèle thermique compact qui est en permanence comparé à une « carte de température » obtenue par des capteurs. Cette comparaison apporte des corrections

sur le modèle thermique et les envoie au modèle de durée de vie du module. De cette manière, les TSEP sont toujours recalculés suivant l'évolution du système. Les indicateurs de défaillances obtenus par cette méthode donneront une indication pertinente de la défaillance, le biais imposé par la température étant supprimé ici.

#### 4. Approche expérimental du suivi de l'état de santé des modules

Avant de réaliser un « Health-monitoring » en ligne, il est important de connaître les limites de fiabilité du module créé par le projet. Cette interrogation peut être levée par la réalisation de tests de vie accélérée. Dans ces tests, des facteurs d'accélération pertinents doivent être trouvés afin de déclencher les modes de défaillances attendus en nominal. Le but de ces tests est de fixer la limite de fiabilité d'une technologie donnée en appliquant un niveau de contrainte supérieur au mode nominal tout en déclenchant les mêmes modes de défaillances mais dans un laps de temps plus court. Avant de proposer les choix pour le banc de test un rapide tour d'horizon est présenté dans la sous partie suivante.

#### 4.1 Tour d'horizon sur les tests de vie accélérée des modules de puissance

Dans la littérature, de nombreux tests de vie accélérée ont été pratiqués soit sur des puces seules, packagée ou non, soit sur des modules seuls. Très peu d'études voient l'ensemble comme un système complet. Le plan de test a été établi par l'analyse des différents types d'études [3, 6, 8, 13].

Comme précisé dans le second paragraphe, les facteurs d'accélération de la dégradation de la grille du MOSFET sont la haute température, un fort courant de drain (court-circuit) ou l'application d'une forte tension sur la grille de manière continue. Afin d'obtenir un facteur d'accélération du mode de défaillance de la grille et non pas des autres parties de la puce et du module, la méthode de la tension de grille continue sera retenue car moins perturbatrice pour l'environnement proche de la puce.

Concernant les modes de défaillances du module, la littérature nous montre que le cyclage thermique semble accélérer la majeure partie des défaillances attendues. Pour imposer un cyclage thermique, deux méthodes sont possibles: Le cyclage actif ou passif. Le cyclage passif, utilisé par Zhang [12] dans son mémoire de thèse, consiste à placer le module dans une enceinte climatique régulée avec une température variant de -55°C à 180°C. Cette méthode impose des contraintes thermomécaniques sur les composants et déclenche les modes de défaillances attendus dans un module de puissance. De tels tests ne permettent pas de déclencher un mode de défaillance ciblé, l'ensemble du module subira les contraintes de la même manière. Cependant, dans le milieu aéronautique, de tels cyclage passifs sont observés en fonctionnement et les mécanismes de défaillances déclenchés par ces tests mériteraient une étude spécifique. Le cyclage passif n'a pas été choisi pour le projet pour deux raisons. En fonctionnement le module ne subira pas une si grande plage de température ambiante et le but des tests de vie accélérés est de trouver des signatures de défauts pour chaque modes de défaillance. Or le cyclage passif ne permet pas de dé-corréler les défauts les uns des autres. Une étude menée par Jiang [4], montre que le cyclage actif est plus représentatif des contraintes en fonctionnement car la distribution en température dans le module est créée par l'échauffement de la puce. Cette étude explique également qu'en jouant sur les limites inférieures et supérieures de la température ainsi que sur la durée des cycles, il est possible d'exciter certains modes de défaillances plus que d'autres.

#### 4.2 Description du plan de tests de vie accélérée

#### 4.2.1 Description du module de test

Le module de puissance proposé par les partenaires est un module encapsulé, les connectiques de types fils d'interconnexion sont supprimées à l'instar d'une technologie de circuit imprimé flexible qui est pressé sur les éléments du module. Pour réaliser les tests de fiabilité, un module simplifié constitué d'un seul bras de convertisseur avec un seul MOSFET par interrupteur a été réalisé afin d'être capable d'isoler au mieux les modes de défaillances.

#### 4.2.2 Tests de fatigue de la grille du MOSFET

Pour déclencher les modes de défaillances propres à la grille du MOSFET, le test HTGB¹ a été choisi. Deux types de tests HTGB seront réalisés, le premier avec une tension de grille positive supérieure à la tension usuelle et le second avec une tension de grille négative inférieure à la tension usuelle. Chaque test HTGB sera réalisé sur 4 modules identiques afin de vérifier la répétabilité du comportement des indicateurs. Les indicateurs observés durant ce test seront la tension de seuil, le courant de fuite de drain, la résistance à l'état passant et le courant de fuite de grille.

#### 4.2.3 Tests de cyclage de puissance actif (CPA)

Les tests CPA ont été conçu pour déclencher différents modes de défaillance et essayer de dé-corréler les modes de défaillances de grille, de ceux de la métallisation ou encore de ceux des éléments de report.

Le premier test consiste en des cycles thermiques longs créés par l'auto-échauffement du MOSFET sous un courant nominal. Le but est de déclencher une diffusion de la température à travers toutes les couches du module à chaque cycle. Cette diffusion de température devra déclencher les modes de défaillances concernant la métallisation, les reports de soudure ainsi que le substrat. Un second test est composé de cycles thermiques courts, également permis par l'auto-échauffement du MOSFET soumis à un courant supérieur à son nominal. Ce test permettra de déclencher des pièges de charge dans l'oxyde de grille ainsi que la reconstruction métallique de la métallisation supérieure. Pendant les deux

<sup>&</sup>lt;sup>1</sup> High Temperature Gate Bias: test établi dans JEDEC: Global Standards for the Microelectronics industry

types de tests CPA, nous relèverons, le courant de saturation, la tension de seuil, la résistance à l'état passant, la tension en conduction et la résistance thermique. Le courant de saturation sera utilisé comme TSEP car il est une image de la température au point le plus chaud de la puce. Une phase de calibration, décrite dans le paragraphe suivant, a été réalisée et montre déjà qu'un protocole rigoureux est nécessaire pour obtenir une corrélation précise entre le courant de saturation et la température. En effet, comme l'état de charge de la grille crée un biais dans la valeur du courant de saturation, la calibration repasse par un état « off », avec une tension de grille de -5 V entre chaque mesure afin de réinitialiser l'état de charge de la grille.

Le croisement de tous ces indicateurs dans les deux types de test devrait permettre de dissocier les différents modes de défaillances. Pour des raisons de répétabilité, les tests CPA seront également réalisés sur 4 modules identiques. Dans la majeure partie des tests, seul le MOSFET du bas du bras sera testé, le MOSFET du haut subira des tests sur sa diode interne en un protocole de test spécifique en suivant la température de jonction, le courant de fuite de drain et la tension inverse afin d'assurer le fonctionnement complet des modules de puissance.

#### 4.3 Calibration du TSEP

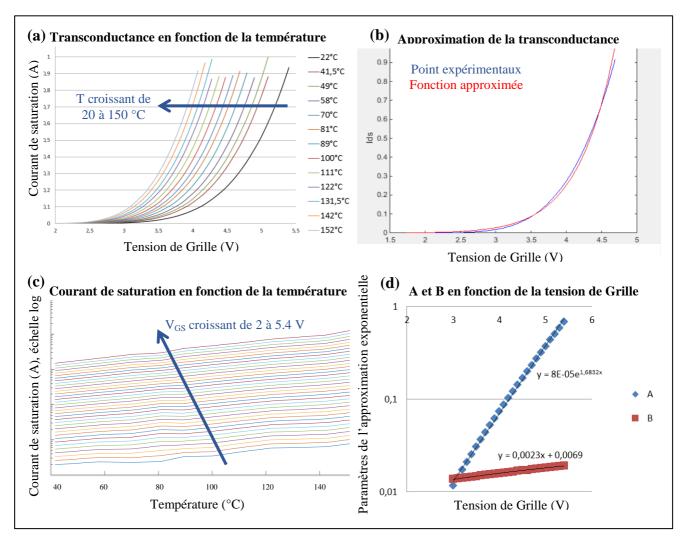

Comme nous l'avons établi précédemment, la calibration du courant de saturation doit être réalisée au fil du vieillissement et comporte plusieurs phases jusqu'au calcul de la température estimée au plus chaud du cyclage. Pour réaliser ces calibrations, le module et ses cartes électroniques associées sont placés sur une plaque chauffante au sein d'un milieu adiabatique (laine de verre) comme montré fig. 4. La plaque chauffante est régulée à différentes températures entre 40 et 150°C, un thermocouple supplémentaire placé au niveau de la semelle du composant et une thermistance placée à l'intérieur du module permettent d'assurer qu'une température est établie de manière permanente et que tout le module, puce comprise, subit une température ambiante connue. Pour chacune des températures, la transconductance du MOSFET est tracée. Il s'agit du lien entre le courant de saturation et la tension de grille lorsque que la tension de drain est fixée (ici 10 V). Les caractéristiques obtenues sont représentées fig. 6.a Le modèle régissant l'évolution de ces courbes est difficile à établir sur cette plage d'évolution de la tension de grille. Nous ne pourrons donc pas tirer l'information de température en ligne à partir de cette seule caractéristique. Pour déterminer la température plus rapidement en ligne nous suivons le protocole suivant :

Figure 4: Module en calibration

Chacune des transconductances peut être approximée par la fonction :

$$I_{DS} = (p_3.V_{GS} + p_4)e^{(p_1.V_{GS} + p_2)}$$

(1)

$I_{DS} = (p_3.V_{GS} + p_4)e^{(p_1.V_{GS} + p_2)} \tag{1}$  Chacun des paramètres  $p_i$  est obtenu par un algorithme génétique et est propre à une température. Fig. 6.b illustre cette approximation.

Grâce à la fonction obtenue, l'expression du courant de saturation en fonction de la température est possible à tension de grille connue. Cette nouvelle caractéristique est présenté fig. 6.c. On remarque que ces caractéristiques peuvent être approximées par la fonction :

$$I_{DS} = Ae^{B.T} (2)$$

Lors de l'enregistrement des valeurs de A et B, on remarque que ces dernières ne dépendent que de la tension de grille (fig. 6.d) via l'ensemble de fonctions :

$$\begin{cases} A = C_1 e^{C_1 V_{GS}} \\ B = C_3 V_{GS} + C_4 \end{cases}$$

(3)

Pour obtenir de manière directe la température en ligne grâce au relevé de la tension de grille et du courant de saturation, on peut donc appliquer la formule suivante, combinaison de (2) et (3) :

$$T(V_{GS}, I_{DS}) = \frac{1}{C_3 \cdot V_{GS} + C_4} \ln \left( \frac{1}{C_1 e^{C_1 \cdot V_{GS}}} \right)$$

(4)

Les paramètres C<sub>i</sub> seront donc propres à chaque calibration et pourront changer au cours de la vie d'un même MOSFET.

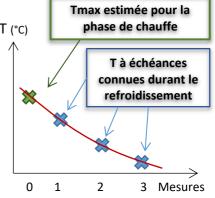

La formule ainsi obtenue sera utilisée après un cycle de chauffe afin de déterminer la température à la fin du dit cycle de chauffe. Le schéma présenté fig. 6 illustre le principe. Trois mesures successives de la tension de grille et du courant de saturation permettront d'évaluer la température à des moments connus de la phase de refroidissement et ainsi de remonter à la température la plus haute atteinte en cycle de chauffe par une méthode d'extrapolation.

Figure 5 : Extrapolation de la température maximale atteinte pendant la chauffe

Figure 6 : (a) Transconductance suivant la température de la puce, (b) Approximation de la transconductance par la fonction (1), (c) Courant de saturation en fonction la température grâce aux fonctions précédemment extrapolées, (d) lien entre les paramètres de (c) et la tension de grille.

#### 4.4 Description du banc de test PCA

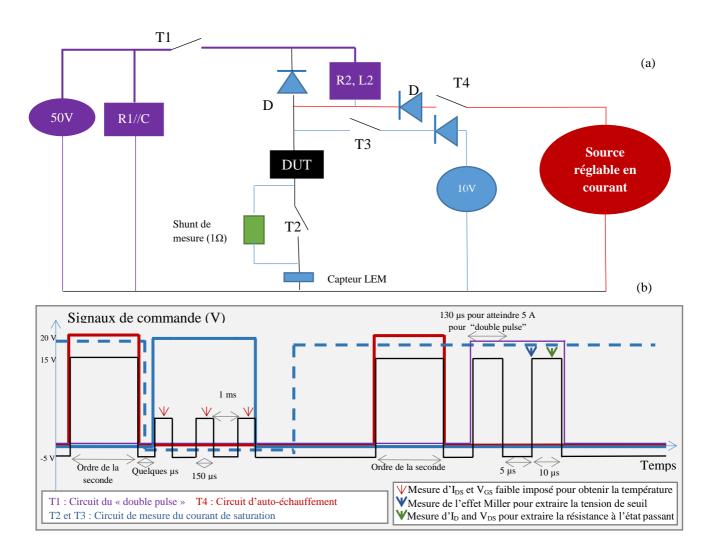

Comme présenté Fig. 7.a sur le schéma de principe, le banc de test CPA est composé d'un circuit de puissance pour déclencher l'auto-échauffement du MOSFET étudié, noté DUT. Un autre circuit permet de mesurer la valeur du courant de saturation grâce à un système de shunt  $(1\Omega)$  applicable uniquement durant cette phase. Enfin, un dernier circuit permet de venir réaliser un « double pulse ». Cette méthode permet de réinitialiser les capacités internes du MOSFET puis de caractériser au mieux sa commutation. Cette étape sera utilisée pour obtenir la tension de seuil via le palier Miller et mesurer la résistance à l'état passant sur le plateau du deuxième pulse.

La Fig. 7.b montre les séquences de commandes des différents interrupteurs pour comprendre où se placent les phases de caractérisation au sein du cyclage thermique. Sur cette figure, les temps à l'échelle ne peuvent être représentés graphiquement car les phases de chauffe ont une durée de l'ordre de la seconde et celles de caractérisation de l'ordre de la microseconde. Les phases de caractérisation, que sont le « double pulse » et la mesure du courant de saturation, doivent être mise en place au plus près de la fin du cycle de chauffe afin d'être le plus représentatif de la température maximale atteinte durant la phase de chauffe.

Des premiers tests d'acquisition ont été menés pour valider l'enchainement des séquences et l'exactitude des mesures enregistrées. L'automatisation d'un cyclage complet est en cours de réalisation. Ce premier cyclage devra tout de même être supervisé afin de vérifier que le cyclage est assez sévère pour déclencher un mécanisme de défaillance dans un temps raisonnable, de l'ordre de la semaine. Il faudra également s'assurer de la sécurité de l'installation puisque que le module pourra montrer une défaillance à n'importe quel moment et enfin il faudra s'assurer du bon conditionnement des données engendrées par ce cyclage afin que l'exploitation soit possible. Dans l'actuelle interface de contrôle du banc, il est prévu de placer les caractérisations tous les n cycles de chauffe. Ce premier cyclage va également nous permettre de choisir ce nombre n afin de ne pas encombrer nos bases avec des résultats de début de cyclage qui ne

seraient pas pertinents et de risquer de manquer d'information sur la fin de la vie du module. Il faudra certainement avoir une échéance réglable en fonction de l'évolution des indicateurs de défauts.

Figure 7: (a) Test de cyclage de puissance actif, (b) signaux de commande

#### 5. Conclusion

Dans cet article, un rapide tour d'horizon des modes de défaillances attendus a été réalisé. Le niveau de fiabilité toujours plus élevé a poussé les chercheurs et les industriels à trouver des méthodes pour caractériser et comprendre ces modes de défaillances. De nombreuses études sur la fiabilité des MOSFET SiC et des modules à base d'IGBT ont été publiées. Ces études ont été les fondations de l'établissement d'un plan de tests dans le but d'établir une approche de « Health-monitoring » sur les modules de puissance à base de MOSFET SiC. L'établissement du banc de test, avec ses verrous technologiques que sont la précision et la possibilité de mesure ainsi que les corrélations entre indicateurs, température et vieillissement, a été discuté. Un schéma logique présentant l'approche de « Health-monitoring » créé pour le projet a été détaillé en expliquant les interactions entre modèle thermique et électrique. La réalisation physique du banc de test PCA a également été décrite, la fonctionnalité de ce banc a été vérifiée. Il reste à faire cycler les modules du projet pour obtenir les premières données et commencer à mettre en œuvre un traitement de données nous permettant d'arriver au diagnostic de défaut en ligne et au pronostic de la durée de vie restante.

#### Remerciements

Le travail effectué n'a pu être réalisé que grâce au soutien de l'Union Européenne à travers le projet du programme Horizon 2020 N°636170. Les partenaires industriels DYNEX, SIEMENS, AIRBUS, LABINAL et les partenaires académiques École polytechnique de Zurich, Université de Sheffield ont travaillé de concours à l'élaboration du projet et donc du module qui subira l'étude de fiabilité.

#### Références

- [1] G. Bower, P. Rogan, J. Kozlowski and M. Zugger, "SiC power electronics packaging pronostics," *IEEE Aerospace conference*, 2008.

- [2] L. Dupont, and Y. Avenas, "Preliminary evaluation of thermo-Sensitive Electrical Parameters based on the forward voltage for Online Chip Temperature Measurements of IGBT Devices", *IEEE transactions on industry applications*, vol. 51, No. 6, pp. 4688-4698, 2015.

- [3] C. Durand, M. Klinger, D. Coutellier, and H. Naceur, "Confrontation of failure mechanisms observed during active power cycling tests with finite element analyze performed on a mosfet power module," 14<sup>th</sup> International Conference on Thermal, Mechanical and multi-physics simulation and experiments in microelectronics and microsystems (EuroSimE), pp. 1-4, April 2013.

- [4] N. Jiang, M. Chen, S. Xu, W. Lai, G. Bing, Y. Chen, "Lifetime evaluation of solder layer in an IGBT module under different temperature levels", 8<sup>th</sup> International power electronicsand motion control IEEE conference (IPEMC-ECCE Asia), pp. 3137-3141,2016.

- [5] M. Musallam, C. Johnson, C. Yin, H. Lu, and C. Bailey, "Real-life expectancy estimation in power modules," Electronic System-integration Technology Conference, pp. 231–236, 2008.

- [6] R. Ouaïda, M. Berthou, J. Leon, X. Perpina, S. Oge, P. Brosselard and C. Joubert, "Gate oxide degradation of sic mosfet in switching conditions," Electron Device Letters, IEEE, vol. 35, no 12, pp. 1284–1286, December 2014.

- [7] D. Othman, S. Lefebvre, M. Berkani, Z. Katir, A. Ibrahim, and A. Bouzourene, "Investigation of 1.2 kV SiC MOSFET for Aeronautics Applications", 15th European Conference on Power Electronics and Applications, 2013.

- [8] T. Santini, M. Sebastien, M. Florent, L-V. Phung and B. Allard, "Gate oxide reliability assessment of sic mosfet for high temperature aeronautic applications," ECCE Asia, IEEE, pp. 385–391, June 2013.

- [9] J. Schrock, B. Pushpakaran, A. Bilbao, W. Ray, E. Hirsch, M. Kelley, S. Holt, and S. Bayne, "Failure analysis of 1200V/150 A sic mosfet under repetitive pulsed overcurrent conditions," IEEE Transactions on Power Electronics, no. 99, pp. 1–1, 2015.

- [10] S. Yang, D. Xiang, A. Bryant, P. Mawby, L. Ran, and P. Tavner, "Condition Monitoring for Device Reliability in Power Electronic Converters: A Review", *Transactions on Power Electronics IEEE*, vol. 25, pp. 2734-2752, 2010.

- [11] Y. Yuan, D. Xiang, and C. Ning, "Self\_calibration for IGBT Junction Temperature measurement in power converter", 8<sup>th</sup> International power electronics and motion control IEEE conference (IPEMC-ECCE Asia), pp. 3125-3130,2016.

- [12] L. Zhang, "Feasibility study on SiC-based Power Modules for high temperature applications", PhD report, chapter 3, Sciences and technologies University of Bordeaux, 2012.

- [13] Y. Zhong, C. Li, and D. Xu, "A novel method for online junction temperature measurement of power modules", 8<sup>th</sup> International power electronics and motion control IEEE conference (IPEMC-ECCE Asia), pp. 3120-3124,2016.