# Experimental Evaluation of IGBT Junction Temperature Measurement via a Modified-VCE (VCE\_VGE) Method with Series Resistance Removal

Nick Baker, Francesco Iannuzzo, Stig Munk-Nielsen, Laurent Dupont, Yvan

Avenas

# ▶ To cite this version:

Nick Baker, Francesco Iannuzzo, Stig Munk-Nielsen, Laurent Dupont, Yvan Avenas. Experimental Evaluation of IGBT Junction Temperature Measurement via a Modified-VCE (VCE\_VGE) Method with Series Resistance Removal. CIPS2016 - 9th Conference on Integrated Power Electronics Systems, Mar 2016, Nuremberg, Germany. 6p. hal-01466153

# HAL Id: hal-01466153 https://hal.science/hal-01466153

Submitted on 13 Feb 2017

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Experimental Evaluation of IGBT Junction Temperature Measurement via a Modified- $V_{CE}$ ( $\Delta V_{CE_{\Delta VGE}}$ ) Method with Series Resistance Removal

Nick Baker, Francesco Iannuzzo, Stig Munk-Nielsen, Aalborg University, Denmark Laurent Dupont, SATIE (UMR 8029), IFSTTAR-COSYS, France Yvan Avenas, G2Elab (UMR 5269), France

# Abstract

Temperature sensitive electrical parameters (TSEPs) allow junction temperature measurements on power semiconductors without modification to module packaging. The on-state collector-emitter voltage ( $V_{CE}$ ) in IGBTs is an attractive option for junction temperature measurement since it is relatively easy to measure during operation. Nevertheless, the resistive contribution of interconnection and packaging materials has been shown to introduce large errors when using the  $V_{CE}$  for junction temperature measurement. This paper uses an IR camera to experimentally evaluate a modified- $V_{CE}$ method designed to remove this series resistance contribution. This method can be described as the difference in  $V_{CE}$  at two different gate voltages (15V and 13V). Experimental validation focuses primarily on the accuracy of the temperature measurement and investigates paralleled chip configurations as well as multiple devices with differing geometry and manufacturer. The modified- $V_{CE}$  shows significant improvement over the normal- $V_{CE}$  in terms of correlation to mean junction temperature, with maximum errors typically below 10°C. These results are additionally compared with one traditional and robust TSEP: the voltage drop under low current injection.

# **1** Introduction

#### 1.1 Background

Knowledge of junction temperature in Insulated-gate Bipolar Transistors (IGBTs) during the operation of power electronic converters can improve condition monitoring systems and enhance power module lifetime [1]

Real time junction temperature measurement is however often difficult. Physical or contact measurement methods such as optical fibres, on-chip sensors, or infra-red cameras are expensive and require substantial modification to standard power module packaging. Electrical methods however can be advantageous. Using a Temperature Sensitive Electrical Parameter (TSEP), such as the on-state voltage drop or threshold voltage, junction temperature measurements can be performed on standard power modules without modification to their structure [2-4].

Electrical methods for junction temperature measurement have been used for many decades on transistors, particularly for offline thermal characterisation of devices. Nevertheless, examples of TSEP-based methods being used online (i.e. during normal transistor operation) are still limited [4].

This paper focuses specifically on the use of the on-state collector-emitter voltage ( $V_{CE}$ ) at high current for IGBT junction temperature measurement. The  $V_{CE}$  is an attractive method for a number of reasons: it is relatively easy to extract during operation [5,6] and it can be used on all IGBT devices. However, junction temperature measurement using the  $V_{CE}$  at high current has several problems. The most critical of these is vastly erroneous measure-

ments due to the inherent series resistance contribution of bond wires and packaging [7,8].

Recently, two methods have been tentatively proposed to mathematically remove the series resistance contribution from the  $V_{CE}$ . These investigations have thus far only been conducted on one single IGBT [7].

This paper takes one of these methods that is most suited for online use and extends the experimental verification to a variety of chips with differing geometry and manufacturer. Temperature measurements will be made under steady-state current injection and validated with an IR camera. The IGBT chips selected for evaluation are all rated for 1200V and are as follows. Where possible, IG-BTs are also assessed in paralleled configuration.

- 1. **Infineon** Chip: *IGC189T120T8RL*, Module: *FS200R12PT4*, square chip, 1.2kV-200A.

- 2. Infineon Chip: *IGC193T120T8RM*, Module: *FF600R12ME4*, rectangular chip, 1.2kV-200A.

- 3. Fuji Chip: Unknown, Module: 6MBI100VA-120-50, square chip, 1.2kV-100A.

First, the paper will provide a brief description of the modified-V<sub>CE</sub> method (referred to as  $\Delta V_{CE\_\Delta VGE}$ ), the test bench, and some details on the calibration procedure. Results and comparison with IR measurements will then be presented for the three different chips.

## **1.2** Modified-V<sub>CE</sub> Method - $\Delta V_{CE \Delta VGE}$

In a first approximation, the measurement principle investigated in this paper is simple and can be demonstrated mathematically as follows:

$$V_{CE1} = V_{IGBT}(V_{GE1}, I_L) + I_L R \qquad Eq.1$$

$$V_{CE2} = V_{IGBT}(V_{GE2}, I_L) + I_L R \qquad Eq.2$$

$$V_{CE1} - V_{CE2} = V_{IGBT}(V_{GE1}, I_L) - V_{IGBT}(V_{GE2}, I_L)$$

Eq.3

The basic premise of the method is to take two V<sub>CE</sub> measurements in quick succession at two different levels of V<sub>GE</sub> (15V and 13V). The measurements should also be performed at the same current level. Providing that the two V<sub>CE</sub> measurements are taken sufficiently quickly (under 200 $\mu$ s), the temperature in the junction and interconnections can be assumed constant. In this case, the voltage drop across the chip will fluctuate while the voltage drop across the resistive materials remains stable. Therefore, one V<sub>CE</sub> measurement can be subtracted from the other in order to mathematically reduce the resistive contribution to zero.

# 2 Test Setup

#### 2.1 Test Bench

An experimental setup is developed in order to experimentally evaluate TSEP junction temperature measurement methods. TSEPs are evaluated in a steady state thermal condition under constant current injection. The test bench with IR camera (CEDIP-FLIR SC7500) can be seen in Fig. 1.

Figure 1 Test Bench with IR Camera

The test bench allows campaigns on a large number of devices in a semi-automatic mode. In particular, IR measurements are made with great care. The positioning of the IR camera is controlled by a 3-axis positioning system in order to attain repeatable image positioning on the chip under test, as well as to perform non-uniformity corrections corresponding to the desired temperature range.

Dielectric gel is removed from commercial power modules via soaking in Ardrox 2312 and cleaning with Acetone and deionised water. Chips are black painted with a thickness between 10-16 $\mu$ m with care taken to achieve as consistent emissivity as possible across the surface.

#### 2.2 **TSEP Measurements**

In order to perform a thorough evaluation of the  $\Delta V_{CE\_\Delta VGE}$  method, four methods of junction temperature measurement are used in total:

- 1. **IR Camera:** an IR camera is used to extract the mean temperature of the chip surface ( $IR_{Mean}$ ).

- 2.  $\Delta V_{CE_{\Delta}VGE}$ : V<sub>GE</sub> is briefly lowered from 15V to 13V during high current injection.

- 3. Normal  $V_{CE}$ : the  $V_{CE}$  value at high current with  $V_{GE}$  at a stable 15V ( $V_{CE}$ ).

- 4.  $V_{CE(low)}$ : the V<sub>CE</sub> at a *low current injection* of between 100-200mA (V<sub>CE(low)</sub>). This is chosen due to its traditional use and repeated evidence of correlation with mean junction temperature [7,9,10] at low currents, ohmic contribution is negligible.

#### 2.3 Measurement Synchronisation

A constant current is fed into the device for several minutes until a thermal steady state is reached. At this point, junction temperature measurement using the above methods is performed.

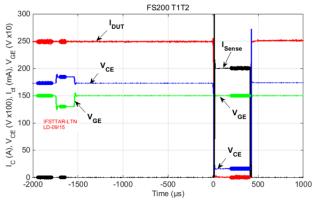

Fig. 2 presents the sequencing of the electrical temperature measurements. In this case,  $I_{DUT}$ =250A for two IG-BTs connected in parallel, and has been constant for several minutes. Between -2000µs and -1750µs, several measurements of V<sub>CE</sub> and I<sub>DUT</sub> are recorded. Immediately after, V<sub>GE</sub> is reduced from 15V to 13V for a period of 200µs. In this period, several measurements of V<sub>CE</sub> and I<sub>DUT</sub> are again recorded. This data is then used for the TSEPs  $\Delta V_{CE} \Delta V_{CE}$  and normal-V<sub>CE</sub>.

At  $0\mu$ s,  $I_{DUT}$  is removed and a low sensing current of 100mA/chip (200mA in total for two paralleled chips) is injected. The  $V_{CE(low)}$  is then recorded from 150 $\mu$ s to 400us and an extrapolation vs. the square root of time is used to estimate the junction temperature at  $0\mu$ s [3]. The full  $I_{DUT}$  of 250A is then returned to the IGBT. IR measurements are performed one second before the before the commencement of the electrical measurements.

**Figure 2** Sequencing of electrical measurements for TSEP junction temperature estimation

#### 2.4 **TSEP** Calibration

All TSEP measurements are calibrated by varying the baseplate temperature from 40-180C and taking the appropriate electrical measurements. Calibration temperature is recorded using an open thermocouple (Type K, Class 2,  $\pm 2.5^{\circ}$ C) placed on the copper layer of the DCB substrate. The thermocouple temperature has been verified using the IR camera, with a maximum difference always lower than 2.2°C in the range of 40°C to 180°C.

The  $V_{CE(low)}$  is the only TSEP that can be calibrated without inducing self-heating, since the sense current is negligible. For the  $V_{CE}$  and  $\Delta V_{CE_{\Delta}VGE}$  high current calibrations, the  $V_{CE(low)}$  is used to compensate for self-heating.

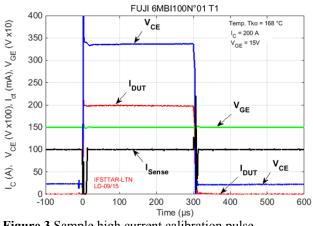

#### 2.5 Self-heating Calibration Compensation

Although current pulses are kept short (300 $\mu$ s) during calibration of V<sub>CE</sub> and  $\Delta$ V<sub>CE\_ $\Delta$ VGE</sub>, self-heating cannot be assumed negligible at high current levels. Therefore, an estimation of the chip(s) temperature is performed using the TSEP V<sub>CE(low)</sub> both before and after the calibration current pulse. Fig. 3 shows the sequencing of this procedure. The 100mA sensing current is run continuously. Between -100 $\mu$ s and 0 $\mu$ s, the V<sub>CE(low)</sub> can be used directly to estimate chip temperature. After 300 $\mu$ s, the calibration pulse ends and there is a short delay of around 10 $\mu$ s before the sense current is again stable. After which, the V<sub>CE(low)</sub> is recorded over time and extrapolated to estimate the chip temperature at the end of the pulse.

Figure 3 Sample high current calibration pulse

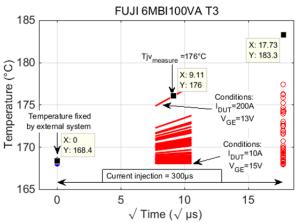

Figure 4 Increase of device temperature due to self-heating during calibration. Measured via  $V_{CE(low)}$ .

The electrical measurements required for calibration of  $V_{CE}$  and  $\Delta V_{CE_{\Delta}VGE}$  are taken towards the end of the pulse. Fig. 4 displays an evaluation of the self-heating that occurs during these pulses on the Fuji *6MBI100VA-120-50*. It can be seen that, in a worst case scenario (high starting baseplate temperature, very high current and 13V gate voltage) we estimate that the self-heating can be more than 15°C. These results are subsequently taken into account when processing calibration data.

# **3** Calibration Results

#### **3.1 Calibration Results**

The temperature sensitivities for the three TSEPs on single IGBT chips at low and high current levels are displayed in Table 1. Two IGBTs are calibrated from each module. It can be seen that the sensitivity of  $\Delta V_{CE\_\Delta VGE}$  appears reasonably consistent for devices from the same manufacturer. Fuji IGBTs displayed a sensitivity of +0.85mV/°C and +0.87mV/°C at 120A, while Infineon IGBTs were around +0.36mV/°C.

We believe that the sensitivity discrepancies of T1 in the Infineon FF600 module is a result of a measurement error or device degradation, since  $V_{CE(low)}$  on this chip was calibrated in a previous study and showed a sensitivity of -2.41mV/°C [10], which is consistent with other Infineon IGBTs here.

| Module            | TSEP                        | IGBT      | Lower<br>Sensitivity<br>@40A | Higher<br>Sensitivity<br>@120A |

|-------------------|-----------------------------|-----------|------------------------------|--------------------------------|

| 7                 | V <sub>CE</sub>             | T1        | -0.42mV/°C                   | +1.51mV/°C                     |

|                   |                             | T2        | -0.42mV/°C                   | $+1.55 mV/^{\circ}C$           |

| 4EO]<br>200       | $\Delta V_{CE\_\Delta VGE}$ | T1        | +0.10mV/°C                   | +0.35mV/°C                     |

| INFINEON<br>FS200 |                             | T2        | +0.11mV/°C                   | +0.37mV/°C                     |

|                   | V <sub>CE(low)</sub>        | T1        | -2.41mV/°C @100mA            |                                |

|                   |                             | T2        | -2.42mV/°0                   | C@100mA                        |

|                   | V <sub>CE</sub>             |           |                              |                                |

|                   |                             | T1        | -0.58mV/°C                   | +2.05mV/°C                     |

| z                 |                             | T2        | -0.45mV/°C                   | $+1.50 mV/^{\circ}C$           |

| 600<br>600        | $\Delta V_{CE\_\Delta VGE}$ | T1        | +0.14mV/°C                   | +0.49mV/°C                     |

| INFINEON<br>FF600 |                             | T2        | $+0.10 mV/^{\circ}C$         | $+0.36 mV/^{\circ}C$           |

|                   | V <sub>CE(low)</sub>        | <b>T1</b> | -2.32mV/°                    | C @100mA                       |

|                   |                             | T2        | -2.43mV/°0                   | C@100mA                        |

| FUJI<br>6MB1100   | V <sub>CE</sub>             | T1        | +0.83mV/°C                   | +3.85mV/°C                     |

|                   |                             | T3        | +0.76mV/°C                   | +3.73mV/°C                     |

|                   | $\Delta V_{CE\_\Delta VGE}$ | T1        | +0.18mV/°C                   | +0.85mV/°C                     |

|                   |                             | Т3        | +0.18mV/°C                   | +0.87mV/°C                     |

|                   | V <sub>CE(low)</sub>        | T1        | -2.25mV/°                    | C @100mA                       |

|                   |                             | Т3        | -2.24mV/°0                   | C@100mA                        |

Table 1 TSEP sensitivity for single IGBT configuration

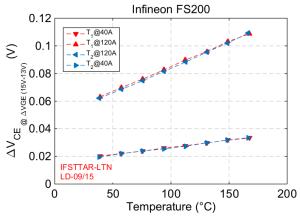

Figure 5 displays a graphical representation of the calibration results for  $\Delta V_{CE_{\Delta}VGE}$  on both T1 and T2 from the Infineon FS200. There appears to be a very good correlation between the two chips in both temperature sensitivity and absolute value for  $\Delta V_{CE_{\Delta}VGE}$ . This introduces the possibility that just one calibration procedure can be performed and the results transferred to all chips within a batch or module. Nevertheless, more research will be required to ascertain this possibility.

Figure 5 FS200  $\Delta V_{CE\_\Delta VGE}$  Calibration: Comparison of T1 and T2

#### 3.2 Calibration Results: Paralleled IGBTs

In the case two chips in parallel, the calibration follows the same procedure as for single IGBTs. However, the  $V_{CE(low)}$  sensing current used is two times higher (200mA). Results of the calibration of paralleled chips in the FS200 and 6MBI100 modules are displayed in Table 2. The layout of the Infineon FF600 did not provide scope to configure two chips in parallel.

Table 2 TSEP sensitivity for two IGBTs in parallel

| Module            | TSEP                        | IGBT   | Lower<br>sensitivity<br>@80A | Higher<br>sensitivity<br>@240A |  |

|-------------------|-----------------------------|--------|------------------------------|--------------------------------|--|

| NO O              | $V_{CE\ Ip}$                | T1//T2 | -0.40mV/°C                   | +1.55mV/°C                     |  |

| INFINEON<br>FS200 | $\Delta V_{CE\ \Delta VGE}$ | T1//T2 | +0.11mV/°C                   | +0.36mV/°C                     |  |

|                   | V <sub>CE Ict</sub>         | T1//T2 | -2.41mV/°C @200mA            |                                |  |

|                   |                             |        |                              |                                |  |

| FUJI<br>6MBI100   | $V_{CE\ Ip}$                | T1//T3 | $+0.77 mV/^{\circ}C$         | +3.75mV/°C                     |  |

|                   | $\Delta V_{CE\ \Delta VGE}$ | T1//T3 | +0.18mV/°C                   | +0.87mV/°C                     |  |

|                   | $V_{CE\_Ict}$               | T1//T3 | -2.24mV/°C                   | C@200mA                        |  |

The sensitivity of each TSEP appears to remain largely unchanged when compared to single IGBTs. This is in contrast to some TSEPs which have a varying sensitivity depending on the number of chips in parallel [11].

# 4 Dissipation Results

#### 4.1 Single IGBTs

Temperature measurements during dissipation are conducted at a range of current values from 40-160A. The input fluid to the heatsink is maintained at 40°C during all tests.

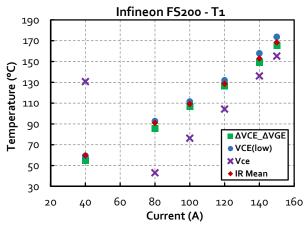

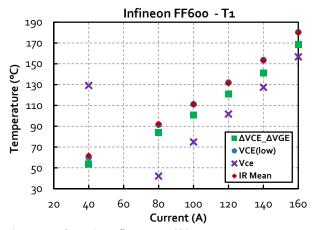

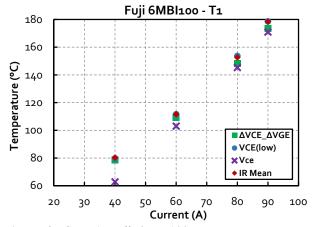

Dissipation results for T1 in all examined modules are displayed graphically in Figs. 6-8. The figures include temperature measurements made via all investigated TSEPs, along with the mean chip surface temperature as measured via the IR camera ( $IR_{Mean}$ ). Meanwhile, Table 3 provides the minimum and maximum deviations from  $IR_{Mean}$  for each set of TSEP measurements on both T1 and T2.

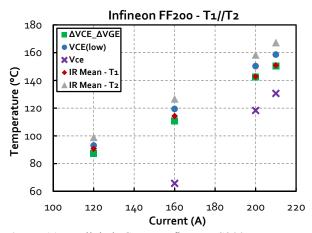

Figure 6 IGBT 1, Infineon FF200; temperature measurement via TSEPs and IR camera during current injection

Figure 7 IGBT 1, Infineon FF600; temperature measurement via TSEPs and IR camera during current injection

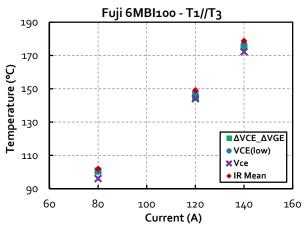

Figure 8 IGBT 1, Fuji 6MBI100; temperature measurement via TSEPs and IR camera during current injection

In the case of the traditional  $V_{CE(low)}$  measurement, results are in accordance with previous research and closely match IR<sub>Mean</sub>, sometimes with a slight overestimation [9]. Clearly, temperature measurement via the normal-V<sub>CE</sub> led to vastly inaccurate results. These errors can swing from +50°C to -50°C across the current range for chips inside Infineon modules. For the Fuji 6MBI100, the results are markedly better: errors are generally within -20°C, and at higher current levels this decreases to just a 5°C underestimation of  $IR_{\text{Mean}}.$

Nevertheless, the  $\Delta V_{CE\_\Delta VGE}$  temperature measurement method demonstrates significant improvement over the normal-V<sub>CE</sub> for all chips tested. In the FS200 module, errors of over 50°C with respect to IR<sub>Mean</sub> are reduced to between -3°C to -7°C. A sizeable error in the region -10°C is observed on IGBTs in the FF600 module, however the error appears to be reasonably consistent throughout all current levels. Once again, the Fuji 6MBI100 module displayed better results in comparison to the Infineon modules, with temperature measurement via  $\Delta V_{CE\_\Delta VGE}$  within -1°C to -6°C of IR<sub>Mean</sub>.

**Table 3** Synthesis of the TSEP deviations from  $IR_{Mean}$  forIGBT junction temperature measurement on single chips

| Module            | TSEP                        | IGBT | Min_Diff<br>(°C) | Max_Diff<br>(°C) |

|-------------------|-----------------------------|------|------------------|------------------|

| 7                 | V <sub>CE</sub>             | T1   | -48              | +71              |

|                   |                             | T2   | -52              | +76              |

| 4E01<br>200       | $\Delta V_{CE\_\Delta VGE}$ | T1   | -3               | -7               |

| INFINEON<br>FS200 |                             | T2   | -4               | -7               |

|                   | V <sub>CE(low)</sub>        | T1   | 0                | +5               |

|                   |                             | T2   | 0                | +3               |

|                   |                             |      | - 0              | < <b>-</b>       |

|                   | $V_{\text{CE}}$             | T1   | -50              | +67              |

| INFINEON<br>FF600 |                             | T2   | -50              | +78              |

|                   | $\Delta V_{CE\_\Delta VGE}$ | T1   | -9               | -12              |

|                   |                             | T2   | -9               | -13              |

|                   | V <sub>CE(low)</sub>        | T1   | +1               | -2               |

|                   |                             | T2   | +1               | -2               |

|                   |                             | 1    |                  |                  |

| FUJI<br>6MB1100   | $V_{CE\_Ip}$                | T1   | -7               | -18              |

|                   |                             | Т3   | -5               | -11              |

|                   | $\Delta V_{CE\_\Delta VGE}$ | T1   | -3               | -6               |

|                   |                             | Т3   | -1               | -6               |

|                   | V <sub>CE(low)</sub>        | T1   | -1               | +1               |

|                   |                             | Т3   | -0               | +2               |

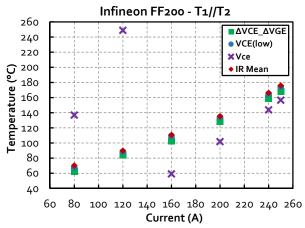

#### 4.2 Paralleled IGBTs

Evaluation of two paralleled IGBTs was feasible in the FF200 and 6MBI100 modules. Graphical depiction of these results can be found in Figures 9 and 10. Here, IR- $_{Mean}$  is calculated as a single mean temperature comprising of the surface of both IGBTs. Table 4 provides minimum and maximum deviations from IR<sub>Mean</sub> for each TSEP.

The results follow the largely the same trend as seen with single IGBTs, with  $\Delta V_{CE\_\Delta VGE}$  presenting a large improvement in accuracy over the normal-V<sub>CE</sub> method. Temperature estimation on the Fuji 6MBI100 is within -5°C of IR<sub>Mean</sub>, while in the Infineon FS200 the discrepancy was between -5°C and -9°C.

Figure 9 Paralleled IGBTs, Infineon FF200; temperature measurement via TSEPs and IR camera

Figure 10 Paralleled IGBTs, Fuji 6MBI100; temperature measurement via TSEPs and IR camera

**Table 4** Synthesis of the TSEP deviations from  $IR_{Mean}$  forIGBT junction temperature measurement on two paralleled devices

| Module            | TSEP                         | IGBT   | Min_Diff<br>(°C) | Max_Diff<br>(°C) |

|-------------------|------------------------------|--------|------------------|------------------|

| NO<br>NO          | $V_{CE}$                     | T1//T2 | -52              | +160             |

| INFINEON<br>FS200 | $\Delta V_{CE \ \Delta VGE}$ | T1//T2 | -5               | -9               |

| INF<br>F          | V <sub>CE(low)</sub>         | T1//T2 | -1               | -3               |

|                   |                              |        |                  |                  |

| FUJI<br>6MBI100   | $V_{CE}$                     | T1//T3 | -5               | -7               |

|                   | $\Delta V_{CE \ \Delta VGE}$ | T1//T3 | -2               | -5               |

|                   | V <sub>CE(low)</sub>         | T1//T3 | -1               | -2               |

#### 4.3 Paralleled IGBTs with Temperature Disequilibrium

The Infineon FS200R12PT4 structure allowed a test with a temperature gradient between two paralleled IGBTs. Loosening one side of the module, one chip was left with a worse thermal contact to the heatsink. Fig. 11 displays the results of TSEP temperature measurements in this condition. In these figures, an IR<sub>Mean</sub> is displayed for each separate chip. The temperature difference between the two IGBTs is more than 20°C at the highest current level.

**Figure 11** Paralleled IGBTs, Infineon FS200; temperature measurement via TSEPs and IR camera with temperature disequilibrium between chips

While the normal- $V_{CE}$  once again delivers wildly inaccurate results, the  $\Delta V_{CE\_\Delta VGE}$  measurement provided a temperature always IGBT to the chip with the coolest mean temperature (IGBT 1). This is within -4°C of the coolest chip at all current levels.

# 5 Discussion

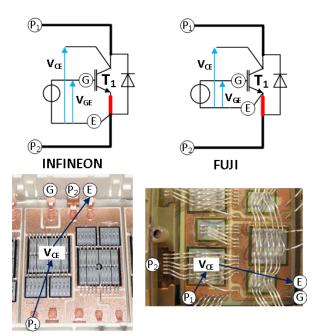

The more favourable results experienced on the Fuji 6MBI100 may be explained by viewing the module layout. Fig. 12 displays images of the internal layout of both the Infineon FS200 and Fuji 6MBI100 modules and a schematic of the measurement points used. It can be seen that in the Fuji 6MBI100, a kelvin connection is possible for the measurement of the  $V_{CE}$  by using the gate-emitter terminal: the gate-emitter path is separate from the load current carrying path for the power-emitter (P2). On the other hand, both the power-emitter and the gate-emitter share the same load current carrying path in the Infineon FS200, and a kelvin connection for  $V_{CE}$  measurement is not possible.

# 6 Conclusion

This paper uses an IR camera to experimentally evaluate TSEP methods for IGBT junction temperature measurement based on the collector-emitter voltage. Experimental validation is performed on a variety of IGBT modules with differing geometry and manufacturer, and includes verification on paralleled chips. The normal-V<sub>CE</sub> at high current is shown to give vastly inaccurate results. A modified- $V_{CE}$  method is thus proposed, which is based on the difference in V<sub>CE</sub> at two different gate voltages (15V and 13V). This method is designed to remove the resistive contribution of interconnection materials at high current levels. The modified-V<sub>CE</sub> method, referred to as  $\Delta V_{CE \ \Delta VGE}$ , shows significant improvement in accuracy, with maximum errors typically within -10°C of the mean junction temperature as measured with an IR camera. Some modules appear to be more suited to temperature measurement using V<sub>CE</sub>-based techniques than others.

**Figure 12** Power module layouts of F200 and 6MBI100, and schematic for electrical measurements

## 7 Acknowledgement

The authors thank the French National Research Agency (MEMPHIS ANR-13-PRGE-0005-01 PROGELEC project)

#### 8 **References**

- N. Baker, M. Liserre, L. Dupont, Y. Avenas, "Improved Reliability of Power Modules: A Review of Online Junction Temperature Measurement Methods", *IEEE Industrial Electronics Magazine*, vol.8, no.3, pp.17-27, Sept. 2014.

- [2] D.-L. Blackburn, "Temperature measurements of semiconductor devices—A review", in *Proc. 20th Annu. Semicond. Therm. Meas. Manage. Symp.*, San Jose, CA, Mar. 11–24, 2004,

- [3] D.L. Blackburn, "A review of thermal characterization of power transistors", in *Proc. IEEE Semicond. Therm. Temp. Meas. Symp.*, San Diego, Feb. 10–12, 1988.

- [4] Y. Avenas, L. Dupont, Z. Khatir, "Temperature Measurement of Power Semiconductor Devices by Thermo-Sensitive Electrical Parameters—A Review", *IEEE Trans. Power Electron.*, vol.27, no.6, pp.3081-3092, June 2012.

- [5] D. Wagenitz, C. Läuschner, R. Thewes, S. Dieckerhoff, "Design and Evaluation of a Sensor for Measuring the IGBT On-State Saturation Voltage", PCIM Europe, Nuremberg, Germany, May 2015.

- [6] S. Beczkowski, P. Ghimre, A.R. de Vega, S. Munk-Nielsen, B. Rannestad, P. Thogersen, "Online Vce measurement method for wear-out monitoring of high power IGBT modules", European Conference on Power Electronics and Applications (EPE), pp.1,7, 2-6 Sept. 2013.

- [7] L. Dupont, Y. Avenas, "Evaluation of thermo-sensitive electrical parameters based on the forward voltage for on-line chip temperature measurements of IGBT devices", ECCE 2014, Sept. 2014

- [8] X. Perpina, J. F. Serviere, J. Saiz, D. Barlini, M. Mermet-Guyennet, and J. Millan, "Temperature measurement on series resistance and devices in power packs based on on-state voltage drop monitoring at high current", Microelectron. Reliabil., vol. 46, pp. 1834–1839, 2006.

- [9] R. Schmidt, U. Scheuermann, "Using the chip as a temperature sensor — The influence of steep lateral temperature gradients on the Vce(T)-measurement," 13th European Conference on Power Electronics and Applications 2009, pp.1-9, 8-10 Sept. 2009.

- [10] N. Baker, L. Dupont, S. Munk-Nielsen, F. Iannuzzo, M. Liserre, "Experimental Evaluation of IGBT Junction Temperature Measurement via Peak Gate Current", European Conference on Power Electronics and Applications (EPE), pp.1,7, 2-6 Sept. 2015.

- [11] N. Baker, S. Munk-Nielsen, F. Iannuzzo, M. Liserre, "IGBT Junction Temperature Measurement via Peak Gate Current," IEEE Trans. Power Electron., vol. 31, no.5, pp. 3784-3793, May 2016.