High temperature operation of SiC transistors ATW on Thermal Management, Los Gatos

> Cyril BUTTAY<sup>1</sup>, Marwan ALI<sup>2</sup>, Oriol AVINO<sup>1,2</sup>, Hervé MOREL<sup>1</sup>, Bruno ALLARD<sup>1</sup>

<sup>1</sup> Laboratoire Ampère, Lyon, France <sup>2</sup> Labinal Power Systems, SAFRAN Group, France

23/9/15

Introduction

High-Temperature behaviour of SiC Devices

Packaging for high-temperature converters

Conclusion

## Introduction

High-Temperature behaviour of SiC Devices

Packaging for high-temperature converters

Conclusion

| Vehicle Location                | Max Temp (℃) |

|---------------------------------|--------------|

| Drive train high temp location  | 177          |

| Floor                           | 85           |

| Near radiator support structure | 100          |

| Back of alternator              | 160          |

| Cooling circuit                 | 120          |

| Exhaust manifold                | 649          |

Most data: Kassakian, J. G. et al. "The Future of Electronics in Automobiles", ISPSD, 2001, p 15-19

- Low-cost, high-volume applications;

- Moving to higher voltages (12V->300V for hybrids)

- ► Little cooling headroom with silicon devices (T<sub>J</sub>=150 to 175 °C)

| Vehicle Location                | Max Temp (℃) |

|---------------------------------|--------------|

| Drive train high temp location  | 177          |

| Floor                           | 85           |

| Near radiator support structure | 100          |

| Back of alternator              | 160          |

| Cooling circuit                 | 120          |

| Exhaust manifold                | 649          |

Most data: Kassakian, J. G. et al. "The Future of Electronics in Automobiles", ISPSD, 2001, p 15-19

- Low-cost, high-volume applications;

- Moving to higher voltages (12V->300V for hybrids)

- ► Little cooling headroom with silicon devices (T<sub>J</sub>=150 to 175 °C)

| Vehicle Location                | Max Temp (℃) |

|---------------------------------|--------------|

| Drive train high temp location  | 177          |

| Floor                           | 85           |

| Near radiator support structure | 100          |

| Back of alternator              | 160          |

| Cooling circuit                 | 120          |

| Exhaust manifold                | 649          |

Most data: Kassakian, J. G. et al. "The Future of Electronics in Automobiles", ISPSD, 2001, p 15-19

- Low-cost, high-volume applications;

- Moving to higher voltages (12V->300V for hybrids)

- ► Little cooling headroom with silicon devices (T<sub>J</sub>=150 to 175 °C)

- dedicated cooling circuit for power electronic systems

# Aircraft

#### The trend:

- Hydraulic, Pneumatic and Electric networks co-exist in current systems

- More-electric aircraft should reduce complexity

- objective: 1 MW on-board electrical power

### From mild to very harsh:

- Some system are located in the cabin

- Jet engine actuator will face -55°C to 225°C cycling

- Many systems are located in non-pressurised areas

- Long system life: around 30 years

- Reliability is the main concern

- Hydraulic, Pneumatic and Electric networks co-exist in current systems

- More-electric aircraft should reduce complexity

- objective: 1 MW on-board electrical power

### The environment:

- From mild to very harsh:

- Some system are located in the cabin

- Jet engine actuator will face -55°C to 225°C cycling

- Many systems are located in non-pressurised areas

- Long system life: around 30 years

- Reliability is the main concern

- Hydraulic, Pneumatic and Electric networks co-exist in current systems

- More-electric aircraft should reduce complexity

- objective: 1 MW on-board electrical power

The environment:

- From mild to very harsh:

- Some system are located in the cabin

- ► Jet engine actuator will face -55 °C to 225 °C cycling

- Many systems are located in non-pressurised areas

- Long system life: around 30 years

Reliability is the main concern

- Hydraulic, Pneumatic and Electric networks co-exist in current systems

- More-electric aircraft should reduce complexity

- objective: 1 MW on-board electrical power

The environment:

- From mild to very harsh:

- Some system are located in the cabin

- ► Jet engine actuator will face -55 °C to 225 °C cycling

- Many systems are located in non-pressurised areas

- Long system life: around 30 years

Reliability is the main concern

- Hydraulic, Pneumatic and Electric networks co-exist in current systems

- More-electric aircraft should reduce complexity

- objective: 1 MW on-board electrical power

The environment:

- From mild to very harsh:

- Some system are located in the cabin

- ► Jet engine actuator will face -55 °C to 225 °C cycling

- Many systems are located in non-pressurised areas

- Long system life: around 30 years

- Reliability is the main concern

### NASA missions to Venus and Jupiter

- ► Venus surface temperature : up to 480 °C

- ► Pressure a few kilometres inside Jupiter: 100 bars, at 400 °C

- Strong thermal cycling, as temperature can drop to 140K at night;

# Deep oil/gas extraction

- Continuous operation, relatively low cycling

- Deep drilling: high ambient temperature (up to 225°C)

- Expected lifetime: 5 years

- Main requirement: sensors and datalogging

- Example of new applications: downhole gas compressor

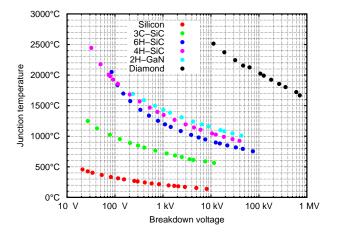

### Maximum operating temperature

Silicon operating temp is intrisically limited at high voltages.

▶ 1200 V devices rated at <200 °C junction temperature

Introduction

# High-Temperature behaviour of SiC Devices

Packaging for high-temperature converters

Conclusion

# Test configuration

- High temperature test system

- Silver-sintered interconnects

- Ceramic substrate (DBC)

- Copper-kapton leadframe

- DUT: 490 mΩ SiC JFET from SiCED

- characterization:

- Tektronix 371A curve tracer

- Thermonics T2500-E conditionner

# Test configuration

- High temperature test system

- Silver-sintered interconnects

- Ceramic substrate (DBC)

- Copper-kapton leadframe

- DUT: 490 mΩ SiC JFET from SiCED

- characterization:

- Tektronix 371A curve tracer

- Thermonics T2500-E conditionner

# **Test configuration**

- High temperature test system

- Silver-sintered interconnects

- Ceramic substrate (DBC)

- Copper-kapton leadframe

- DUT: 490 mΩ SiC JFET from SiCED

- characterization:

- Tektronix 371A curve tracer

- Thermonics T2500-E conditionner

Source: Thermonics T-2500E Datasheet

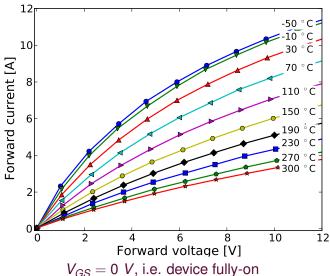

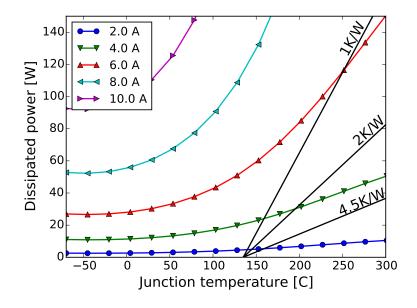

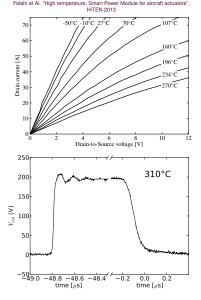

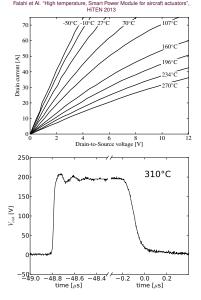

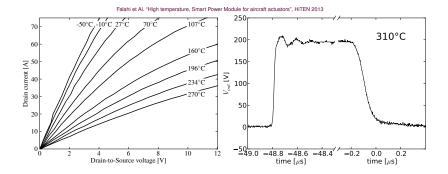

### Static Characterization of 490 m $\Omega$ JFET

Buttay et Al. "Thermal Stability of Silicon Carbide Power JFETs" IEEE transactions on Electron Devices, 2013, 60, 4191-4198

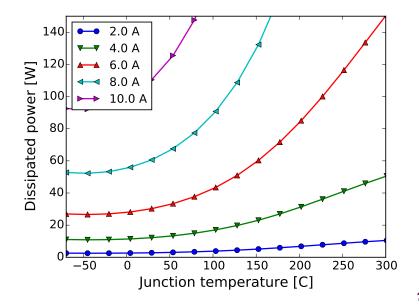

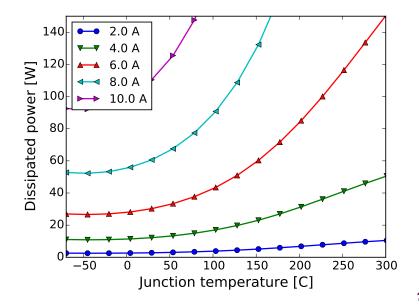

### Power dissipation as a function of the junction temp.

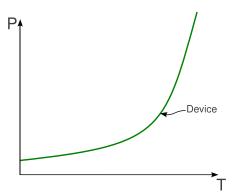

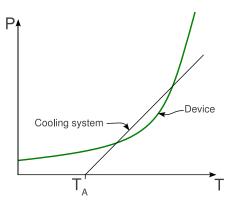

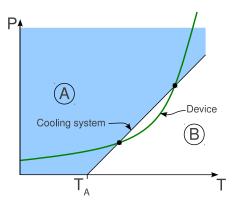

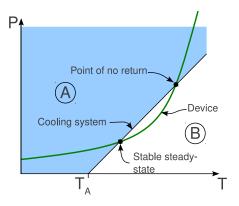

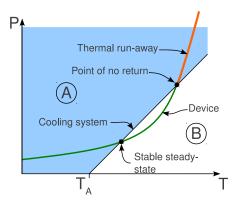

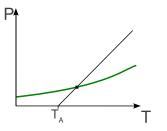

### The device characteristic

- Its associated cooling system

- In region A, the device dissipates more than the cooling system can extract

- In region B, the device dissipates less than the cooling system can extract

- Two equilibrium points: one stable and one unstable

- Above the unstable point, run-away occurs

- The device characteristic

- Its associated cooling system

- In region A, the device dissipates more than the cooling system can extract

- In region B, the device dissipates less than the cooling system can extract

- Two equilibrium points: one stable and one unstable

- Above the unstable point, run-away occurs

- The device characteristic

- Its associated cooling system

- In region A, the device dissipates more than the cooling system can extract

- In region B, the device dissipates less than the cooling system can extract

- Two equilibrium points: one stable and one unstable

- Above the unstable point, run-away occurs

- The device characteristic

- Its associated cooling system

- In region A, the device dissipates more than the cooling system can extract

- In region B, the device dissipates less than the cooling system can extract

- Two equilibrium points: one stable and one unstable

- Above the unstable point, run-away occurs

- The device characteristic

- Its associated cooling system

- In region A, the device dissipates more than the cooling system can extract

- In region B, the device dissipates less than the cooling system can extract

- Two equilibrium points: one stable and one unstable

- Above the unstable point, run-away occurs

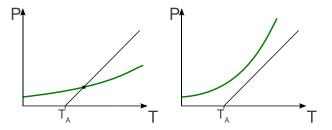

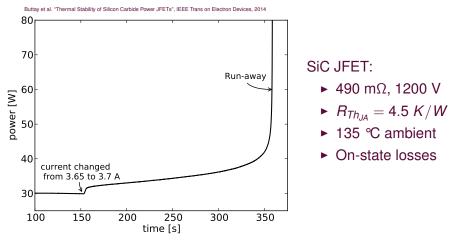

### Thermal Run-away mechanism – examples

Always stable

14/32

### Thermal Run-away mechanism – examples

Always stable

Always unstable

14/32

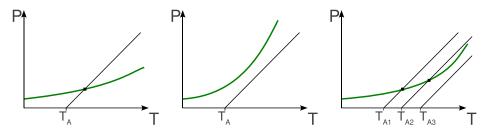

### Thermal Run-away mechanism – examples

Always stable

Always unstable

Becomming unstable with ambient temperature rise

### Power dissipation as a function of the junction temp.

15/32

### Power dissipation as a function of the junction temp.

### High Temperature Thermal Management

High temperature capability  $\neq$  reduced cooling needs! SiC JFETs must be attached to a low- $R_{Th}$  cooling system.

### ► SiC JFETs can operate at > 200 °C

- ► *R<sub>DSon</sub>* dependent on temperature

- sensitive to thermal run-away

- Require efficient thermal management

- Iow thermal resistance (1-2 K/W)

- low or high ambient temperature (> 200 °C possible)

- ▶ SiC JFETs can operate at > 200 °C

- ► *R<sub>DSon</sub>* dependent on temperature

- sensitive to thermal run-away

- Require efficient thermal management

- Iow thermal resistance (1-2 K/W).

- low or high ambient temperature (> 200 °C possible)

- SiC JFETs can operate at > 200 °C

- ► *R<sub>DSon</sub>* dependent on temperature

- sensitive to thermal run-away

- Require efficient thermal management

- low mermal resistance (1-2 k/www. low or high ambient temperatures (> 200 °C possible)

- ► SiC JFETs can operate at > 200 °C

- ► *R*<sub>DSon</sub> dependent on temperature

- sensitive to thermal run-away

- Require efficient thermal management

- low thermal resistance (1-2 K/W)

- low or high ambient temperature (> 200 °C possible)

Introduction

High-Temperature behaviour of SiC Devices

Packaging for high-temperature converters

Conclusion

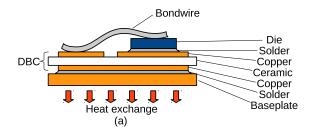

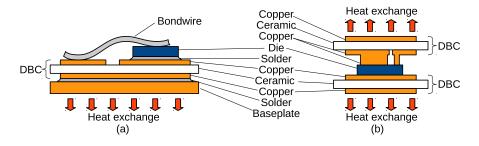

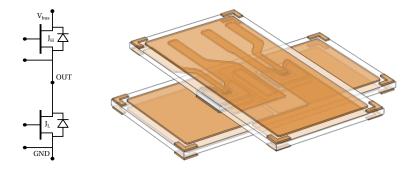

# **Double Side Cooling**

- Standard packaging offers cooling through one side of the die only

- "3-D" or "Sandwich" package offers thermal management on both sides

- Requires suitable topside metal on the die

- Requires special features for topside contact

# **Double Side Cooling**

- Standard packaging offers cooling through one side of the die only

- "3-D" or "Sandwich" package offers thermal management on both sides

- Requires suitable topside metal on the die

- Requires special features for topside contact

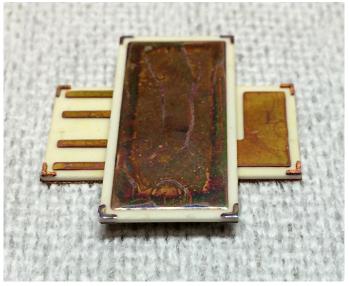

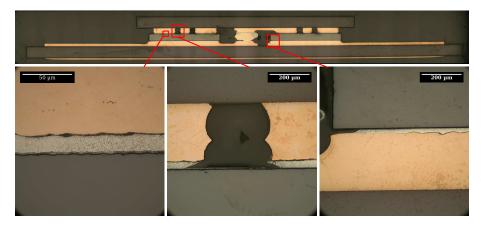

## The proposed 3-D Structure

- Two ceramic substrates, in "sandwich" configuration

- Two SiC JFET dies (SiCED)

- assembled using silver sintering

- ► 25.4 mm×12.7 mm (1 in×0.5 in)

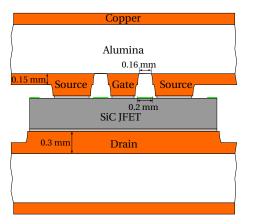

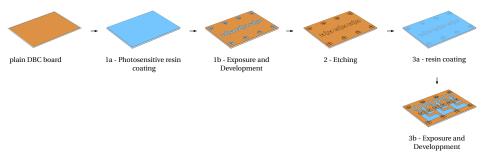

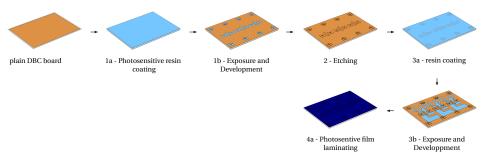

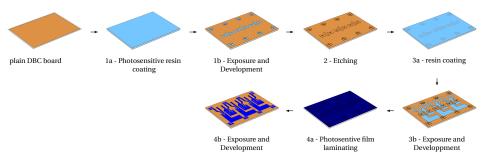

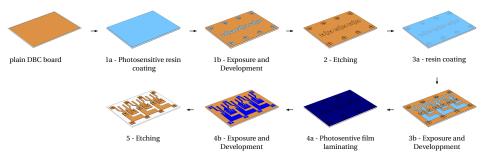

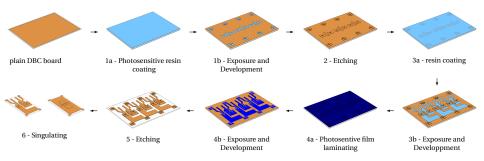

## **Ceramic Substrates**

Scale drawing for 2.4  $\times 2.4~\text{mm}^2$  die

- Si<sub>3</sub>N<sub>4</sub> identified previously for high temperature

- For development: use of alumina

- Etching accuracy exceeds standard design rules

- Double-step copper etching for die contact

- → Custom etching technique

# Bonding Material: Silver Sintering

Göbl, C. et al "Low temperature sinter technology Die attachment for automotive power electronic applications" proc of APE, 2006

### Silver Paste

- Based on micro-scale silver particles (Heraeus LTS-117O2P2)

- ► Low temperature (240 °C) sintering

- Low pressure (2 MPa) process

### No liquid phase involved:

- No movement of the die

- No bridging across terminals

- No height compensation thanks to wetting

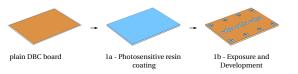

plain DBC board

- Final patterns within 50  $\mu$ m of desired size

- Two designs, for 2.4×2.4 mm<sup>2</sup> and 4×4 mm<sup>2</sup> dies

- Total copper thickness 300  $\mu$ m, pprox 150  $\mu$ m per step

- Final patterns within 50  $\mu$ m of desired size

- Two designs, for 2.4×2.4 mm<sup>2</sup> and 4×4 mm<sup>2</sup> dies

- Total copper thickness 300  $\mu$ m, pprox 150  $\mu$ m per step

- Final patterns within 50  $\mu$ m of desired size

- Two designs, for 2.4×2.4 mm<sup>2</sup> and 4×4 mm<sup>2</sup> dies

- Total copper thickness 300  $\mu$ m, pprox 150  $\mu$ m per step

- Final patterns within 50  $\mu$ m of desired size

- Two designs, for 2.4×2.4 mm<sup>2</sup> and 4×4 mm<sup>2</sup> dies

- Total copper thickness 300  $\mu$ m, pprox 150  $\mu$ m per step

- Final patterns within 50  $\mu$ m of desired size

- Two designs, for 2.4×2.4 mm<sup>2</sup> and 4×4 mm<sup>2</sup> dies

- Fotal copper thickness 300  $\mu$ m,  $\approx$  150  $\mu$ m per step

- Final patterns within 50  $\mu$ m of desired size

- Two designs, for 2.4×2.4 mm<sup>2</sup> and 4×4 mm<sup>2</sup> dies

- Fotal copper thickness 300  $\mu$ m,  $\approx$  150  $\mu$ m per step

- Final patterns within 50  $\mu$ m of desired size

- Two designs, for 2.4×2.4 mm<sup>2</sup> and 4×4 mm<sup>2</sup> dies

- Fotal copper thickness 300  $\mu$ m,  $\approx$  150  $\mu$ m per step

- Final patterns within 50  $\mu$ m of desired size

- Two designs, for 2.4×2.4 mm<sup>2</sup> and 4×4 mm<sup>2</sup> dies

- Fotal copper thickness 300  $\mu$ m, pprox 150  $\mu$ m per step

- Final patterns within 50  $\mu$ m of desired size

- Two designs, for 2.4×2.4 mm<sup>2</sup> and 4×4 mm<sup>2</sup> dies

- Fotal copper thickness 300  $\mu$ m,  $\approx$  150  $\mu$ m per step

- Final patterns within 50  $\mu$ m of desired size

- Two designs, for 2.4×2.4 mm<sup>2</sup> and 4×4 mm<sup>2</sup> dies

- Fotal copper thickness 300  $\mu$ m, pprox 150  $\mu$ m per step

- ► Final patterns within 50 µm of desired size

- ► Two designs, for 2.4×2.4 mm<sup>2</sup> and 4×4 mm<sup>2</sup> dies

- ► Total copper thickness 300  $\mu$ m,  $\approx$  150  $\mu$ m per step

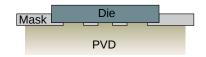

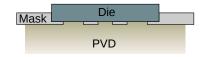

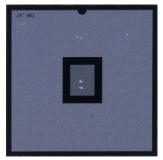

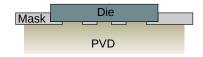

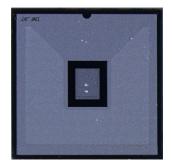

## Preparation of the Dies

- Standard aluminium topside finish not compatible with silver sintering

- Ti/Ag PVD on contact areas

- Need for a masking solution

- ➔ jig with locating pockets.

## Preparation of the Dies

- Standard aluminium topside finish not compatible with silver sintering

- Ti/Ag PVD on contact areas

- Need for a masking solution

- → jig with locating pockets.

#### Before PVD

## Preparation of the Dies

- Standard aluminium topside finish not compatible with silver sintering

- Ti/Ag PVD on contact areas

- Need for a masking solution

- → jig with locating pockets.

24/32

After Ti/Ag PVD

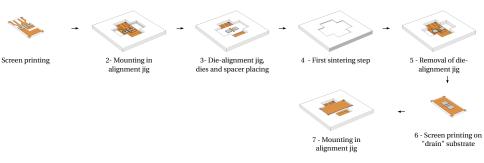

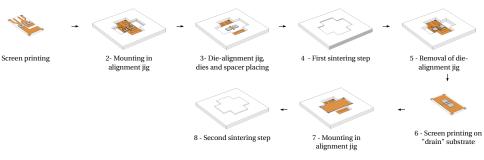

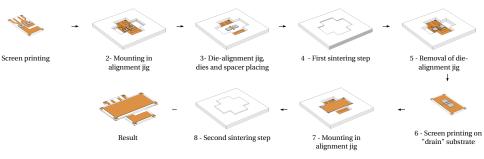

Screen printing

- Ceramic laser-cut jigs for precise alignment of dies and substrate

- ► Two sintering steps using the same temperature profile

Screen printing

2- Mounting in alignment jig

- Ceramic laser-cut jigs for precise alignment of dies and substrate

- Two sintering steps using the same temperature profile

- Ceramic laser-cut jigs for precise alignment of dies and substrate

- Two sintering steps using the same temperature profile

- Ceramic laser-cut jigs for precise alignment of dies and substrate

- Two sintering steps using the same temperature profile

- Ceramic laser-cut jigs for precise alignment of dies and substrate

- Two sintering steps using the same temperature profile

6 - Screen printing on "drain" substrate

- Ceramic laser-cut jigs for precise alignment of dies and substrate

- Two sintering steps using the same temperature profile

- Ceramic laser-cut jigs for precise alignment of dies and substrate

- Two sintering steps using the same temperature profile

- Ceramic laser-cut jigs for precise alignment of dies and substrate

- Two sintering steps using the same temperature profile

- Ceramic laser-cut jigs for precise alignment of dies and substrate

- Two sintering steps using the same temperature profile

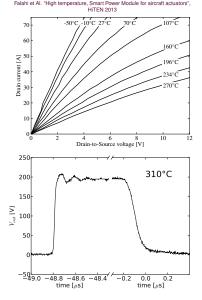

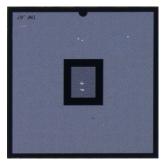

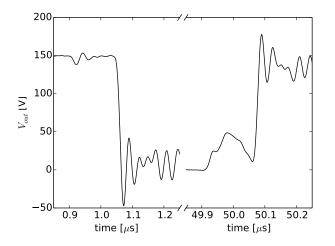

### Some results

### Size: 25×25 mm<sup>2</sup>

300 Ω Resistive load, 0.5 A current (no cooling system used)

oscillations dues to external layout

Introduction

High-Temperature behaviour of SiC Devices

Packaging for high-temperature converters

Conclusion

### ► SiC JFET able to operate continuously at high temperature(> 200 °C)

- Must be provided with efficient thermal management (R<sub>Th</sub> =1-2 K/W)

- Proposition: introduce dual-side cooling

- 3D structure using only high-temperature-rated materials

- Should be able to operate continuously at 300 °C, including passivation (parylene HT or F)

- Proposed etching technique offers satisfying resolution

- Silver sintering used for the interconnects, reliability to be investigated

- Package for demonstration of technology, no cooling attempted yet!

- ► SiC JFET able to operate continuously at high temperature(> 200 °C)

- ► Must be provided with efficient thermal management (R<sub>Th</sub> =1-2 K/W)

- Proposition: introduce dual-side cooling

- 3D structure using only high-temperature-rated materials

- Should be able to operate continuously at 300 °C, including passivation (parylene HT or F)

- Proposed etching technique offers satisfying resolution

- Silver sintering used for the interconnects, reliability to be investigated

- Package for demonstration of technology, no cooling attempted yet!

- ► SiC JFET able to operate continuously at high temperature(> 200 °C)

- Must be provided with efficient thermal management (R<sub>Th</sub> =1-2 K/W)

- Proposition: introduce dual-side cooling

- 3D structure using only high-temperature-rated materials

- Should be able to operate continuously at 300 °C, including passivation (parylene HT or F)

- Proposed etching technique offers satisfying resolution

- Silver sintering used for the interconnects, reliability to be investigated

- Package for demonstration of technology, no cooling attempted yet!

- ► SiC JFET able to operate continuously at high temperature(> 200 °C)

- Must be provided with efficient thermal management (R<sub>Th</sub> =1-2 K/W)

- Proposition: introduce dual-side cooling

- 3D structure using only high-temperature-rated materials

- Should be able to operate continuously at 300 °C, including passivation (parylene HT or F)

- Proposed etching technique offers satisfying resolution

- Silver sintering used for the interconnects, reliability to be investigated

- Package for demonstration of technology, no cooling attempted yet!

- ► SiC JFET able to operate continuously at high temperature(> 200 °C)

- ► Must be provided with efficient thermal management (R<sub>Th</sub> =1-2 K/W)

- Proposition: introduce dual-side cooling

- 3D structure using only high-temperature-rated materials

- Should be able to operate continuously at 300 °C, including passivation (parylene HT or F)

- Proposed etching technique offers satisfying resolution

- Silver sintering used for the interconnects, reliability to be investigated

- Package for demonstration of technology, no cooling attempted yet!

This work was funded by Euripides-Catrenes under the grant name "THOR" and FRAE under the grant name "ETHAER".

cyril.buttay@insa-lyon.fr

### Credits

- picture of the Airbus A350: airbus

- picture of the thrust reverser: Hispano-Suiza http://www.hispano-suiza-sa.com/spip.php?rubrique48

- picture of the Toyota Prius: Picture by Pawel Golsztajn, CC-SA, available on Wikimedia Commons http: //commons.wikimedia.org/wiki/File:Toyota\_Prius.2.JPG

- downhole gas compressor: http: //www.corac.co.uk/products/downhole-gas-compressor

- picture of Jupiter: NASA http://en.wikipedia.org/wiki/File:PIA04866\_modest.jpg

- MOSFET wafers from Mitsubishi http://compoundsemiconductor.net/cws/article/fab/ 38238/1/siliconcarbidewafers

# Static and Dynamic Characterization of 60 m $\Omega$ JFET

Previous results show that SiC JFETs are attractive for > 200  $^\circ\!C$  operation:

- rated at 1200 V (or more), several Amps

- Voltage-controlled devices

- No reliability issue related to gate oxide degradation

### Properties of some semiconductors

|                                                                             | "Classical"       |                   | wide-bandgap        |                     |                   |                   |                   |

|-----------------------------------------------------------------------------|-------------------|-------------------|---------------------|---------------------|-------------------|-------------------|-------------------|

|                                                                             | Si                | GaAs              | 3C-<br>SiC          | 6H-<br>SiC          | 4H-<br>SiC        | GaN               | Diamond           |

| Bandgap Energy<br><i>E</i> g (eV)                                           | 1,12              | 1,4               | 2,3                 | 2,9                 | 3,2               | 3,39              | 5,6               |

| Elec. mobility $\mu_n$ (cm <sup>2</sup> .V <sup>-1</sup> .s <sup>-1</sup> ) | 1450              | 8500              | 1000                | 415                 | 950               | 2000              | 4000              |

| Hole mobility $\mu_p$ (cm <sup>2</sup> .V <sup>-1</sup> .s <sup>-1</sup> )  | 450               | 400               | 45                  | 90                  | 115               | 350               | 3800              |

| Critical elec. field $E_C$ (V.cm <sup>-1</sup> )                            | 3.10 <sup>5</sup> | 4.10 <sup>5</sup> | 2.10 <sup>6</sup>   | 2,5.10 <sup>6</sup> | 3.10 <sup>6</sup> | 5.10 <sup>6</sup> | 10 <sup>7</sup>   |

| Saturation velocity $v_{sat}$ (cm.s <sup>-1</sup> )                         | 10 <sup>7</sup>   | 2.10 <sup>7</sup> | 2,5.10 <sup>7</sup> | 2.10 <sup>7</sup>   | 2.10 <sup>7</sup> | 2.10 <sup>7</sup> | 3.10 <sup>7</sup> |

| Termal cond. $\lambda$ (W.cm <sup>-1</sup> .K <sup>-1</sup> )               | 1,3               | 0,54              | 5                   | 5                   | 5                 | 1,3               | 20                |

Ampere