## Efficient Substrate Noise Coupling Verification and Failure Analysis Methodology for Smart Power ICs in Automotive Applications

Yasser Moursy, Hao Zou, Raouf Khalil, Ramy Iskander, Pierre Tisserand, Dieu-My Ton, Giuseppe Pasetti, Marie-Minerve Louërat

#### ▶ To cite this version:

Yasser Moursy, Hao Zou, Raouf Khalil, Ramy Iskander, Pierre Tisserand, et al.. Efficient Substrate Noise Coupling Verification and Failure Analysis Methodology for Smart Power ICs in Automotive Applications. IEEE Transactions on Power Electronics, 2016, 10.1109/TPEL.2016.2604818. hal-01360881

HAL Id: hal-01360881

https://hal.science/hal-01360881

Submitted on 6 Sep 2016

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Efficient Substrate Noise Coupling Verification and Failure Analysis Methodology for Smart Power ICs in Automotive Applications

Yasser Moursy, *Student Member, IEEE*, Hao Zou, Raouf Khalil, Ramy Iskander, Pierre Tisserand, Dieu-My Ton, Giuseppe Pasetti, and Marie-Minerve Louërat

Abstract—This paper presents a methodology to analyze the substrate noise coupling and reduce their effects in smart power integrated circuits. This methodology considers the propagation of minority carriers in the substrate. Hence, it models the lateral bipolar junction transistors that are layout dependent and are not modeled in conventional substrate extraction tools. It allows the designer to simulate substrate currents and check their effects on circuits functionality. The proposed methodology employs a dedicated tool for substrate network generation referred to as AUTOMICS. We applied the methodology on two test cases. The first case is a DC-DC buck converter chip fabricated with a 0.35  $\mu$ m HV-CMOS technology. The DC coupling current between the switches and the bandgap circuit is simulated and verified with measurements. The second test case is an automotive industrial chip that has a latch-up failure due to substrate coupling. In transient simulations, the failure has been reproduced as in measurements. This highlights the stronghold of the methodology since it can be used to prevent this type of failures before fabrication. The proposed methodology can reduce the number of redesigns in the automotive industry. Hence, it shortens the time-to-market, improves the robustness of the design, and reduces the cost.

Index Terms—Semiconductor device noise, Semiconductor device modeling, DC-DC power conversion, Power FET switches, Failure analysis

#### I. INTRODUCTION

OWADAYS, the electronic systems are extensively employed in the automotive industry. These emerging technologies are mainly deployed to offer safer and more comfortable environment for the automobile driver. The trend in the automotive technology is to enhance the vehicle connectivity to the internet as a part of internet of things (IoT) and to reduce the CO<sub>2</sub> emission. Furthermore, the reliability and durability are the main two features for the automotive electronic applications.

Smart power ICs are employed in the automotive industry since they incorporate the high voltage (HV) and low voltage (LV) circuits on the same die [1]. This feature allows to miniaturize the electronic systems and implement more functionality in the vehicles. However, the substrate noise coupling in the smart power ICs becomes a severe issue.

Yasser Moursy, Hao Zou, Raouf Khalil, Ramy Iskander, and Marie-Minerve Louërat are with Sorbonne Universities, UPMC Univ Paris 06 and CNRS, UMR 7606, LIP6, F-75005, Paris, France (e-mail:yasser.moursy@lip6.fr)

Pierre Tisserand and Dieu-My Ton are with Valeo, Creteil, France. Giuseppe Pasetti is with AMS, Navacchio (PI), Italy.

Failures due to the substrate noise coupling are still reported in tests after fabrication. Most of these failures are caused by the minority carriers propagation since their behavior can not be predicted by the current commercial tools. Therefore, we need to investigate the minority carriers propagation in the substrate and their modeling techniques to validate the capability of simulation for such complicated behavior.

In smart power ICs, the HV circuits commonly drive inductive loads. The presence of such loads stimulates parasitic components and injects minority carriers in the substrate. The noise due to minority carriers injection is function of the operating voltages and currents. This noise becomes nonnegligible and can cause significant effects, such as latch-up. Therefore, techniques were investigated to study the substrate coupling due to the minority carriers propagation. In [2], the noise in smart power ICs was addressed and a TCADguided design methodology for substrate current investigation was proposed. Addressing more complex structure with this methodology could be impractical as it takes excessively long time. In [3], the PN junction and resistor models were modified by additional terminal to take into account the minority carrier concentrations and gradients at the boundaries. These enhanced models can be used to create a substrate network which considers the minority carriers propagation in the substrate. A manually extracted 3D substrate parasitic network was simulated and the DC coupling between highvoltage devices was shown [4]. However, the substrate network was extracted manually that would be tedious for large circuit analyses and the injected current levels in the substrate were considerably low.

The enhanced models were modified in [5] to simulate high levels of injected currents. The capacitive components in the PN junction was modeled in [6]. These components are essential in transient simulations. In order to emulate the large difference in doping concentrations, a model, which is referred to as homojunction model, was developed. The doping concentration discontinuity affects the minority carriers propagation [7]. Therefore, the substrate can be modeled using three enhanced components which are the enhanced diode, enhanced resistor, and enhanced homojunction models that are simulated in SPICE environment.

The main objective of this paper is to propose analysis and verification methodology for substrate noise coupling effects in HV applications. It can be used to analyze failures that occur due to minority carriers coupling. Since this

methodology is able to detect the failures in simulation environment, it can be used to prevent these failures before fabrication. Hence, it reduces the time-to-market and reduces the product cost. It relies on automatically extracting the substrate parasitic components from the layout. The tool used for the extraction and constructing the equivalent substrate network is called AUTOMICS.

The paper is organized as follows. Section II discusses the AUTOMICS substrate extraction framework. In Section III, the proposed methodology for substrate noise analysis is explained. The substrate coupling in a DC-DC buck converter test case is elaborated in Section IV. DC simulation results for the substrate parasitic currents in DC-DC buck converter circuit are compared to measurements. Section V shows an industrial test case (AUTOCHIP1). Transient simulations are performed to reproduce a failure that occurs due to minority carriers coupling. Finally, the conclusions are drawn in Section VI.

## II. AUTOMICS: PRAGMATIC SUBSTRATE PARASITIC EXTRACTION FRAMEWORK

One of the keys to alleviate failures after fabrication is to model the lateral NPN parasitic transistors. These parasitic components are layout dependent and their parameters cannot be extracted automatically by the current extraction tools. They inherently model the minority carriers propagation in the substrate. The enhanced diodes, resistors, and homojunction models allow modeling these parasitic components [8]. AUTOMICS is a parasitic extraction tool that is capable of modeling the substrate including the minority carriers propagation. This tool uses the enhanced components to construct the substrate equivalent network. It is developed using the "openAccess" open source application programming interface (API). The extraction procedure has two steps:

- A. Geometrical features extraction using AUTOMICS tool,

- B. Technological parameters calibration.

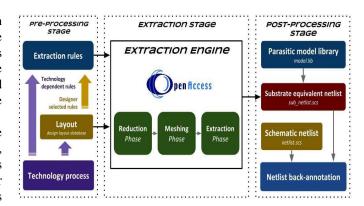

AUTOMICS tool flow starts with the geometrical features extraction of the parasitic components in the layout. The inputs and outputs of the tool are depicted in Figure 1. The main flow of the tool can be divided into three main stages [8], [9]: preprocessing stage, extraction stage, and post-processing stage. The input is the layout of the design. A reduction mechanism is used to filter out the layers that do not contribute in the substrate parasitic coupling such as metal and poly-silicon layers. This reduction is essential to simplify the extracted netlist meanwhile keeping the most relevant information for the parasitic coupling analysis [10]. An adaptive meshing strategy is used to reduce the number of the components [11]. The meshing in the vertical direction can significantly affect the results as shown in [12], [13]. Hence, fine meshing is used along the substrate depth. A netlist describing the extracted parasitic components connections is generated.

The technology parameters calibration is performed using industrial test-benches. Various test structures are fabricated for the  $0.35\,\mu m$  HV-CMOS technology provided by AMS. Then, these test structures are extracted with AUTOMICS tool

Fig. 1. AUTOMICS substrate parasitic extraction flow. [8]

and parameters calibration is performed to fit the simulation results and measurements [14].

### III. PROPOSED SMART POWER ICS VERIFICATION METHODOLOGY

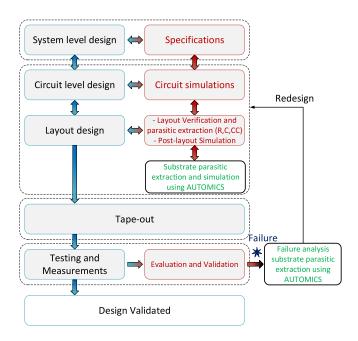

The design flow starts with a set of product specifications as shown in Figure 2. System and circuit level models are built to achieve these specifications. In the layout design, many techniques are used for matching and reducing the coupling between different cells [15]. The layout parasitic components are extracted which are mainly the routing metal layers parasitic resistors, capacitors and the coupling capacitors between different metal layers. The design modifications in these different steps are possible, however, each step down in the flow the modification becomes a burdensome task.

Eventually, the chip is available and ready for further testing and measurements to validate and evaluate its functionality. If the chip manages to pass all these tests then the cycle of the design is done and the product is approved. On the contrary, if the product fails in one critical test then we have to start a failure analysis to identify the root cause of the failure and how to avoid it. The failure analysis depends on measurements and hand-analysis to locate the root cause. The designer experience plays a major role in this step. After identifying the problem, the redesign cycle starts. Such failures would prolong the design cycle and increase the time-to-market and certainly increase the cost. In practice, this redesign cycle could be repeated several times for one product.

Failures due to the substrate coupling are principally caused by the activation of the lateral parasitic NPN bipolar junction transistor. The conventional state-of-art modeling technique is based on TCAD simulations [2], [16]. In addition to the TCAD simulations, fabricated test-benches are used to characterize the lateral NPN transistor and set guidelines for the designer to reduce the substrate coupling noise.

The basic concept of the proposed methodology depends on the ability to simulate the failures due to substrate coupling as shown in Figure 2. If we successfully reproduce the failures then we are able to prevent such failures before the fabrication. Consequently, the number of redesigns is reduced and hence, the cost and time-to-market are reduced. Besides, all the simulations are done in SPICE-like simulator environment, hence, the simulation time is significantly shorter than TCAD simulations.

The proposed design flow has two additional stages in the design flow which are :

- 1) Failure analysis and reproduction,

- 2) Substrate parasitic extraction step.

Fig. 2. Proposed smart power IC design flow to extract the substrate parasitic components using the AUTOMICS tool in verification and failure analyses steps.

#### A. Failure analysis and reproduction

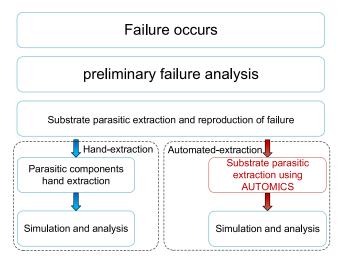

The main objective of this stage is to reproduce a failure occurred in a test-chip on the simulation environment. After the preliminary failure diagnoses, the failure analysis engineer anticipates that the substrate coupling could be the cause of failure. Then, as shown in Figure 3, the conventional substrate failure analysis is based on the substrate parasitic components hand-extraction. Long time may be spent in the parasitic hand extraction.

The proposed step is to replace this hand parasitic extraction with automated parasitic extraction using AUTOMICS. With fast parasitic extraction method, the failure root cause could be identified in short time. This proposed methodology could speed up the failure analysis and add comprehensive explanations based on the substrate noise coupling simulations that can be done. It should be noted that this methodology is based on the preliminary failure analysis decision that the failure is due to the substrate coupling. Hence, it is not a fully automated failure analysis tool.

#### B. Substrate parasitic extraction step

The substrate parasitic components are extracted from the layout using AUTOMICS tool. The designer can select an active area for extraction. This area would contain an aggressor

Fig. 3. Proposed failure analysis due to substrate coupling using AUTOMICS tool.

and a victim. The aggressor is expected to inject minority carriers in the substrate that most probably is a high voltage switch. The victim is a sensitive circuit to this substrate current that can disturb the operation of the whole system such as a bandgap or an oscillator circuits.

The substrate simulations give the designer an estimation for the coupling substrate currents. This information can be used as a guideline to improve isolation techniques i.e, guard rings. The substrate extracted netlist can be back-annotated to the original design and simulated to check the substrate coupling effects on the original circuit. DC analyses can be done to estimate the amount of DC substrate current coupled to different wells on the substrate. In addition to DC analyses, transient simulations show effects due to junction and diffusion capacitances of different wells on the same substrate.

The usage of the proposed methodology as a verification step before fabrication clarifies the substrate noise coupling effects. Hence, it provides quantitative guidelines to take the proper precautions to reduce the substrate coupling. We are going to apply the proposed methodology in DC and transient simulations on two different test cases in the next sections.

## IV. DC SIMULATION TEST CASE: DC-DC BUCK CONVERTER

In this section, we apply the methodology to simulate the substrate coupling current between HV switches and the bandgap circuit. Then, we illustrate the effect of these minority carriers coupling on the bandgap operation. The DC simulation results and measurements are shown.

#### A. DC-DC buck converter circuit operation

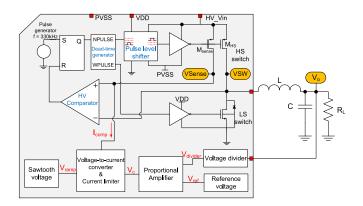

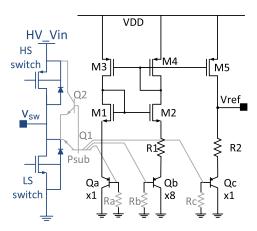

The DC-DC buck converter is used to step-down the input voltage to a well controlled output voltage. A feedback control loop is used to maintain the output voltage constant [17], [18]. Figure 4 shows our chip basic building blocks on the circuit level. The inductor, capacitor, and load resistance are off-chip components. The chip has three input power supplies: the high

voltage supply (HV\_Vin), the low bias voltage for the high side (HS) switch driver (PVSS), the low voltage supply (VDD). The high voltage input (HV\_Vin) ranges from 5 to 15 V while the low voltage bias (VDD) is 5V. Since the gate-source of the used HS switch can not sustain voltages higher than 5V, the HS buffer swing is limited to HV\_Vin and PVSS where  $PVSS = HV_Vin - 5V$ .

Fig. 4. Basic circuit operation of the designed CPM buck converter.

The condition for switching off the HS switch can be expressed as

$$Vsw < VSense \\ HV\_Vin - I_L \times R_{HS} < HV\_Vin - I_{comp} \times R_{sense} \\ I_L > K \times I_{comp}$$

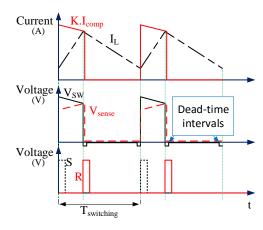

where Vsw and VSense are the switching and the sense nodes voltages,  $I_L$  and  $I_{comp}$  are the inductor and compensated control currents,  $R_{HS}$  and  $R_{sense}$  are the on resistances of high side  $(M_{HS})$  and sense  $(M_{sense})$  transistors, and K is the ratio between the sizes of the HS switch  $(M_{HS})$  and the sense transistor  $(M_{sense})$ . Thus, the HS switch is turned off once the inductor current crosses the scaled compensated current as shown in Figure 5. The factor (K) allows using low compensated control current  $(I_{comp})$ , hence, reduces the power consumption.

The dead-time intervals are inserted to prevent the shoot-through currents in the HS and LS switches. During the dead-time interval, the HS and LS switches are turned off. The current in the inductor does not change instantaneously, hence, the convenient current path is through the body diode of the LS switch. Consequently, the switching node (Vsw) voltage is pulled below ground as shown in Figure 5. This below ground state injects minority carriers in the substrate. The load current of this chip ranges from 0.1 to 0.6 A.

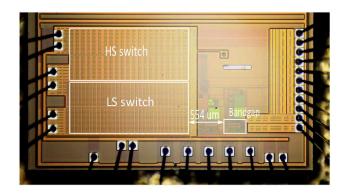

The chip was fabricated using  $0.35\,\mu\mathrm{m}$  HV-CMOS technology. The die photo of the chip is shown in Figure 6. The HS and LS switches are placed in the corner of the die to minimize the power dissipation and the substrate coupling current. The bandgap is placed about 554  $\mu m$  apart from the LS switch. The distance is maximized in order to investigate the substrate coupling effects without significant disturbance to the system performance.

Fig. 5. Transient signals of the inductor current  $(I_L)$  and the scaled sense current  $(K.I_{comp})$ , the sense voltage  $(V_{sense})$  and the switching node voltage  $(V_{sw})$  and the set and reset signals.

Fig. 6. DC-DC converter chip die photo.

#### B. Effects of the substrate coupling on the bandgap voltage

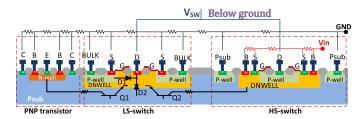

In Figure 7, the bandgap circuit is shown with the output stage, i.e. the LS and HS transistors. Q1 and Q2 are the parasitic NPN transistors. These transistors represent the substrate coupling components under investigation. A cross-sectional area of the output stage and the BJT used in the bandgap is shown in Figure 8.

The minority carriers are going to be collected by the base of the PNP transistors. This electron collection results in reducing the base current [19]. To explore more this effect, we can assume small parasitic resistances at the base terminals, then this electron collection can be translated into a reduction in the base voltage. The effect of lowering the base voltage results in lowering the reference voltage. Consequently, the more the current coupled into the bandgap the less the reference voltage. This is the expected effect from the simulation of the circuit and the substrate extracted netlist.

#### C. Substrate injection current mechanism

The injection of minority carriers occurs at the dead-time period  $(T_d(total))$ . During this period, the below ground state on the switching node  $(V_{sw})$  forces the body diode  $(D_1)$  and

Fig. 7. Bandgap circuit with the output stage. The grey components represent the parasitic components. The resistances  $R_{a,b,c}$  represent the parasitic contact resistances to ground. Q1 and Q2 are the lateral NPN transistors.

Fig. 8. Cross-sectional area for the output stage and the PNP transistor used in the bandgap circuit.

the substrate diode  $(D_2)$  to conduct. Since we are using the isolated NMOS transistor, the major part of substrate current is due to the conduction of the substrate diode  $(D_2)$ .

The injected current is divided into three main components [20]: 1) leakage current in the MOS transistor (LS switch), 2) body diode current, and 3) substrate diode current. The injected minority carriers in the substrate are going either to be coupled in another N-well or recombined in the substrate. The recombination of electrons in the substrate requires a substrate current to compensate the shortage in holes, which means that the substrate voltage is going to be lowered.

In our extraction, we consider only the deep N-wells (DNWELLs) of the PMOS and NMOS transistors and the N-wells of the BJTs in the bandgap as illustrated in Figure 8. The DNWELL of the PMOS is connected to the input high voltage while the DNWELL of the NMOS is pulled down below ground.

To verify the proposed methodology with the DC measurements, we assumed two test cases:

- Test case 1: the LS switch NMOS transistor source terminal is connected to ground. This means that the injected current is divided into the body and substrate diodes.

- Test case 2: the source of the LS switch transistor is disconnected. This means that the injected current is passed only through the substrate diode.

Through these two test cases we kept the PMOS DNWELL

connected to high voltage of 15 V. We are setting a functional threshold voltage for the bandgap voltage of 1.16 V which represents a 3% deviation from the reference voltage. Below this threshold we assume that the reference bandgap is perturbed.

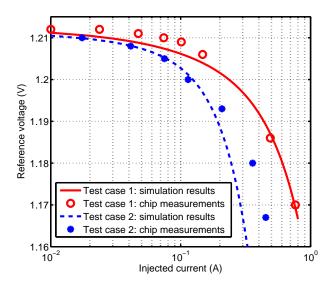

1) Test case 1: the body and substrate diodes are considered: the extracted substrate netlist is back-annotated to the original schematic of the LS and HS switches and the bandgap circuit. The injected current is swept from 0.01 A to 0.8 A. Figure 9 shows the reference bandgap voltage versus the injected current in the simulations and measurements. The simulation results follow the same trend as the measurement points. The reference bandgap voltage did not pass the functional threshold voltage even when the injected current is about 0.8 A.

Most of the injected current passes through the body diode. The remaining part of the injected current flows inside the substrate through the substrate diode. This injected current can be divided into three components. The first component is coupled to the PMOS HS switch DNWELL and results in increasing the power consumption as it drains more current from the supply in normal circuit operation. The second component is recombined in the substrate. The third part which is considerably small is coupled to the bandgap N-wells.

2) Test case 2: the substrate diode is only considered: the substrate diode injects the current in the substrate. This current is divided into recombination substrate current and current collected by N-wells.

Figure 9 shows simulated results and the measurements. For high current values, the simulated data shows greater effect of the injected current on the bandgap rather than the measurements. The main reason of this deviation is that on the chip many other N-wells can serve as a collecting points while in the simulation, we simulate only the injecting point and two other collecting points which are the bandgap and the HS switch DNWELL. In Figure 9, the bandgap failed to sustain its reference voltage when the injected current becomes higher than 300 mA. This injected current lowers the bandgap voltage below the 3% threshold that we assumed. As in this case all the injected current is passed directly to the substrate.

In our design, The average current in the dead-time period can be expressed as

$$I_{av}(deadtime) = \frac{T_d(total)}{T_{switching}} \times I_{av}(load)$$

(1)

where  $T_{switching}$  is the switching period and  $I_{av}(load)$  is the average load current.  $T_d(total)$  is approximately 340 ns and the maximum load current is 0.6 A, hence, the maximum average dead-time current is 67 mA. In the normal operation, the source of the LS switch is connected to ground. Hence, from the test case 1, we can justify that the bandgap reference voltage will not be affected by the current injected in the dead-time.

#### V. Transient simulation industrial case study: Autochip1

The AUTOCHIP1 is a smart power IC developed using  $0.35 \,\mu\text{m}$  HV-CMOS technology from AMS. It has been developed for 24 V Valeo automotive technology applications and is able to sustain overvoltages up to 90 V. It aims at controlling

Fig. 9. Bandgap reference voltage versus the injected current. Test case 1 considers the body and substrate diodes while test case 2 considers only the substrate diode

28 V up to 32 V heavy duty alternators by rotor high current driver up to 5 A. It integrates on the same die a power stage to drive rotor coil, similar to the one described in [21], different I/O interfaces, a power management block and a small digital part that manages a serial communication with an external digital core, implemented on an FPGA. The FPGA solution has been chosen to increase the flexibility, like in [22].

The alternator operation is to recharge the battery during the engine rotation. It comprises two parts: the rotor and the stator. The current in the rotor induces a magnetic flux. Its rotation produces a variable magnetic field that cuts the stator coil. Consequently, the stator generates a current that is used to charge the battery. The control of the stator current is performed by controlling the rotor current.

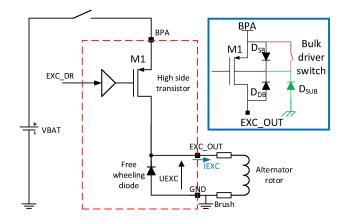

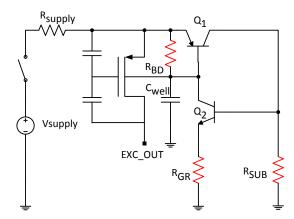

As depicted in the Figure 10, it includes a high-side switch and a low-side freewheeling diode. This stage regulates the current of the rotor. The regulation loop is done by monitoring the BPA voltage defining the Pulse width modulator (PWM) signal duty cycle by comparison with a reference voltage. In order to tolerate the reverse bias voltage conditions on the battery side, a bulk driver circuit is used to avoid the parasitic diode conduction under the reverse bias condition [22]. As shown in Figure 10, in normal operation the voltage of PMOS source node (BPA) is higher than the drain node voltage, hence, the bulk driver switch is turned on connecting the bulk and the source of the PMOS switch. In the reverse bias condition, when the PMOS source node is pulled below ground, in order to prevent the parasitic diode  $D_{DB}$  from conducting, the bulk driver switch is turned off and the floating well reverse voltage protection is formed [23].

One important test is the electrical connection and disconnection of the product that has high dV/dt up to 20V/ns that can be intermittent or during maintenance. AUTOCHIP1 failed to pass the fast connection test, we are going to elaborate the failure root cause in the coming section.

Fig. 10. AUTOCHIP1 power stage principle. In the frame, the high side switch with reverse protection scheme.

Fig. 11. AUTOCHIP1 damage after battery connection. [14]

#### A. Conventional problem identification

The complete evaluation of the AUTOCHIP1 performances has been done in AMS and Valeo laboratories in parallel. Many fast battery connections at different temperatures and different voltages have been done. AUTOCHIP1 failed to sustain a fast connection of 50 V battery and it was severely damaged. Figure 11 shows the microphotograph of the AUTOCHIP1 after the test. The damage is in the battery connection (BPA) pad and its bonding wire.

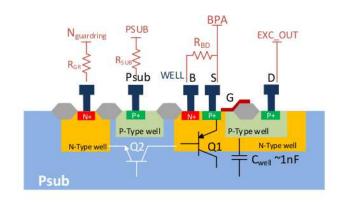

This damage is due to excessive current drawn from the battery during the fast battery connection test. The preliminary failure analysis starts with preparing another testbench using the same design but adding a limiting resistor in series with the battery. The *Em*ission *Mi*croscope (EMMI) was used to identify the potential origin of the failure. An emission occurs on one side of the PMOS high side switch which is surrounded by P-substrate contact and N-guard ring biased to ground. Such optical emissions occur due to the recombination of carriers at the base of a BJT. Hence, this preliminary test indicates that there could be an activation of the lateral NPN BJT between the PMOS bulk, substrate, and the guard ring.

The origin of this high current is that during the fast transition of the battery, the bulk driver switch exhibits a high resistance that activates the vertical PNP transistor between the PMOS bulk and source and the P-substrate injecting high current in the substrate. The substrate voltage is shifted up switching on the lateral NPN transistor and a parasitic

semiconductor rectifier (SCR) structure is triggered. The cross-section of the PMOS and the guard ring with the parasitic components are shown in Figure 12. These two BJT parasitic transistors are not included in the model of the PMOS transistor. Consequently, their effects are not revealed in the schematic circuit simulations. Also, the resistance of the bulk driver switch  $R_{\rm BD}$  must be included in the extraction. The switch resistance during fast transition is approximately 45  $\Omega$ . It should be noted that the guard ring is connected to ground and not to the supply in order to avoid injecting minority carriers in case of reverse bias condition.

A new schematic was done involving the substrate parasitic components added by hand and simulated in order to replicate the measurement behavior. Such simulations are needed to increase the confidence level of the redesign and to validate the root cause explanation. This hand-extraction step took more than three months.

Fig. 12. AUTOCHIP1 parasitic components hand extraction.

#### B. Proposed problem identification

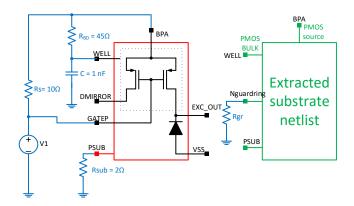

Our proposed methodology can be used to identify such failure. At this stage, the layout of the design is available and can be processed by AUTOMICS tool. The selected area is the PMOS and the guard rings. The main four terminals are the PMOS bulk (WELL), PMOS source (BPA), the N-type guard ring ( $N_{guardring}$ ) and the p-substrate contact (PSUB). These terminals are preserved in the substrate parasitic extraction.

The active substrate thickness is set to  $25~\mu m$  to minimize the number of components with an acceptable accuracy. The substrate is divided into five sub-layers. The sub-layers thicknesses, extraction time and number of layout shapes processed are reported in Table I. The vertical PNP and lateral NPN transistors are extracted in addition to the parasitic substrate resistances. We added resistances to emulate the parasitic metal tracks and vias resistances for the substrate and guard ring connections.

Figure 13 shows the test bench used for simulating the substrate network with the original schematic. The voltage source V1 is set to  $0\,\mathrm{V}$  then ramps up to  $12\,\mathrm{V}$  in  $10\,\mathrm{ns}$ . Two simulations are performed. The first one is simulation of the original circuit only. The second simulation is the original circuit and the extracted substrate network.

TABLE I

AUTOCHIP1 SUBSTRATE EXTRACTION PARAMETERS

| Parameter               | Value              | Parameter             | Value                |

|-------------------------|--------------------|-----------------------|----------------------|

| Active substrate depth  | 25 μm              | Number of sub-layers  | 5                    |

| Layer 1 depth           | 1.55 μm            | Layer 4 depth         | $15\mu\mathrm{m}$    |

| Layer 2 depth           | $3.5\mu\mathrm{m}$ | Layer 5 depth         | $25  \mu \mathrm{m}$ |

| Layer 3 depth           | 6.5 μm             | # of shapes processed | 1900                 |

| Extraction elapsed time | 232.6 s            | Extraction CPU time   | 199.5 s              |

Fig. 13. AUTOCHIP1 simulation testbench.

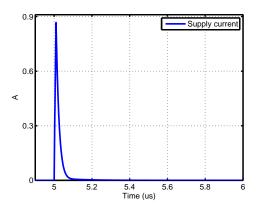

In case of simulating the original circuit alone, a current spike is drawn from the supply connection and then the current returns to zero in fraction of a microsecond as shown in Figure 14. This current spike is due to the parasitic capacitance (Cwell) of the N-well of the PMOS transistor. As the current returns back to zero, this indicates that the circuit works properly. This is expected since the schematic components does not consider the layout aspects like the guard ring connection, as a result the lateral NPN transistor is not modeled.

Fig. 14. Simulation of AUTOCHIP1 schematic without the substrate network. Fast transition current occurs due to parasitic capacitance then returns to zero. This indicates the proper operation of the circuit which is not the actual case.

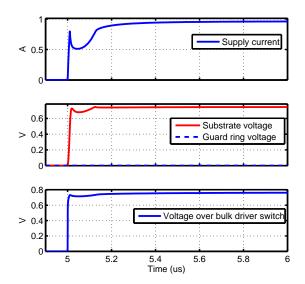

Figure 15 shows the simulation results of the AUTOCHIP1 extracted substrate network. The spike in the supply current appears and does not return to zero. A holding current appears indicating the presence of a latched SCR structure. The substrate voltage across the parasitic resistor is about 0.7 V and

is held constant indicating the lateral NPN is turned on. The results show an acceptable agreement with the measurement on the AUTOCHIP1 reported by AMS. The simulation time and number of extracted components are shown in Table II.

These results could be used by a designer to analyze the latch-up structure and provide solution for this problem before fabrication. This proposed methodology saves the time required for the substrate parasitic extraction. Also, it could be used before the fabrication as a verification test for the design sensitivity to the latch-up structure. Using such tool would save long time of redesign and consequently, lower the cost and ameliorate the circuit design.

Fig. 15. AUTOCHIP1 Substrate network simulation. The substrate voltage is measured at the substrate contact (PSUB). The latchup occurs and a current of 1A is drawn from the supply.

TABLE II Substrate simulation parameters for Transient time = 8  $\mu s$

| Parameter               | Value   | Parameter               | Value |

|-------------------------|---------|-------------------------|-------|

| Number of nodes         | 22511   | Number of diodes        | 2417  |

| Simulation CPU time     | 611.6 s | Number of resistors     | 33795 |

| Simulation elapsed time | 616.1 s | Number of homojunctions | 583   |

#### C. Proposed solutions for latch-up problems

Figure 16 shows a simplified circuit for the extracted parasitic components of the PMOS transistor.

In order not to trigger the SCR structure at the fast connection test, we have to ensure that the lateral BJT does not turn on. Starting with the vertical PNP transistor, the switching on of this transistor depends on passing a large current through the  $R_{BD}$  and the well capacitance. It turns on as the bulk driver circuit response is slow relative to the input voltage slew rate and its resistance  $R_{BD}$  is large. Hence, the first proposed solution is to reduce the resistance of the bulk driver switch at the power up.

Fig. 16. AUTOCHIP1 High side transistor and its parasitic components equivalent circuit. Resistances in red should be modified to prevent latch-up.

The second precaution is to modify the guard ring resistance. Adding a resistance in series with the guard ring requires an excess current through the substrate resistance to switch on the lateral NPN transistor. Thus, if the vertical transistor is turned on, the amount of current passing through the substrate resistance will not be sufficient to turn on the lateral NPN transistor and consequently, the latch-up structure will not be triggered.

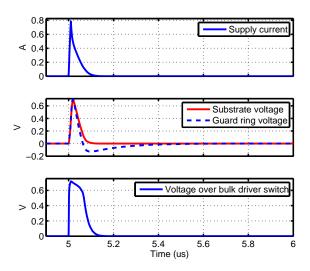

These precautions are done and the bulk driver resistance  $(R_{BD})$  is lowered to 4  $\Omega$  and the guard ring resistance  $(R_{GR})$  is risen to 5  $k\Omega$ . The simulation results of the extracted substrate network with the modified components are shown in Figure 17. The substrate voltage rises due to the injection of holes, however, the voltage across the guard ring resistor is also increased. Hence, the latch-up is prevented.

Fig. 17. Simulation of AUTOCHIP1 Substrate network with latch-up prevention techniques.

Using the proposed latch-up prevention techniques, AUTOCHIP2 was designed and fabricated. It manages to pass the battery connection test safely.

#### VI. CONCLUSION

A methodology for analysis and verification of substrate noise coupling was presented. It is based on substrate parasitic extraction tool referred to as AUTOMICS. The tool employs enhanced models that account for the propagation of minority carriers. The methodology fills the gap due to the absence of the lateral NPN transistor modeling in conventional tools. Hence, it is capable of estimating the coupling current between the HV circuits and the low voltage circuits. This would be helpful in the design to optimize the circuit protection. Also, it is used to simulate the failures due to the activation of this lateral NPN transistors. Simulating the failure means we would be able to prevent it before fabrication. The methodology was verified on DC-DC buck converter circuit and the coupling effect of the HV switch and the bandgap was simulated. The simulation and measurement results were consistent. Then, it was verified on an industrial test case AUTOCHIP1 that failed due to fast transition on its supply contact. This fast transition activated the lateral NPN transistor and triggered a latchup. The simulation results reproduced the failure behavior and were in good agreement with the measurements. Also, failure prevention techniques were verified on simulations. The proposed methodology gives an insight of the substrate noise coupling behavior. Hence, using it in the verification stage before fabrication would reduce the number of redesigns and shorten the time-to-market and consequently, the cost is reduced.

#### ACKNOWLEDGMENT

The authors would like to thank the consortium of European project AUTOMICS for their technical cooperation.

#### REFERENCES

- [1] B. Murari, F. Bertotti, and G. A. Vignola, *Smart power ICs: technologies and applications*. Springer Science & Business Media, 2002, vol. 6.

- [2] M. Schenkel, "Substrate current effects in smart power ICs," Ph.D. dissertation, Diss., Technische Wissenschaften ETH Zürich, Nr. 14925, 2003, 2003.

- [3] F. L. Conte, J.-M. Sallese, M. Pastre, F. Krummenacher, and M. Kayal, "A circuit-level substrate current model for smart-power ICs," *Power Electronics, IEEE Transactions on*, vol. 25, no. 9, pp. 2433–2439, 2010.

- [4] F. Lo Conte, J.-M. Sallese, and M. Kayal, "Circuit level modeling methodology of parasitic substrate current injection from a high-voltage H-bridge at high temperature," *Power Electronics, IEEE Transactions* on, vol. 26, no. 10, pp. 2788–2793, 2011.

- [5] C. Stefanucci, P. Buccella, M. Kayal, and J.-M. Sallese, "Spice-compatible modeling of high injection and propagation of minority carriers in the substrate of Smart Power ICs," *Solid-State Electronics*, vol. 105, pp. 21–29, 2015.

- [6] C. Stefanucci, P. Buccella, M. Kayal, and J. M. Sallese, "Modeling Minority Carriers Related Capacitive Effects for Transient Substrate Currents in Smart Power ICs," *Electron Devices, IEEE Transactions* on, vol. 62, no. 4, pp. 1215–1222, 2015.

- [7] C. Stefanucci, P. Buccella, M. Kayal, and J.-M. Sallese, "Impact of enhanced contact doping on minority carriers diffusion currents," in Microelectronics and Electronics (PRIME), 2014 10th Conference on Ph. D. Research in. IEEE, 2014, pp. 1–4.

- [8] H. Zou, Y. Moursy, R. Iskander, C. Stefanucci, P. Buccella, M. Kayal, and J.-M. Sallese, "Substrate noise modeling with dedicated CAD framework for smart power ICs," in *Circuits and Systems (ISCAS)*, 2015 IEEE International Symposium on. IEEE, 2015, pp. 1554–1557.

- [9] H. Zou, Y. Moursy, R. Iskander, M.-M. Louerat, and J.-P. Chaput, "A novel CAD framework for substrate modeling," in *Microelectronics and Electronics (PRIME)*, 2014 10th Conference on Ph. D. Research in. IEEE, 2014, pp. 1–4.

- [10] P. Buccella, C. Stefanucci, H. Zou, Y. Moursy, R. Iskander, J.-M. Sallese, and M. Kayal, "Methodology for 3-D Substrate Network Extraction for Spice Simulation of Parasitic Currents in Smart Power ICs," Computer-Aided Design of Integrated Circuits and Systems, IEEE Transactions on, 2015.

- [11] H. Zou, Y. Moursy, R. Iskander, and M.-M. Louerat, "An adaptive mesh refinement strategy for substrate modeling," in 2016 IEEE International Symposium on Circuits and Systems (ISCAS). IEEE, 2016, pp. 2358– 2361.

- [12] B. Stanisic, N. Verghese, R. Rutenbar, L. Carley, and D. Allstot, "Addressing substrate coupling in mixed-mode ICs: simulation and power distribution synthesis," *IEEE Journal of Solid-State Circuits*, vol. 29, no. 3, pp. 226–238, mar 1994.

- [13] C. Stefanucci, P. Buccella, M. Kayal, and J. Sallese, "Influence of substrate meshing on the accuracy of EPFL substrate model for smart power ICs," *International Journal of Microelectronics and Computer Science*, vol. 5, no. 2, 2014.

- [14] Y. Moursy, H. Zou, R. Iskander, P. Tisserand, D.-M. Ton, G. Pasetti, E. Seebacher, A. Steinmair, T. Gneiting, and A. Heidrun, "Towards Automatic Diagnosis of Minority Carriers Propagation Problems in HV/HT Automotive Smart Power ICs," in *Design, Automation & Test in Europe Conference & Exhibition (DATE)*. IEEE, 2016, pp. 265–268.

- [15] A. Hastings, The art of analog layout. Prentice Hall, 2006.

- [16] E. Gnani, V. Giudicissi, R. Vissarion, C. Contiero, and M. Rudan, "Automatic 2-D and 3-D simulation of parasitic structures in smart-power integrated circuits," *Computer-Aided Design of Integrated Circuits and Systems, IEEE Transactions on*, vol. 21, no. 7, pp. 791–798, 2002.

- [17] N. Costantino, R. Serventi, F. Tinfena, P. D'Abramo, P. Chassard, P. Tisserand, S. Saponara, and L. Fanucci, "Design and test of an hv-cmos intelligent power switch with integrated protections and self-diagnostic for harsh automotive applications," *IEEE Transactions on Industrial Electronics*, vol. 58, no. 7, pp. 2715–2727, 2011.

- [18] S. Saponara, G. Pasetti, N. Costantino, F. Tinfena, P. DAbramo, and L. Fanucci, "A flexible led driver for automotive lighting applications: Ic design and experimental characterization," *IEEE Transactions on Power Electronics*, vol. 27, no. 3, pp. 1071–1075, 2012.

- [19] V. Tomasevic, A. Boyer, and S. Ben Dhia, "Bandgap failure study due to parasitic bipolar substrate coupling in smart power mixed ics," in Electromagnetic Compatibility of Integrated Circuits (EMC Compo), 2015 10th International Workshop on the. IEEE, 2015, pp. 34–38.

- [20] P. Buccella, C. Stefanucci, J.-M. Sallese, and M. Kayal, "Simulation, analysis and verification of substrate currents for layout optimization of smart power ics," *IEEE Transactions on Power Electronics*.

- [21] S. Saponara, G. Pasetti, F. Tinfena, L. Fanucci, and P. D'Abramo, "HV-CMOS Design and Characterization of a Smart Rotor Coil Driver for Automotive Alternators," *Industrial Electronics, IEEE Transactions on*, vol. 60, no. 6, pp. 2309–2317, 2013.

- [22] L. Fanucci, G. Pasetti, P. D'Abramo, R. Serventi, F. Tinfena, P. Chassard, L. Labiste, and P. Tisserand, "An high voltage CMOS voltage regulator for automotive alternators with programmable functionalities and full reverse polarity capability," in *Design, Automation & Test in Europe* Conference & Exhibition (DATE), 2010. IEEE, 2010, pp. 526–531.

- [23] H.-P. Hong and J.-C. Wu, "A reverse-voltage protection circuit for MOS-FET power switches," *Solid-State Circuits, IEEE Journal of*, vol. 36, no. 1, pp. 152–155, 2001.

Yasser Moursy received his B.Sc. degree in electronics and communications from Alexandria University, Egypt in 2008. He obtained his M.Sc. degree in electronics from Alexandria University in 2011. From 2008 to 2012, he worked as a teaching assistant in Alexandria University. From 2012 to 2016, he was a Ph.D. student at Pierre and Marie Curie University, France, studying the substrate noise coupling in Smart power ICs for automotive applications. His research interests include analog design, integrated power converters and power management.

Hao Zou received the M.Sc. degree in electronics and information systems in 2013 from the Université Pierre et Marie Curie Paris 6 (France). Since 2013, he is pursuing his Ph.D. degree at the Laboratoire d'Informatique de Paris 6 (LIP6) at the same university. His research interests are substrate parasitic modeling for Smart Power ICs and Electronic Design Automation developments.

**Dieu-My Ton** received her B.Sc. degree in Electronics from Ecole Française d'Electronique et d'Informatique (EFREI) in 2006. She joined Valeo in 2011. Currently, she is a Marketing and Application Engineer responsible for managing the collaborative projects from European Commission in microelectronics field for alternator regulators and mild-hybrid machines.

Raouf Khalil received his B.Sc degree in Electrical Engineering (Electronics and Communications Department) from Ain Shams University, Cairo, Egypt in 2008. He received his M.Sc. and his Ph.D. degrees from Pierre and Marie Curie University, Paris, France in 2009 and 2013, respectively. In 2015, he joined Intento Design as an Analog Mixed Signal IC Designer. His research interests include ADCs, DACs, DC/DC Converters, sensor circuit interface and design migration.

Giuseppe Pasetti received the M.Sc. and Ph.D. degrees in electronic engineering from University of Pisa, Pisa, Italy. Currently, he is with AMS AG, Navacchio, Italy, as an Analog Design Engineer.

Ramy Iskander received the M.Sc. degree in 2004 and the Ph.D. degree in 2008, from the Laboratoire d'Informatique de Paris 6 (LIP6) at Université Pierre et Marie Curie (UPMC), Paris, France. Before, he worked for more than 10 years in international EDA companies. He is an Associate Professor within the Laboratoire LIP6 at UPMC. He published more than 80 papers on analog design automation methods for nanometer technology covering modeling, simulation, synthesis, layout generation and technology migration. He served as a reviewer for French Na-

tional ANR projects and for several book reviews, international conferences and international journal papers. He is the scientific coordinator of the European FP7/ICT/Green Car project called AUTOMICS covering modeling and simulation of substrate coupling effects for automotive applications. In 2015, Dr. ISKANDER founded the startup Intento Design, bringing to the EDA market a disruptive technology for very fast analog IP design and migration. Today, Dr. ISKANDER serves as the CEO and President of Intento Design.

Marie-Minerve Louërat received her Master degree in Electrical Engineering in 1983 and her PhD in 1986 from Université Paris Sud, Paris XI-Orsay, France. In 1986 she joined the Centre National de la Recherche Scientifique (CNRS), France. She started at Fluids, Automation and Thermal Systems laboratory (FAST) at Université Paris Sud-CNRS, while teaching electronics. In 1992, she moved to the Computer Science Laboratory (LIP6) at University Pierre et Marie Curie-CNRS, France, while teaching VLSI. Marie-Minerve Louërat's research interest is

electronic design automation method and tools for analogue and mixed-signal circuit and systems. Most of her research activities have been supported by contracts, through academic and industrial cooperative projects in the framework of the FP7 and Eureka/MEDEA and Catrene projects. She published papers on static timing analysis, analogue and AMS design automation, analog-to-digital converters, AMS system modeling and simulation. In 1998, she co-founded the Avertec Company, a spin-off from UPMC specialized in static timing analysis. She is a member of the AMS Working Group of Accellera Systems Initiative who has standardized the AMS extension of SystemC in 2010. She has served on the Technical Program Committee of Design, Automation, and Test in Europe Conference (DATE) and several others international conferences.

Since 2013, she is the head of the System on Chip Department at LIP6.

Pierre Tisserand studied electrical engineering in 1981 and received the Ph.D. degree in instrumentation and microelectronic from the Henri Poincaré University, Nancy, France, in 1998. He has been the ASIC and Mechatronic Advanced Projects Manager with the Valeo Engine and Electrical Systems, Créteil, France, since 2003. He coauthored several papers and 30 patents.