# Modélisation et intégration de convertisseurs DC-DC à capacité commutée et à résonance

Florian Chevalier, Gaël Pillonnet

# ▶ To cite this version:

Florian Chevalier, Gaël Pillonnet. Modélisation et intégration de convertisseurs DC-DC à capacité commutée et à résonance. Symposium de Génie Electrique (SGE 2016), Jun 2016, Grenoble, France. hal-01348479

HAL Id: hal-01348479

https://hal.science/hal-01348479

Submitted on 24 Jul 2016

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Modélisation et intégration de convertisseurs DC-DC à capacité commutée et à résonance

Florian Chevalier, Gaël Pillonnet

Université Grenoble-Alpes – CEA-LETI – 17 rue des Martyrs – 38 054 Grenoble CEDEX 9

RÉSUMÉ – L'émergence de systèmes sur puce intégrant de multiples fonctions pour les applications embarquées a fait apparaître un besoin d'alimentations DC-DC distribuées. Dans ce cadre, les convertisseurs à capacité commutée se sont imposés comme une solution permettant d'enfouir les alimentations au plus près des fonctions. Cependant, elles restent intrinsèquement limitées en rendement, et une amélioration peut-être obtenue si la capacité entre en résonance avec une inductance, mais il faut s'assurer que le système est toujours intégrable d'un point de vue technologique. La modélisation proposée dans ce papier, validée expérimentalement, va permettre de comparer l'architecture résonante à celle à capacité commutée en prenant en compte leurs paramètres caractéristiques. Ainsi, le modèle aidera à l'optimisation des composants passifs et du design des MOSFET, permettant d'avancer vers une solution pour l'intégration du convertisseur résonant sur un procédé CMOS.

Mots-clés – Alimentation à découpage, PowerSoC, capacité commutée, convertisseur résonant, inductance intégrée.

#### 1. INTRODUCTION

La tendance actuelle dans l'industrie est à l'enfouissement sur une même puce de fonctions aussi hétérogènes que des processeurs multicœurs, des mémoires ou des interfaces analogiques et communicantes. Chacune a besoin d'une alimentation dédiée stable, efficace et compacte. Une alimentation centralisée ne peut pas répondre à ces contraintes. La distribution d'énergie doit être repensée pour fournir une gestion rapide, flexible, efficace et bien intégrée aux systèmes sur puce complexes.

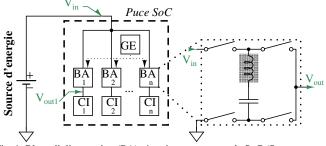

Pour répondre à cet enjeu, une solution est de dédier un bloc d'alimentation à chaque fonction intégrée [1], comme présenté en figure 1. Cette stratégie repose sur une division en petits blocs d'alimentation distribués et dont la réalisation est compatible avec la technologie du système, par exemple CMOS. Ainsi, les multiples condensateurs et inductances nécessaires à ces blocs devront être également intégrés en CMOS afin d'éviter de solliciter des E/S pour connecter des composants extérieurs [2].

Fig. 1. Blocs d'alimentation (BA) répartis sur une puce de SoC (System on Chip), contrôlés par un module de gestion d'énergie (GE) pour alimenter des fonctions intégrées (CI)

La topologie à capacité commutée SCC (pour *Switched Capacitor Converter*) offre des possibilités d'intégration très dense. Elle a ainsi été largement étudiée pour l'intégration de blocs d'alimentation [4]. Bien qu'une densité de puissance de l'ordre

de 1 W/mm<sup>2</sup> ait été atteinte [4], le rendement de cette topologie est limité par des pertes intrinsèques [1]. En effet, la charge et de la décharge de la capacité *via* la résistance à l'état passant des transistors crée par nature des pertes, liées à la fréquence de commutation, à la valeur de la capacité et de la résistance à l'état passant [5]. De plus, la modulation du rapport de conversion est également à l'origine de pertes [6].

Pour dépasser cette limitation du rendement, il a été proposé d'associer à la capacité une inductance dans la boucle de charge et décharge, placée comme sur la figure 1 [7]. Cette structure est appelée à résonance (ReSC pour *Resonant Switching Converter*): le processus permet le transfert sans perte d'énergie à la capacité. L'avantage de cette structure est l'utilisation d'une inductance plus petite que celle d'un convertisseur inductif traditionnel (par exemple un *buck*), permettant une intégration potentielle à l'aide d'options dans le procédés standards [8, 9]. Une densité de puissance de 1 W/mm² a été atteinte par un ReSC en utilisant les inductances parasites du PCB [10]. Cependant ces résultats ne permettent pas de savoir si la performance vient de la technologie ou de la topologie elle-même.

À l'échelle des systèmes sur puce, il est donc nécessaire de comparer le SCC conventionnel avec les avancées envisageables grâce au ReSC. en effet, dans un objectif de conception de système, un modèle permettrait de comparer les performances et les pertes et de trouver un compromis dans le design des deux architectures. Les limites fondamentales des SCC et ReSC ont déjà été montrées [11, 12], mais ne vont pas jusqu'à la comparaison complète des deux convertisseurs dans le même contexte.

Ce papier a pour but de fournir un modèle unifié des deux topologies SCC et ReSC. La section 2 détails les mécanismes de pertes et la modélisation analytique des convertisseurs dans une configuration simple. Ces modèles seront validés en pratique dans la section 3. Les limitations et les éléments clés permettant une intégration seront alors discutés.

# 2. MODÉLISATION DES CONVERTISSEURS

### 2.1. Considérations générales

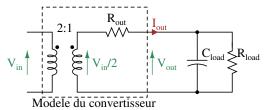

L'analyse décrite ici fournit des expressions analytiques pour une résistance de sortie  $R_{\rm out}$  pour les topologies SCC et ReSC. Ces expressions reposent sur la simplification du convertisseur par le circuit équivalent de la figure 2. En effet, il a été établi, pour de nombreuses configuration, que le rendement est directement lié à cette résistance  $R_{\rm out}$  [13]. Celle-ci représente toutes les résistances du chemin parcouru par le courant entre l'entrée et la sortie, et est ainsi une image des pertes en conduction. Les pertes par commutation ne rentrent pas dans le cadre de cette étude. Pour plus de clarté, nous ne considérerons que la configuration 2:1, où la tension de sortie à vide est la moitié de la tension d'entrée. On supposera également la capacité de sortie suffisamment grande pour que  $V_{\rm out}$  soit constant [14].

# 2.2. Modélisation du SCC

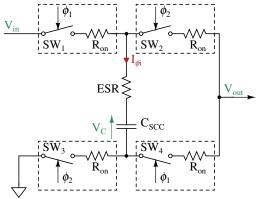

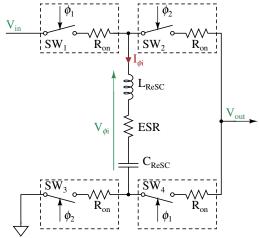

Le convertisseur à capacité commutée SCC est composé d'une capacité volante et d'une matrice de transistors fonction-

Fig. 2. Modèle équivalent du convertisseur en configuration 2 :1 pour l'étude des pertes en conduction ; la capacité de sortie est suffisamment grande pour

nant en interrupteurs, dont la commande permet d'obtenir un rapport de conversion N :M. La figure 3 présente le cas particulier d'une topologie 2 :1. La conversion s'effectue en deux phases  $\Phi_{1,2}$  pour transférer l'énergie de l'entrée  $V_{\rm in}$  à la sortie  $V_{\rm out}$  via la capacité  $C_{\rm SCC}$ . Lors de la première phase  $\Phi_1$ , les interrupteurs  $SW_1$  et  $SW_4$  sont fermés et la capacité  $C_{\rm SCC}$  est connectée entre l'entrée et la sortie et se charge pendant une durée  $T_{\Phi 1}$ . Pour la seconde phase  $\Phi_2$ , l'énergie stockée dans  $C_{\rm SCC}$ est transférée à la sortie par SW $_2$  et SW $_3$  pendant  $T_{\Phi 2}$ . En configuration 2:1,  $T_{\Phi 1}=T_{\Phi 2}=T/2$  avec T la période de commutation. On supposera identique la résistance à l'état passant des quatre interrupteurs.

Fig. 3. Schéma de principe du convertisseur à capacité commutée SCC avec une résistance ESR représentant toutes les pertes dans les ESR de la capacité, des connexions et des interrupteurs

Comme développé dans d'autres travaux de la littérature [15, 16], la résolution classique de l'équation différentielle d'un circuit RC donne le courant  $i_{\Phi i}$  pendant la phase  $\Phi_i$ :

$$i_{\Phi i}(t) = \frac{\Delta V_{\Phi i}}{R} e^{-t/\tau} \tag{1}$$

avec  $au=RC_{\rm SCC}$  la constante de temps,  $\Delta V_{\Phi 1}=V_{\rm in}-V_{\rm out}-V_{C}(0)$  la tension au début de la phase  $\Phi_1, \Delta V_{\Phi 2}=V_{\rm out}-V_{C}(0)$  la tension au début de la phase  $\Phi_2, R=2R_{\rm on}+R_{ESR}$  la résistance équivalente du chemin de charge et de décharge, et t=0au début de chaque phase.

L'énergie dissipée dans la résistance équivalente R à chaque phase est donnée par :

$$E_{R,\Phi i} = \int_{t-0}^{T_{\Phi i}} V_R i_{\Phi i} dt = \frac{1}{2} C_{\text{SCC}} \Delta V_{\Phi i}^2 \left( 1 - e^{2\beta} \right)$$

(2)

avec

$$T_{\Phi i} = T/2$$

et  $\beta = \frac{T}{4RC_{SCC}}$ .

Les charges  $Q_{\Phi i}$  en mouvement dans la capacité volante sont calculées à partir de :

$$Q_{\Phi i} = \int_{T=0}^{T_{\Phi i}} i_{\Phi i}(t)dt = C_{\text{SCC}} \Delta V_{\Phi i} \left(1 - e^{-\frac{T}{2\tau}}\right)$$

(3)

En combinant les équations (2) et (3), on déduit la tension initiale aux bornes de la résistance équivalente R:

$$\Delta V_{\Phi i} = \frac{\overline{i_{\Phi i}}}{C_{\text{SCC}} F\left(1 - e^{-\frac{T}{2\tau}}\right)} \tag{4}$$

où  $\overline{i_{\Phi i}}$  est le courant moyen au cours d'une période et vaut  $Q_{\Phi i}T$ , et avec F la fréquence de commutation. En régime établi et en configuration 2 :1, les charges reçues  $Q_{\Phi 1}$  et fournies  $Q_{\Phi 2}$  par la capacité sont égales. Ainsi,  $\overline{i_{\Phi 1}} = \overline{i_{\Phi 2}} = \overline{i_R}$ . L'énergie totale dissipée dans R au cours d'une période est donnée par :

$$E_R = E_{R,\Phi 1} + E_{R,\Phi 2} = \frac{1}{C_{\text{SCC}}F^2} \frac{1 + e^{-\beta}}{1 - e^{-\beta}} \overline{i_R}^2$$

(5)

L'énergie dissipée dans R est :

$$P_R = \frac{E_R}{T} = \frac{1}{C_{\text{SCC}}F} \coth\left(\frac{\beta}{2}\right) \overline{i_R}^2 \tag{6}$$

Le courant de sortie moyen  $\overline{i_{out}}$  est égal à :

$$\overline{i_{out}} = \frac{Q_{\Phi 1} + Q_{\Phi 2}}{T} = 2\overline{i_R} \tag{7}$$

En combinant (6) et (7), la résistance de sortie équivalente  $R_{\text{out}}$  du modèle de Thévenin présenté en figure 2 s'exprime par :

$$R_{\text{out,SCC}} = \frac{P_R}{i_{\text{out}}^2} = \frac{\beta}{2} \coth\left(\frac{\beta}{2}\right) R$$

(8)

Ce résultat est valable dans les régions FSL et SSL (respectivement Fast Switching Limit, haute fréquence, et Slow Switching Limit, basse fréquence) [5]. En effet, en haute fréquence (donc pour de faibles valeurs de  $\beta$ ), les pertes sont majoritairement dues à la conduction, alors qu'en basse fréquence et pour  $\beta$  élevé, les pertes par transfert de charges sont prédominantes. Or dans ce modèle, le  $R_{\rm on}$  des MOSFET, la capacité  $C_{\rm SCC}$  et la période de commutation T sont explicités, l'influence de ces paramètres peut être déterminée individuellement.

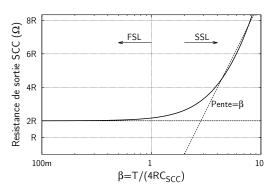

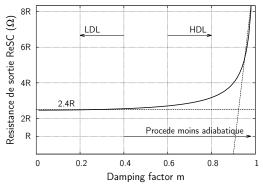

La figure 4 montre l'évolution de la résistance de sortie en fonction de  $\beta$ . L'équation (8) admet une asymptote horizontale à 2R (zone FSL), où  $\beta < 1/5$ , d'après l'équation :

$$\lim_{\beta \to 0} \beta \coth\left(\frac{\beta}{2}\right) R = R \approx 2R_{\text{on}} \tag{9}$$

D'un autre côté, pour  $\beta > 5$ , la résistance équivalente vaut approximativement  $R\beta$ : il s'agit de la zone SSL.

Fig. 4. Tendance de la résistance de sortie en fonction de  $\beta$

# 2.3. Modélisation du convertisseur résonant ReSC

Comme il a été démontré dans la littérature [4] et dans l'équation (8), l'architecture SCC est intrinsèquement limitée, principalement à cause du transfert de charges lorsque le produit  $C_{\rm SCC}F$  est faible (zone SSL). Associer une inductance en série avec la capacité, comme sur la figure 5, modifie le mécanisme de transfert d'énergie pour une charge adiabatique. En commutant à une période égale à la moitié de la période de résonance du circuit LC, une commutation douce est possible par le retour à zéro de la tension ou du courant. Les pertes par commutation sont alors fortement diminuées. Le rendement de la charge et décharge du condensateur dépend alors du coefficient de qualité du réseau RLC.

Fig. 5. Schéma du convertisseur résonant autour d'un circuit RLC dans une configuration 2 :1

Le modèle proposé ici est valide lorsque les quatre MOSFET commutent à la moitié de la fréquence de résonance du circuit RLC, afin de maintenir une commutation douce. Ainsi, la période de commutation  $T_{\varPhi i}$  est lié au facteur m du circuit RLC par :

$$T_{\Phi i} = \pi \sqrt{\frac{L_{\text{ReSC}} C_{\text{ReSC}}}{1 - m^2}}$$

with  $m = \frac{R}{2} \sqrt{\frac{C_{\text{ReSC}}}{L_{\text{ReSC}}}}$  (10)

où  $R=2R_{\rm on}+ESR$  est la résistance équivalente de tout le chemin résistif (résistance à l'état passant des MOSFET, ESR du condensateur et de l'inductance).

La suite du développement suit la même méthode que celle appliquée au SCC ci-dessus. Elle reste valide pour un coefficient d'amortissement m<1.

De manière analogue à ce qui a été fait précédemment, en résolvant le circuit RLC du second ordre formé par le réseau LC et les résistances à l'état passant des MOSFET, on obtient le courant  $i_{\varPhi i}$  lorsque m < 1:

$$i_{\Phi i}(t) = C_{\text{ReSC}} \Delta V_{\Phi i} e^{-m\omega_0 t} \left( \frac{m^2 \omega_0^2}{\omega} + \omega \right) \sin \omega t$$

(11)

avec  $\Delta V_{\varPhi i} = V_{in} - Vout - V_{\varPhi i}(0)$  la valeur initiale de la tension aux bornes de la résistance équivalent R,  $\omega_0$  la fréquence propre du réseau LC,  $\omega$  sa fréquence de résonance telle que  $\omega = \omega_0 \sqrt{1-m^2} = 1/T_{\varPhi i}$

Ainsi, l'énergie dissipée dans les éléments résistifs (c'est-à-dire  $R_{\rm on}$  et ESR) peut être déduite pendant une demi-période :

$$E_{\Phi i} = \int_{0}^{T_{\Phi i}} Ri_{\Phi i}^{2} dt = \frac{C_{\text{ReSC}} \Delta V_{\Phi i}}{2} \left[ 1 - \exp\left(-\frac{2\pi m}{\sqrt{1 - m^{2}}}\right) \right]$$

(12)

La charge transférée dans le réseau LC à chaque phase est calculée par :

$$Q_{\Phi i} = \int_0^{T_{\Phi i}} i_{\Phi i} dt = C_{\text{ReSC}} \Delta V_{\Phi i} \left[ 1 + \exp\left(-\frac{2\pi m}{\sqrt{1 - m^2}}\right) \right]$$

(13)

Sachant que  $\overline{i_{\varPhi i}}=Q_{\varPhi i}/T_{\varPhi i}$ , on trouve la tension aux bornes de R en combinant les équations (12) et (13) :

$$\Delta V_{\Phi i} = \frac{\overline{i_{\Phi i}}}{C_{\text{ReSC}} F \left(1 - e^{-m\omega_0 T/2}\right)}$$

(14)

où F est la fréquence de commutation définie par :

$$F = \frac{1}{T_{\Phi 1} + T_{\Phi 2}} = 2\pi \sqrt{\frac{L_{\text{ReSC}} C_{\text{ReSC}}}{1 - m^2}}$$

En régime établi et en configuration 2 :1, les charges <u>reç</u>ues  $Q_{\underline{\Phi}1}$  et fournies  $Q_{\underline{\Phi}2}$  par le réseau LC sont égales, soit  $\overline{i_{\underline{\Phi}1}}=\overline{i_{\underline{\Phi}2}}=\overline{i_R}$ . L'énergie totale dissipée dans R au cours des deux phases est  $E_R=E_{\underline{\Phi}1}+E_{\underline{\Phi}2}$ , c'est-à-dire :

$$E_R = \frac{\overline{i_R}^2}{C_{\text{ReSC}} F^2} \frac{1 - \exp\left(-\frac{\pi m}{\sqrt{1 - m^2}}\right)}{1 + \exp\left(-\frac{\pi m}{\sqrt{1 - m^2}}\right)}$$

(15)

L'énergie totale dissipée dans les éléments résistifs vaut :

$$P_R = \frac{E_R}{T} = \frac{\overline{i_R}^2}{C_{\text{ReSC}}F^2} \tanh\left(\frac{\pi m}{2\sqrt{1-m^2}}\right)$$

(16)

De manière analogue à ce qui a été exposé dans l'équation (8), la résistance de sortie équivalente s'exprime par :

$$R_{\text{out,ReSC}} = \frac{P_R}{\overline{i_R}^2} = \frac{1}{4C_{\text{ReSC}}F} \tanh\left(\frac{\pi m}{2\sqrt{1 - m^2}}\right)$$

(17)

Pour un coefficient d'amortissement m inférieur à l'unité, la résistance de sortie peut être reliée uniquement à la résistance à l'état passant et à m:

$$R_{\rm out,ReSC} = \frac{\pi}{4m\sqrt{1-m^2}}\tanh\left(\frac{\pi m}{2\sqrt{1-m^2}}\right)R \quad (18)$$

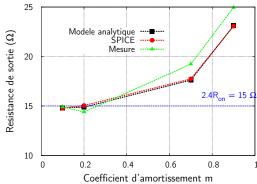

Le comportement de  $R_{\text{out,ReSC}}$  en fonction de m est représenté en figure 6, et est asymptotiquement limité à :

$$\lim_{m \to 0} \frac{\pi}{4} \frac{\tanh\left(\frac{\pi m}{2\sqrt{1 - m^2}}\right)}{m\sqrt{1 - m^2}} R = 1.2R \approx 2.4R_{\text{on}}$$

(19)

Lorsque m<0,5, la résistance de sortie reste proche de sa limite basse à 2,4R (ce point sera discuté ci-dessous), dans la zone LDL (pour Lower Damping Limit). Dans ce mode de fonctionnement, la capacité et l'inductance s'échangent leur énergie dans un régime quasi-harmonique, à une fréquence fixée par les éléments LC directement. Le changement de phase permet un transfert adiabatique de charge à la capacité à travers l'inductance ( $\omega\approx\omega_0$ ). Le courant s'annule périodiquement permettant une commutation douce : les pertes par commutation sont réduites (ce point ne sera développé dans ce papier).

Lorsque  $m \to 1$ , la charge et la décharge du condensateur sont de moins en moins adiabatiques. Il y a donc de plus en plus de pertes en conduction, le régime harmonique étant de plus en plus amorti. Dans ce cas, le ReSC est équivalent au SCC, du fait que l'inductance n'agit plus comme une source intermédiaire de courant entre l'entrée, la sortie et la capacité.

Fig. 6. Évolution de la résistance de sortie du ReSC en fonction du coefficient d'amortissement  $\boldsymbol{m}$

# 2.4. Comparaison des impédances

Les équation (8) et (18) donnent les relations entre les résistances équivalentes de sortie des convertisseurs et les éléments de conception  $R,\,F,\,C_{\rm SCC},\,C_{\rm ReSC}$  et  $L_{\rm ReSC}$ , et peuvent se présenter sous la forme :

$$R_{\text{out,SCC}} = k_{\text{SCC}}R \qquad k_{\text{SCC}} = \beta \coth \frac{\beta}{2}$$

(20)

$$R_{\text{out,ReSC}} = k_{\text{ReSC}}R \qquad k_{\text{ReSC}} = \frac{\pi}{4} \frac{\tanh\left(\frac{\pi m}{2\sqrt{1 - m^2}}\right)}{m\sqrt{1 - m^2}} \tag{21}$$

Ces équations montrent une méthode de réduction des pertes par conduction dans les topologies de convertisseur SCC et ReSC. Dans le cas du SCC, réduire les pertes par conduction passe par une augmentation de la fréquence de commutation, qui va entraîner une augmentation des pertes par commutation, ou une augmentation de la valeur de la capacité qui va occuper plus d'espace si l'on raisonne en technologie CMOS, donc diminuer la densité de puissance.

Dans le cas du ReSC, les pertes en conduction dépendent du coefficient d'amortissement m, qu'il faut donc réduire. Ceci revient à diminuer la valeur de la résistance ou augmenter la valeur de l'inductance, comme montré dans l'équation (11). La réduction de la partie résistive se fait par une augmentation de la taille des MOSFET, ce qui va entraîner une augmentation des pertes par commutation. Une autre solution est une augmentation de la valeur de l'inductance, ce qui revient à l'agrandir, donc à diminuer la densité de puissance. Avec l'objectif d'une intégration CMOS, la rapport entre la valeur d'une inductance à air et son ESR est un élément clé.

A priori, d'après les figures 4 et 6, le choix d'un concepteur porterait plutôt sur le SCC, dont la limite basse (2R) en FSL est inférieure à celle du ReSC (2,4R) en LDL. Mais les conditions dans lesquelles ces limites sont atteintes sont complètement différentes dans les deux cas.

En effet, prenons par exemple m=0,1, considérée comme la valeur permettant d'avoir de faibles pertes. Dans ce cas, l'équation (17) donne une valeur de résistance de sortie de 2,47R:

$$m = 0.1 \iff k_{\text{ReSC}} = 2.47$$

(22)

Pour avoir le même coefficient pour le SCC,  $\beta$  doit valider l'équation (8)

$$k_{\text{ReSC}} = k_{\text{SCC}} = 2.47 \iff \beta \coth \frac{\beta}{2} = 2.47 \iff \beta = 1.7$$

Si la fréquence de commutation est la même pour le SCC et le ReSC (pour avoir les mêmes pertes en commutation), la capacité du SCC  $C_{\rm SCC}$  peut être calculée en fonction de la capacité du

ReSC  $C_{ReSC}$  par :

$$C_{\text{SCC}} = \frac{T}{4\beta R} = \frac{\pi \sqrt{L_{\text{ReSC}} C_{\text{SCC}}}}{4\beta R} = \frac{\pi}{2\beta m \sqrt{1 - m^2}} C_{\text{ReSC}}$$

(24)

Si m=0,1 et  $\beta=1,7$  dans (24), alors  $C_{\rm SCC}=10C_{\rm ReSC}$  pour la même résistance de sortie. En contrepartie, le ReSC a besoin d'une inductance dont la valeur est égale à :

$$L_{\text{ReSC}} = \frac{R\sqrt{1 - m^2}}{2Fm} = \frac{4R^2}{m^2} C_{\text{ReSC}}$$

(25)

Le tableau 1 résume les rapports entre les valeurs de capacités du SCC et du ReSC pour différents coefficients d'amortissement. Diminuer m implique une valeur d'inductance plus grande, mais aussi une valeur de capacité plus faible, à fréquence de commutation constante. Ainsi, un compromis devra être trouvé sachant la technologie de fabrication visée. Si cette technologie permet une la fabrication d'une inductance de valeur élevée et à faible ESR, alors la topologie ReSC offrira un meilleur rendement et une meilleure intégration que la topologie SCC.

Tableau 1. Ratio between SCC and ReSC capacitance and evolution of the inductance for a constant switching frequency

|                |                                  | 0 1                                              |  |

|----------------|----------------------------------|--------------------------------------------------|--|

| $\overline{m}$ | $\frac{C_{ m SCC}}{C_{ m ReSC}}$ | $\frac{L_{\text{ReSC}}}{L_{\text{ReSC}(m=0.1)}}$ |  |

| 0.1            | 9.3                              | 1                                                |  |

| 0.3            | 3.0                              | 0.1                                              |  |

| 0.5            | 1.8                              | 0.04                                             |  |

| 0.7            | 1.3                              | 0.02                                             |  |

| 0.9            | 1.04                             | 0.01                                             |  |

# 3. VALIDATION EXPÉRIMENTALE

# 3.1. Banc de test

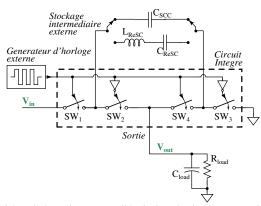

La validation expérimentale du modèle développé dans la section précédente s'est faite à l'aide d'un circuit commercial [17]. Ce circuit a été conçu pour fonctionner en tant que SCC, sans régulation de la tension de sortie. Le fabricant fournit un modèle SPICE « clé en main » (blackbox), qui permettra de déterminer le dimensionnement et les performances avant la phase de tests. L'alimentation doit être comprise entre 1,5 et 6,5 V; une tension d'entrée de 5 V a été choisie afin d'avoir une tension de sortie à vide de 2,5 V (en configuration 2:1). La résistance à l'état passant de chaque interrupteur a été mesurée à 6  $\Omega$ . Les résistances de sortie seront comprises entre  $2R_{\rm on}$  et  $10R_{\rm on}$ . Compte-tenu du courant de sortie que peut délivrer le circuit (10-100 mA), la résistance de charge sera prise dans la gamme  $10\text{-}100\,\Omega$  afin de ne pas masquer la résistance de sortie ou surcharger le circuit. La capacité volante est externe. Il sera ainsi facile de lui associer en série une inductance externe pour obtenir la topologie ReSC. La fréquence de commutation est fournie par une générateur d'horloge externe, et pourra donc être ajustée. Un schéma équivalent du montage et du circuit est proposé en figure 7. La capacité de sortie a été calculée de manière à ce que sa décharge dans  $R_{\rm out}$ soit plus longue que la moitié d'une période de commutation, et a été fixée à 100  $\mu$ F.

Comme représenté sur la figure 2, la mesure de la tension aux bornes de la résistance de charge donne le courant de sortie. La différence entre la valeur théorique  $V_{\rm in}/2$  et la valeur  $V_{\rm out}$  mesurée est la tension aux bornes de la résistance de sortie  $R_{\rm out}$ , permettant directement le calcul des pertes :

$$R_{

m out} = rac{V_{

m in}/2 - V_{

m out}}{V_{

m out}/R_{

m load}}$$

Fig. 7. Schéma du banc de test, avec l'équivalent du circuit commercial dans le cadre pointillé; la capacité de sortie est suffisamment grande pour considérer constante la tension de sortie

La fréquence de commutation du circuit est limitée à 30 kHz, ce qui implique des valeurs de capacité et d'inductances plus grandes que celles pouvant être intégrées. L'objectif de ce banc de test est la validation des équations (8) et (18) ou de travaux précédents [10]. Il sera possible par la suite d'utiliser ces tendances pour une dimensionnement CMOS.

Le modèle ci-dessus ne prenant pas en compte les tempsmorts (mesurés à  $1,7~\mu s$ ), la fréquence de commutation doit les masquer : la fréquence sera donc de l'ordre de quelques kHz.

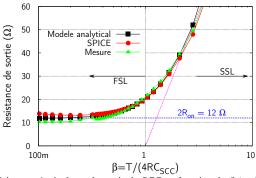

## 3.2. Validation du modèle du SCC

L'équation (8) expose les pertes dans le convertisseur SCC dépendant principalement de la fréquence de commutation de la valeur de la capacité. Ainsi, si cette dernière valeur est fixée à  $10~\mu\mathrm{F}$ , représenter  $R_{\mathrm{out}}$  en fonction de  $\beta$  renseigne sur la dépendance à la fréquence de commutation (figure 8). La résistance série (ESR) de la capacité  $C_{\mathrm{SCC}}$  est négligeable devant les 6  $\Omega$  du  $R_{\mathrm{on}}$  des transistors.

Fig. 8. Résistance équivalente de sortie du SCC en fonction de  $\beta$  ( $\propto$  1/F), comparaison des résultats de mesure avec les modèles analytiques et SPICE

On voit sur la figure 8 que les résultats fournis par le modèle analytique (courbe noire et carrés) correspondent aux résultats de mesure (courbe verte et triangles). La troisième courbe (rouge et cercles) correspond aux résultats de simulation SPICE. L'asymptote basse pour les faibles valeurs de  $\beta$  confirme la limite des équations (8) et (9) :

$$\lim_{\beta \to 0} \beta \coth\left(\frac{\beta}{2}\right) R = R \approx 2R_{\rm on} = 12\Omega \tag{26}$$

Le modèle, validé en mesures, montre les limites à l'augmentation de la fréquence ou de la valeur de la capacité :  $R_{\rm out}$  atteint un minimum pour  $\beta<0,2$  à  $2R_{\rm on}.$  Ainsi, la seule option pour améliorer le rendement est la diminution du  $R_{\rm on}$  des transistors, mais dépend fortement de la conception et de la technologie utilisée.

# 3.3. Validation du modèle du ReSC

L'équation (18) modélise les perte du ReSC de la même manière que pour le SCC, en supposant que les pertes en conduction sont liées à la résistance de sortie. Le modèle dépend d'un coefficient où le facteur d'amortissement m est explicité. En effet, l'efficacité de cette topologie dépend de la qualité de la résonance. Ce modèle est valide uniquement à la fréquence de résonance, ainsi une représentation graphique en fonction de la fréquence (comme pour le SCC) n'est pas pertinente : les résultats seront donc présentés en fonction de m. Pour cela, différents couples LC seront utilisés suivant un double objectif : maintenir des fréquences de résonances acceptables par le circuit et assurer une comparaison pertinente avec le SCC.

Atteindre un coefficient d'amortissement de 0,1 avec  $R_{on}$ aussi élevé va imposer des contraintes très fortes sur l'inductance et la capacité. La résistance série de la capacité va encore dégrader les performances du convertisseur. Pour limiter cet effet, il a été décidé de travailler avec des composants CMS, dans la gamme 1  $\mu$ F-100 $\mu$ F avec une tenue en tension d'au moins 5 V. Ainsi, avec  $C_{\rm ReSC}=1~\mu{\rm F}$  combinée avec  $L_{\rm ReSC}=3,3~{\rm mH}$ , il est possible d'atteindre m=0,1 sachant que  $R=12~\Omega$ (cf. (10)). La fréquence de commutation sera alors de 3 kHz, et  $C_{\rm SCC} = 10~\mu{\rm F}$  pour une équivalence en SCC (cf. (24)). La même méthode est appliquée pour les autres valeurs de m, résumée dans le tableau  $\overline{\ 2}$ . La valeur de  $C_{\mathrm{ReSC}}$  a été maintenue à  $1~\mu\mathrm{F},$  sauf pour m=0,9, où la valeur de  $L_{\mathrm{ReSC}}$  aurait imposé une fréquence trop élevée pour le circuit. Les résultats sont présentés en figure 9. Dans ce cas, le modèle est à nouveau validé avec moins de 10% d'erreur dans le pire cas.

Tableau 2. Values of the passive elements of each converter for the experimental validation of the models

|                | ReSC                |        | SCC                 |  |

|----------------|---------------------|--------|---------------------|--|

| $\underline{}$ | LC values           | F      | C value             |  |

| 0.1            | 3.3 mH              | 3 kHz  |                     |  |

|                | $1~\mu\mathrm{F}$   |        | $10~\mu\mathrm{F}$  |  |

| 0.2            | 1 mH                | 5 kHz  |                     |  |

|                | $1~\mu\mathrm{F}$   |        | 5 $\mu \mathrm{F}$  |  |

| 0.75           | $68~\mu\mathrm{H}$  | 13 kHz |                     |  |

|                | $1~\mu\mathrm{F}$   |        | $1.6~\mu\mathrm{F}$ |  |

| 0.9            | $150~\mu\mathrm{H}$ | 3 kHz  |                     |  |

|                | $3.3~\mu\mathrm{F}$ |        | $3.3~\mu F$         |  |

|                |                     |        |                     |  |

Fig. 9. Valeur de la résistance de sortie du ReSC en fonction de la qualité de la résonance, comparaison des résultats de mesure avec les modèles analytiques et SPICE

Les modèles de convertisseurs SCC et ReSC sont validés expérimentalement. La comparaison entre des deux convertisseurs est pertinente dans la mesure où ils reposent sur les mêmes principes : une résistance globale équivalente dépendant à la fois de la résistance à l'état passant et d'un coefficient dépendant de l'environnement,  $k_{\rm SCC}$  et  $k_{\rm ReSC}$  d'après les équations (20) et (21). Sachant les contraintes technologiques et pour une surface donnée, il sera alors possible de trouver la meilleure architecture pour une application.

### 4. CONCLUSION

Cette étude a défini un modèle basé sur les mêmes considérations pour deux topologies de convertisseurs : le convertisseur à capacité commutée (SCC) et le convertisseur résonant à capacité commutée (ReSC), dans les deux cas dans une configuration 2:1. La représentation selon un modèle de Thévenin par une source  $V_{\rm in}/2$  en série avec une résistance met en évidence la dépendance du rendement à la valeur de cette résistance de sortie. Le modèle fournit une expression pour cette résistance dépendant de paramètres intrinsèques (résistances à l'état passant et parasites) ou externes (fréquence de commutation) du convertisseur.

Ce modèle a été validé expérimentalement à l'aide d'un circuit commercial, conçu pour fonctionner en SCC. L'utilisation d'une capacité externe a permis l'adaptation du circuit à la configuration ReSC en ajoutant une inductance en série dans la boucle externe. Les mesures ont confirmé le modèle et l'estimation du rendement pour les deux architectures de convertisseur. Les paramètres critiques ont été mis en évidence dans un objectif d'amélioration du rendement ou d'une intégration CMOS.

#### 5. REMERCIEMENTS

Les auteurs tiennent à remercier l'Institut Carnot LETI pour le financement de ce projet sur une Action Exploratoire.

### 6. RÉFÉRENCES

- [1] W. Kim, M. S. Gupta, G.-Y. Wei, and D. Brooks, "System level analysis of fast, per-core DVFS using on-chip switching regulators", in *High Performance Computer Architecture*, 2008. HPCA 2008. IEEE 14th International Symposium on, 2008, pp. 123–134.

- [2] G. Pillonnet, N. Jeanniot, and P. Vivet, "3D ICs: An Opportunity for Fully-Integrated, Dense and Efficient Power Supplies", in 3D Systems Integration Conference (3DIC), 2015 IEEE International, 2016, pp. 1–4.

- [3] S. R. Sanders, E. Alon, H.-P. Le, M. D. Seeman, M. John, and V. W. Ng, "The Road to Fully Integrated DC-DC Conversion via the Switched-Capacitor Approach", *Power Electron. IEEE Trans. On*, vol. 28, no. 9, pp. 4146–4155, Sep. 2013.

- [4] M. D. Seeman, V. W. Ng, H.-P. Le, M. John, E. Alon, and S. R. Sanders, "A comparative analysis of Switched-Capacitor and inductor-based DC-DC conversion technologies", in *Control and Modeling for Power Electronics* (COMPEL), 2010 IEEE 12th Workshop on, 2010, pp. 1–7.

- [5] M. D. Seeman and S. R. Sanders, "Analysis and Optimization of Switched-Capacitor DC-DC Converters", in *Computers in Power Electronics*, 2006. COMPEL '06. IEEE Workshops on, 2006, pp. 216–224.

- [6] D. Maksimovic and S. Dhar, "Switched-capacitor DC-DC converters for low-power on-chip applications", in *Power Electronics Specialists Confe*rence, 1999. PESC 99. 30th Annual IEEE, 1999, vol. 1, pp. 54–59.

- [7] Y. Pascal and G. Pillonnet, "Efficiency Comparison of Inductor-, Capacitor-, and Resonant-Based Converters Fully Integrated in CMOS Technology", Emerg. Sel. Top. Circuits Syst. IEEE J. On, vol. 5, no. 3, pp. 421–429, Sep. 2015

- [8] G. Villar-Pique, H. J. Bergveld, and E. Alarcon, "Survey and Benchmark of Fully Integrated Switching Power Converters: Switched-Capacitor Versus Inductive Approach", *IEEE Trans. Power Electron.*, vol. 28, no. 9, pp. 4156–4167, Sep. 2013.

- [9] J. Wibben and R. Harjani, "A High-Efficiency DC-DC Converter Using 2 nH Integrated Inductors", Solid-State Circuits IEEE J. Of, vol. 43, no. 4, pp. 844–854, Apr. 2008.

- [10] C. Schaef and J. T. Stauth, "A 3-Phase Resonant Switched Capacitor Converter Delivering 7.7 W at 85% Efficiency Using 1.1 nH PCB Trace Inductors", *Solid-State Circuits IEEE J. Of*, vol. PP, no. 99, pp. 1–9, 2015.

- [11] S. Ben-Yaakov, "Behavioral Average Modeling and Equivalent Circuit Simulation of Switched Capacitors Converters", *Power Electron. IEEE Trans. On*, vol. 27, no. 2, pp. 632–636, Feb. 2012.

- [12] M. S. Makowski, "A canonical switched capacitor DC-DC converter", in Control and Modeling for Power Electronics (COMPEL), 2014 IEEE 15th Workshop on, 2014, pp. 1–8.

- [13] A. Junussov and A. Ruderman, "Analysis of a reconfigurable Fibonacci switched capacitor converter with a multiphase balanced switching", *Power Engineering, Energy and Electrical Drives (POWERENG)*, 2015 IEEE 5th International Conference on, 2015, pp. 164-169.

- [14] A. Ruderman, "Filter capacitance reduction in DC/DC step-down reconfigurable Switched-Capacitor Converters by a balanced switching", Optimization of Electrical and Electronic Equipment (OPTIM), 2012 13th International Conference on, 2012, pp. 776-782.

- [15] S. Ben-Yaakov and M. Evzelman, "Generic and unified model of Switched Capacitor Converters", in *Energy Conversion Congress and Exposition*, 2009. ECCE 2009. IEEE, 2009, pp. 3501–3508.

- [16] O.-Y. Wong and H. Wong, "Understanding the non-ideal characteristics of switched-capacitor DC-DC converters", in 2014 IEEE International Conference on Electron Devices and Solid-State Circuits (EDSSC), 2014, pp. 1–2.

- [17] Linear Technology, "Inductorless 5V to -5V converter", LTC1046 datasheet