# Background Offset and Gain Calibration for Time-Interleaved ADC Using Digital Sinusoidal Calibration Signal

Raouf Khalil, Marie-Minerve Louërat, Roger Petigny, Hugo Gicquel

# ▶ To cite this version:

Raouf Khalil, Marie-Minerve Louërat, Roger Petigny, Hugo Gicquel. Background Offset and Gain Calibration for Time-Interleaved ADC Using Digital Sinusoidal Calibration Signal. The International Conference on Synthesis, Modeling, Analysis and Simulation Methods and Applications to Circuit Design (SMACD) 2012, Sep 2012, Seville, Spain. pp.273-276, 10.1109/SMACD.2012.6339392 . hal-01282407

# HAL Id: hal-01282407 https://hal.science/hal-01282407

Submitted on 7 Oct 2022

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

Distributed under a Creative Commons Attribution - NonCommercial 4.0 International License

# Background Offset and Gain Calibration for Time-Interleaved ADC Using Digital Sinusoidal Calibration Signal

# Raouf Khalil and Marie-Minerve Louërat LIP6,Pierre and Marie Curie University, Paris, France Email: raouf.khalil-ayad@lip6.fr

This paper presents background offset and gain calibration for time-interleaved analog-to-digital converter (TIADC). The calibration technique depends on detecting the offset and the amplitude of a calibration signal. The detection is based on a simple algorithm performed in the digital part. A digital sinusoidal wave is needed to implement the calibration technique. The calibration technique behaviors are theoretically analysed and verified by simulations. A 12-bit, 4-channel, 800 MS/s TIADC is used as an example.

### I. INTRODUCTION

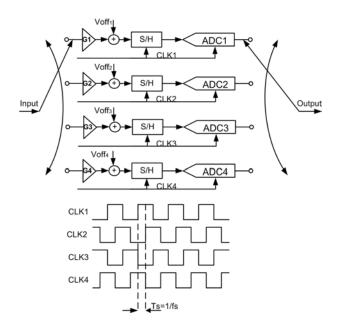

Modern communication systems applications emphasize the need for faster, higher resolution, analog-to-digital converters (ADCs) than those commercially available. These applications do not only require faster ADC but also need large dynamic range and low distortion. Speed and resolution requirements became hard to achieve with a single ADC, so an array of M ADC is used. The time-interleaved ADC (TIADC) aims to get high speed converter using low speed ADC [1]. TIADC consists of M parallel ADCs channels. The channels operate with the same sampling frequency  $f_{clk}$  with M uniformly spaced phases as shown in Fig 1. The whole system sampling frequency  $f_s$  equals  $M f_{clk}$ . Mismatches between the different channels, result in a significant performance degradation of the TIADC. The signal-to-noise and distortion ratio (SNDR), i.e. the effective number of bits ENOB, as well as the spuriousfree dynamic range (SFDR) are the most affected performance aspects. Four different types of mismatches can appear in the TIADC; offset mismatch, gain mismatch, time skew mismatch and bandwidth mismatch [2]. In this paper, we focus on the offset and gain mismatches in the TIADC and we assume that the other types of mismatches are corrected. The paper is organised as follows: Section II discusses the effects of offset and gain mismatch, the proposed technique is developed in section III; whereas simulation results are presented in section IV. Section V concludes the paper.

### II. OFFSET AND GAIN MISMATCHES

In order to illustrate the effects of offset and gain mismatch, a case study of a 12-bit, 4-channel, 800 MS/s TIADC is presented.

The offset mismatch, as shown in Fig 1, can be modelled as different DC offset voltages  $Voff_i$  - where i is an integer from

Roger Petigny and Hugo Gicquel STMicroelectronics, Grenoble, France Email: roger.petigny@st.com

Fig. 1. Four channels time interleaved ADC

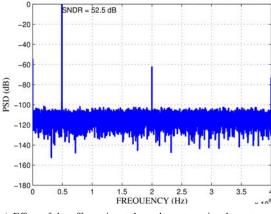

1 to M - added to each channel. The DC offsets have white Gaussian distribution with zero mean and standard deviation  $\sigma_{\text{offset}}$ . For a DC input signal, each channel will generate a different code because of these offset voltages. The offset mismatch produces spurious tones at  $\frac{k_{fs}}{M}$ , where k in an integer from 1 to M. We can see in Fig 2(a), the effect of the offset mismatch on the TIADC. These tones highly degrades the SFDR of the TIADC down to 61 dB.

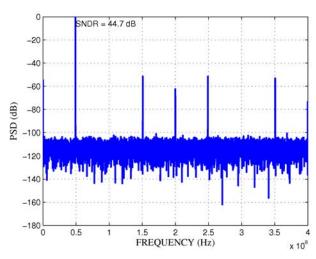

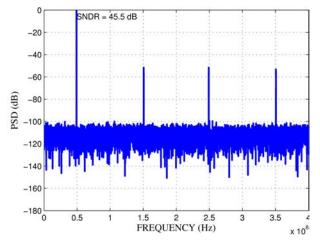

The gain mismatch is modelled as different gains  $G_i$  for each channel of the TIADC. These  $G_i$  are modelled as white Gaussian distribution with a mean equal to one and with a standard deviation  $\sigma_{gain}$ . The gain mismatch appears in the time domain as an amplitude modulation (AM) [2]. New spurious tones appear in the spectrum at  $\frac{kf_s}{M} \pm f_{in}$  where  $f_{in}$ is the input signal frequency. These spurious tones degrade the SNDR of the TIADC down to 45.5 dB. As shown in Fig 2(b), the corresponding ENOB becomes 7.3 bit. The ENOB degradation caused by the offset and gain mismatch is independent of the input signal frequency.

Calibration techniques are necessary in order to maintain the

TIADC performances. There are two modes of calibration: the foreground mode and the background mode. The foreground mode is characterized by its simplicity because the calibration is performed when the ADC is offline. However it does not account for the temperature and supply variations. On the other hand, the background mode is more complex as the calibration is performed when the ADC is online. However it ensures better correction than the foreground mode. In previous publications, offset mismatch is corrected using random sampling method to increase the SFDR of the TIADC [3]-[5]. In this technique, extra ADCs are used to spread the power of the spurious tones in the bandwidth to improve the SFDR. The improvement of the SFDR depends on the number of extra ADCs but the SNDR is not improved. In [6], 2channel TIADC was used. A random chopper-based is used to overcome the offset mismatch. the input signal is converted to white signal which allows the detection of the DC offset. On the other hand, the gain mismatch is corrected by correlationbased algorithms between the input signal and gain spurious tone. The drawback of this technique is the conversion rate that depends on the input signal. Also, The complexity of the notch filter used increases with number of ADCs used in the system. Our proposed offset and gain calibration technique is based on a simple algorithm, performed in background mode. The algorithm is presented in the following section.

## III. PROPOSED OFFSET AND GAIN CALIBRATION TECHNIQUES

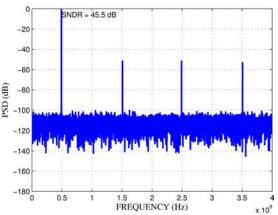

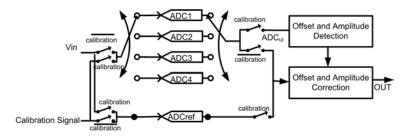

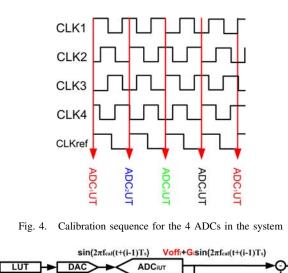

Our proposed calibration technique is presented in Fig 3. An additional reference ADC (ADC<sub>ref</sub>) is used as suggested in [7], [8]. ADC<sub>ref</sub> operates with clock frequency CLK<sub>ref</sub> equal to  $\frac{f_s}{M+1}$ , where M is the number of channels used in the TIADC. Therefore, the CLK<sub>ref</sub> cycles are in phase with the other clocks as shown in Fig 4. Thus, the ADC<sub>ref</sub> can replace the ADC under test ADC<sub>iUT</sub> to convert the input signal. A sine wave calibration signal with frequency equal to  $f_{cal}$  is generated digitally and injected to the ADC<sub>iUT</sub>. The generation of the calibration signal is performed using a Look-up table (LUT) and a digital-to-analog converter DAC as shown in Fig 5 and Fig 6. Digital algorithm is applied on the calibration signal at the output of the ADC<sub>iUT</sub> to detect and correct the offset and gain mismatches errors.

### A. Offset Calibration Technique

As mentioned earlier, the offset mismatch introduces different DC offset Voff<sub>i</sub> in each channel. Voff<sub>i</sub> is added to the digital output of the calibration signal for each  $ADC_{iUT}$ . From the equations below (Eq 1-Eq 3), X<sub>lut</sub> is the digital sinusoidal signal stored in the LUT. This digital signal is converted to analog by the DAC and injected to the  $ADC_{iUT}$ . The DC offset can be detected by averaging the  $ADC_{iUT}$  output during a known multiple of the calibration signal period. An accumulator is used for averaging the digital output of the

(a) Effect of the offset mismatch on the output signal spectrum. ( $\sigma_{\rm offset}=1mV$ )

(b) Effect of the gain mismatch on the output signal spectrum. ( $\sigma_{\rm gain}=0.005$ )

Fig. 2. 12-bit, 4-channel, 800 MS/s time-interleaved ADC suffering from offset and gain mismatches

Fig. 3. Proposed background calibration technique using 4-channel time-interleaved ADC

calibration signal as shown in Fig 5.

$$\mathbf{X}_{\text{lut}} = \sin(2\pi f_{cal}(t + (i-1)T_s)) \tag{1}$$

$$ADC_{iUT} = Voff_i + G_i sin((2\pi f_{cal}(t + (i-1)T_s)))$$

(2)

$$avg(ADC_{iUT}) = Voff_i$$

(3)

The correction is done simply by subtracting the calculated offset  $Voff_i$  from  $ADC_i$  output. The offset of  $ADC_{ref}$  must be also calibrated.

Fig. 5. The offset calibration technique for one ADC under test

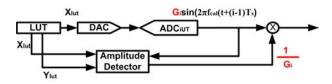

#### B. Gain Calibration Technique

As shown in Fig 5, the output of the calibration signal from each  $ADC_{iUT}$  is multiplied by a gain G<sub>i</sub>. This gain can be detected by calculating the amplitude of the  $ADC_{iUT}$  output. The used algorithm is illustrated in the following equations (Eq 4-Eq 9). The algorithm uses the sine and cosine digital signals stored in the LUT (X<sub>lut</sub> & Y<sub>lut</sub>). Fast Fourier Transform (FFT) is applied to the known calibration signal frequency  $f_{cal}$ .

$$ADC_{iUT}(t) = G_{i}sin(2\pi f_{cal}(t + (i-1)Ts))$$

(4)

$$\mathbf{X}_{\text{lut}}(\mathbf{t}) = \sin(2\pi f_{cal}(t + (i-1)Ts)) \tag{5}$$

$$Y_{lut}(t) = \cos(2\pi f_{cal}(t + (i-1)Ts))$$

(6)

$$\mathbf{X} = [\operatorname{avg}(\operatorname{ADC}_{\mathrm{iUT}} \times \mathbf{X}_{\mathrm{lut}})]^2 \tag{7}$$

$$\mathbf{Y} = [\operatorname{avg}(\operatorname{ADC}_{\operatorname{iUT}} \times \mathbf{Y}_{\operatorname{lut}})]^2 \tag{8}$$

$$G_i = 2\sqrt{X+Y} \tag{9}$$

Accumulator

After detecting the gain  $G_i$ , ADC<sub>i</sub> output is multiplied by  $\frac{1}{G_i}$  to correct the gain mismatch as shown in Fig 6. The gain calibration technique can be performed in the presence of phase shift between the ADC output and the LUT. Also, there are no dependency between the gain and the offset techniques so they can be implemented in parallel.

Fig. 6. The gain calibration technique for one ADC under test

#### **IV. SYSTEM LEVEL SIMULATION RESULT**

Simulink is used to model 12-bit, 4 ideal channels, 800 MS/s TIADC, shown in Fig 3. The sampling frequency of

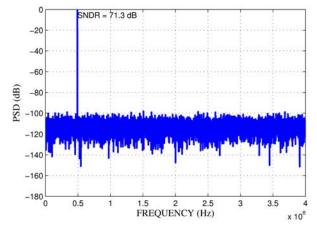

each ADC is 200 MHz and the clock frequency of the  $ADC_{ref}$ CLK<sub>ref</sub> is 160 MHz. 4096 samples are used in the calibration algorithm to detect the offset Voff<sub>i</sub> and the gain G<sub>i</sub> mismatches. The digitally generated calibration signal frequency  $f_{cal}$  is 60 MHz. The DAC is modelled to add some non-linearity (third harmonic distortion HD3) and thermal noise to the calibration signal, for which -50 dB and  $1mV_{rms}$  are used respectively. Fig 7(a) shows the simulation results before applying the proposed technique. The input frequency  $f_{in}$  is selected to be 50 MHz. The power spectral density shows the spurious tones caused by the offset mismatch at 0, 200 MHz and 400 MHz. The spurious tones at 150 MHz, 250 MHz and 350 MHz are caused by the gain mismatch. The ENOB equals 7.1 bit and SFDR equals 62.6 dB. Fig 7(b) shows the simulation results after applying the offset calibration technique. The spurious tones caused by the offset mismatch are suppressed and the SFDR increases to 100dB. The gain calibration technique is further applied and ENOB increases to 11.6 bit as shown in Fig 7(c). The proposed technique has improved the TIADC performances using the calibration signal which is highly distorted by the DAC.

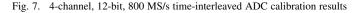

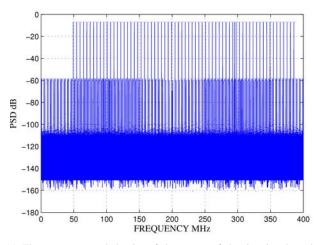

In Fig 8, a multiple-frequency input signal is injected instead of using single frequency input signal. In actual applications, the TIADC is used in multi-channel receiver to convert multiple-frequency input signal. In this test, equally spaced frequencies from 50 MHz to 390 MHz, i.e 132 different frequencies, are injected to the TIADC. Without calibration, these frequencies produce a lot of undesired spurious tones because of the offset and gain mismatches as shown in Fig 8(a). After applying the proposed calibration technique, the input frequencies are left alone, as shown in Fig 8(b), whereas the undesired spurious tones are totally suppressed.

#### V. CONCLUSION

An offset and gain background calibration technique has been proposed. The background mode is performed using a reference ADC that operates using a slower frequency. The calibration technique is based on applying digital algorithm on a digital sinusoidal calibration signal, injected to the ADC under test. The offset calibration depends on averaging the output of each ADC under test. The gain calibration depends on applying FFT to the output of the ADC under test. The calibration technique is tolerant to high distortion which simplifies the DAC implementation. The system simulation proves the efficiency of the proposed technique: a significant improvement has been demonstrated in both the ENOB and the SFDR performances of the TIADC.

#### VI. ACKNOWLEDGEMENT

This project is funded by French Research Program NANO-2012 in cooperation with STMicroelectronics R&D Team, Grenoble.

#### REFERENCES

J. Black, W. and D. Hodges, "Time interleaved converter arrays," in Solid-State Circuits Conference. Digest of Technical Papers. 1980 IEEE International, vol. 15, feb 1980, pp. 14 – 15.

(a) Power spectral density of the output of the time-interleaved ADC before offset and gain calibration

(b) Power spectral density of the output of the time-interleaved ADC after offset calibration

(c) Power spectral density of the output of the time-interleaved ADC after gain calibration

(a) The power spectral density of the output of the time-interleaved ADC before calibration.

(b) The Power spectral density of the output of the time-interleaved ADC after calibration.

Fig. 8. Multiple-frequency input signal injected to the time-interleaved ADC

- [2] N. Kurosawa, H. Kobayashi, K. Maruyama, H. Sugawara, and K. Kobayashi, "Explicit analysis of channel mismatch effects in timeinterleaved ADC systems," *IEEE Transaction on Circuits and systems-I: fundamental theory and applications*, vol. 48, pp. 261–271, 2001.

- [3] M. Tamba, A. Shimizu, H. Munakata, and T. Komuro, "A method to improve SFDR with random interleaved sampling method," in *ITC International Test Conference*, 2001.

- [4] J. Elbornsson, F. Gustafsson, and J.-E. Eklund, "Analysis of mismatch effects in a randomly interleaved A/D converter system," *Circuits and Systems I: Regular Papers, IEEE Transactions on*, vol. 52, no. 3, pp. 465 – 476, march 2005.

- [5] C. Vogel, V. Pammer, and G. Kubin, "A novel channel randomization method for time-interleaved ADCs," in *Instrumentation and Measurement Technology Conference*, 2005. IMTC 2005. Proceedings of the IEEE, vol. 1, may 2005, pp. 150–155.

- [6] S. Jamal, D. Fu, N.-J. Chang, P. Hurst, and S. Lewis, "A 10-b 120-Msample/s time-interleaved analog-to-digital converter with digital background calibration," *Solid-State Circuits, IEEE Journal of*, vol. 37, no. 12, pp. 1618 – 1627, dec 2002.

- [7] E. Iroaga, B. Murmann, and L. Nathawad, "A background correction technique for timing errors in time-interleaved analog-to-digital converters," in *Circuits and Systems*, 2005. ISCAS 2005. IEEE International Symposium on, may 2005, pp. 5557 – 5560 Vol. 6.

- [8] M. El-Chammas and B. Murmann, "A 12-GS/s 81-mW 5-bit timeinterleaved flash ADC with background timing skew calibration," *IEEE Journal of solid state*, vol. 46, no. 4, pp. 838 –847, april 2011.