## Temperature dependence and dynamic behaviour of full well capacity in pinned photodiode CMOS image sensors

Alice Pelamatti, Jean-Marc Belloir, Camille Messien, Vincent Goiffon, Magali Estribeau, Pierre Magnan, Cédric Virmontois, Olivier Saint-Pé, Paillet Philippe

#### ▶ To cite this version:

Alice Pelamatti, Jean-Marc Belloir, Camille Messien, Vincent Goiffon, Magali Estribeau, et al.. Temperature dependence and dynamic behaviour of full well capacity in pinned photodiode CMOS image sensors. IEEE Transactions on Electron Devices, 2015, 62 (4), pp.1200-1207. 10.1109/TED.2015.2400136. hal-01275212

HAL Id: hal-01275212

https://hal.science/hal-01275212

Submitted on 17 Feb 2016

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### Open Archive TOULOUSE Archive Ouverte (OATAO)

OATAO is an open access repository that collects the work of Toulouse researchers and makes it freely available over the web where possible.

This is an author-deposited version published in: <a href="http://oatao.univ-toulouse.fr/">http://oatao.univ-toulouse.fr/</a>

**Eprints ID**: 13927

**To link to this article**: DOI: 10.1109/TED.2015.2400136 URL: http://dx.doi.org/10.1109/TED.2015.2400136

**To cite this version**: Pelamatti, Alice and Belloir, Jean-Marc and Messien, Camille and Goiffon, Vincent and Estribeau, Magali and Magnan, Pierre and Virmontois, Cédric and Saint-Pé, Olivier and Bréart-de-Boisanger, Michel <u>Température dependence and dynamic behaviour of full well capacity in pinned photodiode cmos image sensors. (2015)</u>

IEEE Transactions on Electron Devices, vol.62 (n°4). pp.1200-1207. ISSN 0018-9383

Any correspondance concerning this service should be sent to the repository administrator: <a href="mailto:staff-oatao@listes-diff.inp-toulouse.fr">staff-oatao@listes-diff.inp-toulouse.fr</a>

# Temperature Dependence and Dynamic Behaviour of Full Well Capacity in Pinned Photodiode CMOS Image Sensors

Alice Pelamatt, Jean-Marc Belloir, Camille Messien, Vincent Goiffon, Magali Estribeau, Pierre Magnan, Cédric Virmontois, Olivier Saint-Pé, Philippe Paillet,

Abstract—This study presents an analytical model of the Full Well Capacity (FWC) in Pinned Photodiode (PPD) CMOS image sensors. By introducing the temperature dependence of the PPD pinning voltage, the existing model is extended (with respect to previous works) to take into account the effect of temperature on the FWC. It is shown, with the support of experimental data, that whereas in dark conditions the FWC increases with temperature, a decrease is observed if FWC measurements are performed under illumination. This study also shows that after a light pulse, the charge stored in the PPD drops as the PPD tends toward equilibrium. On the base of these observations, an analytical model of the dynamic behaviour of the FWC in noncontinuous illumination conditions is proposed. The model is able to reproduce experimental data over six orders of magnitude of time. Both the static and dynamic models can be useful tools to correctly interpret FWC changes following design variations and to accurately define the operating conditions during device characterizations.

Index Terms—CMOS Image Sensor, CIS, pinned photodiode, PPD, Pinning Voltage, full well capacity, FWC, dynamic behaviour, modeling, analytical modeling, temperature, active pixel sensor, APS, capacitance.

#### I. Introduction

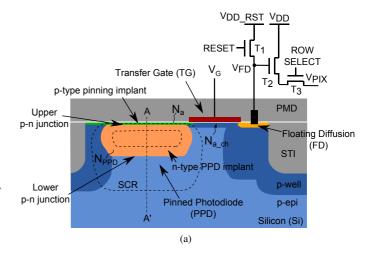

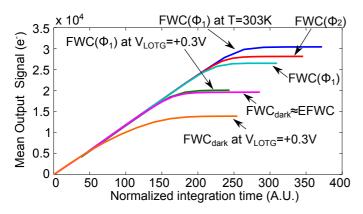

RIVEN by low noise applications, Pinned Photodiode (PPD) [1]–[3] CMOS Image Sensors (CIS) (schematized in Fig. 1a) have recently become the main image sensors technology for both commercial and scientific applications. Despite the technology maturity, the literature on the physics of the PPD is not yet exhaustive and the definition, estimation, modeling and measurement of PPD fundamental parameters remain topical subjects. Figure 2 shows the mean sensor output signal as a function of a normalized integration time measured in different operating conditions. As it can be observed, the saturation level, which corresponds here to the Full Well Capacity (FWC) of the PPD, strongly varies with the photon flux  $(\Phi)$ , with temperature (T) and with the Transfer Gate (TG)biasing voltage applied during charge-integration  $(V_{\rm LOTG})$ . The dependence of the FWC on the illumination conditions has been addressed in [4] and later in [5], where FWC variations

A. Pelamatti (email: alice.pelamatti@isae.fr), J.M. Belloir, V. Goiffon, C. Messien, M. Estribeau and P. Magnan are with ISAE-SUPAERO, Université de Toulouse, Toulouse, France. C. Virmontois is with CNES, Toulouse, France. O. Saint Saint-Pé is with Airbus Defence&Space, Toulouse, France. P. Paillet is with CEA, Bruyères-le-Châtel, France.

The authors would like to thank CNES and Airbus Defence&Space for supporting the Ph.D of A. Pelamatti, and CNES and CEA for supporting the Ph.D of J.M. Belloir.

| Studied sub-array size | $64 \times 128$ pixels                           |

|------------------------|--------------------------------------------------|

| Pixel pitch            | $7~\mu\mathrm{m}$                                |

| PPD size               | $2.5 \ \mu\mathrm{m} \times 2.5 \ \mu\mathrm{m}$ |

| CVF                    | $20 \; \mu { m V/e^-}$                           |

| (b)                    |                                                  |

Fig. 1. (a) Schematic drawing of the PPD 4 Transistors (4T) Active Pixel Sensor (APS). STI stands for Shallow Trench Isolation, PMD for Pre-Metal Dielectric, SCR stands for Space Charge Region. (b) Details on the device under test.

are explained by means of the TG sub-threshold current. In [6] we recently proposed an analytical model of the FWC, extended to all TG biasing conditions.

In this paper, the analytical model is used as a support to describe the saturation mechanisms responsible for the different FWC levels in the different operating conditions presented in Fig. 2. With respect to [6], the model is extended to take into account the effect of temperature on the FWC. For this purpose, a new temperature model of the pinning voltage is proposed. As it will be discussed, opposite behaviours of the FWC with temperature can be observed depending on the operating conditions. A second contribution of this paper is the extension of the analytical model to non-equilibrium conditions. In particular, this study presents and validates a model of the dynamic behaviour of the FWC following a light pulse.

#### II. DEVICE UNDER TEST

The device tested in this study is a  $256 \times 256$ , 7  $\mu m$ -pitch pixel array, manufactured in a commercial  $0.18~\mu m$

Fig. 2. Mean sensor output signal plotted as a function of a normalized integration time (with respect to the charge generation rate) measured for different operating conditions.  $\Phi_1=4\times 10^{13}~\mathrm{ph/s/cm^2},\,\Phi_2=2\times 10^{14}~\mathrm{ph/s/cm^2}.$  Unless specified, all measurements have been performed at  $T=333~\mathrm{K}$  and  $V_{\mathrm{LOTG}}=-0.5~\mathrm{V}$ . A.U. stands for Arbitrary Units, EFWC stands for Equilibrium Full Well Capacity (see section V). Details on the device under test can be found in section II.

PPD CIS process. The pixel array is divided in several subarrays of  $64 \times 128$  pixels, each sub-array having a different PPD/TG design. The measurements presented in this work refer to a sub-array with pixels having a square  $2.5 \times 2.5 \mu \text{m}^2$ PPD, a long TG and a long Floating Diffusion (FD) (both  $2.5~\mu\mathrm{m}$  wide) on one side. The TG is  $0.7~\mu\mathrm{m}$  long. The Charge to Voltage conversion Factor (CVF) is about  $20 \mu V/e^{-}$ (10\% standard deviation over the sub-array), which, associated with readout chain characteristics, guarantees that the output voltage saturation is limited by the PPD FWC<sup>1</sup>. Details on the device under test are summarized in Fig. 1b. Measurements are performed within a climatic chamber (with a temperature precision of  $\pm 0.1$  K). Unless specified, experimental data correspond to the mean array signal, averaged over 100 acquisitions. The exposure time differs depending on  $\Phi$  and T.

## III. DEFINITION AND ESTIMATION OF THE FULL WELL CAPACITY

The FWC corresponds to the maximum amount of charge that can be held by a PPD. It represents a key parameter, as it allows to estimate the dynamic range of the image sensor. If  $C_{\rm PPD}$  is the PPD capacitance, the FWC can be expressed as a function of two independent parameters,  $V_{\rm pin}$  and  $V_{\rm OC}$ :

$$FWC = \frac{1}{q} \int_{V_{DC}}^{V_{PD}} C_{PPD}(V_{PPD}) dV_{PPD}$$

(1)

with q the elementary charge.

$V_{\rm pin}$  is the maximum PPD channel potential, often referred to as pinning voltage [7], and is reached during the reset of the photodiode, i.e. during the charge transfer phase in standard PPD CIS operation for a no image lag detector<sup>2</sup>. It

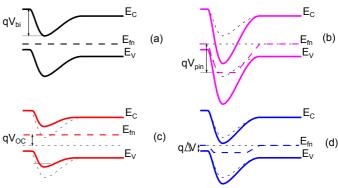

Fig. 3. Schematic of the energy-band diagram of the PPD along the cut A-A' in Fig. 1, (a) at equilibrium, (b) at full depletion (after charge transfer), (c) at full well under illumination (TG in accumulation mode) and (d) at full well in the dark with the TG not in accumulation mode. The dashed black lines in (b), (c) and (d) represent the band diagram at equilibrium schematized in (a).  $V_{\rm pin}$  is the pinning voltage,  $V_{\rm bi}$  is the built-in voltage,  $V_{\rm CC}$  is the open circuit voltage and q $\Delta V$  represents the difference between  $E_{\rm fn}$  at full well at equilibrium and  $E_{\rm fn}$  at full-well considering a leakage of the TG.

corresponds to the maximum variation of the electron quasi-Fermi level  $E_{\rm fn}$  at full depletion (Fig. 3b) with respect to equilibrium conditions (Fig. 3a). After the transfer phase, the photodiode potential is floating, and it decreases as charges are integrated in the PPD capacitance. At full well, the total current across the photodiode is null ( i.e. the PPD reaches an open circuit condition), therefore, the open circuit voltage  $V_{\rm OC}$  in (1) corresponds to the minimum PPD potential. As detailed in the following sections,  $V_{\rm OC}$  strongly varies with T,  $\Phi$  and  $V_{\rm LOTG}$ , whereas  $V_{\rm pin}$  only depends on T and on technological and geometrical parameters.

#### IV. PINNING VOLTAGE TEMPERATURE DEPENDENCE

The pinning voltage, also referred to as pinch-off voltage [8], in analogy to the pinch-off voltage in Junction Field Effect Transistors (JFETs), corresponds to the PPD biasing voltage required to fully deplete the photodiode. It represents a critical design parameter in PPD CIS:

- as shown in (1), the higher is  $V_{\rm pin}$ , the higher is the achieved FWC;

- however,  $V_{\rm pin}$  must be carefully adjusted, depending on the supply voltage domain, to guarantee a good Charge Transfer Efficiency (CTE) toward the FD [9].

By using an abrupt junction approximation [10], the pinning voltage  $(V_{pin})$  can be expressed as:

$$V_{\rm pin}(T) \approx \frac{q N_{\rm PPD} W_{\rm PPD}^2}{2\epsilon_{\rm Si}} - V_{\rm bi}(T)$$

(2)

where  $\epsilon_{\rm Si}$  is the Si permittivity,  $W_{\rm PPD}$  is the depth of buried channel and  $N_{\rm PPD}$  is the doping concentrations of the PPD buried channel implant.  $V_{\rm bi}$  corresponds to the built-in voltage of the upper junction, which depends on the intrinsic concentration  $n_{\rm i}$ , on  $N_{\rm PPD}$  and on the pinning implant doping concentration  $N_{\rm a}$  [10]. To model the temperature behaviour of  $V_{\rm bi}$ ,  $n_{\rm i}(T)$  has been modeled as in [11].

To simplify the model in (2) as much as possible, the contribution of the lower p-n junction has been neglected (this

<sup>&</sup>lt;sup>1</sup>For higher CVF values, the maximum output signal can be limited by the saturation of the readout electronics. In this case, FWC variations do not reflect on the experimental measurements.

<sup>&</sup>lt;sup>2</sup>If the image sensor presents a non-negligible image lag, the PPD never reaches full depletion, leading to an under-estimation of the FWC and  $V_{\text{Din}}$ .

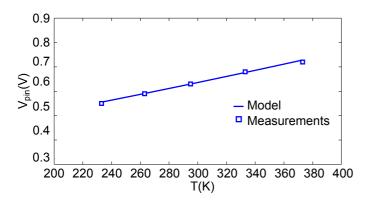

Fig. 4. Pinning voltage as a function of temperature: comparison between experimental data (extracted with the integral method presented in [14]) and the model of (2). The best fit has been obtained for  $N_{\rm PPD}=2.4\times10^{16}~{\rm cm}^{-3},$   $N_{\rm a}=1\times10^{18}~{\rm cm}^{-3}$  and  $W_{\rm PPD}=280~{\rm nm}.$

can be justified by the fact that the doping concentration of the epitaxy is much lower than the one of the p+ implant). Geometrical effects such as the geometrical modulation of  $V_{\rm pin}$  described in [12] or additional 3D effects such as the ones presented in [8] have also been neglected. The study of the impact of temperature on the geometrical dependence of  $V_{\rm pin}$  is left for future studies.

Different pinning voltage extraction techniques have been proposed in the literature [8], [13], [14]. In this work  $V_{\rm pin}$  has been extracted from the pinning voltage characteristic [13] with the integral method proposed by Goiffon et~al. in [14]. As it can be observed in Fig. 4,  $V_{\rm pin}$  increases with temperature, and the model in (2) well reproduces the temperature behaviour observed on experimental data.

## V. TEMPERATURE DEPENDENCE OF THE FWC AT EQUILIBRIUM

After the reset of the photodiode, the PPD is empty, and the PPD channel potential is equal to the pinning voltage. If the PPD is reset and left in the dark with the TG accumulated, the PPD capacitance is discharged by the dark current  $I_{\rm junc}$ , until reaching a saturation level which corresponds to the equilibrium condition of a p-n junction. The saturation charge obtained in dark conditions and neglecting the TG leakage current is referred to as the EFWC [6], [14]. The open circuit voltage  $V_{\rm OC}$  corresponding to the EFWC can be obtained by solving:

$$I_{\text{TOT}} = I_{\text{junct}} = I_{\text{sat}} \left( e^{-\frac{V_{\text{OC}}}{nv_{\text{th}}}} - 1 \right) = 0$$

(3)

with n the diode non-ideality factor (1 < n < 2),  $v_{\rm th} = \frac{kT}{q}$  the thermal voltage, and  $I_{\rm sat}$  the saturation current [10]. As in standard p-n junctions, the equilibrium condition expressed in (3) holds for  $V_{\rm OC}=0$ . The EFWC can be calculated with (1) as:

$$EFWC(T) = \frac{1}{q} \int_0^{Vpin(T)} C_{PPD}(V_{PPD}) dV_{PPD}. \quad (4)$$

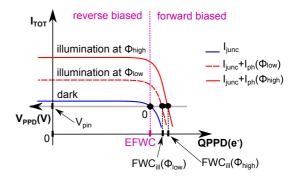

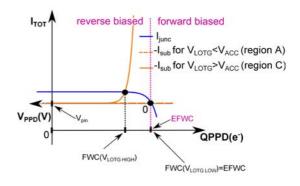

The blue solid curve in Fig. 5 represents the PPD current in the dark as function of the PPD voltage  $V_{\rm PPD}$  and of the stored

Fig. 5. Schematic of the PPD I-V characteristic in the dark and under two different illumination levels. Full depletion is reached when  $Q_{\rm PPD}=0$  and  $V_{\rm PPD}=V_{\rm pin}$ . Full well is reached at open circuit condition ( $I_{\rm TOT}=0$ ). The open circuit PPD potential  $V_{\rm OC}$  (and the corresponding FWC) varies depending on the illumination condition. In particular, EFWC corresponds to the FWC in the dark, whereas FWC $_{\rm ill}$  is the FWC under illumination. For clarity purposes, schematics are not to scale.

charge  $Q_{\rm PPD}$ . The EFWC corresponds to the open circuit condition (i.e.  $I_{\rm junc}=0$ ).

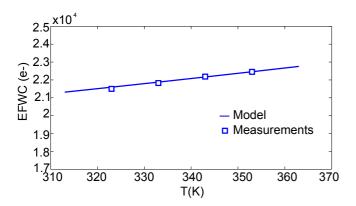

In practice, in nominal PPD CIS operating conditions, the EFWC cannot be reached, and the FWC measured in the dark with TG accumulated corresponds to a saturation charge which is always slightly lower than the EFWC. This difference is attributed to the fact that the TG will always have a small leakage current (sub-threshold current), whichever the TG biasing voltage during integration. To simplify the development of the model, the small difference between EFWC and FWC<sub>dark</sub> is neglected. Charge partition phenomena during the transitions of the TG signal [15] (which can result in an artificial increase of the FWC) will also be neglected in this study. Figure 6 shows the measured EFWC as function of temperature. As it can be observed, the model well reproduces the increase of the EFWC with temperature, which is mainly attributed to the increase in  $V_{\rm pin}$ .

Whereas the voltage dependence of  $C_{\rm PPD}$  is taken into account to fit experimental data in section VI, for clarity purposes  $C_{\rm PPD}$  variations will be neglected in the following equations, and the FWC will be simply expressed as:

$$FWC = EFWC - \frac{1}{q}V_{OC}C_{PPD}.$$

(5)

Note that when FWC > EFWC,  $V_{\rm OC} < 0$  and the PPD is forward biased (resulting in blooming phenomena).

## VI. TEMPERATURE DEPENDENCE OF THE FWC AT PSEUDO-EQUILIBRIUM

When the PPD is illuminated, or when the TG is not accumulated during charge integration, the PPD reaches a different saturation level than the EFWC. In the following subsections, the saturation mechanisms for different operating conditions are detailed. In particular, subsection VI-A discusses the behaviour of the FWC when the TG is accumulated during integration, which is a typical biasing mode used to reduce the dark current [16], [17]. In sections VI-B the FWC is modeled for the case in which the TG is not accumulated during integration to implement an anti-blooming function.

Fig. 6. Measured EFWC as a function of temperature. The best fit has been obtained for  $N_{\rm PPD}=3.4\times10^{16}~{\rm cm^{-3}},~N_{\rm a}=1\times10^{18}~{\rm cm^{-3}}$  and  $W_{\rm PPD}=280~{\rm nm}.$

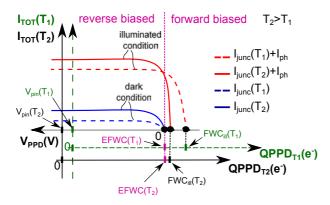

Fig. 7. Schematic of the effect of temperature on the PPD I-V characteristic in the dark and under illumination. For more details on the schematic main features, refer to the explanations in the caption of Fig. 5. The increase in temperature causes an increase in  $V_{\rm pin}$  (which is represented as a left shift of the  $Q_{\rm PPD}$  axis origin  $Q_{\rm PPD}=0$ ), which yields to an increase of the EFWC. As it can be observed, under illumination the FWC tends to decrease as temperature is increased. For clarity purposes, schematics are not to scale.

## A. FWC variations as a function of temperature for different illumination conditions (accumulated TG)

If the PPD is exposed to a photon flux  $\Phi$ , with the TG in accumulation mode, the open circuit condition can be expressed as:

$$I_{\text{sat}}\left(e^{-\frac{V_{\text{OC}}}{nv_{\text{th}}}} - 1\right) = I_{\text{ph}}(\Phi) \tag{6}$$

with  $I_{\rm ph}(\Phi)=\eta\Phi$  the photocurrent, where  $\eta$  is the quantum efficiency. The corresponding open circuit voltage can be calculated as:

$$V_{\rm OC} = -nv_{\rm th} \ln \left( 1 + \frac{I_{\rm ph}(\Phi)}{I_{\rm sat}} \right). \tag{7}$$

By combining (5) and (7), the FWC can finally be expressed as

$$FWC(\Phi, T) = EFWC(T) + \frac{1}{q} C_{PPD} n v_{th} \ln \left[ 1 + \frac{I_{ph}(\Phi)}{I_{sat}(T)} \right].$$

As shown in (7),  $V_{\rm OC} < 0$ , which means that the PPD is forward biased at full-well (Fig. 3c), and thus FWC>EFWC (which is in agreement with the measurements presented in

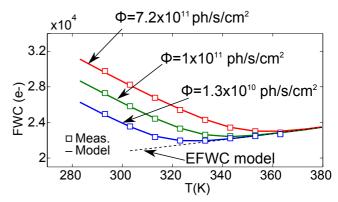

Fig. 8. Full well capacity as a function of temperature measured for 3 different photon fluxes and for the TG in accumulation mode. Square markers represent experimental data, solid lines refer to the FWC modeled as in (8). The dashed line refers to the EFWC modeled as in (4). The best fit has been obtained with the same parameters as in Fig. 6

Fig. 2). Equation (8) shows that the FWC depends logarithmically on the photon flux [4], [6]. This effect is schematized in Fig. 5, where the sum of the dark current and the photocurrent is plotted for two different photon fluxes (solid and dashed red curves). As it can be observed,  $V_{\rm OC}$  increases as  $\Phi$  is increased, which results in a higher FWC.

Equation (8) also indicates that the FWC under illumination is a strong function of temperature. In particular, there are two different and opposite temperature effects, which are schematized in Fig. 7:

- on one hand, as the temperature is increased, there is an increase in the thermal voltage  $v_{\rm th}$  and in  $V_{\rm pin}$ . These two contributions alone would lead to an increase of the FWC with temperature (as in dark conditions).

- On the other hand, there is an exponential increase in the saturation current  $I_{\rm sat}$  [10] which results in a decrease of  $V_{\rm OC}$  and in a net decrease of the FWC.

Figure 8 shows the FWC measured for different  $\Phi$  as a function of temperature. As long as the ratio  $\frac{I_{\mathrm{ph}}(\Phi)}{I_{\mathrm{sat}}} >> 1$ , the temperature dependence of  $I_{\mathrm{sat}}(T)$  is the dominant effect, and the FWC decreases with temperature. If the temperature is increased, the saturation current becomes comparable to the photocurrent and eventually the FWC becomes equal to the EFWC and starts to increase with temperature. As it can be observed, the model can well reproduce the behaviour observed on experimental data.

## B. FWC variations as a function of temperature for different TG biasing conditions

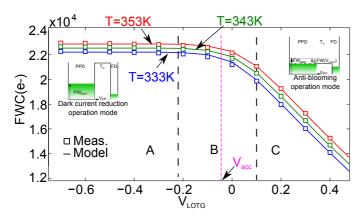

Figure 9 shows the FWC measured in the dark plotted as a function of  $V_{\rm LOTG}$  for three different measurement temperatures. Three operating regions can be identified:

- for negative  $V_{\rm LOTG}$  the FWC corresponds to the EFWC (region A);

- when  $V_{\rm LOTG}$  is increased, we observe a transition region (region B) in which the FWC drops moderately with  $V_{\rm LOTG}$ ;

- for even higher  $V_{\rm LOTG}$ , the FWC drops linearly with  $V_{\rm LOTG}$  (region C).

Fig. 9. Measured and simulated FWC as a function of  $V_{\rm LOTG}$  at different T in dark conditions. The best fit has been obtained with the same parameters as in Fig. 6.

The knee voltage, indicated in Fig. 9 as  $V_{\rm acc}$ , corresponds roughly to the  $V_{\rm LOTG}$  at which the TG sub-threshold current  $(I_{\rm sub})$  [10] is comparable to  $I_{\rm junc}$ .  $V_{\rm acc}$  can also be seen as the biasing voltage  $V_{\rm LOTG}$  at which the TG exits the accumulation mode). FWC variations can be modeled by introducing in (3) the contribution of  $^3$   $I_{\rm sub} = I_{\rm D0} e^{\frac{V_{\rm LOTG} - V_{\rm OC} - V_T}{mv_{\rm th}(T)}}$ :

$$I_{\rm D0}e^{rac{V_{

m LOTG}-V_{

m OC}-V_T}{mv_{

m th}(T)}} + I_{

m sat}\left(1 - e^{-rac{V_{

m OC}}{nv_{

m th}}}\right) = 0$$

(9)

where  $I_{\rm D0}$  depends on the TG geometrical and physical parameters, m is the TG sub-threshold slope (m>1) and  $V_{\rm T}$  is the TG threshold voltage (considering body effect).

To highlight the effect of the different parameters, (9) can be expressed as a function of  $V_{\rm OC}$ . In particular, as schematized in Fig. 10:

• in region A ( $V_{\rm LOTG} < V_{\rm acc}$ )  $I_{\rm sub}$  is negligible with respect to  $I_{\rm junc}$ , thus:

$$V_{\rm OC_A} \approx 0$$

(10)

• in region C ( $V_{\rm LOTG} > V_{\rm acc}$ )  $I_{\rm sub} >> I_{\rm sat}$ , thus:

$$V_{\rm OC_C} = V_{\rm LOTG} - V_{\rm T} - nv_{\rm th} \ln \left( \frac{I_{\rm sat}}{I_{\rm D0}} \right)$$

(11)

where to simplify the expression it is assumed that  $n, m = 1^4$ . Combining (10) and (11) with (5) gives, respectively:

$$FWC_{A}(T) = EFWC(T)$$

(12)

$$FWC_{C}(T) = EFWC(T) - \frac{1}{q}C_{PPD}\left(V_{LOTG} - V_{T}(T)\right)$$

(13)

where the ratio  $\frac{I_{\rm sat}}{I_{\rm D0}} << 1$  has been neglected. Note that, in region C, the PPD is reversed biased ( $V_{\rm OC}>0$ ). In (13) only two parameters can vary with temperature:  $V_{\rm pin}$  and  $V_{\rm T}$ . As the increase in the FWC with temperature in Fig. 9 is more or less constant at all TG biasing conditions, the increase of  $V_{\rm pin}$  can be identified as the dominant effect.

Fig. 10. Schematic of the effect of  $V_{\rm LOTG}$  on the PPD I-V characteristic. For clarity purposes, the schematic is not to scale and  $-I_{\rm sub}$  is plotted instead of  $I_{\rm sub}$ . Since full well is reached for  $I_{\rm junc} = -I_{\rm sub}$ , the open circuit condition corresponds to the crossing of the two curves.

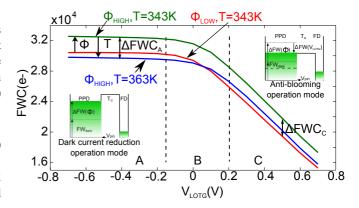

Fig. 11. Full well capacity measured at  $T=343~{\rm K}$  for two photon fluxes ( $\Phi_{\rm LOW}=3\times 10^{14}~{\rm ph/s/cm^2}$  and  $\Phi_{\rm HIGH}=1.4\times 10^{15}~{\rm ph/s/cm^2}$ ) and at  $T=363~{\rm K}$  for  $\Phi_{\rm HIGH}$ , as a function of  $V_{\rm LOTG}$ .

The reasoning in section VI-B can be extended to the illumination conditions by adding a constant photocurrent to (9). Figure 11 shows the FWC measured for two different photon fluxes and two different temperatures as a function of  $V_{\rm LOTG}$ . If  $V_{\rm LOTG} < V_{\rm acc}$ , the FWC is the same as in (8), whereas when  $V_{\rm LOTG} > V_{\rm acc}$ , the FWC drops linearly with  $V_{\rm LOTG}$ . As expected from section VI-A, the FWC increases with  $\Phi$  and decreases with T. It can also be observed that, as the temperature is increased from  $T=343~{\rm K}$  to  $T=363~{\rm K}$ , the FWC decreases more in region A ( $\Delta {\rm FWC_A} \approx 2000~{\rm e^-}$ ) than in region C ( $\Delta {\rm FWC_C} = 1200~{\rm e^-}$ ). This can be explained by the fact that the temperature dependence of  $I_{\rm sat}$  and  $I_{\rm D0}$  is not the same (in particular, for the biasing conditions in Fig. 11,  $I_{\rm sat}$  is a stronger function of temperature than  $I_{\rm D0}$ ).

#### VII. DYNAMIC BEHAVIOUR OF THE FWC

In the previous sections it has been assumed that, at full well, the PPD is at equilibrium (case of EFWC) or in a pseudo equilibrium state where photo-generation within the SCR is compensated by the charge diffusion toward the p-doped surrounding regions ( $I_{\rm junc}$ ) and eventually by the leakage of the TG ( $I_{\rm sub}$ ). However, if the operating conditions are suddenly changed, the time necessary to reach a new pseudo-equilibrium state can be much larger than the time between

<sup>&</sup>lt;sup>3</sup>This sub-threshod current contribution can also explain the phenomena reported in [18]

$<sup>^4 {\</sup>rm This}$  simplification is not used in the fitting model, where m is calculated as  $m=1+\frac{1}{C_{\rm ox}}\sqrt{\frac{\epsilon_{\rm Si}qNa_{\rm ch}}{4\Phi_B}}$  [10] and n is set to 1.75.

two acquisitions. This can lead to measurement uncertainty or to a wrong interpretation of experimental results. In this section, a new analytical model to describe the dynamic behaviour of the FWC in pulsed-light conditions is presented and validated with the support of experimental data. All measurements have been performed at room temperature.

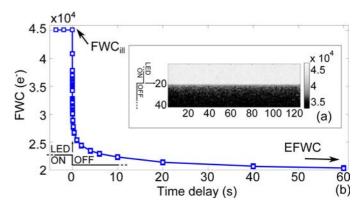

To observe the dynamic evolution of the PPD FWC, a light step has been applied by means of an LED placed at 15 cm from the detector 5, which is operated in rolling shutter mode. The pulse intensity is adjusted to reach the full well condition. The light is first turned ON and 100 images are acquired to ensure that the device has reached pseudo-equilibrium, then the LED is turned OFF. The sequence is repeated, sweeping the integration time from 34 ms (corresponding to the minimum integration time in this configuration) to 60 s. The image acquired during a light step (LED from ON to OFF) is shown in Fig. 12a. The top region (lines 1 to 20) corresponds to the lines which have been read while the LED was still ON. In this region the FWC is equal to the FWC measured under steady illumination (pseudo-equilibrium condition); in the bottom region (line 20 to 40), there is a quick drop in the stored charge. As the device is operated in rolling shutter mode, the FWC drop is attributed to the increase in the delay between the light step and the instant at which the line is readout.

Figure 12b shows the FWC as a function of the time delay between the light step and the line acquisition. The time resolution is  $135~\mu s$ , which corresponds to the time between the acquisition of two successive lines. As the time delay is increased, the FWC tends asymptotically toward a FWC of about 21 ke- which is close to the EFWC that can be extrapolated at room temperature in Fig. 6. Therefore, applying a light pulse can be a useful technique to fill the PPD to estimate the EFWC at room temperature (and below). Note that an integration time of several tens of seconds must be used to avoid an overestimation of the EFWC. Nevertheless, this integration time is shorter than the time required to fill the PPD only with thermally generated charges (which is a typical method to estimate EFWC).

In order to model the charge transient in the PPD, the data in Fig. 12 has been converted from electrons to PPD voltage, which at saturation corresponds to the open circuit voltage  $V_{\rm OC}$ . To simplify the model as much as possible,  $C_{\rm PPD}$  variations with  $V_{\rm OC}$  are neglected. Under these assumptions,  $V_{\rm OC}$  can be approximated to:

$$V_{\rm OC}(t) \approx \frac{q}{C_{\rm PPD}} \left[ {\rm EFWC - FWC}(t) \right]$$

(14)

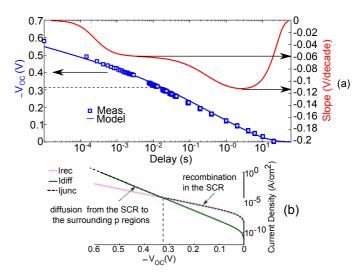

where  $V_{\rm OC}>0$  (the PPD is forward biased). Figure 13 shows  $V_{\rm OC}$  calculated as (14), plotted as a function of time (in logarithmic scale)<sup>6</sup>. The figure also shows the slope of the curve as a function of time. As it can be observed the slope reaches a first plateau at -0.06 V/decade and then a second plateau at -0.12 V/decade. As discussed in the

Fig. 12. (a) Image acquired while the light is turned from ON to OFF. A sudden drop in the FWC can be observed after line 20, which corresponds to the last line to be readout before the LED is turned off. (b) Measured mean output charge as a function of the time delay between the light step and the line acquisition at  $T=300~{\rm K}$  and  $V_{\rm LOTG}=-0.5~{\rm V}$ .

Fig. 13. Measured and simulated  $V_{\rm OC}$  as a function of the delay between the light step and the line acquisition. Two regimes corresponding to two different time constants can be identified by observing the slope of  $V_{\rm OC}(t)$ . These regimes are attributed to the diffusion of charges from the PPD SCR to the surrounding p-regions and to charge recombination within the SCR, respectively. (b) Simulated diffusion and recombination currents as a function of  $V_{\rm OC}$ .

following, these two different time constants are associated to two different regimes of  $I_{\rm junc}$ .

When the light is turned OFF, the time variation of the charge stored in the PPD can be expressed as:

$$\frac{\partial \text{FWC}(t)}{\partial t} = -\frac{1}{q} \left( I_{\text{junc}} + I_{\text{sub}} \right). \tag{15}$$

To simplify the analysis,  $I_{\rm sub}$  will be neglected (for consistency, experimental data have been obtained with  $V_{\rm LOTG}=-0.5~{\rm V}$ ).

In forward bias, the diode current  $I_{junc}$  can be expressed as the sum of two current contributions [10]:

$$I_{\text{rec}} = A_{\text{PPD}} \frac{q n_i W}{2\tau_0} \left[ e^{\frac{-q V_{OC}}{2kT}} - 1 \right]$$

(16)

$$I_{\text{diff}} = A_{\text{PPD}} \frac{q D_n n_i^2}{N_o L_n} \left[ e^{\frac{-q V_{OC}}{kT}} - 1 \right]$$

(17)

<sup>&</sup>lt;sup>5</sup>This set-up corresponds to a typical image-lag measurement set-up.

$<sup>^6</sup>$ The best fit has been obtained for  $C_{\rm PPD} = 5.4~{\rm fF}$ , which is between the maximum (7.5 fF) and minimum (4 fF) PPD capacitance extracted in [14] for the same pixel geometry at room temperature.

where  $I_{\rm rec}$  is the recombination current within the SCR, with  $\tau_0$  the minority carrier life-time and  $I_{\rm diff}$  the diffusion current from the PPD to the surrounding p-regions. As shown in Fig. 13b, the diffusion current dominates at large forward bias, and is responsible for the quick FWC drop following the light pulse. At lower forward voltages the recombination current becomes the main current contribution, which is responsible for the slow descend of the FWC toward the EFWC. The behaviour of the FWC as function of time can be obtained from (14) with

$$V_{\rm OC}(t) = V_{\rm OC}(t_{0^-}) + \frac{1}{C_{\rm PPD}} \int_0^{T_{int}} I_{\rm junc}(t) dt$$

(18)

where  $V_{\rm OC}(t_{0^-})$  is the open circuit voltage corresponding to the FWC with the LED ON ( $V_{\rm OC}(t_{0^-})<0$ ). As shown in Fig. 13 the model is able to reproduce the dynamic behavior of the FWC over 6 time delay decades. The small difference at very short delays can be explained by a very fast increase in  $C_{\rm PPD}$  at high forward biasing voltages (which is not taken into account in the model).

#### VIII. SUMMARY AND CONCLUSION

The analytical model of the PPD FWC proposed in [6] has been extended. It has been shown that the FWC is highly dependent on the operating conditions. In particular, the FWC has been studied in three saturation conditions:

- at equilibrium: the FWC corresponds to the EFWC. It only depends on  $V_{\rm pin}$  and  $C_{\rm PPD}$ ;

- under illumination with the TG accumulated: the PPD is forward biased, and FWC > EFWC;

- with the TG not accumulated ( $V_{\rm LOTG} > V_{\rm acc}$ ): the PPD is forward biased (FWC > EFWC) or reverse biased (FWC < EFWC) depending on the illumination level.

The model has been validated with the support of experimental data and its range of application has been extended by introducing the effect of temperature on the saturation level. For this purpose, a temperature model of the pinning voltage has been proposed. This study showed that opposite trends can be observed depending on the operating conditions:

- in the dark: the FWC increases for increasing temperature. Its variation is attributed to the increase of  $V_{\rm pin}$ .

- Under illumination: the FWC decreases for increasing temperatures (as long as  $\frac{I_{\rm ph}(\Phi)}{I_{\rm sat}} >> 1$ ). Its variation is attributed to the exponential increase of  $I_{\rm sat}$  with temperature, which results in a lower  $V_{\rm OC}$ .

Understanding the effect of temperature can be of great importance as it can highlight the variation of one specific parameter (such as the dark current, the pinning voltage or the TG threshold voltage and leakage current) following geometrical variations or radiation campaigns [19].

This work also discussed the dynamic behaviour of the FWC in non steady-state light conditions. It has been shown that once the light source is removed, the FWC drops toward the EFWC as the PPD recovers from forward bias to equilibrium. To explain this behaviour, this study proposed a dynamic model of the FWC based on the different current regimes in a p-n junction. The model is able to reproduce

the experimental behaviour over a wide range of time delays (about 6 decades). As the FWC strongly depends on the previous and next operating conditions and on the time elapsed since the experimental variation, the proposed model can be a useful tool to study non-equilibrium transients, e.g. PPD voltage variations between two different operating conditions. Furthermore, these results underline the importance of carefully choosing the pulse intensity in image lag measurements. In particular, if the EFWC condition is exceeded during the light pulse, Charge Transfer Efficiency (CTE) measurements can be affected by the FWC transient toward the EFWC, leading to a wrong interpretation of the experimental results.

Finally, this study not only validates and extends the model proposed in [6], but also validates the pinning voltage extraction method presented in [14] and underlines the importance of relevant FWC levels such as the EFWC in the understanding of the PPD static and dynamic behaviour.

#### REFERENCES

- [1] N. Teranishi, A. Kohono, Y. Ishihara, E. Oda, and K. Arai, "No image lag photodiode structure in the interline CCD image sensor," in *Electron Devices Meeting*, 1982 International, vol. 28, 1982, pp. 324–327.

- [2] B. Burkey, W. Chang, J. Littlehale, T. Lee, T. Tredwell, J. Lavine, and E. Trabka, "The pinned photodiode for an interline-transfer CCD image sensor," in *Electron Devices Meeting*, 1984 International, vol. 30, 1984, pp. 28 – 31.

- [3] E. Fossum and D. Hondongwa, "A review of the pinned photodiode for CCD and CMOS image sensors," *Electron Devices Society, IEEE Journal of the*, vol. 2, no. 3, pp. 33–43, May 2014.

- [4] A. BenMoussa, B. Giordanengo, S. Gissot, G. Meynants, X. Wang, B. Wolfs, J. Bogaerts, U. Schuhle, G. Berger, A. Gottwald, C. Laubis, U. Kroth, and F. Scholze, "Characterization of backside-illuminated CMOS APS prototypes for the extreme ultraviolet imager on-board solar orbiter," *IEEE Transactions on Electron Devices*, vol. 60, no. 5, pp. 1701–1708, 2013.

- [5] G. Meynants, "Global shutter pixels with correlated double sampling for CMOS image sensors," *Advanced Optical Technologies*, vol. 2, no. 2, pp. 177–187, 2013.

- [6] A. Pelamatti, V. Goiffon, M. Estribeau, P. Cervantes, and P. Magnan, "Estimation and modeling of the full well capacity in pinned photodiode CMOS image sensors," *IEEE Electron Device Letters*, vol. 34, no. 7, pp. 900–902, July 2013.

- [7] A. Krymski, N. E. Bock, N. Tu, D. Blerkom, and E. R. Fossum, "Estimates for scaling of pinned photodiodes," in *IEEE Workshop in CCD and Advanced Image Sensors*, vol. 60, 2005.

- [8] S. Park and H. Uh, "The effect of size on photodiode pinch-off voltage for small pixel CMOS image sensors," *Microelectronics Journal*, vol. 40, no. 1, p. 137140, 2009.

- [9] Y. Lim, K. Lee, H. Hong, J. Kim, S. Sa, J. Lee, D. Kim, and J. Hynecek, "Stratified photodiodea new concept for small size high performance CMOS image sensor pixels," in *Proc. 2007 International Image Sensor Workshop*, 2007, pp. 311–315.

- [10] Y. Taur and T. H. Ning, Fundamentals of Modern VLSI Devices, 2nd ed. Cambridge University Press, Aug. 2009.

- [11] K. Misiakos, D. Tsamakis, D. Tsamakis, and D. Tsamakis, "Accurate measurements of the silicon intrinsic carrier density from 78 to 340 k," *J. Appl. Phys.*, vol. 74, no. 5, p. 3293, 1993.

- [12] H. Takeshita, T. Sawada, T. Iida, K. Yasutomi, and S. Kawahito, "High-speed charge transfer pinned-photodiode for a cmos time-of-flight range image sensor," vol. 7536, 2010.

- [13] J. Tan, B. Buttgen, and A. J. P. Theuwissen, "Analyzing the radiation degradation of 4-transistor deep submicron technology CMOS image sensors," *IEEE Sensors Journal*, vol. 12, no. 6, pp. 2278–2286, Jun. 2012.

- [14] V. Goiffon, M. Estribeau, J. Michelot, P. Cervantes, A. Pelamatti, O. Marcelot, and P. Magnan, "Pixel level characterization of pinned photodiode and transfer gate physical parameters in CMOS image sensors," *Electron Devices Society, IEEE Journal of the*, vol. 2, no. 4, pp. 65–76, Jul. 2014.

- [15] N. Teranishi and N. Mutoh, "Partition noise in CCD signal detection," IEEE Transactions on Electron Devices, vol. 33, no. 11, pp. 1696–1701, Nov. 1986

- [16] B. Mheen, Y.-J. Song, and A. Theuwissen, "Negative offset operation of four-transistor CMOS image pixels for increased well capacity and suppressed dark current," *IEEE Electron Device Lett.*, vol. 29, no. 4, pp. 347 –349, Apr. 2008.

- [17] T. Watanabe, J.-H. Park, S. Aoyama, K. Isobe, and S. Kawahito, "Effects of negative-bias operation and optical stress on dark current in CMOS image sensors," *IEEE Trans. Electron Devices*, vol. 57, no. 7, pp. 1512 –1518, Jul. 2010.

- [18] M. Sarkar, B. Buttgen, and A. Theuwissen, "Feedforward effect in standard CMOS pinned photodiodes," *IEEE Trans. Electron Devices*, vol. 60, no. 3, pp. 1154–1161, 2013.

- [19] V. Goiffon, M. Estribeau, P. Cervantes, R. Molina, M. Gaillardin, and P. Magnan, "Influence of transfer gate design and bias on the radiation hardness of pinned photodiode cmos image sensors," *Nuclear Science*, *IEEE Transactions*, vol. 61, no. 6, pp. 3290–3301, oct 2014.