#### An athermal measurement technique for long time constants traps characterization in GaN HEMT transistors

Alexis Divay, Mohamed Lamine Masmoudi, Olivier Latry, Cédric Duperrier, Farid Temcamani

#### ▶ To cite this version:

Alexis Divay, Mohamed Lamine Masmoudi, Olivier Latry, Cédric Duperrier, Farid Temcamani. An athermal measurement technique for long time constants traps characterization in GaN HEMT transistors. ESREF 2015, Oct 2015, Toulouse, France. hal-01230925

#### HAL Id: hal-01230925 https://hal.science/hal-01230925

Submitted on 19 Nov 2015

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# An athermal measurement technique for long time constants traps characterization in GaN HEMT transistors

Eroupe de Physique des Matériaux

A. Divay<sup>a</sup>, M. Masmoudi<sup>a</sup>, O. Latry<sup>a</sup>, C. Duperrier<sup>b</sup>, F. Temcamani<sup>c</sup>

<sup>a</sup> Normandie Université, University of Rouen, GPM UMR CNRS 6634, 76300 Saint Etienne du Rouvray, France , <sup>b</sup>University of Cergy, ETIS UMR 8051 CNRS, ENSEA, 95000 Cergy-Pontoise, France , <sup>c</sup>ECS-Lab, ENSEA, 95000 Cergy-Pontoise, France

### Introduction

- The trap characterization techniques generally used on GaN HEMT transistors are limited by self-heating (DLTS, DLOS, ...) [1].

- An athermal method is proposed in order to measure long time constant traps in GaN HEMT transistors.

- Defects with time constants ranging from several ms to 1000s are observable with limitation of self-heating effects.

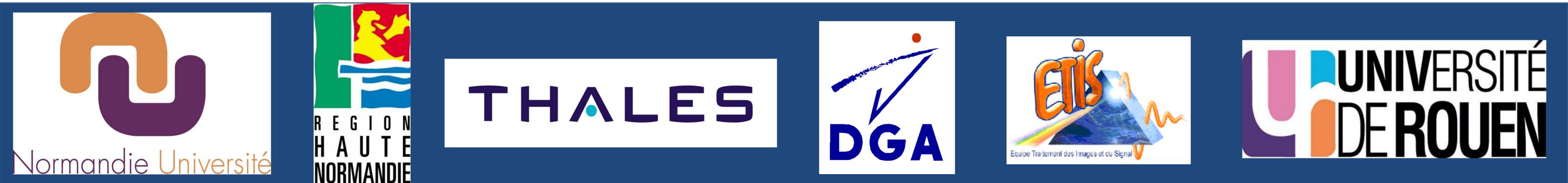

| Principle of the measurement technique                               |         | Ids(A) Ids me                        | easured<br>e and hold function | n)     |   |

|----------------------------------------------------------------------|---------|--------------------------------------|--------------------------------|--------|---|

| $Vgs (V) \xrightarrow[0]{t} 1 2 3 4 5 6 7 8 9$<br>IV Pulser Trig ext | Ids (A) | $_{\rm Vgs}(V) \stackrel{0}{\sim} A$ | Ids in<br>the transistor       | time(1 | m |

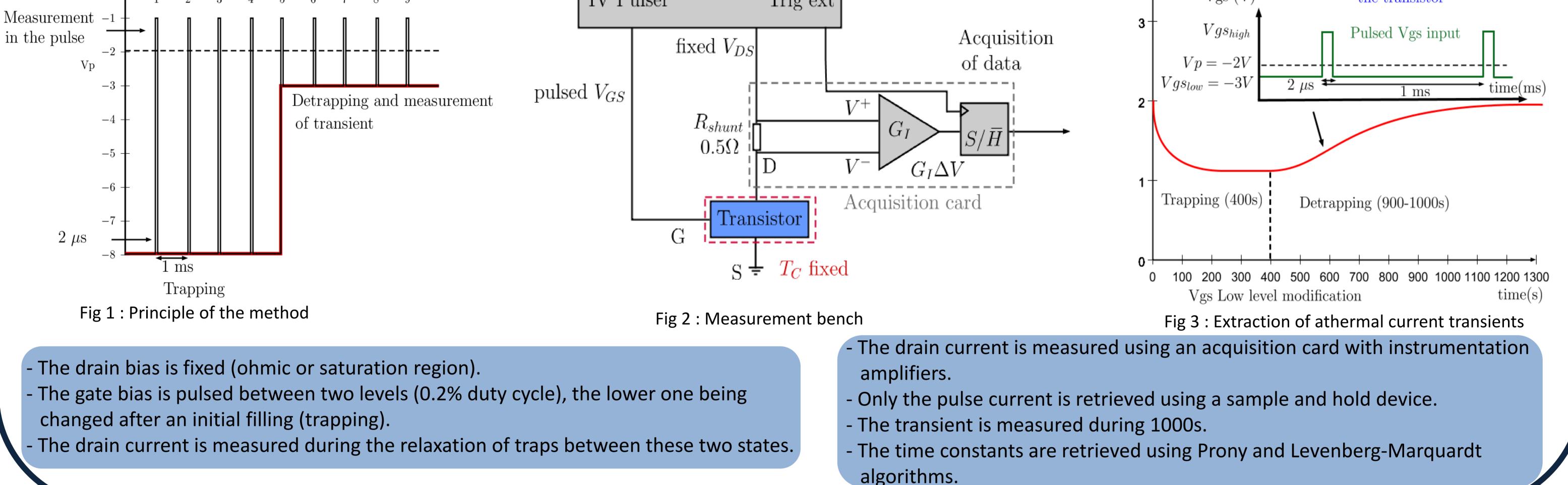

### Validation of the method using modeling

## Measurements on AlGaN/GaN HEMTs on SiC substrate

- Modeling of the electro-thermal source of the device using ADS (Advanced Design System).

- A generic trap activation energy is included in the model.

- Output : We extract the right activation energy down to  $\tau$  = 20ms.

- The concept is validated even for high current densities (around 0.42 A/mm).

- The simulated temperature rise is  $\Delta T_i = 0.4^{\circ}C$ .

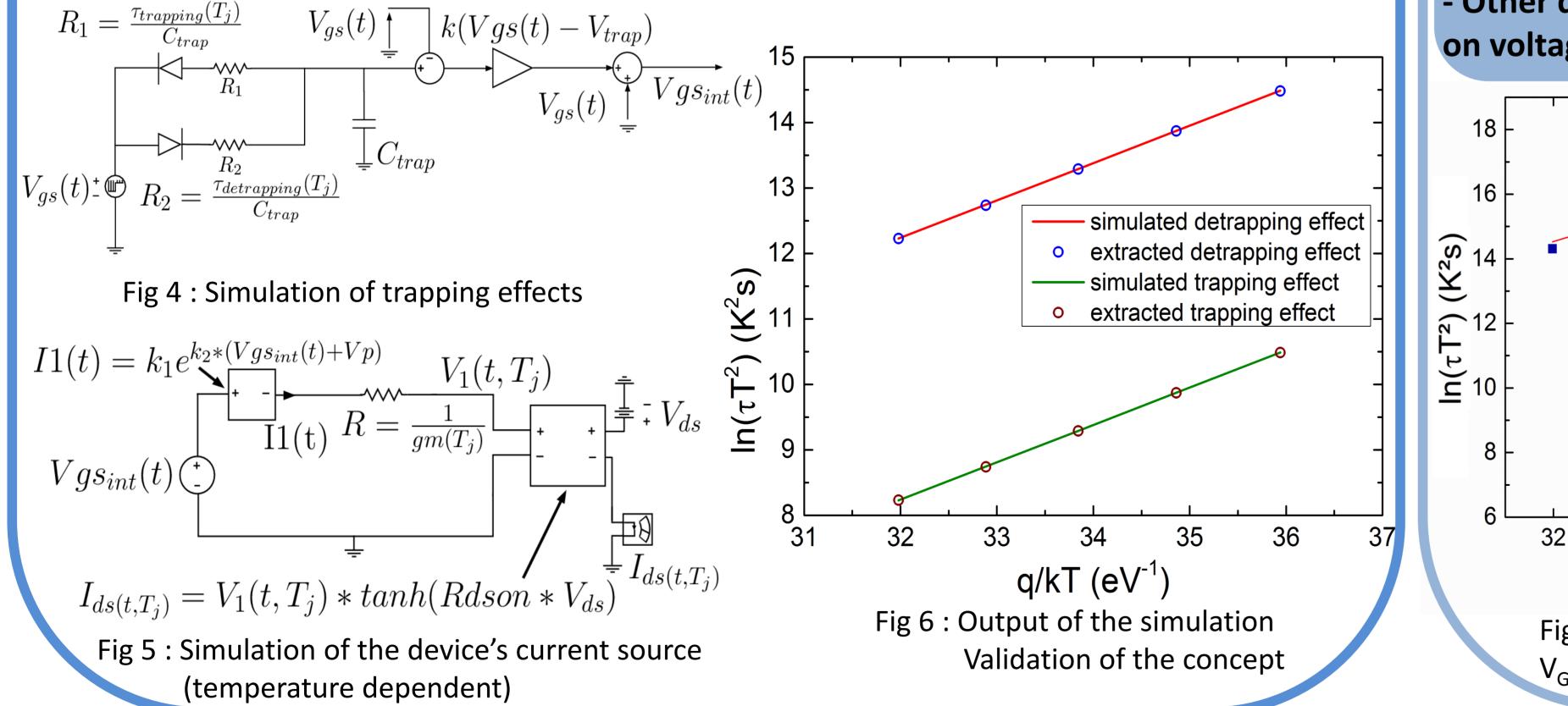

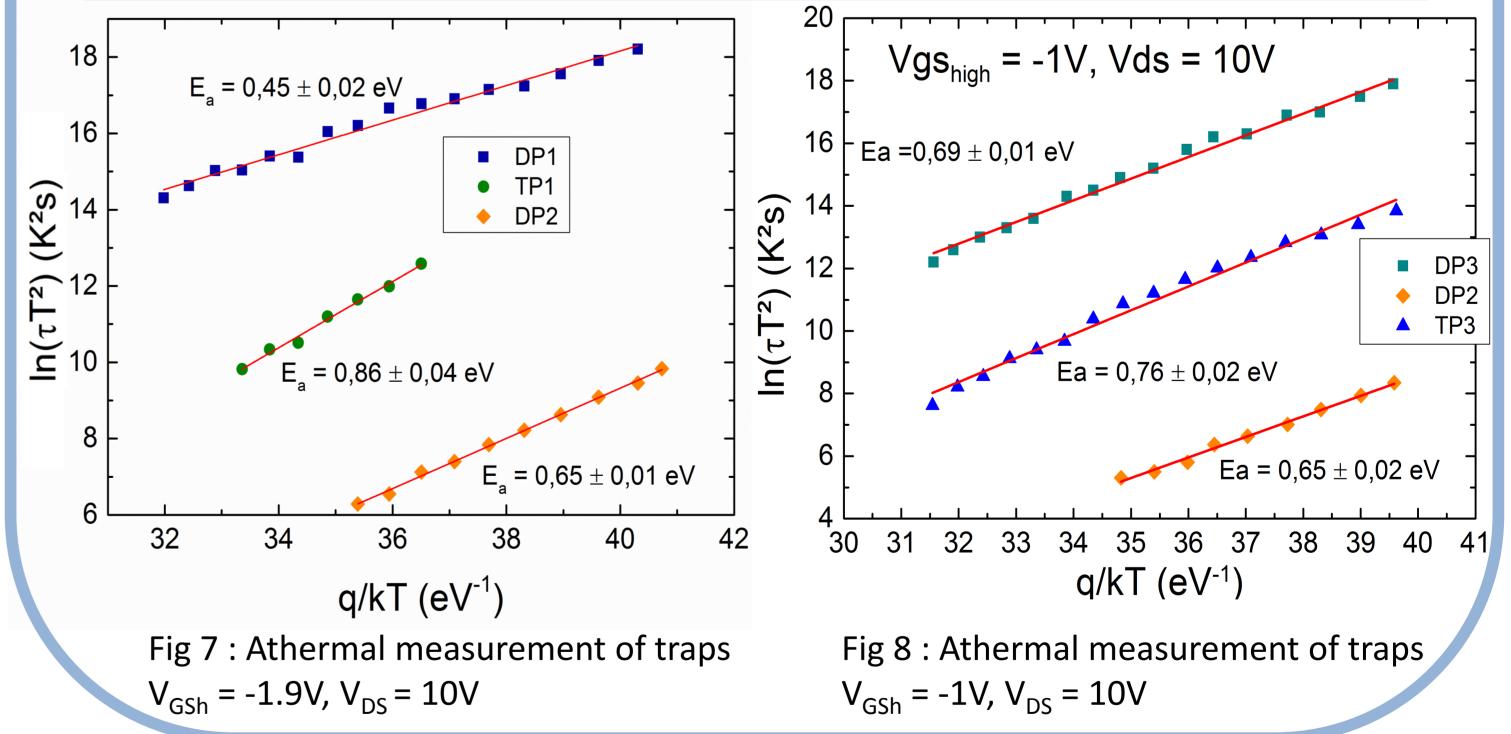

- Different polarization protocol were used in order to characterize the trapping state in GaN HEMT transistors : in saturation and ohmic region.

- Time constants are found to be slower in the ohmic region.

- A trap at Ea = 0.65 eV is found at every protocol (not dependent on voltage) and is linked to gallium vacancies [2].

- Other defects are retrieved at 0.45, 0.86, 0.69 and 0.76 eV which are dependent on voltage and temperature.

### Conclusion

- The measurement concept is validated by the simulation, the temperature rise during the measurement is estimated around 0.4°C.

- The various polarization protocols allow the measurement of traps in different localization and have shown several activation energies.

- A good precision on the extracted activation energies is obtained :  $\pm 0.02-0.04$  eV.

#### References

[1] J. Joh, J.A. del Alamo, J. Jimenez, IEEE Electron Trans. On Electron Devices 48 (3) (Mar. 2001) pp. 560-566

[2] L. Stuchlíková, J. Šebok, J. Rybár, et. Al., Advanced Semiconductor Devices & Microsystems (ASDAM), 2010 8th International Conference on (Oct. 25–27 2010), pp. 135–138